# **IBM** TECHNICAL NEWSLETTER

for the

# **RT Personal Computer Virtual Resource Manager**

#### Virtual Resource Manager Programming Reference

© Copyright International Business Machines Corporation 1985, 1987 © Copyright Motorola, Inc. 1985

—OVER—

**Order Numbers:** 79X3823 SN20-9858 June 26, 1987 © Copyright IBM Corp. 1987

TB79X3824 Printed in U.S.A.

#### **Summary of Changes**

This technical newsletter provides additional command and device support available with the Virtual Resource Manager.

A change to the text is indicated by a vertical bar to the left of the change.

Perform the following:

| Remove Pages    | <b>Insert Update Pages</b> |

|-----------------|----------------------------|

| Title page      | Title page                 |

| 1-11 and 1-12   | 1-11 and 1-12              |

| 2-7 and 2-8     | 2-7 and 2-8                |

| 2-15 and 2-16   | 2-15 and 2-16              |

| 3-7 to 3-10     | 3-7 to 3-10                |

| 4-65 to 4-70    | 4-65 to 4-70               |

| 5-23 and 5-24   | 5-23 and 5-24              |

| 5-33 to 5-36    | 5-33 to 5-36               |

| 5-141 and 5-142 | 5-141 and 5-142            |

| 7-1 to 7-14     | 7-1 to 7-24                |

| 8-7 and 8-8     | 8-7 and 8-8                |

| D-21 and D-22   | D-21 to D-24               |

**Note:** Please file this cover letter at the back of the manual to provide a record of changes.

# Virtual Resource Manager Programming Reference

**Programming Family**

Personal Computer Software

#### First Edition (January 1987)

This edition applies to Version 2.1 of the Virtual Resource Manager, and to all subsequent releases until otherwise indicated in new editions or technical newsletters. Changes are made periodically to the information herein; these changes will be incorporated in new editions of this publication.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

International Business Machines Corporation provides this manual "as is," without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this manual at any time.

Products are not stocked at the address given below. Requests for copies of this product and for technical information about the system should be made to your authorized IBM RT Personal Computer dealer.

A reader's comment form is provided at the back of this publication. If the form has been removed, address comments to IBM Corporation, Department 997, 11400 Burnet Road, Austin, Texas, 78758. IBM may use or distribute whatever information you supply in any way it; believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1985, 1987

Some material reprinted courtesy of Motorola, Inc.

©Copyright Motorola, Inc. 1985

## **About This Book**

#### **Audience and Purpose**

This book describes the Virtual Resource Manager (VRM), which is a collection of processes, device drivers, and commands that control and extend hardware functions for an operating system. The VRM shields the operating system from hardware changes and allows more than one operating system (and their applications) to run simultaneously.

This book also defines the Virtual Machine Interface (VMI) to the VRM. The VMI controls how an operating system communicates with the VRM. This information is useful to developers who design or modify operating systems components that run in the virtual machine environment.

This book is intended for systems programmers and developers who need to understand the role of the Virtual Resource Manager in the RT Personal Computer<sup>1</sup>. The reader of this book is expected to have an understanding of hardware and operating systems fundamentals.

#### How to Use This Book

This book describes the programming environment of the Virtual Resource Manager (VRM), which is a software layer between the hardware and the operating system of the RT PC.

*Virtual Resource Manager Device Support* describes VRM IPL and configuration, as well as how the VRM supports specific devices and device subsystems.

The VRM communicates with operating systems by way of supervisor call instructions and virtual interrupts sent across the Virtual Machine Interface (VMI). The VMI provides a uniform interface to the various configurations of input/output devices operating below the virtual machine level.

<sup>&</sup>lt;sup>1</sup> RT Personal Computer, RT PC, and RT are trademarks of International Business Machines Corporation.

This book contains programming information on the VRM and virtual machine characteristics that will enable you to develop and implement processes, access methods, device drivers and other VRM components.

In addition to the calls that cross the VMI, this book also describes the internal VRM runtime routines and the commands used with the VRM debugger.

The book consists of the following sections:

Chapter 1, "Virtual Resource Manager Concepts" on page 1-1 provides a brief introduction to the VRM and its place in the RT PC system. This chapter provides a high-level overview of the characteristics of the VRM and the Virtual Machine Interface.

Chapter 2, "Virtual Machine Interface Characteristics" on page 2-1 goes into more detail about the VMI and discusses virtual machine control registers, interrupt processing, and accessing virtual memory segments.

Chapter 3, "VRM Programming Environment" on page 3-1 provides a closer look at the functional characteristics of the VRM. This chapter describes the I/O subsystem, naming conventions, and the component management tasks performed by the VRM.

Chapter 4, "System Control Instructions" on page 4-1 describes the instructions that can change the state of the virtual machine. These instructions are **load program status** and **supervisor call**. The supervisor call instructions are listed and defined.

Chapter 5, "Virtual Resource Manager Programming Interfaces" on page 5-1 lists and describes the VRM runtime routines that allow you to tailor the open-coded system to your needs and resources. These routines control everything the VRM does, including input/output control, device, queue and memory management, and error logging and trace capabilities.

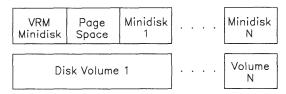

Chapter 6, "Managing Minidisks" on page 6-1 explains the functions related to the creation and management of minidisks in the system.

Chapter 7, "Floating-Point Services" on page 7-1 describes the floating-point computation support provided by the VRM for the various floating-point hardware options.

Chapter 8, "Virtual Resource Manager Debugger" on page 8-1 discusses how to use the VRM debugger to locate and correct errors in user-installed code.

Appendix A, "Index of Supervisor Call Instructions" on page A-1 lists the supervisor call instructions by number and indexes them to the appropriate page.

Appendix B, "TOC Object Module Information" on page B-1 provides information on the TOC (table of contents) object module format used by the VRM. This section is useful for developers who are adding code to or debugging code in the VRM.

Appendix C, "Key Sequences for System Functions" on page C-1 lists the IBM-defined keystroke combinations and the system function that results when you enter the particular key sequence. These key sequences pertain only to the standard RT PC keyboard.

Appendix D, "C Language VRM Subroutines" on page D-1 provides the C language equivalent to the VRM internal calls described in Chapter 5, "Virtual Resource Manager Programming Interfaces" on page 5-1. In addition, this appendix defines the external variables you may use with the VRM.

A glossary and index follow these chapters and appendices.

A Reader's Comment Form and Book Evaluation Form are provided at the back of this book. Use the Reader's Comment Form at any time to give IBM information that may improve the book. After you become familiar with the book, use the Book Evaluation Form to give IBM specific feedback about the book.

Please note the following items regarding hexadecimal notation, reserved fields, the bit padding and numbering conventions, and highlighting conventions used in this book:

- A hexadecimal value as expressed in this publication is preceded by a zero and a lowercase *x*. For example, the hexadecimal value 'F3' is represented as 0xF3.

- The value of reserved fields input to the Virtual Resource Manager must be set equal to zero. The value of reserved fields returned by the VRM is unpredictable.

- The bit-numbering convention used by IBM has the most significant bit on the left and the least significant bit for a given field on the right. For example, in a 32-bit word, the most significant bit (bit 0) is the leftmost bit and the least significant bit (bit 31) is the rightmost bit.

- High-order bits in a given field not used to express a value are padded with zeroes. For example, if an input parameter sent in a 32-bit register is only a 16-bit value, the value occupies bits 16 through 31 of the register and bits 0 through 15 of the register are padded with zeroes.

- Terms highlighted in bold-faced italics (such as *example*) are specific to the RT PC and are included in the glossary. Terms highlighted in bold type (such as *example*) are system-generated items, such as commands, file names, and so on. Terms or phrases that appear in monospace type (such as *example*) are examples of what you might see on a display screen or what you must enter into the system to perform a given function.

#### **Related Information**

The following RT PC publications provide additional information on topics related to the VRM. Depending on the tasks you want to perform and your experience level, you may want to refer to the following publications:

- *IBM RT PC Installing and Customizing the AIX Operating System* provides step-bystep instructions for installing and customizing the Advanced Interactive Executive<sup>2</sup> Operating System, including how to add or delete devices from the system and how to define device characteristics. This book also explains how to create, delete, or change AIX and non-AIX minidisks.

- *IBM RT PC Installing the Virtual Resource Manager* provides step-by-step instructions for installing the Virtual Resource Manager and shows you how to change the IBM-recommended choices to suit your system needs. (Available as a separate volume only when the Virtual Resource Manager is purchased separately from the AIX Operating System.)

- *IBM RT PC Hardware Technical Reference* is a three-volume set. Volume I describes how the system unit operates, including I/O interfaces, serial ports, memory interfaces, and CPU interface instructions. Volumes II and III describe adapter interfaces for optional devices and communications and include information about IBM Personal Computer family options and the adapters supported by 6151 and 6150. (Available optionally)

- *IBM RT PC Assembler Language Reference* describes the IBM RT PC Assembler Language and the 032 Microprocessor and includes descriptions of syntax and semantics, machine instructions, and pseudo-operations. This book also shows how to link and run Assembler Language programs, including linking to programs written in C language. (Available optionally)

- *IBM RT PC AIX Operating System Programming Tools and Interfaces* describes the programming environment of the AIX Operating System and includes information about using the operating system tools to develop, compile, and debug programs. In addition, this book describes the operating system services and how to take advantage of them in a program. This book also includes a diskette that includes programming examples, written in C language, to illustrate using system calls and subroutines in short, working programs. (Available optionally)

- *IBM RT PC Messages Reference* lists messages displayed by the IBM RT PC and explains how to respond to the messages.

- *IBM RT PC AIX Operating System Commands Reference* lists and describes the AIX Operating System commands.

<sup>&</sup>lt;sup>2</sup> Advanced Interactive Executive and AIX are trademarks of International Business Machines Corporation.

- *IBM RT PC C Language Guide and Reference* provides guide information for writing, compiling, and running C language programs and includes reference information about C language data structures, operators, expressions, and statements. (Available optionally)

- *IBM RT PC Problem Determination Guide* provides instructions for running diagnostic routines to locate and identify hardware problems. A problem determination guide for software and three high-capacity (1.2MB) diskettes containing the IBM RT PC diagnostic routines are included.

- *IBM RT PC Keyboard Description and Character Reference* describes the national character and keyboard support for the 101-key, 102-key, and 106-key keyboards, including keyboard position codes, keyboard states, control code points., code sequence processing, and nonspacing character sequences.

- *RT PC VRM/Hardware Quick Reference* contains brief descriptions of the hardware and Virtual Resource Manager. This booklet includes information on command parameters and return codes and hardware and memory layout data.

- *IBM RT PC AIX Operating System Technical Reference* describes the system calls and subroutines that a C programmer uses to write programs for the AIX Operating System. This book also includes information about the AIX file system, special files, file formats, GSL subroutines, and writing device drivers. (Available optionally)

#### **Ordering Additional Copies of This Book**

To order additional copies of this book (without program diskettes), use either of the following sources:

- To order from your IBM representative, use Order Number SBOF-0136.

- To order from your IBM dealer, use Part Number 79X3822.

Two binders and the *Virtual Resource Manager Technical Reference* are included with the order. For information on ordering a binder, books, or the *RT PC VRM/Hardware Quick Reference* separately, contact your IBM representative or your IBM dealer.

## Contents

| Chapter 1. Virtual Resource Manager Concepts1-About This Chapter1Understanding the VRM1Understanding the VMI1Processor and Virtual Machine States1Virtual Memory Management1-Input/Output Subsystem1-                                                                         | 3<br>4<br>5<br>9<br>11<br>14                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Virtual Machine Communications1-                                                                                                                                                                                                                                              | 17                                                                                                                                    |

| Chapter 2. Virtual Machine Interface Characteristics       2         About This Chapter       2         VMI Components and Characteristics       2         Virtual Machine Interrupts       2         Access to Segments       2-2                                            | 2-3<br>2-4<br>14                                                                                                                      |

| Chapter 3. VRM Programming Environment3-About This Chapter3VRM Internal Characteristics3Device Management3-Process Management3-Queue Management3-Semaphore Management3-Timer Management3-Program Management3-Minidisk Management3-                                            | <ul> <li>3-3</li> <li>3-4</li> <li>3-8</li> <li>13</li> <li>13</li> <li>18</li> <li>20</li> <li>28</li> <li>29</li> <li>30</li> </ul> |

| Chapter 4. System Control Instructions4About This Chapter4Load Program Status Instruction4Supervisor Call Instructions4Execution Control SVCs4Memory Management SVCs4-2Input/Output SVCs4-2Virtual Machine Communications SVCs4-7Machine Control SVCs4-7NVRAM Control SVCs4-8 | -5<br>-6<br>-7<br>-9<br>23<br>46<br>72<br>76                                                                                          |

| Chapter 5. Virtual Resource Manager Programming Interfaces . 5-1 |

|------------------------------------------------------------------|

| About This Chapter                                               |

| Process Management                                               |

| Memory Management                                                |

| Semaphore Management                                             |

| Timer Management                                                 |

| Program Management                                               |

| Virtual Machine Control Procedures                               |

| Input/Output Procedures                                          |

| Minidisk Management                                              |

| Device Management                                                |

| VRM Trace and Error Process Interfaces                           |

| Event Monitoring                                                 |

|                                                                  |

| Chapter 6. Managing Minidisks 6-1                                |

| About This Chapter                                               |

| Minidisk Manager Operations                                      |

| Data Access Operations                                           |

| Query Operations                                                 |

|                                                                  |

| Chapter 7. Floating-Point Services                               |

| About This Chapter                                               |

| VRM Floating-Point Support                                       |

|                                                                  |

| Chapter 8. Virtual Resource Manager Debugger                     |

| About this Chapter                                               |

| Debugging Code in the VRM                                        |

| Debugger Programming Interfaces                                  |

| Rules for Entering Commands                                      |

| Debugger Commands                                                |

| Debugger Commanus                                                |

| Appendix A. Index of Supervisor Call Instructions                |

| Annualize D. TOC Object Medicle Information D1                   |

| Appendix B. TOC Object Module Information                        |

| TOC Object Module Format                                         |

| TOC Object Module Definition                                     |

| Subroutine Linkage ConventionsB-8                                |

| Appendix C. Key Sequences for System Functions                   |

| Appendix D. C Language VRM Subroutines                           |

| Glossary | •• | •• | • | •• | • | •• | • | • | • | ••  | • | • | • | • | • | • | • | ••  | • | • | • | • | • | • • | • • | • | • | • | • • | • | • | • | • | •• | • | • | • | ••  | 2  | <b>X-</b> 2 | 1 |

|----------|----|----|---|----|---|----|---|---|---|-----|---|---|---|---|---|---|---|-----|---|---|---|---|---|-----|-----|---|---|---|-----|---|---|---|---|----|---|---|---|-----|----|-------------|---|

| Index    | •• | •• | • | •• | • | •• | • | • | • | • • | • | • | • | • | • | • | • | • • | • | • | • | • | • | • • |     | • | • | • | • • | • | • | • | • | •• | • | • | • | . ] | X- | 1           | 3 |

# Figures

| 1-1.  | RT PC System Structure                                |

|-------|-------------------------------------------------------|

| 1-2.  | RT PC Architecture Model                              |

| 1-3.  | The VMI and Multiple Virtual Machines                 |

| 1-4.  | Processor and Virtual Machine States 1-11             |

| 1-5.  | Virtual Memory Units                                  |

| 1-6.  | Virtual Memory Addressing 1-14                        |

| 2-1.  | Memory Locations Used as Virtual Registers            |

|       | Virtual Timer Status Register                         |

| 2-3.  | Virtual Machine Program Status Block Locations        |

| 2-4.  | Virtual Machine Program Status Block 2-17             |

| 2-5.  | Status Flags for Execution-Level Interrupts 2-19      |

| 3-1.  | Virtual Resource Manager Structure                    |

|       | VRM I/O Subsystem                                     |

| 3-3.  | Virtual Resource Manager Elements                     |

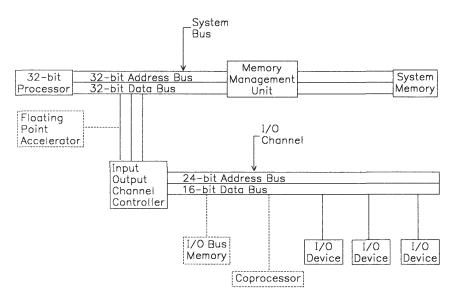

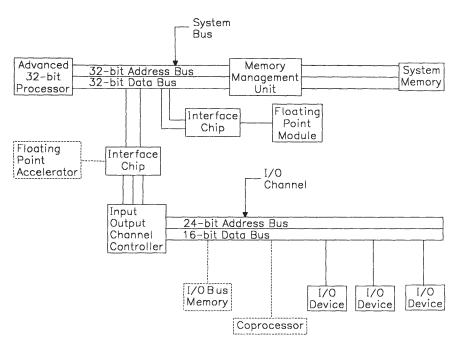

| 3-4.  | RT PC Hardware Structure with Standard Processor Card |

| 3-5.  | RT PC Hardware Structure with Advanced Processor Card |

| 3-6.  | Exception Control Register Format                     |

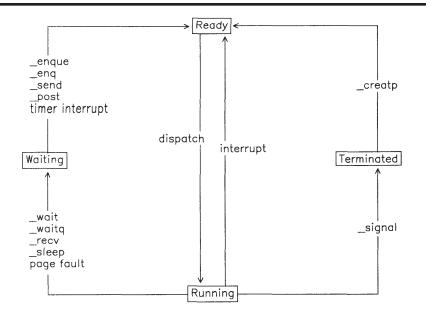

| 3-7.  | VRM Process States                                    |

| 3-8.  | Rules for Process State Change                        |

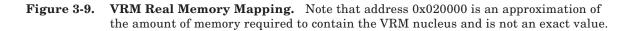

| 3-9.  | VRM Real Memory Mapping 3-21                          |

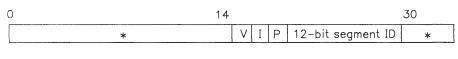

|       | Segment Register Bit Map 3-22                         |

| 3-11. | VRM Virtual Memory Map/Segment Register Conventions   |

| 3-12. | Segment Register 15 Mapping 3-24                      |

|       | Minidisk Map                                          |

|       | SVC Types                                             |

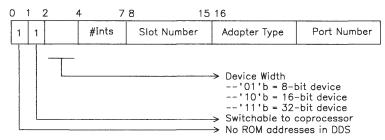

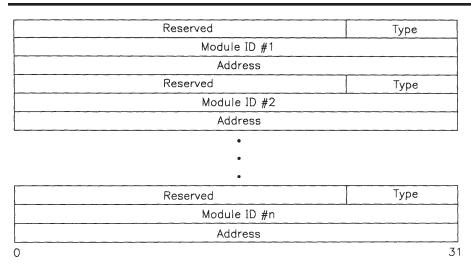

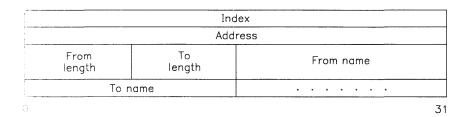

| 4-2.  | Define Device Structure — Header                      |

| 4-3.  | Define Device Structure — Hardware Characteristics    |

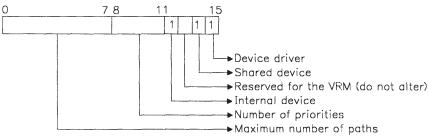

| 4-4.  | Internal Device Type                                  |

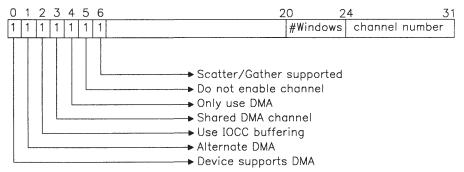

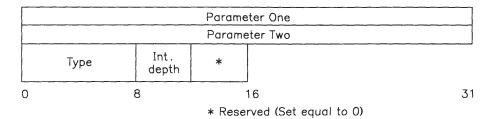

| 4-5.  | DMA Type                                              |

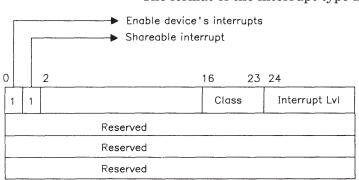

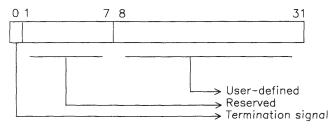

| 4-6.  | Interrupt Type                                        |

| 4-7.  | Operation Completion Information                      |

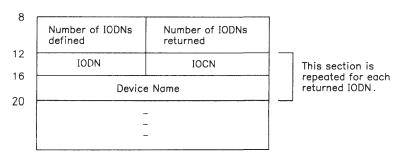

| 4-8.  | Query Device Structure (IODN = 0) 4-60                |

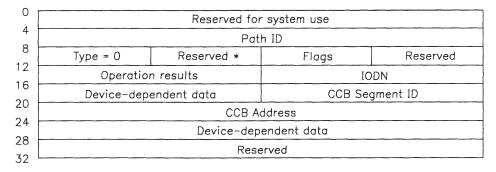

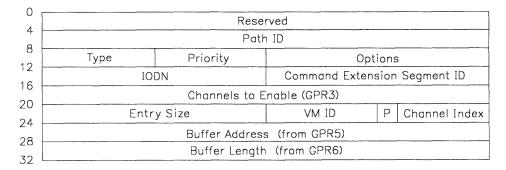

|       | Send Command Program Status Block 4-66                |

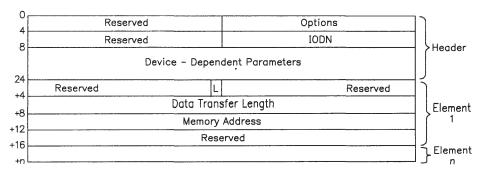

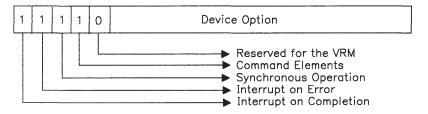

|       | Command Control Block (CCB)                           |

| 4-11. | Start I/O Program Status Block                        |

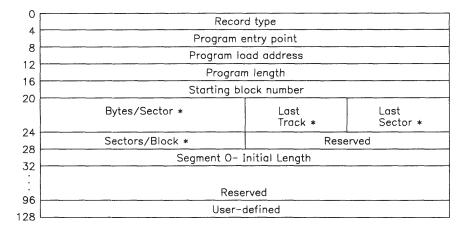

|       | IPL Record Format                                     |

|       | Virtual Machine Program Status Block from IPL         |

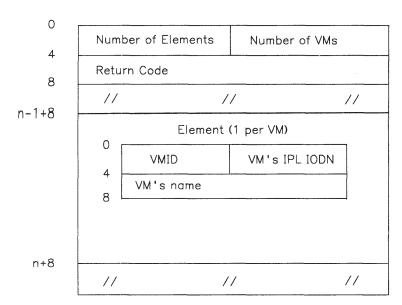

| 4-14. | Structure Returned from "Query VM SVC" 4-84           |

| 4-15. | Layout of NVRAM 4-88                                  |

|       |                                                       |

| 5-1.    | Entry Point Array Structure for _change                | 5-9     |

|---------|--------------------------------------------------------|---------|

| 5-2.    | Signal Mask                                            | 5-14    |

| 5-3.    | Acknowledge Parameters                                 | 5-18    |

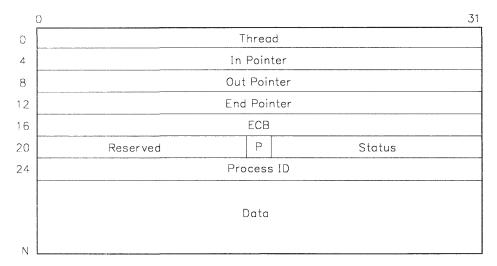

| 5-4.    | Start I/O Acknowledgement Queue Element                | 5-26    |

| 5-5.    | Send Command Acknowledgement Queue Element             | 5-26    |

| 5-6.    | General Purpose Acknowledgement Queue Element          | 5-27    |

| 5-7.    | Send Command Queue Element Format                      | 5-33    |

| 5-8.    | Start I/O Queue Element Format                         | 5-33    |

| 5-9.    | General Purpose Queue Element Format                   | 5-33    |

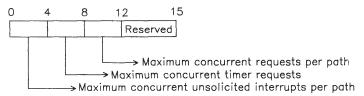

| 5-10.   | Query Path Structure                                   | 5-38    |

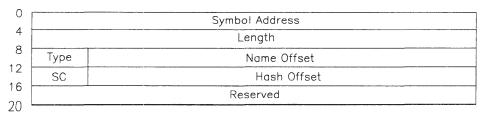

| 5-11.   | Symbols List for _bind                                 | 5-76    |

| 5-12.   | Structure Returned from _queryv                        | 5-83    |

| 5 - 13. | VRM Ring Queue                                         | 5-92    |

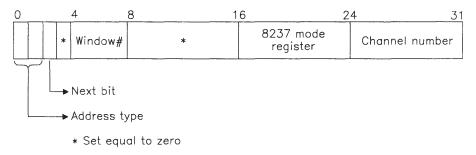

| 5-14.   | DMA Type Field                                         | 5-98    |

| 5 - 15. | Query Device Structure                                 | . 5-116 |

| 5-16.   | Send Command Queue Element for errrecvr                | . 5-120 |

|         | Acknowledgement Queue Element for errrecvr             |         |

| 5-18.   | Error Entry Acknowledgement Queue Element for errrecvr | . 5-122 |

| 5-19.   | Send Command Queue Element for trace                   | . 5-123 |

| 5-20.   | Acknowledgement Queue Element for trace                | . 5-124 |

| 5-21.   | Send Command Queue Element for trace                   | . 5-125 |

|         | Acknowledgement Queue Element for trace                |         |

|         | Acknowledgement Queue Element for trace                |         |

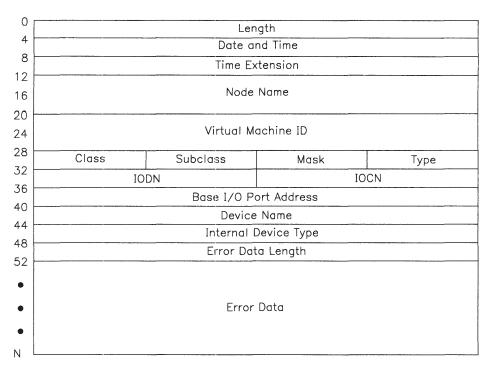

| 5-24.   | Hardware Error Entry Structure                         | . 5-130 |

| 5-25.   | Non-Hardware Error Entry Structure                     | . 5-131 |

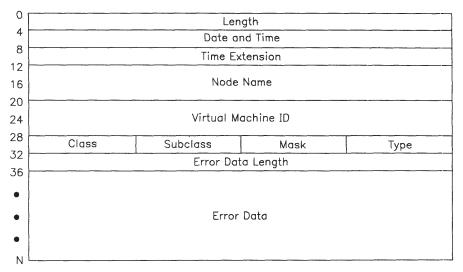

|         | Generic Trace Entry Structure                          |         |

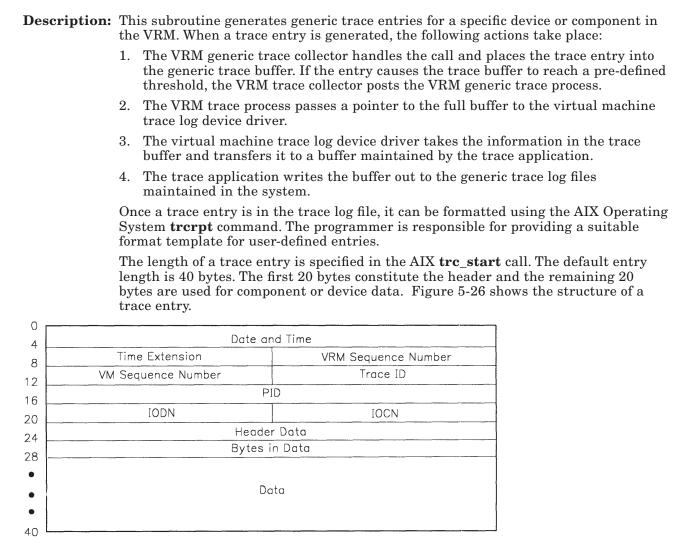

|         | Trace Entry Structure                                  |         |

| 5-28.   | Trace Entry Format                                     | . 5-138 |

| 5-29.   | Tables Used to Identify Data Structures to be Dumped   | . 5-140 |

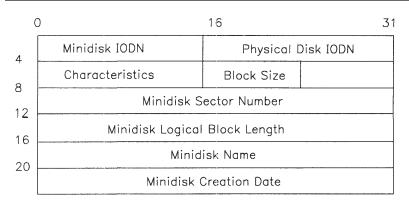

| 6-1.    | 'Query Minidisk' Structure                             | 6-20    |

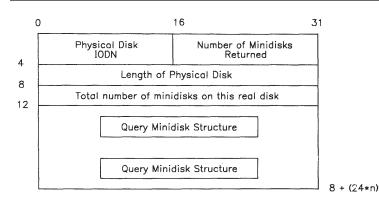

|         | 'Query All Minidisks' Structure                        |         |

|         | Minidisk Command Header Format                         |         |

| 7-1.    | PSB Data Word 1 for Floating-Point Exceptions          | 7-11    |

|         | Screen produced by the Help command                    |         |

|         | Breakpoint Display                                     |         |

|         | CTldsp Command Selection Menu                          |         |

| 8-4.    | Semaphore Control Block Display                        | 8-23    |

|         | Timer Request Block Display                            |         |

| 8-6.    | Process Control Block Display                          | 8-26    |

|         | SLIH Control Block Display                             |         |

|         | SLIH Chain Display                                     |         |

|         | Module Table Entry Display                             |         |

| 8-10.   | Device Table Entry                                     | 8-31    |

| 8-11.   | Generic Control Block Display                          | 8-32    |

| 8-12.   | Prompt for Queue Element Selection                     | 8-33    |

| 8-13. | Response Queue Element                        |

|-------|-----------------------------------------------|

|       | Send Command Queue Element                    |

| 8-15. | Start I/O Queue Element                       |

| 8-16. | General Purpose Queue Element                 |

|       | Detach Queue Element                          |

| 8-18. | Utilization Information Display               |

|       | Queue Control Block Display                   |

| 8-20. | Path Information Display                      |

| 8-21. | Device Extension for Path Information Display |

| 8-22. | Timer Information Display                     |

|       | Virtual Machine Display                       |

| 8-24. | Segment Information Display                   |

| 8-25. | Virtual Page Information Display              |

| 8-26. | Find Display (Argument Found)                 |

|       | Display from the Ior Command                  |

| 8-28. | Example of a System Module Map                |

| 8-29. | Format of a Screen Display                    |

| 8-30. | SRegs Display                                 |

| 8-31. | Translation Lookaside Buffer Display          |

| 8-32. | Trace Entry Display Format                    |

| 8-33. | User-defined Trace Entry Display              |

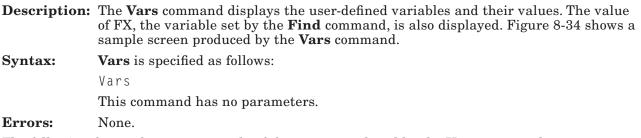

| 8-34. | Vars Display                                  |

| 8-35. | Xlate Display                                 |

| B-1.  | TOC Object Module StructureB-2                |

| B-2.  | TOC Object Module HeaderB-3                   |

| B-3.  | Format of an ESD EntryB-6                     |

| B-4.  | Format of an RLD EntryB-7                     |

| B-5.  | Contents of a Stack Frame                     |

**Chapter 1. Virtual Resource Manager Concepts**

#### CONTENTS

| About This Chapter                       |

|------------------------------------------|

| Understanding the VRM                    |

| Understanding the VMI                    |

| Virtual Machine Architecture             |

| Real and Virtual Machine Concepts1-8     |

| System Integrity and the Virtual Machine |

| Processor and Virtual Machine States1-9  |

| Virtual Memory Management 1-11           |

| Input/Output Subsystem                   |

| Code Definition                          |

| Device Definition                        |

| Device Attach/Detach                     |

| Input/Output Procedures                  |

| Device Query                             |

| Virtual Machine Communications 1-17      |

#### **About This Chapter**

This chapter provides a general description of the Virtual Resource Manager (VRM), its primary components and characteristics, and its relationship to other parts of the system. This chapter also introduces the Virtual Machine Interface, which is the VRM's well-defined, uniform interface to operating systems.

## Understanding the VRM

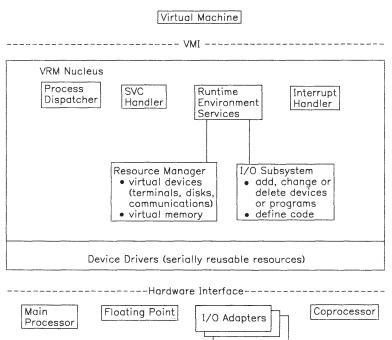

The **Virtual Resource Manager** (VRM) is a collection of processes, device drivers and runtime routines that extend and control hardware functions for an operating system. The VRM shields the operating system from hardware changes and allows more than one operating system (and their applications) to execute. To an operating system, the VRM is perceived as hardware.

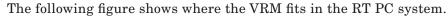

Figure 1-1. RT PC System Structure

The components of the VRM are shown in more detail in Figure 3-1 on page 3-4. The layout of the hardware components is shown in more detail in Figure 3-4 on page 3-8.

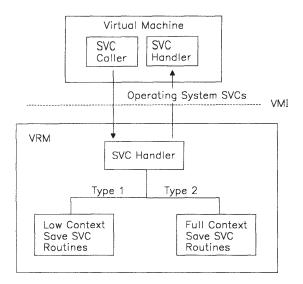

Ordinarily, an operating system device driver sends commands directly to a device, and the device returns real interrupts to the operating system in response to these commands. In the RT PC system, however, the VRM receives the operating system commands, called supervisor calls (SVC), and routes them to the appropriate device. On return, the VRM takes the real hardware interrupts and issues virtual interrupts (if necessary) to the operating system. The relationship of real-to-virtual interrupts is seldom one-for-one. However, the command and interrupt structures of the VRM simulate the command and interrupt structures used by an operating system.

The primary components of the VRM are processes and device drivers. The function of VRM processes and device drivers is analogous to the function of operating system processes and device drivers.

**Processes** receive a portion of the processor's time for program execution and are typically used to control virtual resources. Process types include device manager and protocol processes. **Device managers** control virtualized devices, such as virtual terminals. Protocol processes (also known as protocol procedures) handle specific types of functions for virtual devices. All virtual machines are represented as processes in the VRM. Processes allow asynchronous execution of multiple operations. A dispatcher prioritizes and manages the execution of processes.

**Device drivers** are a collection of subroutines that control the interface between the I/O device adapters and the processor. The most significant difference between VRM and operating system components is in the level of device drivers. The device driver implementation used by the AIX Operating System places the burden of function on the VRM device management facilities (drivers, managers, and protocols). AIX Operating System device drivers are high-level routers of commands that provide limited flexibility. The AIX Operating System has one device driver for the printer, one for the fixed disk, one for diskette, one for a display, one for streaming tape, and so on.

The VRM provides a lower level layer of hardware management. This layer includes the device drivers, device managers (if necessary) and protocol processes that allow for increased flexibility.

It is VRM hardware management, for example, that provides *virtual devices*. A virtual device is a functionally complete simulation of a physical device. For example, the VRM supports up to 32 virtual terminals that work off a single instance of terminal hardware. Only one virtual terminal is active at a time, however.

While the VRM interface to hardware is as dynamic as the hardware that can be configured on the RT PC, the VRM interface to operating systems (also called *virtual machines*) is a well-defined, uniform interface. This *Virtual Machine Interface* (VMI) not only shields the operating system from hardware changes, but it allows concurrent virtual machines to run on the system.

## **Understanding the VMI**

The VMI is a software interface between operating systems and the VRM. The VMI presents a fixed interface to operating systems. This interface consists of supervisor call instructions (see "Supervisor Call Instructions" on page 4-7 for definitions of all the SVCs) and virtual interrupts. Changes in hardware configurations or VRM programs, therefore, do not necessarily require an operating system change. The VMI also supports the existence of several virtual machines from a single real machine.

#### **Virtual Machine Architecture**

A virtual machine is, by definition, a simulation of a physical machine and its related devices. Therefore, the operations and components of a virtual machine closely parallel the operations and components of a physical machine.

A virtual machine typically runs on the normal execution level (level 7) until it completes its work, is interrupted, or is preempted.

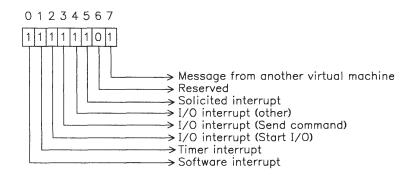

*Interrupts* are grouped and prioritized by levels determined by the source or cause of the interrupt. An interrupt handler can be assigned to each level or sublevel and executes when an interrupt on the corresponding level or sublevel is received.

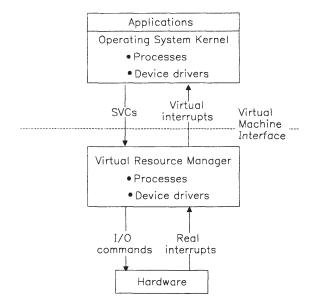

Now that a processing model is defined, the similarities and differences between physical and virtual machine components can be described. Figure 1-2 on page 1-7 shows some of the similarities and differences between virtual and physical machines. When a process executes, data manipulation and computation are done in the general purpose registers of the processor. System control registers (SCRs) keep track of such facilities as the processor, timer, and interrupts.

For example, the instruction address register (IAR) contains the address of the next instruction to be executed. The interrupt control status register (ICS) contains data that indicates pending and masked interrupts and machine state. The condition status register (CS) contains information about the results of certain executed instructions.

The virtual machine counterparts to the system control registers are the virtual machine control registers (VMCR). Each virtual machine maintains a set of VMCRs to save and restore its state and pertinent data as it and other virtual machines are dispatched.

For more details on SCRs, see *IBM RT PC Hardware Technical Reference*. VMCRs are discussed in "Virtual Machine Control Registers" on page 2-4 of this book.

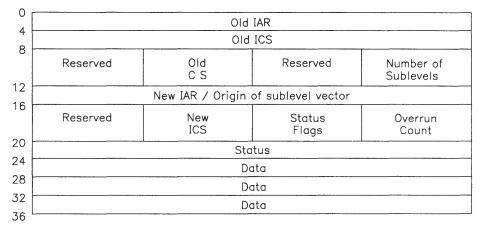

When an interrupt occurs, a set of interrupt handlers determine the cause of the interrupt and perform interrupt-specific processing. Interrupt handling involves saving the status of the machine at the time of the interrupt and determining the address of that interrupt level's interrupt handling routine. This is accomplished with the use of program status words in the physical machine and program status blocks in the virtual machine. For both physical and virtual machines, then, the interrupt level points to a program status word or block, which in turn directs the machine to the address of the appropriate interrupt handling routine. The sequence of events is much the same for physical and virtual machines.

For more information on program status words, see *IBM RT PC Hardware Technical Reference*. Program status blocks are defined in "Virtual Machine Program Status Blocks" on page 2-15 of this book.

As shown in Figure 1-2 on page 1-7, most virtual machines include an operating system and one or more applications. Multiple virtual machines may have different operating systems or multiple copies of one operating system.

#### **1-6** VRM Programming

Figure 1-2. RT PC Architecture Model

When a virtual machine is successfully IPLed, the initial machine state is defined as follows:

- The virtual machine is established as VRM process and is assigned a virtual machine identifier (VMID).

- The virtual machine is initialized in operating system state on the base execution level (level 7).

- Page 0 of the IPL segment (segment 0) is pinned.

- The virtual machine's segment 0 is created and loaded so no problem state tasks have access to it.

- The time of IPL is set and the timer is initially disabled.

- All level 0-6 and machine communications interrupts are masked (VICS bit 31 = 1).

For more information on the virtual machine state immediately after IPL, see "IPL Virtual Machine SVC" on page 4-78.

#### **Real and Virtual Machine Concepts**

The real machine is the actual hardware components that are connected to make up a system. A typical system usually includes a processor, keyboard, display device, diskette drive, and fixed disk. Other hardware components, such as a plotter, printer, tape drive, or communications device may be added to extend system function. All these devices make up the real machine.

A virtual machine is a functional simulation of a computer and its related devices. Because this functionally equivalent machine is simulated to you, and does not really exist, it is called a virtual machine.

Although virtual machines are logically independent of the physical machine and (in the case of multiple virtual machines) of each other, physical resources must be shared by the users. Physical resources which may be designated as shared among virtual machines include segments of storage, input/output devices such as disks, diskettes, displays, and so on.

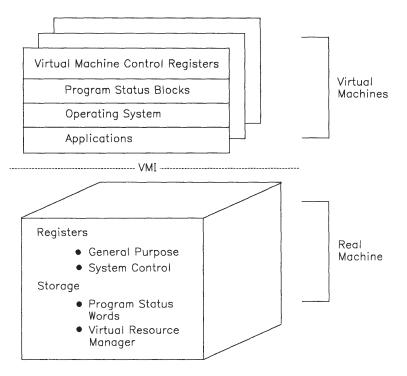

Figure 1-3 shows how the VMI presents multiple virtual machines to the VRM and system hardware.

Figure 1-3. The VMI and Multiple Virtual Machines

The principal advantages of the VMI are:

- The VMI allows concurrent execution of multiple operating systems.

- A virtual machine as defined by the VMI has a high-level but physical, machinelike interface. For this reason, the VMI provides more function than the individual hardware components.

- The VMI insulates operating systems from changes in the hardware configuration. To an operating system, the VMI is perceived as hardware. Changes below the VMI level do not necessarily require any change in the operating system.

- The removal of physical constraints gives you the impression of multiple (in the case of virtual terminals) or expanded (in the case of virtual memory) resources.

#### System Integrity and the Virtual Machine

The VMI isolates virtual machines from each other and from the VRM. However, you can install code into the VRM. If the code is added incorrectly, you can compromise system integrity. Certain limitations are imposed on virtual machine functions. Those limitations include:

- All virtual machines execute in the processor's unprivileged state. Virtual machines have no access to privileged instructions.

- Hardware devices (with the exception of floating-point hardware) are typically accessible only in privileged state. Virtual machines can access bus I/O devices only by setting a bit in a virtual register (see "Virtual Interrupt Control Status (VICS) Register" on page 2-8).

The following section provides more details on privileged and unprivileged instructions, as well as hardware and virtual machine states.

## **Processor and Virtual Machine States**

At the hardware level, the processor can be in one of two execution states, privileged or unprivileged. The execution state determines which instructions the processor allows. In the unprivileged state, the processor executes only unprivileged instructions. Application programs are typically made up of these unprivileged instructions. Privileged instructions execute only when the processor is in the privileged state. Privileged instructions are restricted-use instructions which help control the operating environment of the system. *IBM RT PC Hardware Technical Reference* lists and describes the entire RT PC instruction set. As stated, the processor operates on two execution levels, privileged and unprivileged. The virtual machine also executes on two levels. The execution states of the virtual machine are:

- Problem state The state that most applications run in.

- Operating system (OS) state The state that operating systems run in.

A bit mask in a "virtual register" keeps track of the virtual machine state. A virtual register is a dedicated word of virtual memory that describes the characteristics of the virtual machine. The virtual interrupt control status register (VICS) describes (among other things) the state of the virtual machine. Bit 29 of the VICS determines the virtual machine state. If bit 29 is 1, the virtual machine is in problem state. If bit 29 is 0, the virtual machine is in operating system state. For more information on the VICS, refer to "Virtual Interrupt Control Status (VICS) Register" on page 2-8.

Both problem and operating system state of the virtual machine run in the processor's unprivileged state. When the VRM is running, the processor is in privileged state.

Two instructions, the **supervisor call instruction** (SVC) and the **load program status** instruction (lps) can change the virtual machine's execution state. The SVC instruction can change the execution state from problem to operating system. Each SVC has a function code associated with it. The VRM recognizes the SVC and determines from the function code what actions to take.

SVCs with function code < 32,768 (0x7FFF and below) are operating system (OS) SVCs. The VRM sends OS SVCs to the operating system for execution of the specified function. SVCs with function code > 32,767 (0x8000 and above) are VRM SVCs directed to the VRM. Not all 32,768 function codes possible for execution by the VRM are supported. Only a few dozen codes represent defined SVC functions. However, all 32K of function codes are reserved for VRM SVC use. Figure 1-4 summarizes processor and virtual machine states and describes VRM and OS handling of SVCs.

| Virtual Machine States        |                                                        |                                                    |              |  |  |  |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------|----------------------------------------------------|--------------|--|--|--|--|--|--|--|--|

|                               | VRM                                                    |                                                    |              |  |  |  |  |  |  |  |  |

| VRM SVCs<br>(Code<br>>32,767) | VRM sends an<br>exception to the<br>operating system * | VRM executes                                       | Error in VRM |  |  |  |  |  |  |  |  |

| OS SVCs<br>(Code<br><32,768)  | VRM relays to<br>operating system<br>for execution     | VRM relays to<br>operating system<br>for execution | Error in VRM |  |  |  |  |  |  |  |  |

| Hardware<br>State             | Unpri                                                  | Privileged                                         |              |  |  |  |  |  |  |  |  |

\* Except for Return SVC and Machine Identification SVC

#### Figure 1-4. Processor and Virtual Machine States

The other instruction that can change the execution state of the virtual machine is the **lps** instruction.

The **lps** instruction is a privileged hardware instruction. Ordinarily, a program check (privileged instruction exception) is generated when an **lps** is issued from problem state. However, when a virtual machine is in operating system state and an **lps** instruction is detected, the VRM emulates the **lps** for the virtual machine. Therefore, the virtual machine must be in operating system state when you issue an **lps** instruction.

This "virtual" **lps** instruction can change the level of interrupt processing, as well as the execution state of the virtual machine.

"Supervisor Call Instructions" on page 4-7 describes the format and variations of the SVCs handled by the VRM. See "Load Program Status Instruction" on page 4-6 for more information, including the format, of the **lps** instruction.

#### Virtual Memory Management

This section describes the mechanisms and strategy used by the system to provide and direct memory access in the virtual machine environment. The addressing mechanism in the VRM has the following goals:

• To provide virtual memory to the virtual machines, relieving the operating systems in those machines of handling page faults and related mechanics. (If the virtual machine so requests, it can be notified by virtual interrupts when a page fault requiring I/O occurs and when the page fault is cleared. See "Set Interrupt SVC" on page 4-18.)

- To shield the virtual machine operating system from changes in the hardware supporting paging.

- To efficiently use the addressing hardware.

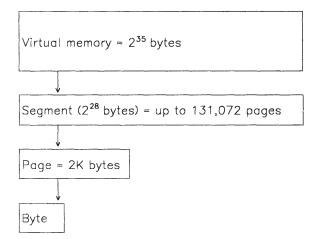

The RT PC system supports an extremely large virtual memory. Total virtual memory addressability is  $2^{35}$  bytes. Each virtual machine can address up to  $2^{32}$  bytes (16 segments times  $2^{28}$  bytes per segment) of virtual memory at a time.

The VRM supports the creation of up to 1024 segments. These resources are shared by the VRM and all virtual machines.

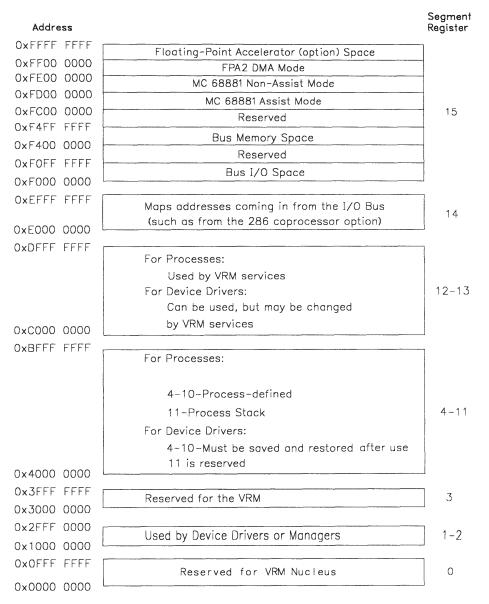

In addition, the VRM reserves two segment registers (14 and 15) for its own use.

This extensive virtual memory must be divided into smaller units for manageability. The three memory units (from largest to smallest) are:

- 1. Segments

- 2. Pages

- 3. Bytes.

The relationship between the memory units is shown in Figure 1-5.

#### Figure 1-5. Virtual Memory Units

A segment is designed to contain up to 131,072 pages, and a page consists of 2K bytes. Sixteen segment registers allow you to access the various segments. Virtual machines may have many segments, but can simultaneously access only 16 segments at a time. Therefore, 2<sup>32</sup> is the maximum number of bytes accessible with any given segment register configuration. By changing the contents of the segment registers, all 2<sup>35</sup> bytes can be accessed. The VRM further restricts this access, as discussed in "Access to Segments" on page 2-26. A segment is created by the "Create Segment SVC" on page 4-27. The size and protection characteristics are specified by the caller, and a 12-bit segment identifier is returned.

Protection can be specified on the page level. The segment exists until:

- An SVC instruction explicitly destroys the segment.

- The work station is powered off.

- The virtual machine that created the segment is terminated.

For segments shared by virtual machines, the segment exists until the virtual machine that created the segment with **Create Segment SVC** is terminated.

The ID returned when a segment is created not only uniquely identifies the segment, but also helps determine the segment's virtual address.

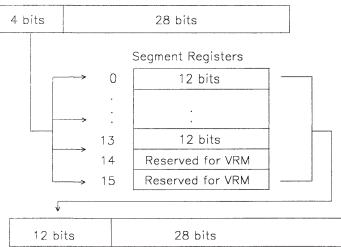

Machine instructions generate 32-bit effective addresses, with the four high-order bits specifying a segment register and the 28 low-order bits providing a displacement within the segment. The system provides 16 segment registers, but two of the 16 are always dedicated to input/output operations and cannot be explicitly changed. The VRM can also access registers 0-13, but saves and restores the register contents after use.

The four high-order bits of the effective address specify the segment register, and the segment register contains the 12-bit segment ID. The 12-bit segment ID plus the 28 low-order bits of the effective address yield the segment's 40-bit virtual address. Figure 1-6 on page 1-14 shows how the effective address and segment registers provide the virtual address.

Effective Address

Virtual Address

**Figure 1-6.** Virtual Memory Addressing. The four high-order bits of the effective address specify one of 16 (0-15) segment registers. The segment ID plus the 28-bit displacement of the effective address yield the segment's 40-bit virtual address.

All VMI references to the segment must use the segment ID, either directly or by specifying the segment register containing the segment ID.

#### **Input/Output Subsystem**

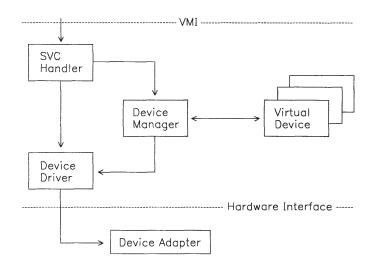

The input/output subsystem (IOS) supports a high-level functional interface for input/ output operations that is different from the processor's I/O read and write instructions. The subsystem provides the mechanisms for I/O device management, manipulation, and data transfer. Each I/O operation is initiated from the operating system state and consists of queueing a work request (a command or a set of commands) to an IOS component.

The IOS is intentionally defined as a queue-driven subsystem that allows work requests to be enqueued to IOS components. The IOS definition makes no statement as to where the actual queue manipulation takes place. In some implementations of the VRM, the manipulation may occur under program control. On other VRM implementations, the same function may occur in an advanced I/O channel. The actual mechanism used by the I/O subsystem is transparent to the subsystem user with the exception of performance characteristics.

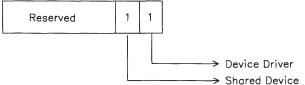

The IOS is defined so that most device types may be installed into the system and a set of IOS components not previously part of the VRM may be installed into the VRM to communicate with the device. These IOS components become an extension of the VRM, may run in privileged mode, and may have full access to the VRM facilities. The VRM is dependent on the virtual machine for controlling installation of these IOS components since the potential for compromising the integrity of the system exists.

The interface to the IOS is through a fixed set of IOS SVC handlers that manage devices and control interaction with devices. The virtual machine specifies an *input/output device number* (IODN) with each SVC. The IODN uniquely identifies the IOS component that is to service the request. The IOS services execute synchronously to the user's virtual machine, although they may enqueue a command for asynchronous processing. For asynchronous requests, the IOS component signals completion of the request by issuing a virtual interrupt.

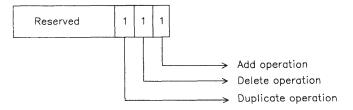

#### **Code Definition**

The "Define Code SVC" on page 4-49 adds IOS components to the VRM. The **Define Code SVC** allows you to add VRM code without having to rebuild the entire VRM. Each component is given a 16-bit *input/output code number* (IOCN) when it is defined.

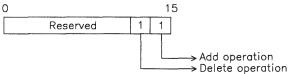

#### **Device Definition**

The virtual machine must use the Define Code SVC to install the device code and then use the **Define Device SVC** to start each device that is not part of the standard VRM program product. This process must be repeated at least at every IPL and may occur as often as required by the virtual machine. Devices are identified by IODNs specified when the devices are initially defined. VMI references are always based on this 16-bit IODN. Once a device is defined to the VRM by the **Define Device SVC**, the IODN and its associated IOCN become an extension of the VRM. From the perspective of the VMI, there is no difference between a nucleus device and a third-party installed device.

Certain devices can be addressed directly by issuing problem state instructions and bypassing the IOS. IBM warns you that this technique should be used only with great caution. If the device that is being addressed is capable of generating processor interrupts, then these devices must be made known to the IOS. Processor interrupts are generated in privileged mode and only the VRM can field and directly handle hardware interrupts.

**Warning:** Use extreme care when dealing with VRM-generated interrupts. If the VRM receives hardware interrupts that it cannot reset, you may jeopardize system integrity and generate an error fatal to the entire work station.

#### **Device Attach/Detach**

A virtual machine uses the **Attach Device SVC** to gain access to a device and establish protocols with the VRM with respect to that device. In particular, the virtual machine indicates the interrupt level and sublevel to be used by the VRM when it needs to interrupt the virtual machine. The **Detach Device SVC** is used to terminate the linkage between the virtual machine and the device. Unless a virtual machine is attached to a device, the virtual machine can neither initiate I/O operations nor receive interrupts from that device.

Under certain circumstances, a virtual machine may issue instructions directly to a hardware device; however, that virtual machine never receives any interrupts back from the device unless the virtual machine has properly attached the device.

#### **Input/Output Procedures**

After a virtual machine attaches to a device, true I/O commands (for positioning, device control or transfer of data) are allowed. An I/O command consists of initiation, execution, and notification phases. A virtual machine initiates an I/O command with the **Start I/O SVC** or **Send Command SVC** The VRM executes the I/O command when necessary. Optionally, the virtual machine is notified upon the completion of the I/O command by a virtual interrupt from the VRM.

The following I/O procedures are supported:

• I/O Initiation

The virtual machine specifies the device and controls the execution and flow of the I/O operation in two ways, depending on the supervisor call. For the **Start I/O SVC**, the virtual machine provides the pertinent information in a command control block (CCB); for the **Send Command SVC**, parameters are passed in general purpose registers.

• I/O Execution

When an I/O command becomes the next command for the device, the VRM begins the execution phase. During this phase, the VRM performs the function requested by the command or issues the appropriate device-level commands to cause control or transfer. Execution of a command element cannot be cancelled once it has begun.

• I/O Notification

When all command elements for an I/O command have been executed, the VRM then interrogates the interrupt options associated with that I/O command. If an interrupt was requested, then an interrupt is queued for presentation to the virtual machine.

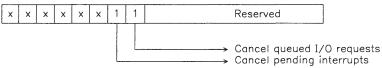

• I/O Cancellation

The **Cancel I/O SVC** purges queued I/O commands and command elements. Facilities include cancelling commands queued by the virtual machine to a device and cancelling

interrupts queued to the virtual machine from a device. Commands in progress are not cancelled.

#### **Device Query**

Information about a device or I/O commands associated with a device may be obtained from the **Query Device SVC**. If the **Query Device SVC** specifies a device with an IODN of 0, the query is interpreted as asking for all defined IODNs.

## **Virtual Machine Communications**

Virtual machines can communicate with messages. Messages are not explicitly structured, and are divided into two types. Immediate messages are short enough (at most 96 bits) to be transmitted in the general purpose registers reserved for SVC parameters. Address messages consist of 40-bit virtual addresses, a length attribute and a type attribute. An address message typically points to part of a segment, but may effectively point to an entire segment. In either case, the recipient understands the message format.

Message sending is asynchronous in that the machine issuing a send command does not wait for the receiver to receive a message. Two priorities of messages are provided, normal and emergency.

A message sent to a virtual machine causes an interrupt to be presented to that machine (when the corresponding level is not masked). The virtual machine specifies the levels and sublevels to be used for normal and emergency messages.

# Chapter 2. Virtual Machine Interface Characteristics

## CONTENTS

| About This Chapter                       |

|------------------------------------------|

| VMI Components and Characteristics       |

| Virtual Machine Control Registers        |

| Virtual Machine Interrupts               |

| Interrupt and Execution Priority Levels  |

| Virtual Machine Program Status Blocks    |

| PSB Status Word                          |

| The Interrupt Processing Cycle           |

| Access to Segments                       |

| Segment Register 14 Usage                |

| Segment Register 15 Usage                |

| Protection of Segments                   |

| Mapped Page Ranges                       |

| Segment Sharing Between Virtual Machines |

# **About This Chapter**

This chapter provides a general description of the Virtual Machine Interface (VMI), its primary components and characteristics, and its relationship to other parts of the system.

# VMI Components and Characteristics

The VMI consists of:

- The problem state instruction set. Hardware executes these instructions directly. For a detailed discussion of this instruction set, refer to *IBM RT PC Hardware Technical Reference*.

- A simulated privileged machine structure and a set of privileged machine functions. Operating systems running in a virtual machine use these functions to control the state of the virtual machine. The privileged machine structure includes status registers, timers, interrupt handlers, input/output functions, and simulated privileged operations such as the **load program status** instruction.

- A paged virtual memory system. Paging involves copying virtual memory into or out of real memory. A page consists of 2,048 bytes of memory.

- Device-independent interfaces to the display and other input devices.

- Functions for multiple virtual machine management. These functions, which provide for fully independent virtual machines, include initiation, termination, communication between machines, and resource sharing.

## Virtual Machine Control Registers

The processor can access a set of 32-bit hardware registers for general purpose operations and system control registers for controlling the processor state. A similar set of "registers" is provided to each virtual machine. These "virtual" registers are actually reserved virtual memory locations. Because each virtual machine has a distinct virtual memory space starting at location 0, these locations are valid for all virtual machines on the system.

Reserved words should not be used by virtual machines. These words will support added functions.

Refer to Figure 2-1 on page 2-5 for a summary of dedicated virtual memory locations and the values associated with each location.

| Memory location |     | Bytes | Value                                 |

|-----------------|-----|-------|---------------------------------------|

| Decimal         | Hex | Hex   |                                       |

| 0               | 0   | B8    | Reserved                              |

| 184             | B8  | 4     | Number of free paging disk slots      |

| 188             | BC  | 4     | Number of page replacement cycles     |

| 192             | C0  | 4     | Number of page faults with preemption |

| 196             | 4   | 4     | Number of non-paging disk I/Os        |

| 200             | C8  | 2     | Reserved                              |

| 202             | CA  | 2     | PCB segment ID                        |

| 204             | CC  | 1     | Floating-point hardware (if any)      |

| 205             | CD  | 1     | Processor type                        |

| 206             | CE  | 2     | Trace buffer synch flag               |

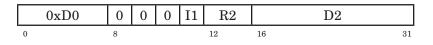

| 208             | D0  | 2     | VRM sequence number                   |

| 210             | D2  | 2     | Virtual machine sequence number       |

| 212             | D4  | 2     | Interrupt request buffer              |

| 214             | D6  | 1     | Process priority                      |

| 215             | D7  | 1     | Floating-point register set           |

| 216             | D8  | 4     | Bus I/O base address                  |

| 220             | DC  | 4     | Bus memory base address               |

| 224             | E0  | 4     | Virtual interrupt control status      |

| 228             | E4  | 2     | Execution level                       |

| 230             | E6  | 2     | Virtual machine ID (right justified)  |

| 232             | E8  | 4     | Time of day, extended                 |

| 236             | EC  | 4     | Virtual timer status                  |

| 240             | F0  | 4     | Real time of day                      |

| 244             | F4  | 4     | Real time of IPL                      |

| 248             | F8  | 4     | Virtual timer source                  |

Figure 2-1 (Part 1 of 2).

Memory Locations Used as Virtual Registers

| Memory location |     | Bytes | Value                                                              |

|-----------------|-----|-------|--------------------------------------------------------------------|

| 252             | FC  | 4     | Virtual time since IPL                                             |

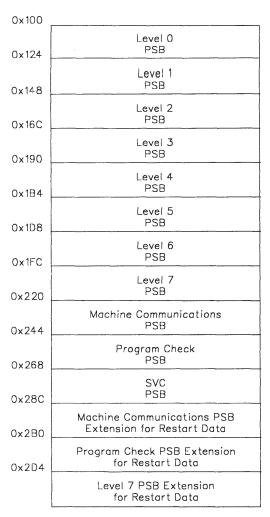

| 256             | 100 | 18C   | PSBs (see Figure 2-3 on page 2-16)                                 |

| 652             | 28C | 24    | Task exception restart data (machine communications PSB extension) |

| 688             | 2B0 | 24    | Task exception restart data (program check PSB extension)          |

| 724             | 2D4 | 24    | Task exception restart data (level 7<br>PSB extension)             |

Figure 2-1 (Part 2 of 2). Memory Locations Used as Virtual Registers

The VRM reserves the first 184 (0xB8) bytes of virtual memory, as well as two bytes at location 200 (0xC8). The rest of the memory locations are defined in the following section.

## **Paging Data**

Locations 0xB8 through 0xC8 provide data on paging. The number of free paging disk slots should be used by a virtual machine to control its creation of segments. The virtual machine should not create new segments when this number is small. Using all of the paging disk slots will abend the system. The number of page replacement cycles, page faults with preemption, and non-paging disk I/Os should be used by a scheduler in a virtual machine to prevent *thrashing*. Thrashing is a condition in which the system is doing so much paging that little useful work can be done.

## **POST Control Block (PCB) Segment Identifier**

The POST (power-on self test) control block is a one-page segment that keeps track of the devices and memory of the real machine. The segment ID is available to the virtual machine at location 0xCA. POST control block addresses start at 0x000 and end at 0x7FF.

Note that the PCB cannot be altered in any way. Therefore, the only virtual memory SVCs that can be performed on this segment are **Load Segment Register SVC** and **Query Page Protect SVC**.

For more information on the format of the POST control block and the fields in a control block entry, see *VRM Device Support*.

#### **Floating-Point Hardware**

This byte indicates if any floating-point hardware is configured on the machine, and, if so, the configuration type. Possible values for this field include:

0 = no floating-point hardware configured

1 = Floating-Point Accelerator (FPA1) present

2 = APC floating-point coprocessor is present

4 = Advanced Floating-Point Accelerator (FPA2) present without APC

C = FPA2 present with APC (DMA operations supported).

## |Processor Type and Mode

Bit 0 of this byte indicates the type of processor in use on the machine. When bit 0 = 0, the Processor and Memory Management Card is configured. When bit 0 = 1, the Advanced Processor Card is configured. Bit 1 indicates if the processor supports loop mode. The virtual machine may optimize loops to run efficiently when in loop mode. When bit 1 = 0, the processor does not support loop mode; when bit 1 = 1, the processor may optimize loops. See *IBM RT PC Hardware Technical Reference* for details on loop mode.

## **Trace Buffer Synch Flag**

This halfword is used as a pacing mechanism because the VRM can send only two buffers of trace data to the operating system at a time. The first byte contains a value for the number of buffers the VRM has sent to the operating system. The second byte contains a value for the number of buffers processed by the operating system. If the operating system count is two more than the VRM count, the VRM cannot send another buffer until the operating system processes one.

### **VRM Sequence Number**

The basic unit of timer granularity is approximately 16.6 milliseconds (ms). Because the VRM can generate many trace entries in this period of time, the sequence number provides a greater granularity so that trace entries can be logged more precisely.

### Virtual Machine Sequence Number

The basic unit of timer granularity is approximately 16.6 ms. Because the VRM can generate many trace entries in this period of time, the sequence number provides a greater granularity so that trace entries can be logged more precisely.

#### **Interrupt Request Buffer**

The halfword at location 0xD4 contains the interrupt levels queued to the virtual machine. Bits 0-9 map one to one with the corresponding bits of the virtual ICS (see "Virtual Interrupt Control Status (VICS) Register"). Bits 10-15 are zero. The interrupt request buffer keeps track of pending interrupts for virtual machines.

#### **Process Priority**

The value found at location 0xD6 reflects the priority of the process executing in the virtual machine. The VRM uses this value to prioritize input/output and paging activities. The process priority can be used by the virtual machine's operating system to influence VRM scheduling algorithms.

The range of values valid for process priority is 0-15. The highest priority is 0. The default value, 15, is the lowest priority.

## **Floating-Point Register Set**

This byte has meaning only when the floating-point accelerator hardware is part of the system. The value at 0xD7 indicates which floating-point register set the virtual machine is using.

#### **Bus I/O Base Address**

The bus I/O address is a fullword of storage that contains the address of the beginning of bus I/O space. Virtual machines can perform I/O operations directly to bus-attached I/O devices when using bus I/O space.

### **Bus Memory Base Address**

The bus memory base address is a fullword of storage that contains the address of the beginning of bus-attached memory. Virtual machines can load and store directly to bus-attached memory.

## Virtual Interrupt Control Status (VICS) Register

The virtual interrupt control status register (VICS) describes the state of the virtual machine. The VICS is modified by SVC instructions, by virtual machine interrupts, by the **load program status** (lps) instruction, and by storing directly into the VICS register memory location.

Whenever you change any of the values in the VICS (with the exception of disabling certain interrupts), you must issue one of the execution control SVCs in order for the VRM to recognize the change. "Execution Control SVCs" on page 4-9 lists and defines these SVCs.

Disabling interrupts can be done with simple **load** and **store** instructions directly to the VICS and does not require issuance of an execution control SVC for the VRM to recognize

the change. To re-enable interrupts, however, an execution control SVC (such as the **No Operation SVC**) is required to effect the change.

The VICS is contained in location 0xE0.

Bits 7, 10, 13-15, and 24-26 of the VICS are reserved.

Bits 11 and 12 should not be changed by **load** and **store** instructions because the VRM will ignore these changes.

The rest of this virtual register is defined as follows:

- Bits 0-6: Level in progress. A value of one in any of these bits indicates the preempted execution levels.

- Bit 8: Program check in progress.

- Bit 9: Machine communications in progress. Bits 0-9 indicate the execution levels that are in progress by setting the bit corresponding to the preempted levels to one. The bit for the current level is set to zero.

- Bit 11: Termination in progress.

- Bit 12: Virtual machine in wait state (Virtual Machine Wait SVC issued).

When any of bits 16 through 23 equal one, interrupts are inhibited on the indicated level. If interrupts occur for an inhibited level, they are queued.

- Bit 16: Level 0

- Bit 17: Level 1

- Bit 18: Level 2

- Bit 19: Level 3

- Bit 20: Level 4

- Bit 21: Level 5

- Bit 22: Level 6

- Bit 23: Machine communications level

- Bit 27: Bus I/O access control. A value of one in this bit allows the virtual machine to access the bus-attached I/O devices. A value of zero prohibits access. Any attempt to access bus-attached I/O devices when this bit is zero gives the virtual machine a program check interrupt with data address exception on.

- Bit 28: Bus memory access control. A value of one in this bit allows the virtual machine to access bus-attached memory. A value of zero prohibits access. Any attempt to access bus-attached memory when this bit is zero gives the virtual machine a program check interrupt with data address exception on.

- Bit 29: Problem state. A value of one in this bit puts the virtual machine in problem state; a value of zero puts it in operating state. The VRM uses this bit to determine the legality of SVC calls.

- Bit 30: Inhibit paging interrupts. A value of one in this bit puts the virtual machine in wait state until a page is moved to real memory. A value of zero causes a machine communications interrupt with the page fault indicator on when a page fault occurs.

A value of one in this bit causes page faults to be processed synchronously with no 'page fault occurred' interrupt. The setting of this bit does pot disable 'page fault cleared' interrupts. A 'page fault cleared' interrupt is generated when the I/O completes for a page fault that resulted in a 'page fault occurred' interrupt. 'Page fault cleared' interrupts can be disabled by setting bits 23 or 31 of the VICS.

This bit is effectively on whenever the virtual machine executes on the program check or machine communications level. These levels cannot be interrupted by a machine communications interrupt.

Bit 31: Inhibit all levels (0-6). A value of zero in this bit causes VRM to use bits 16-23 of the VICS as the interrupt mask. A value of one inhibits all interrupts on levels 0-6 and the machine check level. If interrupts occur on any of these levels, they are queued. A one in this bit supersedes the settings of the interrupt mask in bits 16-23. SVC instruction interrupts and program checks cannot be explicitly masked.

## **Execution Level**

The current execution level for the virtual machine is contained in the halfword at location 0xE4. The execution level value is updated whenever the execution level is changed. A virtual machine can use the processor's **store half** instruction to explicitly change the execution level. Along with the VICS and program status blocks, the execution level defines the current state of the virtual machine.

### **Virtual Machine Identification**

Virtual machine memory location 0xE6 contains the 15-bit virtual machine ID when the virtual machine first receives control. The value at location 0xE6 reflects the ID of the virtual machine dispatched at IPL and is not updated.

### **Real Time of Day, Extended**

The real time of day can be found at location 0xF0 (see "Real Time of Day"). The extended time of day value found at 0xE8 divides the current second into approximately 60 Hz when the counter is enabled (bit 2 of the Virtual Timer Status register is on). Thus, 16.6 ms is the finest granularity of real-time measurement available.

#### Virtual Timer Status Register

The word of memory at location 0xEC contains information concerning the current interrupt levels and whether the timer is enabled.

This virtual register is changed only as the result of executing the Set Timer SVC instruction (see "Set Timer SVC" on page 4-19). The virtual timer status register is defined in Figure 2-2 on page 2-12.

For more information on interrupts, see "Virtual Machine Interrupts" on page 2-14. Real Time of Day

## **Real Time of IPL**

Location 0xF0 contains the time in seconds from midnight, Jan. 1, 1970. The current second is further divided into 1/60th of a second increments for more precise measurement. This extended value is found at location 0xE8.

The word of storage at location 0xF4 contains a timestamp taken when the virtual machine was loaded.

#### **Virtual Timer Source**

In addition to time of day, the VRM supports a virtual machine timer (VMT). The VMT is a counter that allows the operating system in the virtual machine to perform time-slicing, accounting, and performance measurement functions. The VRM decreases the value of the VMT every 16.6 ms. The timer value is contained in storage location 0xF8.

The virtual timer source register can be loaded (by way of the **Set Timer SVC**) to cause an interrupt at fixed intervals. For example, if the timer is loaded with 3, an interrupt occurs every 3 times 16.6 ms. Each virtual machine may have a different setting for the virtual timer source. Therefore, the setting for a particular virtual machine is valid only when that virtual machine is currently running.

An interrupt is set to the virtual machine when all the following conditions are met:

- The counter decreases from 1 to 0.

- The timer is enabled.

- The interrupt level/sublevel has been specified through the "Set Timer SVC" on page 4-19.

## Virtual Time since IPL

For each elapsed second, the VRM increases the time from IPL for that virtual machine. This value is reflected to the virtual machine in location 0xFC. The fullword at this location is defined as follows:

| Bits  | Meaning                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Enable interrupts. When zero, no interrupts are created. This does not start or stop the virtual machine timer, but enables or disables the setting of virtual machine interrupt request register bits. When the virtual machine is initialized, this bit is zero.                                                                                                                                                  |

| 1     | Interrupt valid. When zero, no interrupts are created. This bit is set to one when a valid interrupt level is specified. When the virtual machine is initialized, this bit is zero.                                                                                                                                                                                                                                 |

| 2     | Enable 60 Hz counter. When this bit equals one, the current second is divided into approximately 60 Hz. (Actual counter value is 16.6 ms, while one hertz equals 16.6666 ms.) Note that when the status of this counter is changed, the change may not take effect for 16.6 ms (if disabling the counter) or one second (if enabling the counter). This extended time-of-day value is then stored at location 0xE8. |

| 3-20  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                            |