## AMD-K6® Processor Code

# Optimization

**Application Note**

Publication # 21924 Rev: D Amendment/0 Issue Date: January 2000

#### © 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, K6, 3DNow!, and combinations thereof, K86, Super7, and AMD-K5 are trademarks, and RISC86 and AMD-K6 are registered trademarks of Advanced Micro Devices, Inc.

MMX is a trademark and Pentium is a registered trademark of the Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## Contents

|   | Revision Historyix                                                   |

|---|----------------------------------------------------------------------|

| 1 | Introduction 1                                                       |

|   | Purpose                                                              |

|   | AMD-K6 <sup>®</sup> Family of Processors                             |

|   | AMD-K6-2 and AMD-K6-III Processors                                   |

| 2 | RISC86 Microarchitecture 5                                           |

|   | Overview                                                             |

|   | Enhanced RISC86 <sup>®</sup> Microarchitecture                       |

| 3 | AMD-K6 <sup>®</sup> -2 and AMD-K6-III Processors Execution Units and |

|   | Dependency Latencies 11                                              |

|   | Execution Unit Terminology 12                                        |

|   | Six-Stage Pipeline                                                   |

|   | Register Execution Units                                             |

|   | Load Unit                                                            |

|   | Store Unit                                                           |

|   | Branch Condition Unit 19                                             |

|   | Floating-Point Unit 19                                               |

|   | Latencies and Throughput 20                                          |

|   | Resource Constraints 21                                              |

|   | Code Sample Analysis 22                                              |

| 4 | Instruction Dispatch 27                                              |

| 5 | Optimization Coding Guidelines 57                                    |

|   | General x86 Optimization Techniques                                  |

|   | General AMD-K6 Family x86 Coding Optimizations                       |

|   | AMD-K6 Family Integer x86 Coding Optimizations                       |

AMD-K6<sup>®</sup> Processor Code Optimization

| Considerations for Other Processors                                           | 89   |

|-------------------------------------------------------------------------------|------|

| AMD-K6-2 and AMD-K6-III Processors x87 Floating Point<br>Coding Optimizations | . 85 |

| AMD-K6-2 and AMD-K6-III Processors Multimedia Coding Optimizations            | . 67 |

## **List of Figures**

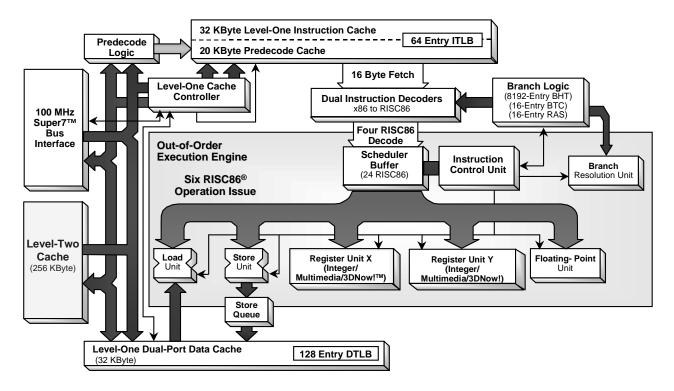

| Figure 1. | AMD-K6 <sup>®</sup> -III Processor Block Diagram 8 |

|-----------|----------------------------------------------------|

| Figure 2. | Processor Pipeline 13                              |

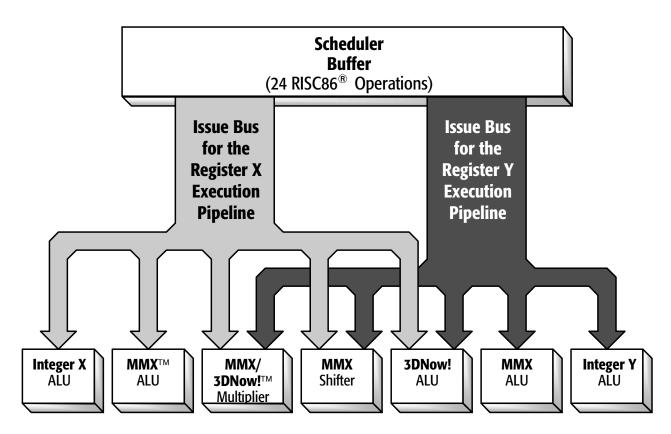

| Figure 3. | Register X and Y Functional Units 14               |

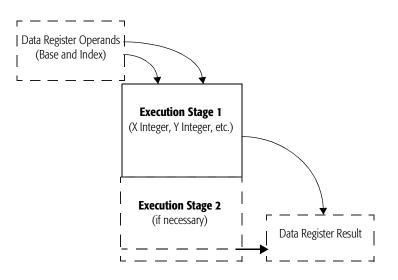

| Figure 4. | Register X and Y Execution Stages 15               |

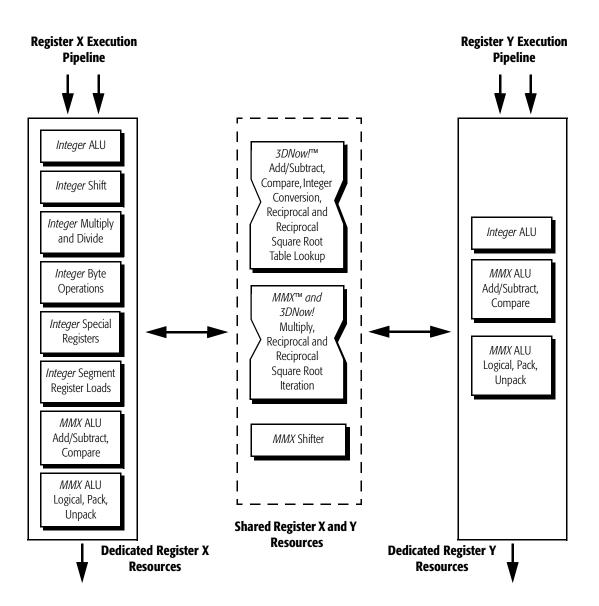

| Figure 5. | Microarchitecture and Execution Resources 16       |

| Figure 6. | Load Execution Unit 17                             |

| Figure 7. | Store Unit Execution Pipeline 19                   |

AMD-K6<sup>®</sup> Processor Code Optimization

21924D/0—January 2000

## **List of Tables**

| Table 1.  | RISC86 <sup>®</sup> Execution Latencies and Throughput 20                                              |

|-----------|--------------------------------------------------------------------------------------------------------|

| Table 2.  | Sample 1 – Integer Register Operations 23                                                              |

| Table 3.  | Sample 2 – Integer Register and Memory Load<br>Operations                                              |

| Table 4.  | Sample 3 – Integer Register and Memory<br>Load/Store Operations                                        |

| Table 5.  | Sample 4 – Integer, MMX <sup>TM</sup> , and Memory<br>Load/Store Operations                            |

| Table 6.  | Integer Instructions                                                                                   |

| Table 7.  | MMX Instructions 47                                                                                    |

| Table 8.  | Floating-Point Instructions 51                                                                         |

| Table 9.  | 3DNow! <sup>™</sup> Instructions 55                                                                    |

| Table 10. | Decode Accumulation and Serialization 59                                                               |

| Table 11. | Specific Optimizations and Guidelines for<br>AMD-K6 <sup>®</sup> and AMD-K5 <sup>™</sup> Processors 89 |

| Table 12. | AMD-K6 Processor Versus Pentium <sup>®</sup><br>Processor-Specific Optimizations and Guidelines 91     |

| Table 13. | AMD-K6 Processor and Pentium Processor with<br>Optimizations for MMX Instructions                      |

| Table 14. | AMD-K6 Processor and Pentium Pro/Pentium II<br>Specific Optimizations93                                |

| Table 15. | AMD-K6 Processor and Pentium Pro with<br>Optimizations for MMX Instructions                            |

AMD-K6<sup>®</sup> Processor Code Optimization

21924D/0—January 2000

## **Revision History**

| Date          | Rev | Description                                                                                                                                                                                 |

|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feb 1998      | Α   | Initial Release                                                                                                                                                                             |

| May 1998      | В   | Added IN and OUT instructions to Table 6, "Integer Instructions," on page 29.                                                                                                               |

| May 1998      | В   | Clarified address modes on page 68 and page 82.                                                                                                                                             |

| August 1999 C |     | Changed title and Introduction to reflect that the information in this document applies to the AMD-K6 <sup>®</sup> family of processors - mainly to the AMD-K6-2 and AMD-K6-III processors. |

| August 1999   | C   | Revised address mode information on page 76.                                                                                                                                                |

| August 1999   | C   | Revised examples in "Division and Square Root" on page 90.                                                                                                                                  |

| Jan 2000      | D   | Changed mem64 to mem32 for PUNPCKLBW, PUNPCKLWD, and PUNPCKLDQ in Table 7 on page 47.                                                                                                       |

AMD-K6<sup>®</sup> Processor Code Optimization

21924D/0-January 2000

## Introduction

## Purpose

The AMD K86<sup>™</sup> family of x86 processors can efficiently execute code written for previous-generation x86 processors. However, to get the highest performance from the unique microarchitecture of the AMD-K6<sup>®</sup> family of processors, certain code optimization techniques should be applied.

This document contains information to assist programmers in creating optimized code for the AMD-K6 family. This document is targeted at compiler/assembler designers and assembly language programmers writing high-performance code sequences. It is assumed that the reader possesses an in-depth knowledge of the x86 architecture.

The information in this application note pertains to the AMD-K6 family of processors – information specific to the AMD-K6-2 processor Model 8 and AMD-K6-III processor Model 9 is noted. For information about the recognition of processor model numbers, see the *AMD Processor Recognition Application Note*, order# 20734.

## AMD-K6<sup>®</sup> Family of Processors

Processors in the AMD-K6 family use a decoupled instruction decode and superscalar execution microarchitecture, including state-of-the-art RISC design techniques, to deliver sixth-generation performance with x86 binary software compatibility. An x86 binary-compatible processor implements the industry-standard x86 instruction set by decoding and executing the x86 instruction set as its native mode of operation. Only this native mode permits delivery of maximum performance when running PC software.

## AMD-K6<sup>®</sup>-2 and AMD-K6<sup>®</sup>-III Processors

The AMD-K6-2 and AMD-K6-III processors (hereafther both are referred to as the processor) bring superscalar RISC performance to desktop systems running industry-standard x86 software. The processor implements advanced design techniques such as:

- Instruction pre-decoding

- Multiple x86 opcode decoding

- Single-cycle internal RISC operations

- Multiple parallel execution units

- Out-of-order execution

- Data-forwarding

- Register renaming

- Dynamic branch prediction

The processor is capable of issuing, executing, and retiring multiple x86 instructions per cycle, resulting in superior scaleable performance.

Although the processor is capable of extracting code parallelism out of off-the-shelf, commercially available x86 software, specific code optimizations for the processor can result in significantly higher delivered performance. This document describes the RISC86<sup>®</sup> microarchitecture in the processor and makes recommendations for optimizing execution of x86 software on the processor. The coding techniques for achieving peak performance on the processor include, but are not limited to, those recommended for the Pentium<sup>®</sup>, Pentium II, and Pentium Pro processors. However, many of these optimizations are not necessary for the processor to achieve maximum performance. For example, due to more flexible pipeline control in the AMD-K6 microarchitecture, the processor is less sensitive to instruction selection and the scheduling of code. This flexibility is one of the distinct advantages of the AMD-K6 processor microarchitecture.

In addition to the ability to execute MMX<sup>TM</sup> instructions, the processor includes the implementation of the 3DNow!<sup>TM</sup> instruction set. 3DNow! technology was created based on suggestions from leading graphics and software vendors. Utilizing a data format and single instruction multiple data (SIMD) operations based on the MMX instruction model, the processor can produce up to four, 32-bit, single-precision floating-point results per clock cycle. 3DNow! technology also includes new integer multimedia instructions, a new instruction to allow the prefetching of data under software control, and a faster enter/exit multimedia-state instruction.

The 3DNow! units provide support for high-performance, floating-point vector operations, which can replace x87 instructions and enhance the performance of 3D graphics and other floating-point-intensive applications. The complete multimedia processing unit in the processor combines existing MMX instructions with the new 3DNow! instructions. The 3DNow! instructions share the use of the MMX registers with the multimedia unit. By mixing 3DNow! instructions with MMX instructions, it now becomes possible to write x86 programs containing both MMX integer and floating-point instructions without a performance penalty that would have been incurred if MMX and x87 floating-point instructions were intermixed. All these improvements have been carefully designed to bring a better multimedia experience to mainstream PC users while maintaining backwards compatibility with all existing x86 software.

AMD-K6<sup>®</sup> Processor Code Optimization

21924D/0—January 2000

## **RISC86<sup>®</sup> Microarchitecture**

## **Overview**

When discussing processor design, it is important to understand the terms architecture, microarchitecture, and design implementation. The term architecture refers to the instruction set and features of a processor that are visible to software programs running on the processor. The architecture determines what software the processor can run. The architecture of the AMD-K6 processor is the industry-standard x86 instruction set.

The term *microarchitecture* refers to the design techniques used in the processor to reach the target cost, performance, and functionality goals. The AMD-K6 processor is based on a sophisticated RISC core known as the Enhanced RISC86 microarchitecture. The Enhanced RISC86 microarchitecture is an advanced decoupled decode/execution design approach that enables industry-leading performance for x86-based software.

The term *design implementation* refers to the actual logic and circuit designs from which the processor is created according to the microarchitecture specifications.

## Enhanced RISC86<sup>®</sup> Microarchitecture

The Enhanced RISC86 microarchitecture defines the characteristics of the AMD-K6 family of processors. The innovative RISC86 microarchitecture approach implements the x86 instruction set by internally translating x86 instructions into RISC86 operations. These RISC86 operations were specially designed to include direct support for the x86 instruction set while observing the RISC performance principles of fixed-length encoding, regularized instruction fields, and a large register set. The Enhanced RISC86 microarchitecture used in the AMD-K6 processor enables higher processor core performance and promotes straightforward extensions in future designs. Instead of directly executing complex x86 instructions, which have lengths of 1 to 15 bytes, the AMD-K6 processor executes the simpler fixed-length RISC86 operations, while maintaining the instruction coding efficiencies found in x86 programs.

The AMD-K6 processor includes parallel instruction decoders, a centralized RISC86 operation scheduler, and several execution resources that support superscalar execution—multiple decode, execution, and retirement—of x86 instructions. These elements are packed into an aggressive and highly efficient six-stage processing pipeline.

Decoding of the x86 instructions into RISC86 operations begins when the on-chip level-one instruction cache is filled. Predecode logic determines the length of an x86 instruction on a byte-by-byte basis. This predecode information is stored along with the x86 instructions in a dedicated, level-one predecode cache to be used later by the decoders. The predecode data is essential to the ability of the short decoders to operate.

The AMD-K6 processor categorizes x86 instructions into three types of decodes—short, long, and vector. The decoders process either two short, one long, or one vector decode at a time. The three types of decodes have the following characteristics:

Short decodes—common x86 instructions less than or equal to 7 bytes in length that produce one or two RISC86 operations. The two short decoders can work in parallel, resulting in a maximum of four RISC86 operations per clock with no additional latency.  Long decodes—more complex and somewhat common x86 instructions less than or equal to 11 bytes in length that produce up to four RISC86 operations.

Vector decodes—complex x86 instructions requiring long sequences of RISC86 operations.

Short and long decodes are processed completely within the decoders. Vector decodes are started by the vector decoder with the generation of an initial set of four RISC86 operations, and then completed by fetching a sequence of additional operations from an on-chip ROM (at a rate of four operations per clock). RISC86 operations, whether produced by decoders or fetched from ROM, are then loaded into a buffer line in the centralized scheduler for dispatch to the execution units.

AMD-K6<sup>®</sup>-2 and AMD-K6<sup>®</sup>-III Processor-Specific Microarchitecture The internal RISC86 instruction set consists of the following seven categories or types of operations (the execution unit that handles each type of operation is displayed in parenthesis):

- Memory load operations (load)

- Load immediate (instruction control unit)

- Memory store operations (store)

- Integer register operations (alu/alux)

- MMX/3DNow! register operations (multimedia execution unit (meu))

- x87 floating-point register operations (float)

- Branch condition evaluations (branch)

The following example shows a series of x86 instructions and the corresponding decoded RISC86 operations.

| <u>x86</u> | <u>Instructions</u> |   | <u>RISC86 Operations</u> |

|------------|---------------------|---|--------------------------|

| MOV        | CX, [SP+4]          | > | Load                     |

| ADD        | AX,BX               | > | Alu (Add)                |

| СМР        | CX,[AX]             | > | Load                     |

|            |                     |   | Alu (Sub)                |

| JΖ         | foo                 | > | Branch                   |

|            |                     |   |                          |

The MOV instruction converts to a RISC86 load operation that requires indirect data to be loaded from memory. The ADD instruction converts to an alu register operation that can be sent to either of the integer units. The CMP instruction converts into two RISC86 operations. The first RISC86 load operation requires indirect data to be loaded from memory. That value is then compared (alu function) with CX.

Once the RISC86 operations are placed in the centralized scheduler buffer, they can be immediately issued to the appropriate execution pipeline. The processor contains ten execution pipelines—store, load, integer X ALU, integer Y ALU, MMX ALU (X), MMX ALU (Y), MMX/3DNow! multiplier, 3DNow! ALU, Floating-Point, and Branch. Figure 1 shows a block diagram of these units within the processor. The Register X and Y Functional Units contain several execution resources, which are described in Chapter 3 on page 11.

Figure 1. AMD-K6<sup>®</sup>-III Processor Block Diagram

The centralized scheduler buffer, in conjunction with the instruction control unit (ICU), buffers and manages up to 24 RISC86 operations at a time (which equals up to 12 x86 instructions). This buffer size is matched to the processor's six-stage RISC86 pipeline and decode rate of four RISC86 operations per clock.

On every clock, the centralized scheduler buffer can accept up to four RISC86 operations from the decoders, issue up to six RISC86 operations to corresponding execution unit pipelines, and retire up to four RISC86 operations. The register execution units are shared between six execution pipelines. A maximum of two of these register operations can be issued at a time.

When managing the 24 RISC86 operations, the ICU uses 69 physical registers contained within the RISC86 microarchitecture. Forty-eight of the physical registers are located in a general register file and are grouped as 24 committed or architectural registers plus 24 rename registers. The 24 architectural registers consist of 16 scratch registers and 8 registers that correspond to the x86 general-purpose registers—EAX, EBX, ECX, EDX, EBP, ESP, ESI, and EDI. There is an analogous set of registers specifically for MMX and 3DNow! operations. There are 9 MMX/3DNow! committed or architectural registers plus 12 MMX/3DNow! rename registers. The 9 architectural registers consist of one scratch register and 8 registers that correspond to the MMX registers (mm0-mm7).

The processor offers sophisticated dynamic branch logic that includes the following elements:

- Branch history/prediction table

- Branch target cache

- Return address stack

These components serve to minimize or eliminate the delays due to the branch instructions (jumps, calls, returns) common in x86 software.

The processor implements a two-level branch prediction scheme based on an 8192-entry branch history table. The branch history table stores prediction information that is used for predicting the direction of conditional branches. The target addresses of conditional and unconditional branches are not predicted, but instead are calculated on-the-fly during instruction decode by special branch target address ALUs. The branch target cache augments performance of taken branches by avoiding a one-cycle cache-fetch penalty. This specialized target cache does this by supplying the first 16 bytes of target instructions to the decoders when a branch is taken.

The return address stack serves to optimize CALL and RETURN instruction pairs by remembering the return address of each CALL within a nested series of subroutines and supplying it as the predicted target address of the corresponding RETURN instruction.

As shown in Figure 1 on page 8, the high-performance, out-of-order execution engine is mated to a split 64-Kbyte writeback level-one cache (Harvard architecture) with 32 Kbytes of instruction cache and 32 Kbytes of data cache. The level-one instruction cache feeds the decoders and, in turn, the decoders feed the scheduler. The ICU controls the issue and retirement of RISC86 operations contained in the centralized scheduler buffer. The level-one data cache satisfies most memory reads and writes by the load and store execution units. The store queue temporarily buffers memory writes from the store unit until they can safely be committed into the cache (that is, when all preceding operations have been found to be free of faults and branch mispredictions). The system bus interface is the industry-standard Super7 and Socket 7 interface.

## AMD-K6<sup>®</sup>-2 and AMD-K6<sup>®</sup>-III Processors Execution Units and Dependency Latencies

The AMD-K6-2 and AMD-K6-III processors contain several specialized execution pipelines—store, load, register X, register Y, floating-point, and branch condition. Each pipeline operates independently and handles a specific subset of the RISC86 instruction set. The register X and register Y pipelines each contain integer, multimedia, and 3DNow! technology execution resources, some of which are shared between the two. This chapter describes the operation of these units, their execution latencies, and how these latencies affect concurrent dependency chains.

*Note:* meu–Multimedia execution units execute MMX and 3DNow! instructions.

A dependency occurs when data needed in one execution unit/resource is being processed in another unit/resource (or a different stage of the same unit/resource). Additional latencies can occur because the dependent execution unit must wait for the data from the supplying unit. Table 1 on page 20 provides a summary of the execution units, the operations performed within these units, the operation latency, and the operation throughput.

## **Execution Unit Terminology**

| Introduction | The execution units operate with two different types of register values—operands and results. Of these there are three types of operands and two types of results.                                                                                                                                                                                                            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands     | <ul> <li>The three types of operands are as follows:</li> <li>Address register operands—used for address calculations of load and store operations</li> <li>Data register operands—used for register operations</li> <li>Store data register operands—used for memory stores</li> </ul>                                                                                       |

| Results      | <ul> <li>The two types of results are as follows:</li> <li>Data register results—produced by load or register operations</li> <li>Address register results—produced by Lea or Push operations</li> <li>The following examples illustrate the operand and result definitions:</li> <li>Add AX, BX</li> <li>The Add operation has two data register operands (AX and</li> </ul> |

|              | <ul> <li>BX) and one data register result (AX).</li> <li>Load BX, [SP+4·CX+8]</li> <li>The Load operation has two address register operands (SP and CX as base and index registers, respectively) and a data register result (BX).</li> <li>Store [SP+4·CX+8], AX</li> </ul>                                                                                                  |

|              | <ul> <li>The Store operation has a store data register operand (AX) and two address register operands (SP and CX as base and index registers, respectively).</li> <li>Lea SI, [SP+4·CX+8]</li> <li>The Lea operation (a type of store operation) has address register operands (SP and CX as base and index registers,</li> </ul>                                             |

respectively), and an address register result (SI).

## **Six-Stage Pipeline**

To help visualize the operations within the processor, Figure 2 illustrates the effective pipeline stages. This is a simplified illustration in that the processor contains multiple parallel pipelines (starting after common instruction fetch and x86 decode pipe stages), and these pipelines often execute operations out-of-order with respect to each other. This view of the processor execution pipeline illustrates the effect of execution latencies for various types of operations.

For many instructions, the effective pipeline is seven stages. For register operations that do not require execution stage 2, the effective pipeline is six stages.

| Instruction x86->RISC86 <sup>®</sup> | RISC86   | Operand | Execution | Execution | Commit |

|--------------------------------------|----------|---------|-----------|-----------|--------|

| Fetch Decode                         | Op Issue | Fetch   | Stage 1   | Stage 2*  |        |

*Note:* \* *Execution Stage 2 is optional*

### Figure 2. Processor Pipeline

## **Register Execution Units**

The register execution resources are attached to the register X unit execution pipeline and the register Y unit execution pipeline. Each register execution pipeline has dedicated resources that consist of an integer execution unit and a multimedia/ALU execution unit. In addition, both pipelines can use shared execution units for 3DNow! operations and MMX shift and multiply operations. Figure 3 on page 14 shows the details of the register X and Y execution pipelines.

Figure 3. Register X and Y Functional Units

The register X integer ALU execution resource can execute all ALU operations including ALU, multiply, divide (signed and unsigned), shift, and rotate. Data register results are available after a minimum of one clock of execution latency.

The dedicated integer execution unit contained within the register Y execution pipeline can execute the basic word and doubleword ALU operations (ADD, AND, CMP, OR, SUB, and XOR), zero-extend, and sign-extend operations. Data register results are available after one clock.

The register X and Y execution pipelines each contain a dedicated multimedia execution unit that handles add/subtract, logical, and pack/unpack MMX instructions. The MMX ALU units are symmetrical and can be used simultaneously. This means that the processor can execute two MMX ALU operations each clock cycle.

A number of execution resources are available to both the register X and Y execution pipelines. These shared resources

include the MMX shifter, 3DNow! ALU, and the combined MMX/3DNow! multiplier. Figure 5 on page 16 shows which instruction types are associated with the various execution pipelines.

Any combination of two operations that do not utilize the same shared execution resource can be issued and executed simultaneously. For example, the following pairs of register operations can execute together: MMX logical and 3DNow! add, 3DNow! add and 3DNow! multiply, MMX multiply and 3DNow! add, etc. If issued simultaneously, the following examples result in resource contentions and the stall of one RISC86 operation: MMX multiply and 3DNow! multiply, two MMX multiplies, two 3DNow! multiplies, two 3DNow! adds, etc.

Figure 4 shows the data flow architecture of the single-stage or double-stage integer execution unit pipeline. There are few operations (such as integer multiply) that require a second execution stage. The operation issue and operand fetch stages (execution stage 0) that precede execution stage 1 are not part of the execution pipeline. The data register result is produced near the end of the execution pipe stage.

Figure 4. Register X and Y Execution Stages

Figure 5. Microarchitecture and Execution Resources

## Load Unit

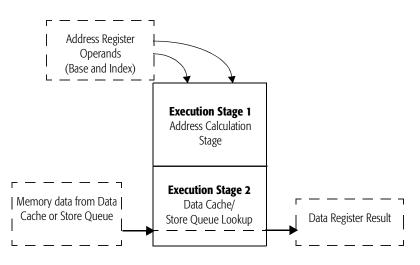

The load unit is a two-stage pipelined design that performs data memory reads. It has a two-clock latency from the time it receives the address register operands until it produces a data register result on a Dcache hit. A cache miss produces longer latencies. The load unit and the Dcache support hit-under-miss operations where a load operation bypasses a previous load operation that is stalled waiting for a cache line refill. This unit uses two address register operands and a memory data value as inputs, and produces a data register result.

Memory read data can come from either the data cache or from the store queue entry (for a recent store). If the data is forwarded from the store queue, there is zero additional execution latency, which means that a dependent load operation can complete its execution one clock after a store operation completes execution.

Figure 6 shows the architecture of the two-stage load execution pipeline. The address register operands are received at the end of the operand fetch pipe stage, and the data register result is produced near the end of the second execution pipe stage. The operation issue and fetch stages that precede these execution stages are not shown.

Figure 6. Load Execution Unit

21924D/0-January 2000

## Store Unit

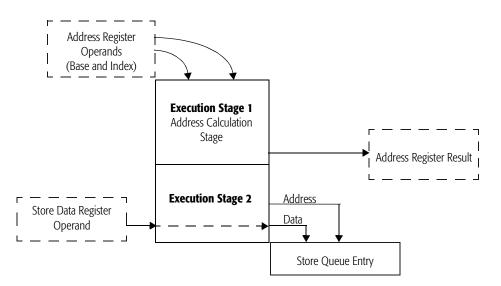

The store execution unit is a two-stage pipelined design that performs data memory writes and, in some cases, produces an address register result. For inputs, the store unit uses two address register operands and, during actual memory writes, a store data register operand. This unit also produces an address register result for some store unit operations. For most store operations, for example those that write data to memory, the store unit produces a physical memory address and the associated data bytes to be written. After execution completes, these results are entered in a new store queue entry. The store queue can hold up to seven data results, each of which can be 64 bits.

The store unit has a one-clock execution latency from the time it receives address register operands until the time it produces an address register result. The most common examples are the Load Effective Address (Lea) and Store and Update (Push) RISC86 operations, which are produced from the x86 LEA and PUSH instructions, respectively. Most store operations do not produce an address register result and only perform a memory write. The Push operation is unique because it produces an address register result and performs a memory write.

The store unit has a one-clock execution latency from the time it receives a store data operand until it enters the store memory address and data pair into the store queue.

The store unit can have a three-clock latency from the time it receives address register operands and a store data register operand until it enters the store memory address and data pair into the store queue.

*Note:* Address register operands are required at the start of execution, but register store data is not required until the end of execution.

Figure 7 on page 19 shows the architecture of the two-stage store execution pipeline. The operation issue and fetch stages that precede this execution stage are not part of the execution pipeline. The address register operands are received at the end of the operand fetch pipe stage, and the new store queue entry is created upon completion of the second execution pipe stage.

Figure 7. Store Unit Execution Pipeline

## **Branch Condition Unit**

The branch condition unit is separate from the branch prediction logic, which is utilized at x86 instruction decode time. This unit resolves conditional branches, such as JCC and LOOP instructions, at a rate of up to one per clock cycle. This unit has a dedicated RISC86 issue bus from the scheduler.

## **Floating-Point Unit**

The floating-point unit (FPU) handles all register operations for x87 instructions. The execution unit is a single-stage design that takes data register operands as inputs and produces a data register result as an output. The most common floating-point instructions have a two clock execution latency from the time the FPU receives data register operands until it produces a data register result. The FPU has its own RISC86 issue bus from the scheduler.

## Latencies and Throughput

Table 1 summarizes the static latencies and throughput of each execution unit.

| Execution<br>Unit       | Operations                                                                                   | Latency | Throughput |

|-------------------------|----------------------------------------------------------------------------------------------|---------|------------|

|                         | Integer ALU                                                                                  | 1       | 1          |

| Register X Integer Unit | Integer Multiply                                                                             | 2–3     | 2–3        |

|                         | Integer Shift                                                                                | 1       | 1          |

| Register X              | MMX <sup>™</sup> Add/Subtract                                                                | 1       | 1          |

| Multimedia Unit         | MMX Logical, Pack, Unpack                                                                    | 1       | 1          |

| Register Y Integer Unit | Integer ALU (16– and 32– bit operands)                                                       | 1       | 1          |

| Register Y              | MMX Add/Subtract                                                                             | 1       | 1          |

| Multimedia Unit         | MMX Logical, Pack, Unpack                                                                    | 1       | 1          |

| Multimedia/3DNow!™      | MMX Shifter                                                                                  | 1       | 1          |

| Shared Execution        | MMX/3DNow! Multiply, Reciprocal and, Reciprocal Square Root Iteration                        | 2       | 1          |

| Units<br>(X and Y)      | 3DNow! Add, Compare, Integer Conversion, Reciprocal, and Reciprocal Square Root Table Lookup | 2       | 1          |

|                         | From Address Register Operands to Data Register Result                                       | 2       | 1          |

| Load                    | Memory Read Data from Data Cache/Store Queue to Data Register Result                         | 0       | 1          |

|                         | From Address Register Operands to Address Register Result                                    | 1       | 1          |

| Store                   | From Store Data Register Operand to Store Queue Entry                                        | 1       | 1          |

|                         | From Address Register Operands to Store Queue Entry                                          | 3       | 1          |

| Branch                  | Resolves Branch Conditions                                                                   | 1       | 1          |

| FPU                     | FADD, FSUB                                                                                   | 2       | 2          |

| rru                     | FMUL                                                                                         | 2       | 2          |

Table 1.

RISC86<sup>®</sup> Execution Latencies and Throughput

Note:

No additional latency exists between execution of dependent operations. Bypassing of register results directly from producing execution units to the operand inputs of dependent units is fully supported. Similarly, forwarding of memory store values from the store queue to dependent load operations is supported.

## **Resource Constraints**

To optimize code effectively, execution resource constraints must be considered. Due to a fixed number of execution units, even with up to six RISC86 operations per cycle, optimal execution parallelism should be carefully scheduled.

For example, if an IMUL is decoded and issued to the X pipeline, for the next two to three cycles integer, MMX, and 3DNow! technology RISC86 operations can only be issued to the Y pipeline. Another example is two ALU instructions that require the load unit. Only one load can occur each cycle, therefore, one instruction would stall for a cycle.

Contention for execution resources can cause delays in the issuing and execution of instructions. In addition, stalls due to resource constraints can increase dependency latencies to cause or exacerbate stalls due to dependencies. In general, constraints that delay non-critical instructions do not impact performance because such stalls typically overlap with the execution of critical operations.

## **Code Sample Analysis**

The samples in this section show the execution behavior of several series of instructions as a function of decode constraints, dependencies, and execution resource constraints.

The sample tables show the x86 instructions, the RISC86 operation equivalents and a description of the events occurring within the processor.

The following nomenclature is used to describe the current location of a RISC86 operation:

- D Decode stage

- $I_X$  Issue stage of register X unit

- $O_X$  Operand fetch stage of register X unit

- $E_{X1}$  Execution stage 1 of register X unit

- $E_{X2}$  Execution stage 2 of register X unit

- I<sub>Y</sub> Issue stage of register Y unit

- O<sub>Y</sub> Operand fetch stage of register Y unit

- E<sub>Y1</sub> Execution stage 1 of register Y unit

- $E_{Y2}$  Execution stage 2 of register Y unit

- $I_L$  Issue stage of load unit

- $O_L$  Operand fetch stage of load unit

- E<sub>L1</sub> Execution stage 1 of load unit

- E<sub>L2</sub> Execution stage 2 of load unit

- I<sub>S</sub> Issue stage of store unit

- O<sub>S</sub> Operand fetch stage of store unit

- E<sub>S1</sub> Execution stage 1 of store unit

- E<sub>S2</sub> Execution stage 2 of store unit

*Note:* Instructions execute more efficiently (that is, without delays) when scheduled apart by suitable distances based on dependencies. In general, the samples in this section show poorly scheduled code in order to illustrate the resultant effects.

| Instruction | Instruction |             | RISC86®   | Clocks |   |            |                |                 |                 |                 |                 |                 |  |

|-------------|-------------|-------------|-----------|--------|---|------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

| Number      |             |             | Operation | 1      | 2 | 3          | 4              | 5               | 6               | 7               | 8               | 9               |  |

| 1           | IMUL        | EAX, EBX    | alux      | D      | D | $I_{\chi}$ | Οχ             | E <sub>X1</sub> |                 |                 |                 |                 |  |

|             |             |             | alux      |        |   |            | IX             | Оχ              | E <sub>X1</sub> |                 |                 |                 |  |

|             |             |             | alux      |        |   |            |                | Iχ              | O <sub>X</sub>  | E <sub>X1</sub> |                 |                 |  |

| 2           | INC         | ESI         | alu       |        |   | D          | Ι <sub>γ</sub> | O <sub>Y</sub>  | E <sub>Y1</sub> |                 |                 |                 |  |

| 3           | MOV         | EDI, 0x07F4 | limm      |        |   | D          |                |                 |                 |                 |                 |                 |  |

| 4           | SHL         | EAX, 8      | alux      |        |   |            | D              |                 | Ιχ              | OX              | E <sub>X1</sub> |                 |  |

| 5           | OR          | EAX, 0x0F   | alu       |        |   |            | D              | I <sub>Y</sub>  | O <sub>Y</sub>  | Iχ              | O <sub>X</sub>  | E <sub>X1</sub> |  |

| 6           | ADD         | ESI, EDX    | alu       |        |   |            |                | D               | Ιγ              | O <sub>Y</sub>  | E <sub>Y1</sub> |                 |  |

| 7           | SUB         | EDI, ECX    | alu       |        |   |            |                | D               |                 | Ιγ              | O <sub>Y</sub>  | E <sub>Y1</sub> |  |

### Table 2. Sample 1 – Integer Register Operations

- 1 It takes two decode cycles because IMUL is vector decoded. The IMUL instruction is executable only in the integer X unit. It is a non-pipelined 2–3 cycle latency register operation that is equivalent to three serially-dependent register operations (the result of the second and third operations are EAX and EDX, respectively).

- 2 This simple alu operation ends up in the Y pipe.

- 3 A load immediate (limm) RISC86 operation does not require execution. The result value is immediately available to dependent operations.

- 4 Shift instructions are only executable in the integer X unit. Issue is delayed by preceding IMUL operations due to a resource constraint of the integer X unit.

- 5 The register operation is bumped out of the integer Y unit in clock 6 because it must wait for more than one cycle for its dependencies to resolve. It is reissued in the next cycle to the integer X unit (just in time for availability of its operand).

- 6 This add alu falls through to the integer Y unit right behind the first issuance of instruction #5 without delay (as a result of instruction #5 being bumped out of the way).

- 7 The issuance of the subtract register operation is delayed in clock 6 due to the resource constraints of the integer Y unit.

| Instruction |     |                    | RISC86 <sup>®</sup> |   |                  |                |                 |                  | Clock                     | s               |                 |          |                 |              |

|-------------|-----|--------------------|---------------------|---|------------------|----------------|-----------------|------------------|---------------------------|-----------------|-----------------|----------|-----------------|--------------|

| Number      |     | Instruction        | Operation           | 1 | 2                | 3              | 4               | 5                | 6                         | 7               | 8               | 9        | 10              | 11           |

| 1           | DEC | EDX                | alu                 | D | $\mathbf{I}_{X}$ | O <sub>X</sub> | E <sub>X1</sub> |                  |                           |                 |                 |          |                 |              |

| 2           | MOV | EDI, [ECX]         | load                | D | ΙL               | OL             | E <sub>L1</sub> | E <sub>L2</sub>  |                           |                 |                 |          |                 |              |

| 3           | SUB | EAX, [EDX+20]      | load                |   | D                | IL             | 0 <sub>L</sub>  | $E_{L1}$         | E <sub>L2</sub>           |                 |                 |          |                 |              |

|             |     |                    | alu                 |   |                  | Iχ             | O <sub>X</sub>  | Iχ               | O <sub>X</sub>            | E <sub>X1</sub> |                 |          |                 |              |

| 4           | SAR | EAX, 5             | alux                |   | D                |                | Iχ              | O <sub>X</sub>   | $\mathbf{I}_{\mathbf{X}}$ | O <sub>X</sub>  | E <sub>X1</sub> |          |                 |              |

| 5           | ADD | ECX, [EDI+4]       | load                |   |                  | D              | ΙL              | 0 <sub>L</sub>   | $E_{L1}$                  | E <sub>L2</sub> |                 |          |                 |              |

|             |     |                    | alu                 |   |                  |                | Ιγ              | O <sub>Y</sub>   | $\mathbf{I}_{Y}$          | O <sub>Y</sub>  | E <sub>Y1</sub> |          |                 |              |

| 6           | AND | EBX, 0x1F          | alu                 |   |                  | D              |                 | $\mathbf{I}_{Y}$ | O <sub>Y</sub>            | E <sub>Y1</sub> |                 |          |                 |              |

| 7           | MOV | ESI, [0x0F100]     | load                |   |                  |                | D               | ΙL               | 0 <sub>L</sub>            | E <sub>L1</sub> | E <sub>L2</sub> |          |                 |              |

| 8           | OR  | ECX, [ESI+EAX*4+8] | load                |   |                  |                | D               |                  | ΙL                        | 0 <sub>L</sub>  | 0 <sub>L</sub>  | $E_{L1}$ | E <sub>L2</sub> |              |

|             |     |                    | alu                 |   |                  |                |                 |                  |                           | Iχ              | O <sub>X</sub>  | Iχ       | O <sub>X</sub>  | $E_{\chi_1}$ |

- 1 This simple alu operation ends up in the X pipe.

- 2 This operation occupies the load execution unit.

- The register operand for the load operation is bypassed, without delay, from the result of instruction #1's register operand. In clock 4, the register operation is bumped out of the integer X unit while waiting for the previous load operation result to complete. It is reissued just in time to receive the bypassed result of the load.

- 4 Shift instructions are only executable in the integer X unit. The register operation is bumped in clock 5 while waiting for the result of the preceding instruction #3.

- 5 The register operand for the load operation is bypassed, without delay, from the result of instruction #2's register operand. This and most surrounding load operations are generated by instruction decoders, and issued and smoothly executed by the load unit at a rate of one clock per cycle. In clock 5, the register operation is bumped out of the integer Y unit while waiting for the previous load operation result to complete.

- 6 The register operation falls through into the integer Y unit right behind instruction #5's register operation.

- 7 This operation falls into the load unit behind the load in instruction #5.

- 8 The operand fetch for the load operation is delayed because it needs the result of the immediately preceding load operation #7 as well as the results from earlier instruction #4.

| Instruction<br>Number | Instruction               | RISC86 <sup>®</sup> | Clocks |    |                  |                 |                 |                |                 |                 |                 |                 |                |  |  |

|-----------------------|---------------------------|---------------------|--------|----|------------------|-----------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|----------------|--|--|

|                       |                           | Operation           | 1      | 2  | 3                | 4               | 5               | 6              | 7               | 8               | 9               | 10              | 11             |  |  |

| 1                     | MOV EDX,<br>[0xA0008F00]  | load                | D      | IL | OL               | E <sub>L1</sub> | E <sub>L2</sub> |                |                 |                 |                 |                 |                |  |  |

| 2                     | ADD [EDX+16], 7           | load                |        | D  | $\mathbf{I}_{L}$ | 0 <sub>L</sub>  | OL              | $E_{L1}$       | E <sub>L2</sub> |                 |                 |                 |                |  |  |

|                       |                           | alu                 |        |    | Iχ               | O <sub>X</sub>  | Iχ              | O <sub>X</sub> | O <sub>X</sub>  | E <sub>X1</sub> |                 |                 |                |  |  |

|                       |                           | store               |        |    | ١ <sub>s</sub>   | 0 <sub>S</sub>  | 0 <sub>S</sub>  | $E_{S1}$       | E <sub>S2</sub> | E <sub>S2</sub> |                 |                 |                |  |  |

| 3                     | SUB EAX, [EDX+16]         | load                |        |    | D                | IL              | IL              | OL             | E <sub>L1</sub> | E <sub>L2</sub> | E <sub>L2</sub> |                 |                |  |  |

|                       |                           | alu                 |        |    |                  | Iχ              | Ο <sub>χ</sub>  | Iχ             | Iχ              | Οχ              | 0χ              | E <sub>X1</sub> |                |  |  |

| 4                     | PUSH EAX                  | store               |        |    | D                | ١ <sub>s</sub>  | ١ <sub>s</sub>  | 0 <sub>S</sub> | E <sub>S1</sub> | E <sub>S2</sub> | E <sub>S2</sub> | E <sub>S2</sub> |                |  |  |

| 5                     | LEA EBX,<br>[ECX+EAX*4+3] | store               |        |    |                  | D               |                 | ١ <sub>s</sub> | Os              | Os              | O <sub>S</sub>  | E <sub>S1</sub> | E <sub>S</sub> |  |  |

| 6                     | MOV EDI, EBX              | alu                 |        |    |                  | D               | Ιγ              | 0 <sub>Y</sub> | Ιγ              | O <sub>Y</sub>  | Iχ              | 0χ              | Eχ             |  |  |

Table 4.

Sample 3 – Integer Register and Memory Load/Store Operations

- 1 This operation occupies the load unit.

- 2 This long-decoded ADD instruction takes a single clock to decode. The operand fetch for the load operation is delayed waiting for the result of the previous load operation from instruction #1. The store operation completes concurrent with the register operation. The result of the register operation is bypassed directly into a new store queue entry created by the store operation.

- The issue of the load operation is delayed because the operand fetch of the preceding load operation from instruction #2 was delayed. The completion of the load operation is held up due to a memory dependency on the preceding store operation of instruction #2. The load operation completes immediately after the store operation, with the store data being forwarded from a new store queue entry.

- 4 Completion of the store operation is held up due to a data dependency on the preceding instruction #3. The store data is bypassed directly into a new store queue entry from the result of instruction #3's register operation.

- 5 The Lea RISC86 operation is executed by the store unit. The operand fetch is delayed waiting for the result of instruction #3. The register result value is produced in the first execution stage of the store unit.

- 6 This simple alu operation is stalled due to the dependency of the EBX result in instruction #5.

AMD-K6<sup>®</sup> Processor Code Optimization

| Inst.<br>Num. | Instruction         | RISC86 <sup>®</sup><br>Operation | Clocks |                  |                |                 |                 |                 |                 |                 |                            |                 |          |                 |  |  |

|---------------|---------------------|----------------------------------|--------|------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------------|-----------------|----------|-----------------|--|--|

|               |                     |                                  | 1      | 2                | 3              | 4               | 5               | 6               | 7               | 8               | 9                          | 10              | 11       | 12              |  |  |

| 1             | PADDSWMM0, MM4      | alu                              | D      | Iχ               | Ο <sub>χ</sub> | E <sub>X1</sub> |                 |                 |                 |                 |                            |                 |          |                 |  |  |

| 2             | PADDSWMM1, MM5      | alu                              | D      | $\mathbf{I}_{Y}$ | O <sub>Y</sub> | $E_{Y1}$        |                 |                 |                 |                 |                            |                 |          |                 |  |  |

| 3             | PSRAW MM0, 3        | alu                              |        | D                | Iχ             | O <sub>X</sub>  | E <sub>X1</sub> |                 |                 |                 |                            |                 |          |                 |  |  |

| 4             | MOVQ MM2, [EAX+EBX] | mload                            |        | D                | ΙL             | OL              | E <sub>L1</sub> | E <sub>L2</sub> |                 |                 |                            |                 |          |                 |  |  |

| 5             | PAND MM0, MM3       | alu                              |        |                  | D              | Iχ              | O <sub>X</sub>  | E <sub>X1</sub> |                 |                 |                            |                 |          |                 |  |  |

| 6             | PMULLWMM2, [EDI+8]  | mload                            |        |                  | D              | ΙL              | 0 <sub>L</sub>  | E <sub>L1</sub> | E <sub>L2</sub> |                 |                            |                 |          |                 |  |  |

|               |                     | alu                              |        |                  |                | Iγ              | O <sub>Y</sub>  | Iχ              | 0χ              | $E_{\chi_1}$    | E <sub>X2</sub>            |                 |          |                 |  |  |

| 7             | MOVQ [ESP+4], MM2   | mstore                           |        |                  |                | D               | ١ <sub>s</sub>  | 0 <sub>S</sub>  | $E_{S1}$        | E <sub>S2</sub> | E <sub>S2</sub>            |                 |          |                 |  |  |

| 8             | ADD EBX, ECX        | alu                              |        |                  |                | D               | Iχ              | O <sub>X</sub>  | $E_{X1}$        |                 |                            |                 |          |                 |  |  |

| 9             | PMULLWMM6, MM7      | alu                              |        |                  |                |                 | D               | Ιγ              | O <sub>Y</sub>  | $E_{Y1}$        | $\mathbf{E}_{\mathbf{Y1}}$ | E <sub>Y2</sub> |          |                 |  |  |

| 10            | PMADDWDMM2, MM6     | alu                              |        |                  |                |                 | D               |                 | Iχ              | Оχ              | O <sub>X</sub>             | O <sub>X</sub>  | $E_{X1}$ | E <sub>X2</sub> |  |  |

### Table 5. Sample 4 – Integer, MMX<sup>™</sup>, and Memory Load/Store Operations

- 1, 2 Instructions 1 and 2 are decoded, issued, and executed simultaneously and in parallel due to no decode restrictions, dependency delays, or execution resource constraints.

- 3 This instruction is decoded, issued, and executed without delay, one cycle behind the preceding one-cycle execution latency instruction on which it is dependent.

- 4 This multimedia operation occupies the load unit.

- 5 This instruction is decoded, issued, and executed without delay, right behind the preceding operations on which it is dependent.

- 6 This and the preceding instruction are decoded and issued together without delay. The operand fetch of the register operation is delayed because of the dependency on the associated load. As a result, the register operation is bumped out of register unit Y in clock 5 and is reissued in the next cycle to register unit X (as it happens), just in time for availability of its operands.

- 7 Completion of this store operation is held up due to a data dependency on the preceding MMX multiply register operation (which has a two-cycle execution latency). The store data is bypassed directly into a new store queue entry from the result of the register operation.

- 8 This operation is issued to register unit X and executes without delay and out-of-order with respect to the preceding register operation from instruction #6 (which was bumped out of the way while waiting for its operands).

- 9 This MMX multiply register operation issues to and starts execution in register unit Y in parallel with an MMX multiply register operation from instruction #6 which simultaneously issues to and starts execution in register unit X. Due to an execution resource constraint, this operation is delayed one cycle in its first execution pipe stage and then executes and completes normally, one cycle behind the other contending register operation. (This takes advantage of the pipelined nature of the MMX multiply execution logic.)

- 10 The issue of this operation is delayed (in clock 6) for one cycle due to two earlier register operations being selected for issue. It is then delayed further during operand fetch while waiting for the preceding two-cycle latency MMX multiply register operations to complete execution.

# **Instruction Dispatch**

This chapter describes the RISC86 operations executed by each instruction. Tables 6 through 9 starting on page 29 define the integer, MMX, floating-point, and 3DNow! instructions. Only the AMD-K6-2 and AMD-K6-III processors support the instructions in Table 9, "3DNow!™ Instructions," on page 55.

The first column in these tables indicates the instruction mnemonic and operand types with the following notations:

- *reg8*—byte integer register defined by instruction byte(s) or bits 5, 4, and 3 of the modR/M byte

- mreg8—byte integer register or byte integer value in memory defined by the modR/M byte

- *reg16/32*—word or doubleword integer register defined by instruction byte(s) or bits 5, 4, and 3 of the modR/M byte

- mreg16/32—word or doubleword integer register, or word or doubleword integer value in memory defined by the modR/M byte

- *mem8*—byte integer value in memory

- *mem16/32*—word or doubleword integer value in memory

- *mem32/48*—doubleword or 48-bit integer value in memory

- *mem48*—48-bit integer value in memory

- *mem64*—64-bit value in memory

- *imm8*—8-bit immediate value

- *imm16/32*—16-bit or 32-bit immediate value

AMD-K6<sup>®</sup> Processor Code Optimization

- *disp8*—8-bit displacement value

- *disp16/32*—16-bit or 32-bit displacement value

- *disp32/48*—doubleword or 48-bit displacement value

- *eXX*—register width depending on the operand size

- *mem32real*—32-bit floating-point value in memory

- *mem64real*—64-bit floating-point value in memory

- *mem80real*—80-bit floating-point value in memory

- *mmreg*—MMX/3DNow! register

- *mmreg1*—MMX/3DNow! register defined by bits 5, 4, and 3 of the modR/M byte

- *mmreg2*—MMX/3DNow! register defined by bits 2, 1, and 0 of the modR/M byte

The second and third columns list all applicable encoding opcode bytes.

The fourth column lists the modR/M byte when used by the instruction. The modR/M byte defines the instruction as register or memory form. If mod bits 7 and 6 are documented as mm (memory form), mm can only be 10b, 01b, or 00b.

The fifth column lists the type of instruction decode—short, long, or vector. The processor decode logic can process two short, one long, or one vector decode per clock. Any pair of short decodable instructions, be it integer, floating-point, MMX, or 3DNow!, can be decoded simultaneously. All MMX and 3DNow! instructions are short decodable except the EMMS, FEMMS, and PREFETCH instructions.

The sixth column lists the type of RISC86 operation(s) required for the instruction. The operation types and corresponding execution units are as follows:

- *load*, *fload*, *mload*—load unit

- *store, fstore, mstore*—store unit

- *alu*—either of the integer register execution units

- *alux*—integer register X execution unit only

- *branch*—branch condition unit

- *float*—floating-point execution unit

- *meu*—Multimedia execution units for MMX and 3DNow! instructions

- *limm*—load immediate, instruction control unit only

The operation(s) of most instructions form a single dependency chain. For instructions whose operations form two parallel dependency chains, the RISC86 operations for each dependency chain is shown on a separate row.

| Table 6. | Integer | Instructions |

|----------|---------|--------------|

|----------|---------|--------------|

| Instruction Mnemonic              | First<br>Byte | Second<br>Byte | ModR/M<br>Byte | Decode<br>Type | RISC86 <sup>®</sup><br>Operations |

|-----------------------------------|---------------|----------------|----------------|----------------|-----------------------------------|

| AAA                               | 37h           |                |                | vector         |                                   |

| AAD                               | D5h           | 0Ah            |                | vector         |                                   |

| AAM                               | D4h           | 0Ah            |                | vector         |                                   |

| AAS                               | 3Fh           |                |                | vector         |                                   |

| ADC mreg8, reg8                   | 10h           |                | 11-xxx-xxx     | vector         |                                   |

| ADC mem8, reg8                    | 10h           |                | mm-xxx-xxx     | vector         |                                   |

| ADC mreg16/32, reg16/32           | 11h           |                | 11-xxx-xxx     | vector         |                                   |

| ADC mem16/32, reg16/32            | 11h           |                | mm-xxx-xxx     | vector         |                                   |

| ADC reg8, mreg8                   | 12h           |                | 11-xxx-xxx     | vector         |                                   |

| ADC reg8, mem8                    | 12h           |                | mm-xxx-xxx     | vector         |                                   |

| ADC reg16/32, mreg16/32           | 13h           |                | 11-xxx-xxx     | vector         |                                   |

| ADC reg16/32, mem16/32            | 13h           |                | mm-xxx-xxx     | vector         |                                   |

| ADC AL, imm8                      | 14h           |                |                | vector         |                                   |

| ADC EAX, imm16/32                 | 15h           |                |                | vector         |                                   |

| ADC mreg8, imm8                   | 80h           |                | 11-010-xxx     | vector         |                                   |

| ADC mem8, imm8                    | 80h           |                | mm-010-xxx     | vector         |                                   |

| ADC mreg16/32, imm16/32           | 81h           |                | 11-010-xxx     | vector         |                                   |

| ADC mem16/32, imm16/32            | 81h           |                | mm-010-xxx     | vector         |                                   |

| ADC mreg16/32, imm8 (signed ext.) | 83h           |                | 11-010-xxx     | vector         |                                   |

| ADC mem16/32, imm8 (signed ext.)  | 83h           |                | mm-010-xxx     | vector         |                                   |

| ADD mreg8, reg8                   | 00h           |                | 11-xxx-xxx     | short          | alux                              |

| ADD mem8, reg8                    | 00h           |                | mm-xxx-xxx     | long           | load, alux, store                 |

| ADD mreg16/32, reg16/32           | 01h           |                | 11-xxx-xxx     | short          | alu                               |

| ADD mem16/32, reg16/32            | 01h           |                | mm-xxx-xxx     | long           | load, alu, store                  |

| ADD reg8, mreg8                   | 02h           |                | 11-xxx-xxx     | short          | alux                              |

| ADD reg8, mem8                    | 02h           |                | mm-xxx-xxx     | short          | load, alux                        |

| ADD reg16/32, mreg16/32           | 03h           |                | 11-xxx-xxx     | short          | alu                               |

| ADD reg16/32, mem16/32            | 03h           |                | mm-xxx-xxx     | short          | load, alu                         |

| ADD AL, imm8                      | 04h           |                |                | short          | alux                              |

AMD-K6<sup>®</sup> Processor Code Optimization

| Instruction Mnemonic              | First<br>Byte | Second<br>Byte | ModR/M<br>Byte | Decode<br>Type | RISC86 <sup>®</sup><br>Operations |

|-----------------------------------|---------------|----------------|----------------|----------------|-----------------------------------|

| ADD EAX, imm16/32                 | 05h           |                |                | short          | alu                               |

| ADD mreg8, imm8                   | 80h           |                | 11-000-xxx     | short          | alux                              |

| ADD mem8, imm8                    | 80h           |                | mm-000-xxx     | long           | load, alux, store                 |

| ADD mreg16/32, imm16/32           | 81h           |                | 11-000-xxx     | short          | alu                               |

| ADD mem16/32, imm16/32            | 81h           |                | mm-000-xxx     | long           | load, alu, store                  |

| ADD mreg16/32, imm8 (signed ext.) | 83h           |                | 11-000-xxx     | short          | alux                              |

| ADD mem16/32, imm8 (signed ext.)  | 83h           |                | mm-000-xxx     | long           | load, alux, store                 |

| AND mreg8, reg8                   | 20h           |                | 11-xxx-xxx     | short          | alux                              |

| AND mem8, reg8                    | 20h           |                | mm-xxx-xxx     | long           | load, alux, store                 |

| AND mreg16/32, reg16/32           | 21h           |                | 11-xxx-xxx     | short          | alu                               |

| AND mem16/32, reg16/32            | 21h           |                | mm-xxx-xxx     | long           | load, alu, store                  |

| AND reg8, mreg8                   | 22h           |                | 11-xxx-xxx     | short          | alux                              |

| AND reg8, mem8                    | 22h           |                | mm-xxx-xxx     | short          | load, alux                        |

| AND reg16/32, mreg16/32           | 23h           |                | 11-xxx-xxx     | short          | alu                               |

| AND reg16/32, mem16/32            | 23h           |                | mm-xxx-xxx     | short          | load, alu                         |

| AND AL, imm8                      | 24h           |                |                | short          | alux                              |

| AND EAX, imm16/32                 | 25h           |                |                | short          | alu                               |

| AND mreg8, imm8                   | 80h           |                | 11-100-xxx     | short          | alux                              |

| AND mem8, imm8                    | 80h           |                | mm-100-xxx     | long           | load, alux, store                 |

| AND mreg16/32, imm16/32           | 81h           |                | 11-100-xxx     | short          | alu                               |

| AND mem16/32, imm16/32            | 81h           |                | mm-100-xxx     | long           | load, alu, store                  |

| AND mreg16/32, imm8 (signed ext.) | 83h           |                | 11-100-xxx     | short          | alux                              |

| AND mem16/32, imm8 (signed ext.)  | 83h           |                | mm-100-xxx     | long           | load, alux, store                 |

| ARPL mreg16, reg16                | 63h           |                | 11-xxx-xxx     | vector         |                                   |

| ARPL mem16, reg16                 | 63h           |                | mm-xxx-xxx     | vector         |                                   |

| BOUND                             | 62h           |                |                | vector         |                                   |

| BSF reg16/32, mreg16/32           | 0Fh           | BCh            | 11-xxx-xxx     | vector         |                                   |

| BSF reg16/32, mem16/32            | 0Fh           | BCh            | mm-xxx-xxx     | vector         |                                   |

| BSR reg16/32, mreg16/32           | 0Fh           | BDh            | 11-xxx-xxx     | vector         |                                   |

| BSR reg16/32, mem16/32            | 0Fh           | BDh            | mm-xxx-xxx     | vector         |                                   |

| BSWAP EAX                         | 0Fh           | C8h            |                | long           | alu                               |

| BSWAP ECX                         | 0Fh           | C9h            |                | long           | alu                               |

| BSWAP EDX                         | 0Fh           | CAh            |                | long           | alu                               |

| Instruction Mnemonic        | First<br>Byte | Second<br>Byte | ModR/M<br>Byte | Decode<br>Type | RISC86 <sup>®</sup><br>Operations |

|-----------------------------|---------------|----------------|----------------|----------------|-----------------------------------|

| BSWAP EBX                   | 0Fh           | CBh            |                | long           | alu                               |

| BSWAP ESP                   | 0Fh           | CCh            |                | long           | alu                               |

| BSWAP EBP                   | 0Fh           | CDh            |                | long           | alu                               |

| BSWAP ESI                   | 0Fh           | CEh            |                | long           | alu                               |

| BSWAP EDI                   | 0Fh           | CFh            |                | long           | alu                               |

| BT mreg16/32, reg16/32      | 0Fh           | A3h            | 11-xxx-xxx     | vector         |                                   |

| BT mem16/32, reg16/32       | 0Fh           | A3h            | mm-xxx-xxx     | vector         |                                   |

| BT mreg16/32, imm8          | 0Fh           | BAh            | 11-100-xxx     | vector         |                                   |

| BT mem16/32, imm8           | 0Fh           | BAh            | mm-100-xxx     | vector         |                                   |

| BTC mreg16/32, reg16/32     | 0Fh           | BBh            | 11-xxx-xxx     | vector         |                                   |

| BTC mem16/32, reg16/32      | 0Fh           | BBh            | mm-xxx-xxx     | vector         |                                   |

| BTC mreg16/32, imm8         | 0Fh           | BAh            | 11-111-xxx     | vector         |                                   |

| BTC mem16/32, imm8          | 0Fh           | BAh            | mm-111-xxx     | vector         |                                   |

| BTR mreg16/32, reg16/32     | 0Fh           | B3h            | 11-xxx-xxx     | vector         |                                   |

| BTR mem16/32, reg16/32      | 0Fh           | B3h            | mm-xxx-xxx     | vector         |                                   |

| BTR mreg16/32, imm8         | 0Fh           | BAh            | 11-110-xxx     | vector         |                                   |

| BTR mem16/32, imm8          | 0Fh           | BAh            | mm-110-xxx     | vector         |                                   |

| BTS mreg16/32, reg16/32     | 0Fh           | ABh            | 11-xxx-xxx     | vector         |                                   |

| BTS mem16/32, reg16/32      | 0Fh           | ABh            | mm-xxx-xxx     | vector         |                                   |

| BTS mreg16/32, imm8         | 0Fh           | BAh            | 11-101-xxx     | vector         |                                   |

| BTS mem16/32, imm8          | 0Fh           | BAh            | mm-101-xxx     | vector         |                                   |

| CALL full pointer           | 9Ah           |                |                | vector         |                                   |

| CALL near imm16/32          | E8h           |                |                | short          | store                             |

| CALL mem16:16/32            | FFh           |                | 11-011-xxx     | vector         |                                   |

| CALL near mreg32 (indirect) | FFh           |                | 11-010-xxx     | vector         |                                   |

| CALL near mem32 (indirect)  | FFh           |                | mm-010-xxx     | vector         |                                   |

| CBW/CWDE EAX                | 98h           |                |                | vector         |                                   |