# THE INSIDERS' GUIDE TO MICROPROCESSOR HARDWARE

# **68HC11 Grows Up to 16 Bits** Motorola's 68HC12 Line Boosts Performance up to 10 Times

# by Jim Turley

Motorola's popular 8-bit microcontroller architecture, the 68HC11, now has a big brother. The new 68HC12 maintains all of its sibling's distinguishing features but doubles both clock rate and bus width, extends the address space, improves code density, and adds dozens of new instructions, including some for fuzzy logic.

Strategically, the 16-bit HC12 family—which initially includes two members—fills a small gap between Motorola's 8-bit 68HC11 family and the 16-bit 68HC16 line. The HC12 provides a source-level software upgrade for 8-bit designers who are outgrowing the HC11 but don't want to develop entirely new code and new hardware for the HC16.

Motorola believes the HC12 and HC16 can peacefully coexist in the company's 16-bit microcontroller lineup because the HC16 offers better performance and better signal-processing capabilities, while the HC12 offers compatibility with the HC11 and lower power dissipation. The first two chips in the new family are both priced below \$25 and will begin sampling in June and October of this year.

# Programming Model Identical to HC11

The HC12's register set and programming model are identical to those of the HC11, as Figure 1 shows. The two 8-bit accumulators, A and B, can be concatenated into a single 16bit register, D. Index registers X and Y are used to reference memory-resident operands, while the stack pointer (SP) and program counter (PC) fulfill the obvious functions.

The HC12's exception stack and fault model are also identical to those of the HC11 chips, so users with existing code that examines or manipulates the stack will find that it works without modification. Source-code compatibility was a primary concern for the HC12's designers; given that Motorola already has a 16-bit product family, the HC12 had to offer something the HC16 didn't.

The familiar programming model belies major changes lurking beneath the surface. Motorola's customer surveys indicated that HC11 users were frustrated by the irregular and nonorthogonal treatment of the X and Y index registers. For example, most HC11 instructions can reference memory through either the X or Y index registers, but using the Y register adds a prefix byte to the object code, which requires an additional clock cycle to fetch over the HC11's 8-bit bus.

These concerns were addressed with the HC12, which encodes X- and Y-indexed instructions equally. At the same time, addressing modes were modified to support both SP and PC as index registers. Thus, compiler writers can more easily reference operands passed on the stack, and positionindependent code can access data relative to the program counter.

# Instruction Set Gets 65 New Mnemonics

The design goals for the HC12 stipulated total source-level (but not binary) compatibility with the HC11 so users could transfer existing assembly source without modification. This it does, duplicating every HC11 mnemonic and addressing mode, right down to some unintended quirks that users have learned to accept.

| 7               | А                                                       | 0  | 7   |   | В |   |   |   | 0 |

|-----------------|---------------------------------------------------------|----|-----|---|---|---|---|---|---|

|                 | 8-bit accumulators A & B or 16-bit double accumulator D |    |     |   |   |   |   | D |   |

| 15              | IX                                                      |    |     |   |   |   |   | 0 |   |

|                 | Index register X                                        |    |     |   |   |   |   |   |   |

| 15              | IY                                                      |    |     |   |   |   |   | 0 |   |

|                 | Index register Y                                        |    |     |   |   |   |   |   |   |

| 15              |                                                         | SP | )   |   |   |   |   |   | 0 |

| Stack pointer   |                                                         |    |     |   |   |   |   |   |   |

| 15              |                                                         | РС | :   |   |   |   |   |   | 0 |

| Program counter |                                                         |    |     |   |   |   |   |   |   |

|                 |                                                         | [  | S X | н | T | Ν | Z | v | С |

|                 | Condition codes register                                |    |     |   |   |   |   |   |   |

Figure 1. The register set of the 68HC12 is identical to that of its predecessor, the 8-bit 68HC11.

The HC12 truly implements its predecessor's instruction set one for one; unlike Philips' 8051XA tools (*see* **081304.PDF**), the HC12 assembler does not replace unimplemented legacy instructions with equivalent constructs. In addition to the HC11 instruction set, the HC12 has more than 65 new operations that should cheer compiler writers and relieve assembly programmers.

Table 1 lists the complete set of HC12 instructions with enhancements over the HC11 indicated. Some examples include the TFR (transfer) and EXG (exchange) instructions, which now handle mismatched register sizes. Exchanging an 8-bit with a 16-bit register zero-extends the 8-bit value; copying mismatched registers sign-extends the smaller register. This latter operation can be used by C compilers to cast a *char* to an *int*.

In cases where HC11 instructions sometimes produce unwanted side effects, as when the TAB and TBA (transfer A/B) instructions set condition codes even though most transfer instructions do not, the HC12 includes compatible instructions (complete with side effects) in addition to the preferred (and more orthogonal) versions. The generalized TFR instruction is now preferred over TAB and TBA, while ANDCC and ORCC replace SEI, CLI, SEC, and CLC.

# No Binary Compatibility with HC11

The HC12's opcode map was completely rewritten, so binary

| MOVB Move byte BCS/BCC Branch if carry set/clear ANDA/ANDE Logical AND A/B   MOVW Move word BCG/BLE Branch if greater/less or equal ANDCC Logical AND A/B   LDD Load dark pointer BC/BLE Branch if greater/less or equal ANDCC Logical AND A/B   LDXLDY Load dark pointer BC/BLE Branch if greater/less or equal ANDCC Anthmetic shift left A/B   LEAS Load effective address, stack BH/SBLS Branch if higher/lower or same ARA/A/SB Arithmetic shift left A/B   LEAXLEXA Load effective address, stack BRCL/RRSET Branch if bits cleared/set COM Compare A/B   STM STS Store dauble D BYSRVS Branch to subroutine COM Compare A/B   STMSTS Store dauble D BYSRVS Branch to subroutine CPD Compare stack pointer   STMSTS Store A/B Store dauble D Descrement, branch if roz CPM COMACOMB Complement A/B   PSHXPBHP Puth condition codes totack DBEN Decrement, branch if razry set/clear CRX.ASR Logical shift left A/B   PULC Pull condition codes totack DBEN Decrement, branch if razry set/clear CRX.ASR Logical shift left A/B   PULX/PULY Pull                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Transfer Flow Control |                                |           |                                  | Shift and Logical |                           |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------|-----------|----------------------------------|-------------------|---------------------------|--|--|

| MOW     Move word     BEC/BINE     Branch if equal/not equal     ANDCC     Logical AND condition codes       LDAALDAB     Load double D     BGE/BILE     Branch if greater/Hso requal     ASUASR     Arithmetic shift left/right       LDD     Load double D     BGE/BILE     Branch if greater/Hso requal     ASUASR     Arithmetic shift left A/8       LDXLDY     Load defective address, stat.     BH/BILO     Branch if higher/lower or same     ARUASR     Arithmetic shift left A/8       LEAS     Load effective address, stat.     BPUEM     Branch if higher/lower or same     Compare A/8     Compare A/8       STD     Store duble D     BYLBN     Branch if higher/lower or same     CPD     Compare A/8     Compare A/8       STD     Store duble D     BYLBN     Branch to subroutine     CPZ     CPC     Compare A/8       PSHAPSHB     Push condition codes to stack     DBSC     Decrement, branch if zero     DPXCP     Compare A/8       PULX/PULB     Puil condition codes to stack     DBN     Decrement, branch if arrow     CBLUSPUL     Compare A/8       PULX/PULB     Puil Condition codes to stack     DBN     Dec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MOVB                       | Move byte                      | BCS/BCC   | Branch if carry set/clear        | ANDA/ANDB         | Logical AND A/B           |  |  |

| LDAALDAB Load A/B<br>LDD<br>LDD<br>LDD<br>LDD<br>LDD<br>LDD<br>LDD<br>LD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MOVW                       |                                | BEQ/BNE   |                                  |                   |                           |  |  |

| LDDLoad double DBGT/BLTBranch if greater than/less thanSLAASLBArithmetic shift left A/8LDSLoad stack pointerBH/BLOBranch if higher/lower or sameASLAASLBArithmetic shift left A/8LDX/LDYLoad effective address, stackBPL/BLSBranch if higher/lower or sameASLAASLBArithmetic shift left A/8LEAXLoad effective address, stackBPL/BLMBranch if bits/fniumsCMPA/CMMBComplement A/8STAASTABStore A/8BRCLR/BRSETBranch if bits/fniumsCMMA/CMMBComplement A/8STASTABStore stack pointerBSRBranch to subroutineCPDCOM/CMBComplement A/8STNSTYStore X/YStore X/YRTCReturn from CALLCPDCompare stack pointerSTNSTYStore X/YStackDEFCDecrement, branch if rot zeroLSULSRLogical shift left A/8PSHX/PSHYPuish A/8 to stackDEFCDecrement, branch if rot zeroLSULSRLogical shift left A/8PULZPuil condition codes to stackJMPJump to subroutineLSULSRLogical shift left A/8PULXPULBPuil A/8 from stackJMPJump to subroutineLSUALSLBLogical shift left double DPULXPULPPuil A/16 to AASEA/ASERTSReturn from subroutineLSRALSRBLogical shift left double DPULXPULPPuil A/17 to stackJSRJump to subroutineLSRALSRBLogical shift left double DPULXPULPPuil A/17 to stackJSRJump to subroutineLSRALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                                |           |                                  |                   |                           |  |  |

| LDS<br>LDXLDYLoad stack pointer<br>LDXLDYBH/BLO<br>Barch if higher/lower<br>BH/SBLSSLDArithmetic shift left double D<br>ASRA-ASRAAtthmetic shift left double D<br>Compare A/BAsra-ASRA<br>Atthmetic shift left A/B<br>COMPACMPBArithmetic shift left double D<br>Compare A/BCompare A/B<br>Compare A/BCompare A/B<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                                |           |                                  |                   |                           |  |  |

| LDXLDY Load Load HSrbLS Branch if higher/Jower or same SRAASRB Arithmetic shift right A/B   LEAX Lead effective address, stack BPU/BM BRACHRN Branch if blus/minus CMPACMPB Complement memory   STD Store double D BYUBNCK BRACHRN Branch if blus/minus CMACOMB Complement A/B   STD Store double D BSVS/BVCK Branch to subroutine CPA COMACOMB Complement A/B   STXSTY Store double D BSR Branch to subroutine CPA Complement A/B   PSHACPSHP Push condition codes to stack DBRC Decrement, branch if not zero LSLALSLB Logical shift left A/B   PULX/PULD Pull condition codes to stack DBRE Decrement, branch if not zero LSLALSLB Logical shift left A/B   PULX/PULY Pull A/B from stack Transfer A to condition codes to A BRUBNE LSCLSEC Long branch if zero/not zero   PULX/PULY Pull X/PULY Pull X/PULY Pull X/PULY BGTLBL LBGTLBL LB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                                |           |                                  |                   |                           |  |  |

| LEAX   Lad efective address, stack   BPL/BMI   Branch if plis/minus   CMPA/CMPB   Compare A/B     LEAXLEAY   Lad efective address, stack   BPL/BMI   Branch always/never   CMPA/CMPB   Complement memory     STD   Store stack pointer   BS/BV/C   Branch always/never   CPS   Compare stack pointer     STX/STY   Store stack pointer   BS/BV/C   Branch always/never   CPS   Compare stack pointer     STX/STY   Store stack pointer   CALL   Call subroutine   CPS   Compare stack pointer     STX/STY   Store stack pointer   DBR/E   Decrement, branch if not zero   LSL/LSLB   Logical shift eft A/B     PSHAP/SHP   Push Avbit for stack   IBEN   Increment, branch if not zero   LSR/LSLB   Logical shift eft A/B     PULX/PUL   Pull A/B for stack   IBEN   Increment, branch if ero zero   LSR/LSLB   Logical shift eft A/B     PULX/PUL   Pull A/B for stack   IBEN   Increment, branch if not zero   LSR/LSLB   Logical shift eft A/B     PULX/PUL   Pull X/PU for stack   IBES/LBNE   Logical shift eft A/B   RCR   RCR   RCR   RCR     Tansfer A to B //B to A </td <td></td> <td></td> <td></td> <td></td> <td>-</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                                |           |                                  | -                 |                           |  |  |

| LEAXUEAY Load effective address X/Y<br>STAASTAB Store A/B<br>STD Store double D<br>STD Store double D<br>STD Store double D<br>STS Store stack pointer<br>STXSTY Store X/Y<br>PSHAPSHB Push A/B to stack<br>PSHX/PSHP Push A/B to stack<br>PSHX/PSHP Push X/Y to stack<br>IBRC Increment, branch if zero<br>PULX/PULP Pull A/B from stack<br>PULX/PULP PULP PULP PULP PULP PULP PULP PULP                                                                                                                                        |                            |                                |           | 0                                |                   | 0                         |  |  |

| STAARSTABStore A/BBRA/BRNBranch always/neverCOMACOMBCompare double DSTDStore double DBSRBRA/BRNBranch overflow set/clearCPDCompare double DSTX/STYStore K/YCALLCall subroutineCPDCompare A/BPSHA/PSHPPush A/B to stackDBEQDecrement, branch if rot zeroLogical shift left A/BPSHA/PSHYPush A/Dble D to stackDBEQDecrement, branch if rot zeroLogical shift left A/BPULA/PULAPull condition codes from stackIBNEIncrement, branch if rot zeroLSLALSLBLogical shift left alght A/BPULA/PULAPull double D from stackIBNEIncrement, branch if rot zeroLSRALSRBLogical shift left alght A/BPULA/PULAPull double D from stackIBNEIncrement, branch if rot zeroLSRALSRBLogical shift left alght A/BPULA/PULAPull A/P from stackIBNEIncrement, branch if rot zeroLSRALSRBLogical shift left alght A/BPULA/PULAPull A/P from stackIBNEIncrement, branch if rot zeroLSRALSRBLogical Shift left alght A/BTARTBATransfer A to B/B to AIBSC/ILBNELong branch if reary set/clearNEGA/NEGBNegate A/BTARTBATransfer to condition codesLBG2/LBNELong branch if fight/owNRCARDRBNotate left A/BTARTBATransfer A/BLBG2/LBNELong branch if rotro/rimeNCACARDLBNotate left A/BTARTBATransfer Add b to AAdd B to AAdd B to ANANegate A/B <td>-</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                          |                                |           |                                  |                   |                           |  |  |

| STDStore double DBVS/BVCBranch overflow set/clearCPDCompare double DSTSStore stack pointerBSRBranch to subroutineCPSCompare stack pointerSTX/STYStore X/YCALLCall subroutineCPX/CPYCompare stack pointerPSHAP/BSHBPush A/B to stackRTCReturn from CALLEDRAEORBExclusive-OR A/BPSHAPPush condition codes to stackDBNEDecrement, branch if zeroLSL/LSRLogical shift left/right memoryPSHAP/BSHPPulk A/B from stackIBNEIDECIncrement, branch if not zeroLSR/LSRLogical shift left/right memoryPULCPull condition codes from stackJSRJumpLSR/LSRLogical shift right A/BPULDPull double D from stackJSRJump to subroutineNEGNegate memoryPULTAPULYPull XY from stackERS/LBCCLong branch if zero/not zeroNRACORANegate memoryTAB/TBATransfer A to condition codes to ALBSC/LBCCLong branch if sers/greater, eq.ROL RAAORABRotate left A/BTSXTSYTransfer stack pointer to XYLBH/LBLDLong branch if ifgh/lowROARAORABRotate left A/BSKD/SYYTransfer double D with X/YLBH/LBLDLong branch if ifgh/lowROARAORABRotate left A/BSKD/SYYTransfer double D with X/YEXAlarge double D with X/YLBH/LBLDLBH/LBLDRota right/lowSKD/SYYStack apointer to X/YExcharge double D with X/YLBH/LBLDLBC/LBLELONg branch if ifg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                                |           |                                  |                   |                           |  |  |

| STS   Store stack pointer   BSR   Branch to subroutine   CPS   Compare stack pointer     STV/STY   Store X/Y   Call subroutine   Call subroutine   CPS   Compare stack pointer     PSHA/PSHB   Push A/B to stack   DBEQ   Decrement, branch if zero   EQALACS   Lagical shift left/right A/B     PSHA/PSHY   Push double D to stack   DBEQ   Decrement, branch if zero   Lagical shift left A/B     PULAPULC   Pull condition codes from stack   DME   Decrement, branch if zero   LSRALSR   Logical shift left A/B     PULAPULP   Pull A/P to stack   IBNE   Increment, branch if carry set/clar   Logical shift right A/B     PULAPULY   Pull A/P to condition codes from stack   JMP   Jump   LBRA   LBRA </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |                                |           |                                  |                   |                           |  |  |

| STX/STYStore X/YCALLCall subroutineCPX/CPYCompare X/YPSHA/PSHBPush A/B to stackRTCReturn from CALLDBFQDecrement, branch if zeroDBFQDegreat the the the the the the the the the th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                          |                                |           |                                  | -                 |                           |  |  |

| PSHAPSHBPush A/B to stackFTCReturn from CALLCALLCALLCALLCALLCall SV-COR A/BPSHCPush double D to stackDBRDecrement, branch if not zeroLS/LSRLogical shift left/right memoryPSHAPSHYPush X/Y to stackIBEQIncrement, branch if not zeroLS/LSRLogical shift left A/BPULAPULDPull aduble D from stackIBNEIncrement, branch if not zeroLS/LSRLogical shift left A/BPULAPULPPull double D from stackJMPJump to subroutineLSRALSRBLogical shift left A/BPULXPULPPull double D from stackJSRJump to subroutineLSRALSRBLogical shift left A/BPULXPULPPull Avit from stackRTSReturn from subroutineLSRALSRBLogical -OR A/BTAB/TBATransfer A to S/B to ALBGC/LBLELong branch if carry set/clearORACORBNegate memoryTSXTSYTransfer stack pointer to X/YLBH/LBLDLong branch if less/greater, eq.ROLAROLBROLAROLBROLAROLBXGDXXGDYExchange registersLBH/LBLDLong branch if high/lowSCALEROR Rotate right A/BXGDXXGDYExchange registersLBH/LBLDLong branch if high/low, samtSEC/CLCSet/clear carryAbd Ad b to AAdd to A/BINCIncrement A/BSEC/CLCSet/clear carryADA/ADDBAdd to A/BINCIncrement A/BSEC/CLCSet/clear carrySBASubract double DINXINYIncrement A/BSEC/CLCSet/clear carry<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                                | -         |                                  |                   |                           |  |  |

| PSHC Push condition codes to stack DBEQ Decrement, branch if zero LSL/LSR Logical shift left/right memory   PSHZ PSHZ Push X/Y to stack DBNE Decrement, branch if zero LSLALSL Logical shift left A/B   PULAPULB Pull A/B from stack IBNE Increment, branch if not zero LSRALSRB Logical shift left A/B   PULC Pull double D from stack JSR Jump LSRALSRB Logical shift left double D   PULT Pull X/Y from stack JSR Jump to subroutine NEG Negate memory   TAB/TBA Transfer A to B/B to A LBCS/LBC Long branch if carry set/clar ORAA/ORAB Logical shift left double D   TAB/TBA Transfer rodition codes to A LBC/LBNE Long branch if ferst/right/low NEG Negate A/B   TSX/TSY Transfer stack pointer to X/Y LBGT/LBLE Long branch if ferst/right/low ROLA/ROLB Rotate left A/B   XGDX/ROPY Exchange registers LBH/LBLO Long branch if high/low RORA/RORB Rotate left A/B   XGDX/ADDE Add b to A Add b to A RTI Return from interrupt Rotate left A/B   ADCA/ADDE Add to A/B INS Increment A/B Increment A/B SEV/CLC Set/clear oref10ow   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | Push A/B to stack              | RTC       | Return from CALL                 | EORA/EORB         |                           |  |  |

| PSH0 Push double D to stack DBNE Decrement, branch if not zero   PSHX/PSHY Push X/Y to stack IBEQ Increment, branch if not zero   PULAPULB Pull A/B from stack IBNE Increment, branch if not zero   PULC Pull condition codes from stack JMP Jump to subroutine   PULXPULY Pull X/Y from stack RTS Return from subroutine   PULXPULY Pull X/Y from stack RTS Return from subroutine   TAP Transfer A to B/B to A LBG2/LBNE Long branch if carry set/clear   TAF Transfer condition codes to A LBG2/LBNE Long branch if gergreater, eq.   TAF Transfer At to condition codes to A LBG7/LBLE Long branch if high/low, samt   SXSTXY Transfer At pointer to X/Y LBH/LBU Long branch if high/low, samt   SK Sign-extend 8 → 16 LBG7/LBLE Long branch if high/low, samt   SK Sign-extend 8 → 16 LBRA/LBNE Long branch if high/low, samt   ADCA/ADDB Add B to A Add B to A   ABA Add B to A Add B to A   ADCA/ADDB Add to A/B   ADDA Nuth (arry to A/B   ADDA/ADDB Subract accumulators   SBA Subract accumulators   SBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                                | -         |                                  |                   |                           |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PSHD                       |                                | DBNE      |                                  |                   |                           |  |  |

| PULAPULB<br>PULCPull A/B from stack<br>PULCIBNEIncrement, branch if not zero<br>JMPLSRALSRBLogical shift right A/B<br>Logical shift right double DPULDPull double D from stack<br>PULXPULYPull X/Y from stackIBNEJumpLSRDLogical shift right A/B<br>Logical shift right A/BPULXPULYPull X/Y from stack<br>TAB/TBATransfer A to B/B to A<br>LBEG/LBNELSRLSRDNEGA/NEGBNegate memoryTAB/TBATransfer A to condition codes<br>TFRTransfer condition codes to A<br>LBGT/LBLTLog branch if arro for zero<br>Log branch if fsetor/not zero<br>Log branch if fsetor/less than<br>LBGT/LBLTORA/ORABLogical-OR A/B<br>ORA/ORABNegate A/BTSXTSYTransfer stack pointer to X/Y<br>TXS/TXYTransfer stack pointer to X/Y<br>LBHS/LBLSLog branch if fight/low,<br>setorah if plus/minusRORRotate left A/B<br>RORRotate left A/BXGDXXGDYExchange registersLBH/LBLOLong branch if fuels/minusTSTTEst memoryXGDXXGDYExchange registersLBV/LBNLong branch if oranch if zero/not zero<br>RTIRORRotate left A/BABAAdd B to A<br>ABZ/ADDBAdd B to A<br>Add to A/BAdd B to A<br>Add to A/BNicellaneousSET/BCL Set/clear carry<br>SEC/CLCSet/clear carry<br>SEC/CLCSBCANSDCBSubract A/BINCA/INCBIncrement A/B<br>INCA/INCBSEV/CLYSet/clear overflow<br>SEC/CLSBCANSDCBSubract A/BDESDecrement A/B<br>INCA/INCBSITSEC/CLBSUBDSubract A/BDEXDESDecrement A/B<br>INCA/I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |                                |           |                                  |                   |                           |  |  |

| PULCPull condition codes from stackJMPJumpJumpPULXPull double D from stackJMRJJRJJRPULX/PULYPull double D from stackJSRJJRJump to subroutineTAB/TBATransfer A to B/B to ALBSC/LBCLong branch if carry set/clearORA/ORABLogical-OR A/BTAPTransfer register to registerLBSC/LBNELong branch if fess/greater, eq.NEGNEGA/NEGBORCCLogical-OR A/BTXS/TSYTransfer register to registerLBGF/LBLELong branch if fess/greater, eq.ROLRotate left A/BORCASGDX/SOYExchange double D with X/YEscAluserLBR/LBLSLong branch if high/low, sameRORRotate right memoryArithmeticExchange registersBRA/LBRNLong branch if overflw set/clearTSTTest memoryABX/ABYAdd B to AAdd b to X/YIncrement A/BTicrement A/BNiscellaneousADDA/ADDBAdd to A/BINCIncrement A/BSEt/CLCSet/clear carrySBCA/SBC8Subtract A/BDECDecrement A/BTBL/ETBLTable lookup and interpolateSUBDSubract A/BDESDecrement A/BTBL/ETBLTable lookup and interpolateSUBDSubract A/BMAXAMMaximum to ATRAPTable lookup and interpolateSUBDMultiply 16 × 16MAXAMaximum to ATRAPTest holesSUBDMultiply 16 × 16MAXAMaximum to ATRAPUnimplemented opcode trapMVLMult                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |                                | IBNE      |                                  | -                 |                           |  |  |

| PULD<br>PULD<br>PULL<br>PULX/PULY<br>PUIX/Y from stack<br>PUX.PULY<br>PUIX/Y from stack<br>PUX.PULY<br>PUIX/Y from stack<br>PUX.PULY<br>PUIX/Y from stack<br>TAB/TBA<br>Transfer A to B/B to A<br>TAB/TBA<br>Transfer A to B/B to A<br>TAB/TBA<br>Transfer a to B/B to A<br>TRASTER To condition codes to A<br>TSX/TSY<br>Transfer stack pointer to X/Y<br>TXS/TXY<br>Transfer stack pointer to X/Y<br>TXS/TXY<br>TRASTER stack pointer to X/Y<br>TXS/TXY<br>TRASTER stack pointer to X/Y<br>AGB to A<br>ABX/ABY<br>ADDA/ADDB<br>Add to A/B<br>ADDDA<br>ADDD<br>ADDD<br>ADDD<br>Add double D<br>SUBA/SUBB<br>Subract A/B<br>SUBA/SUBB<br>Subract A/B<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                |           |                                  |                   |                           |  |  |

| PULX/PULY<br>TAB/TBAPull X/Y from stack<br>Transfer A to B/B to A<br>Tarnsfer A to condition codesRTS<br>A<br>LBC/LBKReturn from suboutine<br>Long branch if carry set/clear<br>LBC/LBKNEGA/NEGBNEgate A/B<br>LORA/ORABTAP<br>Transfer A to condition codesLBCS/LBCCLong branch if carry set/clear<br>LBC/LBKORA/ORABLOgical-OR A/B<br>ORA/ORABTFR<br>Transfer register to register<br>TPA<br>Transfer stack pointer to X/YTransfer atack pointer to X/Y<br>LBH/LENILong branch if igreater/less than<br>por anch if high/low<br>LBH/LENIROR<br>Rotate left A/BRotate left memory<br>ROLA/ROLBSKDSVXGDY<br>Exchange double D<br>DDD<br>ADDA/ADDBAdd b to A<br>A<br>Add obuble DNetwork<br>LBPL/LBMILong branch if plus/minus<br>Test and branch if zero/not zero<br>RTINEGA/NOLBNotate left A/B<br>RORA/RORBABA<br>ADD/AADDBAdd b to A/Y<br>Add double DArithmetic (contt)Network<br>LBR/LRMINetwork<br>Long branch if zero/not zero<br>RTINEGA/RORBNetate left A/B<br>RORA/RORBADD/AADDB<br>Add double DAdd double DNC<br>Increment A/B<br>INS<br>Increment X/YNetwork<br>Increment A/B<br>Increment X/YSet/Clear overflow<br>SEV/CLVSUBD<br>Subract A/B<br>SUBA/SUBB<br>Subract A/BSubract A/B<br>Subract A/BNetwork A/B<br>DEC<br>Decrement A/B<br>DECDecrement A/B<br>Decrement X/YStop processing<br>TA/BMUL<br>MUL<br>MUL<br>Multiply 16 × 16<br>EMULSMultiply 16 × 16, signedMAXM<br>Maximum to A<br>MAXMMaximum to A<br>Maximum to D, 16-bitStop processing<br>TRAPFWULS<br>DIVIde 32 + 16, signedMiNM<br>EMAXMMaximum to memory, 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PULD                       | Pull double D from stack       | JSR       |                                  |                   |                           |  |  |

| TAB/TBA<br>TAPTransfer A to B/B to A<br>TAPLogSLECC<br>Transfer A to condition codesLog Scal-OR A/B<br>Logical-OR A/B<br>ORCCLogical-OR A/B<br>Logical-OR A/B<br>ORCCLogical-OR A/B<br>Logical-OR A/B<br>ORCCTFR<br>Transfer condition codes to A<br>TSX/TSYTransfer condition codes to A<br>TsX/TSYLBGE/LBLE<br>Transfer X/Y to stack pointer to X/Y<br>Transfer X/Y to stack pointer to X/Y<br>LBHX/LBLLog branch if greater/less than<br>LBGF/LBLT<br>LDG branch if high/low, same<br>por and if high/low, same<br>Decompt and if plas/InvROR A/ORAB<br>ROLAROLBRotate left A/B<br>ROR Rotate left A/BXGDX/XGDYExchange double D with X/Y<br>EXGEBF/LBLN<br>LBRA/LBRN<br>LBRA/LBRN<br>LBRA/LBRN<br>LDG branch if plas/InvNORRotate left A/B<br>RORARORB<br>RORARORB<br>Rotate left A/BABA<br>ADCA/ADCBAdd B to A<br>ABX/ABY<br>ADCA/ADCBAdd B to A<br>Add b to A/A<br>BDDA<br>Add to A/BNOCIncrement A/B<br>Increment A/BMiscellaneousADDA/ADDB<br>Add double DINS<br>Subract with carry fom A/B<br>SUBA/SUBBINCIncrement A/B<br>INC/INCBSEV/CLVSet/clear otering<br>SEV/CLVSBA<br>SUBA<br>SUBA<br>SUBASSubract A/B<br>Subract A/BDEC<br>Decrement A/B<br>DEC/DECPDecrement A/B<br>Decrement A/BClear A/B<br>SUB/DECSUBD<br>SUBA<br>SUBASSubract A/B<br>Subract A/BDEC/DECP<br>MAXA<br>MAXimum to A<br>MAXA<br>MAximum to AStoP<br>Adaimum to A<br>MAXimum to A<br>MAXimum to A<br>MAXimum to A<br>MAXimum to D, 16-bitORCA<br>DECFUV<br>DIvide 32 + 16Divide 32 + 16<br>EMAXDMiNM<br>Maximum to D, 16-bitFuzzy LogicFUNC<br>DIvide 32 + 16EMAXD <td>PULX/PULY</td> <td>Pull X/Y from stack</td> <td></td> <td></td> <td>NEGA/NEGB</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                         | PULX/PULY                  | Pull X/Y from stack            |           |                                  | NEGA/NEGB         |                           |  |  |

| TAPTransfer A to condition codesLBEQ/LBNELong branch if zero/not zeroORCCLogical-OR condition codes toTFRTransfer register to registerLBGE/LBLELong branch if ges/greater, eq.ROLRotate left memoryTXX/TSYTransfer X/Y to stack pointer to X/YLBGT/LBLTLong branch if high/low, sameRORRotate left A/BSEXSign-extend 8 > 16LBH/LBLOLong branch if high/low, sameRORARORBRotate right A/BSEXSign-extend 8 > 16LBRA/LBRNLong branch if pign/low, sameRORARORBRotate right A/BSEXSign-extend 8 > 16LBRA/LBRNLong branch if pign/low, sameRORARORBRotate right A/BABX/ABYAdd B to ATest and branch if zero/not zeroRTIReturn from interruptSET/BCLRSet/clear atryADDA/ADDBAdd with carry to A/BIncrement A/BIncrement A/BSEV/CLVSet/clear atryADDA/ADDBAdd to A/BINCIncrement A/BSEV/CLVSet/clear atrySBASubract double DINSIncrement A/BSEV/CLVSet/clear overflowBLA/SUBBSubract double DDECDecrement A/BSUVSUVSoftware interruptBAADecimal adjust ADEC/DECBDecrement A/BSUVSUP Stop processingBUBLSMultiply 16 × 16, signedMAXAMaximum to ASTOPStop processingFMULMultiply 16 × 16, signedMAXAMaximum to ANOPNO eperationFMUSDivide 32 + 16SMXMMa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ТАВ/ТВА                    | Transfer A to B/B to A         | LBCS/LBCC | Long branch if carry set/clear   | ORAA/ORAB         |                           |  |  |

| TFR<br>TPATransfer register to register<br>TPALBGE/LBLE<br>LGGT/LBLTLong branch if less/greater, eq.<br>LGGT/LBLTROLRotate left memory<br>Rotate left A/BTXS/TSYTransfer condition codes to A<br>TXS/TXYTransfer stack pointer to X/Y<br>Transfer X/Y to stack pointer<br>SEXLBGE/LBLE<br>LGGT/LBLTLong branch if high/low, same<br>LBHS/LBLSRORRotate right A/B<br>Rotate right A/BSEXSign-extend 8 → 16<br>EXGDX/XGDYExchange double D with X/Y<br>EXGDX/XGDYLBHS/LBLS<br>EXchange registersLOng branch if plus/minus<br>LBP/LBNI<br>LBRA/LBRN<br>LBRA/LBRN<br>LBRA/LBRN<br>LBV/LBNCLong branch if overflw set/clear<br>Test and branch if zero/not zero<br>RTIRORRotate right A/B<br>RORA/ROBArithmeticTBEQ/TBNE<br>TBC/TSTTest and branch if zero/not zero<br>RTIBSET/BCLRSet/clear carryABA<br>ADDA/ADDB<br>Add to A/BAdd to A/B<br>ADDA/ADDBNCA/INCB<br>NCAINCB<br>SUBAC subract with carry for A/B<br>SUBAC/SUBBIncrement A/B<br>INCAINCBSEV/CLVSet/clear overflow<br>SEC/LCSUBA<br>SUBACSubract A/B<br>Subract A/BDEC<br>DEC/DECBDecrement A/B<br>DEC/DECBStoftware interrupt<br>DEcrement X/YStoftware interrupt<br>WAX<br>MAximum to A<br>MAXMMaximum to A<br>Minimum to A<br>MINAStop processing<br>TRAPMUL<br>MUL<br>MULiply-16 × 16<br>EMAXDMiNA<br>Minimum to D, 16-bitMEMDetermine fuzzy membershipEMULS<br>DIVide 32 + 16EMAXDMaximum to memory<br>MINATBLFuzzy Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TAP                        | Transfer A to condition codes  |           |                                  |                   |                           |  |  |

| TPATransfer condition codes to ALBGT/LBLTLong branch if greater/less thanROLA/ROLBRotate left A/BTSX/TSYTransfer stack pointer to X/YLBHS/LBLSLong branch if high/lowRORRotate right memoryXS/TXYTransfer stack pointerSign-extend 8 → 16LBH/LBLOLong branch if high/low, sameRORRotate right A/BXGDX/XGDYExchange double D with X/YExchange registersLBH/LBLMLong branch if plus/minusROR/ARORBRotate right A/BArithmeticTBEO/TBNETest and branch if zero/not zeroTest and branch if zero/not zeroRTISEC/ALCSet/clear bits in memoryABAAdd B to AABAAdd B to X/YAithmetic (con't)Set/clear carrySEC/CLSet/clear carryADDA/ADDBAdd to A/BINCIncrement memoryINCA/INCBIncrement A/BADDA/ADDBAdd double DINSIncrement A/BCLRClear emorySUBA/SUBBSubract A/BDECDecrement A/KCLRClear emorySUBA/SUBBSubract A/BDECA/DECBDecrement A/KSUAMULMultiply 16 × 16, signedMAXAMaximum to memorySTOPStop processingEMULSMultiply 16 × 16, signedMINAMinimum to memory, 16-bitFuzzy LogicEDIVDivide 32 + 16EMAXMMaximum to memory, 16-bitMEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TFR                        | Transfer register to register  | LBGE/LBLE |                                  | ROL               |                           |  |  |

| TXS/TXY<br>SEX<br>Sign-extend $8 \rightarrow 16$<br>Sign-extend $8 \rightarrow 16$<br>LBHS/LBLS<br>LGRLBHS/LBLS<br>LOng branch if plus/minus<br>Long branch if plus/minus<br>LBRA/LBNI<br>LOng branch if plus/minus<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBNI<br>LBRA/LBNI<br>LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBRA/LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI<br>LBNI <b< td=""><td>TPA</td><td></td><td>LBGT/LBLT</td><td></td><td>ROLA/ROLB</td><td>,</td></b<> | TPA                        |                                | LBGT/LBLT |                                  | ROLA/ROLB         | ,                         |  |  |

| TXS/TXY<br>SEX<br>XGDX/XGDYTransfer X/Y to stack pointer<br>Sign-extend $8 \rightarrow 16$<br>XGDX/XGDYLBHS/LBLS<br>Exchange double D with X/Y<br>EXGLBHS/LBLS<br>LBHS/LBN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBRA/LBNN<br>LBNN<br>LBRA/LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBRA/LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN<br>LBNN                                                                                                                             | TSX/TSY                    | Transfer stack pointer to X/Y  | LBHI/LBLO | Long branch if high/low          | ROR               | Rotate right memory       |  |  |

| SEXSign-extend $8 \rightarrow 16$<br>Exchange double D with X/Y<br>EXGLBPL/LBMI<br>ERALABRNLong branch if plus/minus<br>Long branch if poerflw set/clear<br>Test and branch if zero/not zero<br>RTITSTTest memory<br>Test A/BArithmeticTSTTest A/BABAAdd B to A<br>ABX/ABYAdd B to X/YAdd B to X/YArithmetic (con't)BSET/BCLRSet/clear carry<br>SEC/CLCSet/clear carry overflow<br>SEC/CLCADDA/ADDBAdd to A/B<br>Add double DINCIncrement memory<br>INCA/INCBIncrement A/B<br>DECBit test A/BSUBA/SUBBSubract accumulators<br>SUBA/SUBBSubract A/B<br>DECA/DECBDecrement A/B<br>DECA/DECBTEL/TBLTable lookup and interpolate<br>SUBA/SUBBSUBDSubract A/B<br>DEX/DEYDecrement X/Y<br>DECA/DECBDecrement X/Y<br>Decrement X/YMaximum to A<br>Maximum to A<br>MAXAMaximum to A<br>Maximum to A<br>MAXAMaximum to A<br>Maximum to A<br>MAXAMaximum to A<br>Maximum to A<br>Minimum to A<br>MINAMinimum to memory<br>Minimum to A<br>Maximum to D, 16-bitStudy Curve<br>EMAXMMULDivide $32 + 16$ EMAXMMaximum to memory, 16-bitMeMDetermine fuzzy membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TXS/TXY                    | Transfer X/Y to stack pointer  | LBHS/LBLS | Long branch if high/low, same    | RORA/RORB         |                           |  |  |

| XGDX/XGDY<br>EXchange double D with X/Y<br>EXGLBRA/LBRN<br>EXG/TERC/TBEQ/TBNELong branch always/never<br>LBV/S/LBVC<br>TBEQ/TBNETSTA/TSTBTest A/BArithmeticABA<br>Add B to A<br>ABX/ABYAdd B to A<br>Add b to X/YLBRA/LBRN<br>LBV/S/LBVC<br>TBEQ/TBNELong branch always/never<br>Long branch if overflw set/clear<br>TBE and branch if overflw set/clear<br>Return from interruptTSTA/TSTBTest A/BABA<br>ABX/ABY<br>Add B to X/YAdd B to A<br>ABX/ADDB<br>Add to A/B<br>ADDA/ADDB<br>Add to A/BArithmetic (con't)BSET/BCLR<br>Set/clear bits in memory<br>SEC/CLCSet/clear arry<br>SEC/CLVADDA/ADDB<br>ADDA/ADDB<br>Add double DAdd double D<br>INSIncrement memory<br>INX/INYIncrement A/B<br>Increment X/YBITA/BITB<br>Bit test A/BSUBA/SUBB<br>SUBA/SUBB<br>SUBAA<br>DAA<br>Decimal adjust A<br>MUL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULL<br>MULtiply 16 × 16<br>EMACS<br>MULL<br>MULtiply-add 16 × 16 · 322<br>EDIVSDecomal adjust A<br>MAXM<br>MAXM<br>MAXM<br>MAXM<br>Maximum to memory<br>MAXM<br>Maximum to p, 16-bitTRAP<br>Maximum to memory<br>TRAPTable lookup and interpolate<br>SVMI<br>Stop processing<br>TRAPMINA<br>Minimum to memory<br>EMACS<br>EDIVSDivide $32 + 16$ , signedMAXM<br>EMAXM<br>Maximum to memory, 16-bitTest A/BMINA<br>Maximum to memory, 16-bitDetermine fuzzy membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SEX                        | Sign-extend $8 \rightarrow 16$ | LBPL/LBMI |                                  | TST               |                           |  |  |

| EXGExchange registersLBVS/LBVCLong branch if overflw set/clear<br>Test and branch if zero/not zero<br>Return from interruptMiscellaneousABAAdd B to A<br>ABX/ABYAdd B to X/YReturn from interruptBSET/BCLRSet/clear bits in memory<br>SEC/CLCADCA/ADCBAdd with carry to A/B<br>ADDA/ADDBAdd to A/BIncrement memory<br>INCA/INCBIncrement A/B<br>Increment X/YSEV/CLVSet/clear overflow<br>SEV/CLVBBASubract accumulatorsINSIncrement A/B<br>INSBITA/BITBBit test A/B<br>CLRSUBA/SUBBSubract A/B<br>SUBA/SUBBDECDecrement A/B<br>DECCLRClear A/B<br>SUBA/SUBBSUBDSubract A/B<br>DECDECDecrement A/B<br>DECA/DECBSUISoftware interruptMULMultiply 8 × 8 $\rightarrow$ 16<br>EMULSMAXMMaximum to A<br>Minimum to A<br>Minimum to A<br>MINAMaximum to memory<br>MINATRAPUnimplemented opcode trap<br>NOPFUUSDivide 32 $\div$ 16<br>EDIVSDivide 32 $\div$ 16, signedMAXMMaximum to memory, 16-bit<br>EMAXMMeXMeXMeX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XGDX/XGDY                  | Exchange double D with X/Y     | LBRA/LBRN | Long branch always/never         | TSTA/TSTB         | Test A/B                  |  |  |

| ArithmeticTBEQ/TBNE<br>RTITest and branch if zero/not zero<br>Return from interruptMiscentareousABAAdd B to A<br>ABX/ABYAdd B to X/YRtilReturn from interruptBSET/BCLRSet/clear bits in memory<br>SEC/CLCADCA/ADCBAdd with carry to A/B<br>ADDA/ADDBAdd to A/BINCIncrement memory<br>INCA/INCBSet/CLVSet/clear overflow<br>SEV/CLVADDAAdd double DINCIncrement A/B<br>INSIncrement X/YSet/CLRCLRClear memory<br>CLRA/CLRBSBCA/SBCBSubract accumulatorsINSIncrement X/YBITA/BITBBit test A/BSUBA/SUBBSubract A/B<br>DECA/DECBDECDecrement A/B<br>DECA/DECBSWISoftware interruptDAADecimal adjust A<br>MULMultiply $8 \times 8 \rightarrow 16$<br>EMULMAXAMaximum to A<br>Minimum to A<br>MAXAStop processing<br>MAXMTRAPEMULMultiply $16 \times 16$ , signedMINA<br>EMAXDMinimum to D, $16$ -bit<br>EMAXDMAXMMaximum to memory<br>Maximum to memoryTRAPEDIVSDivide $32 \div 16$ , signedEMAXMMaximum to memory, $16$ -bitMEMDetermine fuzzy membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EXG                        | Exchange registers             | LBVS/LBVC | Long branch if overflw set/clear | Miscellaneous     |                           |  |  |

| ABAAdd B to AAdd B to AAdd B to AAdd B to X/YBSET/BCLRSet/clear bits in memoryABX/ABYAdd B to X/YAdd B to X/YAdd B to X/YSEC/CLCSet/clear carrySEC/CLCADCA/ADCBAdd with carry to A/BINCIncrement memorySEV/CLVSet/clear overflowADDDAdd double DINCIncrement A/BBITA/BITBBit test A/BADDDAdd double DINSIncrement stack pointerCLRClear memorySBASubract accumulatorsINX/INYIncrement X/YCLRA/CLRBClear A/BSUBA/SUBBSubract with carry from A/BDECDecrement A/BSWISoftware interruptSUBDSubract double DDESDecrement A/BSWISoftware interruptDAADecimal adjust ADEX/DEYDecrement X/YBGNDEnter background debugMULMultiply 8 × 8 $\rightarrow$ 16MAXAMaximum to ASTOPStop processingEMULMultiply 16 $\times$ 16, signedMINAMinimum to memoryTRAPUnimplemented opcode trapEMVLSDivide 32 $\div$ 16EMAXMMaximum to D, 16-bitFuzzy LogicEDIVSDivide 32 $\div$ 16, signedEMAXMMaximum to memory, 16-bitMEMDetermine fuzzy membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Arithmetic                 |                                | TBEQ/TBNE |                                  | Miscellaneous     |                           |  |  |

| ABX/ABYAdd B to X/YArithmetic (cont)SEI/CLISet/clear interrupt maskADCA/ADCBAdd with carry to A/BIncrement memoryIncrement memorySEI/CLISet/clear interrupt maskADDA/ADDBAdd to A/BIncrement A/BIncrement A/BSEV/CLVSet/clear overflowADDDAdd double DINCA/INCBIncrement stack pointerINCA/INCBBITA/BITBBit test A/BSBASubract accumulatorsINX/INYIncrement X/YCLRA/CLRBClear memorySBA/SUBBSubract A/BDECDecrement A/BDEC//DECBCLRA/CLRBClear A/BSUBDSubract double DDESDecrement A/BSWISoftware interruptDAADecimal adjust ADEX/DEYDecrement X/YBGNDEnter background debugMULMultiply $8 \times 8 \rightarrow 16$ MAXAMaximum to ASTOPStop processingEMULMultiply $16 \times 16$ MAXMMaximum to memoryTRAPUnimplemented opcode trapEMULSMultiply $-add 16 \times 16 \rightarrow 32$ EMAXDMaximum to D, 16-bitFuzzy LogicEDIVSDivide $32 + 16$ EMAXMMaximum to memory, 16-bitMEMDetermine fuzzy membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                | RTI       | Return from interrupt            |                   | ,                         |  |  |

| ABX/ABYAdd b to X/YSEV/Cl1Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/Cl21Set/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | Arithmetic (con't)             |           | n't)                             |                   |                           |  |  |

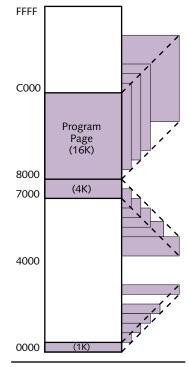

| ADDA/ADDBAdd to A/BINCA/INCBIncrement A/BBITA/BITBBit test A/BADDDAdd double DINSIncrement stack pointerCLRClear memorySBASubract accumulatorsINX/INYIncrement X/YCLRA/CLRBClear A/BSBCA/SBCBSubtract with carry from A/BDECDecrement memoryTBL/ETBLTable lookup and interpolateSUBA/SUBBSubract A/BDECDecrement stack pointerSWISoftware interruptDAADecimal adjust ADEX/DEYDecrement X/YBGNDEnter background debugMULMultiply 8 × 8 → 16MAXAMaximum to ASTOPStop processingEMULMultiply 16 × 16MAXAMaximum to ANOPNo operationEMULSMultiply-add 16 × 16 → 32EMAXDMaximum to D, 16-bitFuzzy LogicEDIVSDivide 32 ÷ 16EMAXMMaximum to memory, 16-bitMEMDetermine fuzzy membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                                |           | •                                |                   |                           |  |  |