THE INSIDERS' GUIDE TO MICROPROCESSOR HARDWARE

# Chromatic's Mpact 2 Boosts 3D

Mpact/3000 Becomes First Media Processor to Ship in Volume

by Yong Yao

Even as manufacturing partners LG Semicon and Toshiba are beginning volume shipments of the first media processor, Mpact/3000,

Chromatic has disclosed its forthcoming Mpact 2 design. Announced at last month's Microprocessor Forum, Mpact 2 (code-named M2) is expected to double the overall performance of Mpact/3000 (code-named M1). The gain is much greater on 3D graphics, as new floating-point capabilities position Mpact 2 to meet the 3D-performance requirement for mainstream PCs in 1998.

The performance gains stem mainly from a doubling of internal clock speed, an additional Rambus channel, the addition of floating-point capability, and a new 3D rendering engine. Other enhancements, such as doubling the onchip cache and supporting 66-MHz PCI, also contribute to the improved performance.

One of the biggest competitive advantages that Chromatic has over other media-processor vendors is the richness

of its software offerings. The recent release of the Mpact software, Mediaware Release 1.0, contains 2D/3D graphics, MPEG-1 audio/video decoding, FM/wavetable synthesis, V.34 modem, and full-duplex speakerphone. We expect future revisions of Mediaware to enhance these functions and also add functions such as DVD playback, video editing, and videoconferencing.

Chromatic expects Mpact 2 to be in PCs for the 1997 holiday season. We believe the technical success of Mpact/3000 makes this goal achievable. The company intends to position Mpact 2 at the high end while Mpact/3000 covers the low end. Whether the PC market will accept that positioning remains to be seen, because Mpact/3000 may not have enough performance by the time Mpact 2 is in production.

#### Mpact 2 Doubles Mpact/3000 Performance

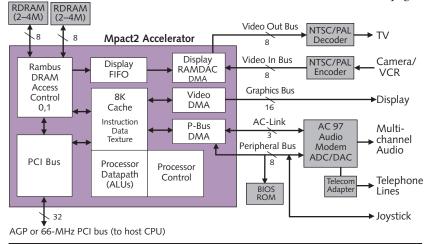

Doubling performance every 12 months is Chromatic's plan for keeping ahead of Intel's processor advances. To meet this goal for Mpact 2, Chromatic will increase the internal clock speed from 62.5 MHz in Mpact/3000 to 125 MHz or higher, replace 4K of cache with 8K, and add a second Rambus channel to reach 1,200 Mbytes/s of total memory bandwidth. The chip supports 300-MHz RDRAMs with an effective transfer rate of 600 MHz. Figure 1 shows the internal block diagram of Mpact 2, which is similar to that of the original Mpact/3000 (see MPR 10/23/95, p. 23).

The faster clock speed is achieved by using a 0.35-micron CMOS process, optimizing critical paths, and decoupling the internal clock from the Rambus interface clock. Unlike its predecessor, the Mpact 2 processor core can run asynchronously from the RDRAM, which provides the freedom to choose the RDRAM and internal clock speeds independently. One drawback to the asynchronous design is additional latency, due to clock synchronization, when accessing RDRAM.

Continued on page 6

**Figure 1.** Mpact 2 doubles performance over Mpact 1 by increasing the internal clock speed, doubling the amount of on-chip cache, adding a second Rambus channel, and doubling the speed of the PCI bus. A multimedia subsystem requires few extra chips.

Inside: TurboSparc > Fujitsu MMA > Piccolo > 603q > MDMX/MVI

#### AT A GLANCE

| Chromatic's Mpact 2 Boosts 3D.  Chromatic's Mpact/3000 recently became the first media processor to reach volume production. The company is also shipping a full set of software for the new chip. The next-generation device, Mpact 2, doubles the performance of the first part while offering an even bigger gain on 3D graphics due to new floating-point capabilities. Mpact 2 is due to be in systems for Christmas 1997. | . 1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Editorial: Clouds Darken Over RISC                                                                                                                                                                                                                                                                                                                                                                                              | . 3 |

| Most Significant Bits  Intel's Katmai, Willamette surface; New MicroUnity chip for cable modems; Newton first design win for StrongArm; Oak describes single-chip DVD decoder; TriTech debuts highly integrated 3D accelerator; S3 upgrades popular 3D accelerator; VLSI SongBird leads audio migration to PCI; Motorola 68376 flies as TouCan.                                                                                 | . 4 |

| Fujitsu Aims Media Processor at DVD  Eschewing PC applications, Fujitsu has developed a relatively simple media processor aimed at video players. The 185-MHz MMA processor uses an LIW design to execute two instructions per cycle. The chip contains 16K of on-chip SRAM and various system logic, reducing the cost of a consumer device.                                                                                   | 11  |

| TurboSparc Offers Low-End Upgrade                                                                                                                                                                                                                                                                                                                                                                                               | 14  |

| ARM Tunes Piccolo for DSP Performance                                                                                                                                                                                                                                                                                                                                                                                           | 17  |

| Digital, MIPS Add Multimedia Extensions                                                                                                                                                                                                                                                                                                                                                                                         | 24  |

| Recent IC Announcements                                                                                                                                                                                                                                                                                                                                                                                                         | 29  |

| Patent Watch                                                                                                                                                                                                                                                                                                                                                                                                                    | 30  |

| Chart Watch                                                                                                                                                                                                                                                                                                                                                                                                                     | 31  |

| Resources                                                                                                                                                                                                                                                                                                                                                                                                                       | 32  |

## MICROPROCESSOR REPORT

#### **Publisher and Editorial Director**

Michael Slater E-mail: mslater@mdr.zd.com

#### **Editor in Chief**

Linley Gwennap E-mail: linley@mdr.zd.com

#### Senior Editor

Jim Turley E-mail: jturley@mdr.zd.com

#### Senior Analyst

Yong Yao E-mail: yyao@mdr.zd.com

#### Senior Analyst

Peter N. Glaskowsky E-mail: png@mdr.zd.com

Editorial Assistant: Kathy Acuff

#### **Editorial Board**

Dennis Allison Rich Belgard

Brian Case Jeff Deutsch

Dave Epstein Don Gaubatz

John Novitsky Bernard Peuto

Nick Tredennick John F. Wakerly

#### **Editorial Office**

298 S. Sunnyvale Avenue Sunnyvale, CA 94086-6245 **Phone:** 408.328.3900 **Fax:** 408.737.2242

Microprocessor Report is published every three weeks, 17 issues per year. Rates are: N. America: \$495 per year, \$895 for two years. Europe: £375 per year, £645 for two years. Elsewhere: \$595 per year, \$1,095 for two years. Additional copies in the same envelope: \$175 per year in North America, \$225 elsewhere. Back issues are available.

### Published by

**President:** Peter Christy E-mail: pchristy@mdr.zd.com

#### **Business Office**

874 Gravenstein Hwy. So., Suite 14 Sebastopol, CA 95472 **Phone:** 707.824.4004 **Fax:** 707.823.0504

> Subscriptions: 707.824.4001 E-mail: cs@mdr.zd.com

World Wide Web: www.chipanalyst.com

Copyright ©1996, MicroDesign Resources. All rights reserved. No part of this newsletter may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without prior written permission.

Winner, Computer Press Award, 1993, 1994

Printed on recycled paper with soy ink.

# Clouds Darken Over RISC

### Some Will Perish After Introduction of Intel/HP Architecture

RISC processors, unless they're home grown, are becoming less and less interesting to system vendors. NEC's rejection of MIPS chips for its systems (see MPR 10/28/96, p. 5) is another sign of the times; the Japanese company is nominally switching to HP's PA-RISC, but the real destination is the future Intel/HP architecture, IA-64. As IA-64 becomes a reality, we expect other vendors to follow NEC's lead. Ultimately, this trend could result in one or more RISC processor vendors giving up on their architectures.

Nearly every major computer company today is either building systems around x86 chips or using its own in-house RISC processor (or both). Apple, of course, gets its processors from IBM and Motorola, but the Mac vendor's involvement in PowerPC is so intimate that it hardly counts as an exception to this rule. Fujitsu is a staunch SPARC system vendor but consumes many processors from its Ross and Hal subsidiaries. Otherwise, the largest computer vendors making significant use of an externally produced RISC processor are Tandem and Pyramid, midsize players at best.

This situation leaves Digital, HP, Silicon Graphics, and Sun with so-called MORPs: my own RISC processor. The volume of chips such as the 21164, PA-8000, or R10000 is truly miniscule, a few tens of thousands per year. Under the old business model, high-end processors like the R4000 would eventually migrate into low-cost systems, pumping up their lifetime volume. In today's competitive market, recycled high-end chips are no longer adequate for the low end; instead, vendors are designing price/performance products like the R5000 and the PA-7300LC, preventing high-end chips from ever reaching volume price points.

If high volumes are never attained, conventional economics says the cost of developing a beast like the R10000's follow-on must be spread across the miniscule volume of parts ultimately produced, resulting in a huge surcharge per chip. The RISC vendors claim the revenue from their systems is more than enough to cover this cost. Each of the MORP vendors collects several billion dollars per year in RISC system revenue. The cost of maintaining a couple of hundred processor designers is perhaps 1% of that revenue.

These vendors are willing to bear this cost because they gain a competitive advantage: better performance, particularly on floating-point applications, than mass-market processors can provide. Furthermore, the costs of moving their user base to a new architecture are daunting, even if that architecture would eliminate the need for internal CPU development. Thus, no vendor has followed HP's lead in terminating its RISC architecture.

That may change in a few years, however. Today's outof-order RISC processors are overburdened with the very complexity that RISC was intended to eliminate. Too little of the chip is doing real work; the rest is devoted to keeping two sets of books, in case the software ever conducts an audit to find out what the CPU has really been up to. While it is certainly possible to work with a balky architecture (witness the success of x86), the performance growth rate of RISC architectures will be difficult to maintain.

HP, with Intel's help, aims to solve this problem by moving to IA-64, a clean new architecture that we believe will push much of this complexity back into the compiler, boosting performance by devoting more of the chip to instruction execution. Because of this leap forward, we expect Merced, the first IA-64 processor, to outperform all traditional RISC processors. HP will solve the migration problem by offering compatibility with PA-RISC, probably through some sort of translation/emulation scheme.

Other RISC vendors will then be faced with some difficult choices. Staying with current instruction sets will probably put them at a performance disadvantage to IA-64. To close this gap, they could develop a new instruction set along the lines of IA-64, but such a massive development effort, as well as moving customers to that instruction set, will be more expensive than maintaining the existing product line.

Once the thought of a new instruction set is on the table, another option is to simply adopt IA-64. This move eliminates the cost of in-house development while ensuring performance competitiveness. If buying processors from Intel is unthinkable, vendors could instead band together to develop a competitive instruction set, sharing the development costs and building more volume for the new design.

SGI can easily differentiate its products on the basis of 3D performance, regardless of the underlying CPU; the company is a good candidate to switch to IA-64 or Project 2K, a new instruction set under development by the PowerPC vendors (see MPR 8/26/96, p. 12). It is less clear how Sun or Digital would differentiate their products from those of other IA-64 vendors. Digital seems likely to stick with Alpha until the bitter end, which, given the company's recent return to unprofitability, may be sooner than later. Sun may stay with SPARC or join an anti-Intel alliance. Efforts to rival IA-64, however, are already two years behind; so far, this delay is probably not fatal, but the clock is ticking for these vendors.

Linley Owening

#### Intel's Katmai, Willamette Surface

Intel's river map rolls onward. Rumors have recently surfaced regarding two new processors planned for 1998. Sources indicate Intel is working on a processor code-named Katmai that will be a minor improvement on Deschutes. (Katmai, pronounced KAT-mye, is named after a river in Alaska; Intel has apparently moved beyond Oregon and California in its naming conventions.)

The key to Katmai appears to be the addition of new MMX instructions, forming a set referred to as MMX 2. No word yet on what the new instructions are, but they may address 3D geometry performance, which MMX does not. One possible addition would be dual floating-point operations similar to those in MIPS V (see page 24). Katmai is said to be planned for a 1H98 debut, about six months after Deschutes first appears.

We believe Intel is moving aggressively to improve the multimedia performance of its processors, particularly for 3D graphics, which is weak today. These moves will both drive another PC upgrade cycle and protect against a significant incursion from media processors (see MPR 10/7/96, p. 3). MMX, as originally announced, is just the first step, and subsequent Intel processors will offer continued improvement.

For the second half of 1998, Intel is preparing a much more significant upgrade, a chip code-named Willamette ("Wil-LAM-ette") after the Oregon river. This device, which we previously called the P68 (see MPR 3/5/96, p. 3), is expected to be based on the P6 core but with significant performance enhancements, perhaps including a larger reorder buffer and an additional integer unit. Willamette will presumably carry forward the MMX 2 enhancements from Katmai. As a result of these changes, we expect Willamette to deliver 30–50% better integer performance per clock cycle than Deschutes and perhaps a bigger improvement on 3D graphics and some other multimedia applications.

Intel is also said to be working on a 100-MHz version of the P6 bus, which is today limited to 66 MHz. The current speed is adequate for systems with four 200-MHz Pentium Pro processors using 512K caches and is likely to support four 300-MHz Deschutes processors if they are each coupled with around 2M of cache. A four-way Willamette server, however, will overwhelm the 66-MHz bus. Even a one-or two-CPU desktop system may need the faster bus for Willamette, since these systems will probably stick with 512K of cache. We expect Intel will support the faster bus speed as an option for Willamette, and possibly for Katmai as well.

Willamette's main role is to fill in the x86 line underneath Merced, the first IA-64 processor. We expect Willamette, along with a subsequent shrink version, will be Intel's mainstream processor throughout 1999 and 2000, giving Merced plenty of time to gain software and system support while easing into the market. —*L.G.*

#### New MicroUnity Chip for Cable Modems

At last month's Microprocessor Forum, MicroUnity's Craig Hansen revealed the first fruit of the company's strategic repositioning (see MPR 8/5/96, p. 5). To replace its highpower BiCMOS chip designed for generalized signal processing, the company has developed a low-power CMOS device tuned for cable modems. The new device retains the instruction set and much of the microarchitecture of the BiCMOS chip but makes several changes to reduce power consumption.

The first change, of course, is from BiCMOS to CMOS. The original processor ran at 1 GHz; because bipolar circuits consume power whether they are switching or not, it makes sense to switch them as fast and as much as possible. This factor led to the idea of a multithreaded design that switches from one instruction stream to the next on every cycle, overlapping five threads at once.

In a CMOS process, this architecture burns far too much power: a prototype multithreaded CMOS processor was measured at 60 W despite clocking at only 200 MHz. The new chip is a traditional single-threaded design running at 113 MHz. Although the peak performance of this design is obviously greatly reduced, the throughput of a single thread is similar to that of the BiCMOS design, which ran each thread at 200 MHz but encountered greater memory latencies relative to the cycle time.

The new media processor, built in 0.35-micron four-layer-metal CMOS, runs at 3.3 V and consumes just 4 W (maximum) at 113 MHz. Although it has five million transistors, about three million are in the 64K of on-chip cache, and the die size is just 100 mm<sup>2</sup>. It retains enough performance to handle various modulation algorithms (such as QAM, DMT, and CDMA), 802.2 bridging, and higher-level services for a cable modem.

An entire cable modem could be built from just the MicroUnity media processor and its associated media codec, 512K of DRAM, 128K of flash, a tuner for the cable input, and an Ethernet connection to the PC. The media codec provides a PCI interface, allowing the use of commodity Ethernet chips. An optional telephone modem can be added through the PCI interface as well.

By leveraging its original media processor design, the company has quickly created a new design, although prototypes have yet to be built. MicroUnity is now seeking a semiconductor partner to fabricate and market the device. With low power consumption and a small die size, the new design is much better suited to the market needs of cable modems and set-top boxes than the original BiCMOS monster. Whether the new device can save MicroUnity from extinction depends on how quickly the market for cable modems increases from its current near-zero state and whether the company has any other irons in the fire. —L.G.

#### Newton First Design Win for StrongArm

Digital's StrongArm has made its first public appearance in the form of Apple's newest Newton. As we predicted (see MPR 2/12/96, p. 1), the SA-110 forms the heart of the new Apple MessagePad 2000, which Apple claims runs "up to 10 times faster than any previous model" of Newton; in fact, the 162-MHz StrongArm chip is rated at 185 MIPS, compared with 18 MIPS for the ARM610 used in previous models. Other than the new CPU, the 2000 is similar to earlier Newtons. Apple expects to ship the new model in 1Q97.

The nominal 160-MHz StrongArm was chosen because its power consumption, at 1.65/3.3 V, most closely matched that of the earlier Newton's 5-V ARM610. The handheld unit is based on a commercial processor, like previous Newtons, and a set of four ASICs built by Cirrus. The 2000 also contains 8M of ROM, 4M of flash memory, and 1M of DRAM. Power is provided by four AA batteries; Apple advertises three to six weeks of useful battery life.

The new unit comes with the usual assortment of productivity applications plus a Web browser and software (with cables) for communicating with desktop Macintoshes and PCs—a notorious shortcoming of previous Newtons. Apple also claims vastly improved handwriting recognition, thanks mostly to the faster processor.

In addition to appearing in the 2000, StrongArm will be at the heart of Apple's licensed Newton reference platforms. Inexplicably, the portable eMate 300, which Apple rolled out on the same day, uses an ARM710 processor.

Digital can now trumpet its first design win for Strong-Arm, one that has the potential to outstrip total Alpha sales in a very short time. The company has publicly demonstrated network computers and other devices based on StrongArm, but no other customers are willing to identify themselves at this time.

Apple's decision to announce the Newton 2000 months before it is available is widely seen as a pre-emptive strike against a spate of Windows CE announcements this week. The new Newton is expected to be more expensive—perhaps by a factor of two—than the WinCE units, so Apple will again have to convince buyers that Newton's features are worth the price premium. —*J.T.*

#### Oak Describes Single-Chip DVD Decoder

At last month's Microprocessor Forum, Oak Technology (www.oaktech.com) previewed a possible future product for DVD players and similar consumer devices: a single chip combining a new 32-bit RISC processor core with multiple blocks of fixed-function logic.

The new architecture takes a different tack than other programmable multimedia processors like Chromatic's Mpact 2 (see cover story). Instead of using a high-performance processor core to execute multimedia functions directly, the design performs the bulk of these functions in hardwired logic, relying on a fairly simple CPU core to manage the flow of data among the various logic blocks.

Hardwired functions include an MPEG-2 transport stream parser, MPEG-2 video and audio decoders, a Dolby Digital AC-3 audio decoder, and a complete digital-video back end for letterbox and pan-and-scan support.

The programmable RISC engine described by Oak's Wen Hsu consists of a simple 32-bit scalar CPU core with 64 32-bit registers, supporting 32K of instruction space and 1K of data. It operates at 67.5 MHz with a three-stage pipeline. Because of the short pipeline, Hsu claims there is no penalty for any type of branch operation, load, or store.

The chip would connect directly to 2M of SDRAM, an audio DAC, an analog video encoder, an 8/16-bit host CPU, and the DVD drive's controller chip. No other significant components would be needed to make a complete DVD player. This system would cost less than a player based on a set of discrete MPEG-2 audio and video decoder chips.

Oak says that such a chip could be fabricated in 0.35-micron CMOS, operating from a 3.3-V supply with 5-V-tolerant I/O, and packaged in a 160-pin PQFP. No specific product plans were disclosed, however.

Media processors from Samsung and Philips can also be used in DVD players, but the higher performance and floating-point support in these parts is likely to make them too expensive for this application. Like Oak, Fujitsu has targeted the DVD market for its MMA chip (see page 11), which was announced at the Forum. MMA's more flexible design may make it easier to adapt to the evolving DVD standard, but Oak's simpler design may be less expensive. Given Oak's unwillingness to discuss an actual product, it appears Fujitsu will reach the market first. —*P.N.G.*

#### ■ TriTech Debuts Highly Integrated 3D Accelerator

The TR25201 3D graphics controller, part of TriTech's new Pyramid3D product family, is the first 3D chip for the personal-computer market to include integrated hardware support for geometry, setup, and rendering in a single device. This combination lets the device offload from the host processor all parts of the 3D pipeline except scene definition.

The result is high-performance and high-quality rendering. TriTech rates the TR25201 at 1M triangles/s (for 25-pixel shaded, textured, fogged, and Z-buffered triangles). The part also provides hardware support for radiosity-based lighting, trilinear MIP-mapped and bump-mapped textures, Phong shading, and complex shading effects such as environment mapping. A PCI interface and integrated 200-MHz RAMDAC are also included, supporting  $1,600 \times 1,200$  resolution.

Microsoft's Direct3D API does not yet allow application developers to take advantage of all the features of Pyramid3D. TriTech is working directly with several ISVs to develop targeted software and with Microsoft to extend Direct3D. Even within the current constraints of Direct3D, the TR25201 is said to offer faster rendering than the other 3D chips in its price range.

Continued on page 21

#### **Chromatic Mpact 2**

Continued from page 1

Simply doubling clock speed would not double the overall performance if there were not enough data to feed the engine. Mpact 2 satisfies this need by doubling the external memory bandwidth as well as the amount of on-chip cache. By simply adding a second Rambus channel, Chromatic doubles the memory bandwidth while adding only eight data pins to the package.

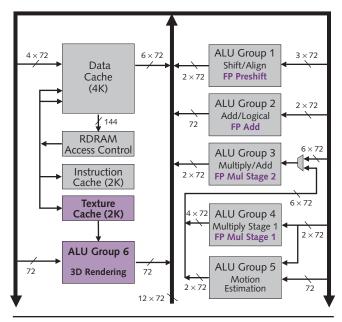

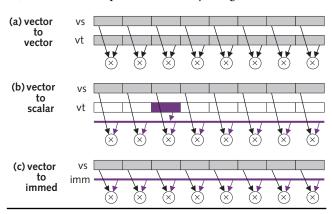

As Figure 2 shows, the new cache is divided among a 2K instruction cache, a 2K texture cache, and a 4K data cache. The data cache has six read ports and six write ports. In the first-generation Mpact design, there is no dedicated cache for textures, and the single 4K cache holds both data and instructions with only four read ports and four write ports.

In addition to PCI and other standard hardware interfaces supported by Mpact 1, the new chip adds support for Intel's AC '97. The AC '97 interface (see MPR 7/8/96, p. 4) allows Mpact 2 to use any off-the-shelf AC '97-compliant audio codec, reducing the cost of the audio subsystem.

The PCI interface has been modified to operate at 66 MHz, twice the frequency of the standard PCI bus. This higher speed enables Mpact 2 to store textures in main memory and increases bandwidth to the rest of the system. Few chip sets exist today to drive a 66-MHz PCI bus, so Mpact 2 will operate the bus at 33 MHz if necessary.

By the time Mpact 2 appears, however, chip sets that support the AGP interface (see MPR 6/17/96, p. 11) should be appearing. These chip sets will connect to Mpact 2 using

Figure 2. Mpact 2's internal data paths are all 72 bits wide, with a 792-bit crossbar carrying 11 results back to all six ALU groups and to the on-chip caches. Changes from the previous design are highlighted in purple. ALU groups 1-4, for example, are modified to support FP operations.

66-MHz PCI. For this reason, Chromatic describes its chip as AGP-compliant. The initial Mpact 2, however, does not support any of the advanced features of AGP, such as dual clocking and split transactions.

Mpact 2 integrates a 220-MHz RAMDAC on chip. The high-speed DAC supports displays up to  $1,600 \times 1,200 \times 18$ with a refresh rate of up to 85 Hz.

#### Mpact 2 Adds Floating-Point Capability

Because Mpact/3000 lacks floating-point capability, the chip's biggest weakness is 3D graphics. Without strong 3D performance, a PC media processor cannot succeed in the long run. At the Forum, architect Stephen Purcell said that improving 3D graphics performance was a major design goal for Mpact 2.

The key to 3D geometry processing is floating-point performance. Instead of adding a separate floating-point unit, Chromatic modified the four general-purpose ALU groups to perform FP operations, as Figure 2 shows. This change has made a minimal impact on die size. All FP operations are performed in single-precision mode, since 3D graphics for a PC rarely use double-precision. To take advantage of the 72-bit data paths, each ALU in Mpact 2 performs two single-precision operations in parallel. This method is similar to the paired-single format in the MIPS V instruction set (see page 24).

To perform a floating-point add or subtract, the operands are first sent to ALU Group 1, which performs a preshift operation to correctly align the operands. This operation uses the existing shifter in that ALU. Using the crossbar, the operands then move to ALU Group 2, which performs the actual add operation. Thus, FP addition is fully pipelined with a latency of two cycles. Similarly, for floating-point multiplication, the operands are first sent to ALU Group 4, then the multiplication is completed in ALU Group 3 on the following cycle. Again, FP multiplication is fully pipelined with a latency of two cycles.

| 3 stages  | Input polygon                                            |

|-----------|----------------------------------------------------------|

| 3 stages  | Generate spans from polygon                              |

| 3 stages  | Generate pixels from spans                               |

| 10 stages | Apply perspective (divide step) to pixels                |

| 3 stages  | Generate texture address and present to texture cache    |

| 2 stages  | Access texture cache and format texel                    |

| 2 stages  | Apply filters                                            |

| 2 stages  | Blend/modulate pixel/texel; diffusion, specular lighting |

| 2 stages  | Apply fog effect                                         |

| 5 stages  | Cluster final pixels                                     |

Figure 3. The 3D-rendering pipeline in the Mpact 2 consists of 35 stages, broken down as shown. Such a long pipeline is not a problem for 3D rendering because there are no pipeline hazards.

Each cycle, a pair of single-precision FP adds can be launched along with a pair of single-precision FP multiplies. At 125 MHz, the peak performance of the Mpact 2 design is thus 500 MFLOPS.

Chromatic added about 30% more instructions to the original Mpact instruction set, many specifically for the new floating-point capability and the 3D graphics unit. Unlike on the integer side, there is no direct support for FP multiplyaccumulate; this operation is synthesized from a multiply and an add with a total latency of four cycles. There is also no FP divide instruction; this operation can be synthesized by a sequence of multiplies and adds.

#### New 3D Unit Speeds Rendering

Even the strong performance of the general-purpose Mpact engine is inadequate for high-speed 3D rendering. Chromatic's design philosophy is to use the programmable engine for general processing and for algorithms that may change, but specific hardware may be required to accelerate fixed algorithms. This philosophy led to the addition of a hardwired motion estimator (ALU Group 5 in Figure 2) in the original Mpact and, in Mpact 2, a new 3D rendering unit.

The 3D unit, ALU Group 6, contains a 35-stage pipeline that runs concurrently with instruction execution. Since 3D graphics operations don't contain any pipeline hazards such as data dependencies or mispredicted branches, the long pipeline provides high throughput without reducing performance. Figure 3 shows this 3D rendering pipeline.

Other hardware improvements also aid Mpact 2 in 3D graphics. The addition of the 66-MHz PCI bus, the dedicated texture cache, and the wider path to external memory all improve 3D rendering performance.

One of the advantages that Mpact 2 has is its flexibility in allocating 3D tasks. The media processor can handle geometry, setup, and rasterization, or let the host processor take over geometry and/or setup. If triangle setup is performed in Mpact, it will be done in firmware using floatingpoint operations. Chromatic claims Mpact 2 can achieve one million triangles per second with 50-pixel triangles, Gouraud shading, 18-bit Z depth, perspective-correct textures, bilinear filtering, alpha blending, and fog. If delivered, this performance would put Mpact 2 right in the mainstream for PC 3D in 1998.

Although Mpact 2 is not a part of Microsoft's Talisman reference platform (see MPR 8/26/96, p. 5), some of Talisman's features have been incorporated into the Mpact 2 hardware. According to Chromatic, features included are chunking, image and texture compression, and affine transformations. Like Talisman, Mpact can also choose to render particular objects below the frame rate but composite them at the full frame rate. These features may help Mpact 2 support Talisman-enabled 3D games and perhaps become an officially supported Talisman platform in the future.

#### Price & Availability

Mpact 2, packaged in a 304-pin SBGA, is slated to sample in 1Q97 with volume production in 3Q97. Pricing has not been determined. Contact Chromatic (Sunnyvale, Calif.) at 408.752.9100 or access the Web at www. mpact.com; contact LG Semicon (San Jose, Calif.) at 408.432.5024; contact Toshiba (San Jose, Calif.) at 408.526.2612.

#### **Chromatic Releases Mediaware 1.0**

Mediaware is the fuel for the Mpact hardware engine. Chromatic recently shipped version 1.0 of Mediaware for Mpact/3000. The release includes an Mpact real-time kernel, Mpact resource manager, 2D/3D graphics, audio, video, fax/modem, and telephony (see sidebar, page 8, for details). Mpact 2 is software-compatible with its predecessor; therefore, the existing Mediaware will run on Mpact 2.

Mediaware 1.0 is designed to run on any Pentium processor. Chromatic is currently revising its software to take advantage of the MMX extensions incorporated in Intel's P55C Pentium and other forthcoming processors. The new code, called MMX Mediaware, is planned to ship in 1H97.

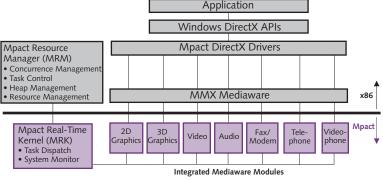

As Figure 4 shows, there are seven Mediaware modules, corresponding to the seven main multimedia functions. These modules, plus the Mpact real-time kernel, reside on the media processor. The rest of Mediaware software— Mpact DirectX drivers, MMX Mediaware, and the Mpact resource manager—run on the host processor.

When Chromatic originally announced its Mpact chip last year, the company expected to include MPEG-1 encoding and full DVD (MPEG-2 video and AC-3 audio) decoding in its initial Mediaware, but these functions have not yet appeared. Chromatic's software efforts were hampered by changing APIs at Microsoft as well as the relatively small size of the company compared with the task at hand.

For future Mediaware releases, we expect Chromatic to add DVD audio and video decoding, 3D positional audio,

Figure 4. The Mpact Mediaware provides seven multimedia functions. It interfaces to applications using Microsoft's DirectX APIs.

#### Complete Contents of Chromatic Mediaware Release 1.0

The most challenging problem in supplying a media processor for PCs is not the hardware but the software. While the Mpact processor is a complex piece of work, the associated Mediaware performs a huge array of functions. To deliver all of these functions, Chromatic has roughly twice as many software engineers as hardware engineers.

Without functional software, a media processor is worthless. Of course, none of the emerging media processors has an established software base, so all of this code must be created before the first systems can ship. By bringing its Mpact processor and Mediaware to market first, Chromatic has established a significant lead over other media-processor contenders. The list of software functions below demonstrates the barriers to entry in this market and sets a standard for competitors to match.

#### Video

Full support for the OpenMPEG command set; real-time MPEG-1 video decode at 30 frames per second, 18-bit color; system layer timestamp-based video/audio synchronization; fully accelerated color-space conversion, bilinear interpolation and filtering; full screen or video in a window; crisp synchronization with graphics output; fully accelerated video CD playback; patented hardware motion-estimation and image processing; PAL/NTSC video input and output.

#### Audio

DOS and Windows 95 audio through WAVE, MIDI, Direct-Sound API; MPEG-1 (layers 1 and 2) audio decode; wavetable synthesis, 32 simultaneous voices, complex envelopes and filters; precise audio control through support for key layering, velocity switching, variable keyboard scaling for alternate tunings, sharpness of attack, and speed of decay; general MIDI-standard compatibility with 128 original instruments and 60 drums, 7 additional Roland GS and Yamaha XG drum kits; up to 8 simultaneous play and record channels with different formats and frequencies resampled up to 44 kHz, with 36-bit internal precision; psychoacoustic minimization of quantization noise; Sound Blaster compatibility; Mpact Audio Process Manager for minimizing synchronization overhead between audio tasks; HMI and Miles driver support; industry-standard joystick with MIDI; industry-standard MPU-401 MIDI port.

#### 2D Graphics

Full DOS and Windows 95 GUI acceleration through Direct-Draw APIs; VGA register-level compatibility and Super VGA graphics modes; VESA BIOS Extensions 2.0 and UniVBE support; noninterlaced screen resolution up to 1,280  $\times$  1,024  $\times$  18-bit color at 60 Hz; full BitBLT acceleration

engine, including transparent BLTs and device bitmaps, with ternary operations; GUI acceleration of two-point line draws and trapezoidal and polygon fills; accelerated YUV conversion, scaling, filtering, clipping, and hardware cursor; full text acceleration engine; full hardware and BIOS support for VESA Display Power Management.

#### 3D Graphics

Full Windows 95 real-time 3D graphics acceleration through Direct3D API; acceleration of 3D-rendering pipeline rasterization; Z-buffering and double-buffered rendering; flat and Gouraud shading; accelerated 3D spans and 3D geometric primitives; diffuse and specular highlighting; true color (24-bit RGB) with decal and color-modulation texture blending; 2×2 ordered dithering; bilinear and trilinear MIP-mapped texture filtering; perspective-corrected texture mapping; support for texel formats including 555 and 565 RGB, 888 RGB and 8888 RGB $\alpha$ , 4-bit- and 8-bit-palletized; full transparency, including alpha maps for textures; full alpha blending support; depth cuing with atmospheric effects; subpixel accurate rendering; buffer/texture memory management through DirectDraw HAL.

#### Fax/Modem

Full Windows 95 support for Microsoft Unimodem V, TAPI and VCOMM APIs; data modulation up to V.34 bis; V.32 bis support; V.22 bis support, Bell 212A and Bell 103; V.42 bis data compression and V.42/MNP 2-4 error correction; V.8 compliance; fax modulation up to V.17 in answer and originate modes; full fax class 1, 2, and 2.0 command-set implementation; data automoding; DTMF generation, dial tone and busy detection, ring detection, and auto answer; V.14 async-to-sync conversion and RS-232 interface support; full range of baud rate and parity support on DTE interface with memory-to-memory interface.

#### Telephony

Support for Windows 95 TAPI and VCOMM APIs; adaptive full-duplex speakerphone with acoustic echo cancellation; answering machine and voicemail functionality; outgoing and incoming message support; concurrent DTMF detection; call-progress detection; IMA ADPCM voice compression/decompression; Caller ID support.

#### Mpact Real-Time Kernel and Mpact Resource Manager

Real-time operating system with oversubscription management; dynamic linking, loading, and profiling of all Mpact threads; RDRAM memory allocation and compaction; host and Mpact communication functions; Mpact dynamic resource allocation and degradation.

video editing, and videoconferencing over POTS, ISDN, and the Internet. With the increased performance provided by Mpact 2, Chromatic can also develop more compelling functions such as cable modem and ADSL-related support.

#### **Mpact Delivers Strong Performance**

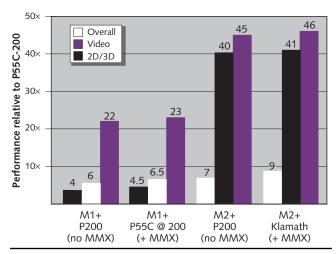

Figure 5 shows some Mpact performance data provided by Chromatic, all compared to the performance of a P55C-200 system with basic graphics and audio subsystems. Some of the numbers are based on simulations and others on real measurements. Mpact's biggest gain over the P55C alone is in its video-motion estimation, since the current MMX does not include any instructions to aid motion estimation. Therefore, we expect Mpact-based products to perform well for applications such as video authoring, videophone, and videoconferencing, where motion estimation is required.

The figure shows a 2× improvement in overall multimedia performance (a composite of the seven main functions) between Mpact/3000 and Mpact 2. The enhancements in Mpact 2 have a much bigger impact on 3D graphics, delivering an 8× improvement in this area. Note the comparison in Figure 5 is against a P55C system with no 3D hardware support; we expect a P55C with a midrange 3D accelerator (not just a "free-D" chip) to match the performance of the Mpact 2 system. The price of Mpact 2 must be close to that of the 3D chip for the Chromatic part to be competitive.

#### Mpact "R" Offers Intermediate Solution

Table 1 lists media processors that Chromatic and its partners plan to offer in 1997. There are actually three versions of the M1 planned. The first is called Mpact/3000, reflecting its 3,000 MOPS of peak throughput. The second version, Mpact R/3000, is identical except for the inclusion of an on-chip RAMDAC (the same one carried forward into Mpact 2). The third offers a 20% speedup by clocking the RDRAM at 300 MHz and the CPU core at 75 MHz. This version is called Mpact R/3600, since it produces 3,600 MOPS.

Chromatic is already testing first silicon of the Mpact R design and expects LG and Toshiba to provide samples later this quarter, with production versions in 1Q97. The company had originally hoped to see widespread use of its Mpact/3000 in PCs during this Christmas season, but it has missed this window of opportunity. At this point, we expect

many PC makers to wait until the integrated RAM-DAC is available, reducing system cost and board footprint compared with the initial implementation. The Mpact R should quickly replace the original Mpact chip in the product line, with the two speed grades offering a price/performance tradeoff. When Mpact 2 reaches the market next fall, it will become the new high-end part.

#### **Mpact Competes Effectively**

Today, more than a dozen vendors are involved in designing and/or manufacturing media processors.

Figure 5. The M1 delivers a performance boost over a basic P55C system on most multimedia functions, as shown by the "overall" bar. The M2 further improves performance, particularly on video encoding and on 3D graphics. In all cases shown, the Mpact runs at 62.5 MHz and the Mpact 2 at 125 MHz. (Source: Chromatic)

The critical questions are how these devices will compete among themselves and how they can effectively compete against software-only and hardwired approaches.

The advantages of a media processor over a hardwired multimedia IC are easy-to-achieve functional integration, flexibility for evolving standards and improving algorithms, and the ability to deal well with real-time applications such as videoconferencing and surfing the Internet. The real-time advantage is due to the lack of real-time support in today's Windows 95 and NT. The programmability of media processors makes it easy to incorporate some kind of real-time kernel that can coexist with Windows. With dynamic resource allocation, a media processor can devote all its horsepower to the current application. This feature offers a potentially lower cost than the hardwired approach. In the hardwired system, if the current application doesn't use a particular function block, transistors dedicated to that function are wasted. The main disadvantages of media processors are programming overhead and design complexity.

A more interesting topic is how the Mpact architecture competes with other media-processor architectures. Like Mpact, Samsung's MSP (see MPR 8/26/96, p. 1) handles seven common multimedia functions. MSP's advantages

|                  | Mpact/<br>3000 | Mpact R/<br>3000  | Mpact R/<br>3600 | Mpact 2/<br>6000 |

|------------------|----------------|-------------------|------------------|------------------|

| MOPS (peak)      | 3,000          | 3,000             | 3,600            | ~6,000           |

| Internal RAMDAC  | No             | Yes               | Yes              | Yes              |

| RDRAM Bandwidth  | 500 MB/s       | 500 MB/s 600 MB/s |                  | 1,300 MB/s       |

| 3D Rendering H/W | No             | No                | No               | Yes              |

| Cache Size       | 4K             | 4K                | 4K               | 8K               |

| AGP, 66-MHz PCI  | No             | No                | No               | Yes              |

| Samples          | Done           | 4Q96 4Q96         |                  | 1Q97             |

| Production       | Now            | 1Q97              | 1Q97             | 3Q97             |

**Table 1.** By 2H97, Chromatic and its manufacturing partners plan to bring four Mpact media processors into the market. (Source: Chromatic)

include an open software model, better potential 3D graphics, and a larger initial market. Also in MSP's favor is that Microsoft has chosen MSP as one of the key components for its Talisman reference design. Microsoft's real-time kernel will likely work with MSP first, and it will take extra time to port it to other architectures, such as Mpact, if Microsoft or Chromatic decides to do so.

The Chromatic chip, on the other hand, is available now, costs less than MSP, and takes advantage of the computing power of the host CPU. Unlike Samsung's media processor, which replaces the host CPU when running multimedia tasks, Mpact assists the CPU. Mpact uses its resource manager for dividing multimedia workloads between the CPU and Mpact in real time. Under this cooperative computing environment, Mpact should be able to compete effectively in the PC market against any of the other media processors that have been announced so far.

Mpact's biggest advantage over other media processors is that it is real and in production; the others are simply prototypes. Trimedia says its TM-1 (see MPR 11/13/95, p. 22) will enter production in 1Q97, but TM-1's software will not be completed until the end of 1997, a full year behind schedule. In the PC business, time to market is everything. If Chromatic and its partners execute properly, we don't believe that other media processors for PCs will present any significant threat to Mpact in 1997.

#### **Open ISA Has Advantages**

The company's unusual business model includes a closed software environment: Chromatic is the only vendor allowed to develop software for Mpact. This restriction creates competitive disadvantages, espe-

cially since most other vendors claim their media-processor architectures are open. But Chromatic and its partners have nothing to lose by saying their architecture is also open, and we believe they will do so in the future.

The potential upside for opening the Mpact instruction-set architecture (ISA) is huge. For example, unlike Samsung and Philips' TriMedia, Chromatic focuses mainly on PC applications today. Mpact could be used for Macs and non-PC applications, but only if software is written for those applications, and Chromatic is not interested in doing so right now. The startup company is already stretched developing the required Mediaware for PCs.

Opening the software environment creates possibilities for third-party ISVs to bring Mpact to non-PC markets. This would allow Chromatic to use its limited software resources for PC applications while expanding the potential base of Mpact processor sales.

Enabling Mpact for non-PC applications is an important way to secure the future of Mpact. Non-PC devices will

greatly expand the potential market size and make Mpact an interesting CPU for network computers, set-top boxes, videoconferencing devices, videophones, car navigators, and so on. There are many advantages to staying away from the "Wintel" architecture, where Intel and Microsoft dominate the entire platform. The majority of the Mpact development for non-PC applications will be software-related, but to encourage this, Chromatic must open its ISA.

#### **Future Devices Are Promising**

Mpact/3000 has proved Chromatic has a working architecture and not just a paper tiger. It also provides a means for kicking off Mpact software development. We believe that its lack of integration and 3D performance are limiting its acceptance, however. The forthcoming Mpact R/3600 and Mpact 2 parts solve these problems and should help propel Mpact into mainstream PCs.

Now that the Mpact 2 design has taped out, we expect Chromatic and its manufacturing partners to develop Mpact 2 derivatives. An obvious one is a notebook version that adds support for an LCD display and advanced power management. A notebook Mpact 2 would be a more compelling product than its desktop counterpart. First, the Mpact design saves space, power, and cost compared with a flock of fixed-function sound, graphics, video, and modem chips. Second, due to thermal restrictions, notebooks tend to use less powerful host CPUs. Therefore, the host needs more help to achieve strong multimedia performance.

Chromatic has already started the design of its third-generation Mpact, codenamed M3. We expect the M3 will be fully

Talisman-compliant, since Mpact must support the PC entertainment applications for which Talisman is designed. In addition, transforming from its own real-time kernel to the Talisman real-time kernel can be beneficial in providing a standard software interface for applications.

By late 1998 or 1999, the IEEE 1394 (FireWire) interface will be important in PCs. Therefore, integrating a 1394 interface into the M3, or at least one of its derivatives, would be useful. Besides adding 1394, some M3 derivatives may include new features such as a video codec or frame-buffer memory on the chip.

To succeed in PCs, Mpact must offer a significant performance gain as a complement to MMX. Mpact is good at real-time events, isochronous applications, and video encoding and decoding. Together with an MMX host processor, Mpact offers significant value over the MMX-only or fixed-function approaches for future multimedia-ready PCs. This value should gain Mpact design wins on both PC mother-boards and add-in cards.  $\square$

At the Forum, Chromatic founder Stephen Purcell announces the second-generation Mpact 2.

# Fujitsu Aims Media Processor at DVD

### MMA Combines Long-Instruction-Word Core, Integrated Peripherals

by Peter N. Glaskowsky

Hoping to claim a share of the growing consumer multimedia market, Fujitsu's Shunsuke Kamijo described the company's new

multimedia assist (MMA) processor at last month's Microprocessor Forum. The new architecture features a twopipeline long-instruction-word (LIW) core capable of executing up to six 16-bit integer operations simultaneously for a peak rate of 1.08 GOPS at 180 MHz. This is a higher clock rate than most other announced media processors, the result of a design that favors simplicity over sophistication.

The first chip in the family adds two 8K SRAMs; graphics, DMA, and SDRAM controllers; and several integrated peripherals to the MMA core. Fujitsu did not announce pricing or availability; we expect to see this product in limited sampling by the end of the year, with production volumes available in the first half of 1997.

Unlike other recently announced media processors, MMA is intended for consumer electronics, such as intelligent televisions and DVD players. MMA can perform DVD decoding, modem functions, and videoconferencing in software (but not all at once). MMA provides no floating-point support, 3D acceleration features, or PCI interface, making it unattractive for the PC market.

#### **MMA Core Includes Five Execution Units**

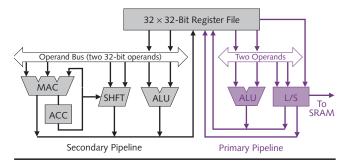

The heart of MMA is its LIW core with two pipelines and five execution units, as Figure 1 shows. Each 64-bit instruction word contains a pair of 32-bit instructions. One instruction is always dispatched to the primary pipeline and the other to the secondary pipeline. This simple LIW is much less sophisticated than the VLIW architecture of Philips' TriMedia (see MPR 11/13/95 p. 22). In TriMedia, each instruction word contains up to five operation slots, and there are 27 execution units. Each unit is fully pipelined, allowing the TriMedia core to sustain five operations per clock in long code segments.

In MMA, one pipeline contains a 32-bit ALU and the load/store unit. The other contains a second ALU along with multiply-accumulate and divide-shift units. When the primary ALU is used in combination with the multiply-accumulate unit in the secondary pipeline, the MMA core can achieve a peak execution rate of three 32-bit or six 16-bit operations per cycle.

MMA's instruction-pairing rules are relatively simple. All five execution units are fully pipelined, yielding single-cycle throughput, so one instruction can be dispatched to each pipeline in each clock cycle. Division and modulo operations are an exception: these take 33 to 36 cycles to complete and stall both pipelines while they execute. Taken branches

require three cycles; one branch-delay slot is provided, which may be used for any single-cycle operation.

Fujitsu also provides 27 instructions for multimedia operations such as MPEG decoding and surround-sound processing. These include variations of ADD, SUB, and MAC instructions with signed and unsigned saturating arithmetic as well as 16-bit SIMD versions of most instructions.

Although the load/store unit supports byte-size data types, the ALUs support only 16- and 32-bit data. Other media processors support byte operations, allowing twice the peak performance when dealing with byte-oriented data types like RGB pixels or 8-bit sound.

MMA provides an unusual saturation mode. A source register may specify the bit at which saturation occurs. This mode allows 32-bit operations to perform 24-bit saturating arithmetic, for example. This should prove useful, since few multimedia data types are exactly 16 or 32 bits in length. For example, MPEG decoding uses 9-bit values, and AC-3 audio requires 24-bit precision. Saturation to an arbitrary (non-power-of-two) value, however, is not supported.

#### Register File Matched to Pipeline Requirements

The MMA core includes a  $32 \times 32$ -bit multiported register file. It supports five simultaneous reads and three writes, enabling sustained single-cycle throughput on the inner loops of common multimedia functions.

This register set is smaller than in most competing media processors. For example, TriMedia has 128 32-bit registers. These larger register sets are especially useful for 3D acceleration. MMA's register set was designed for algorithms like the inverse discrete cosine transform (IDCT) in MPEG decoding. These algorithms typically have working sets that will not fit in a register file; instead, registers are used to store control values and coefficients, and data storage depends on fast access to memory.

**Figure 1.** The MMA core includes two pipelines that operate in parallel. The primary pipeline supports ALU and load/store operations, while the secondary pipeline can perform multiply-accumulate, shift, and ALU operations.

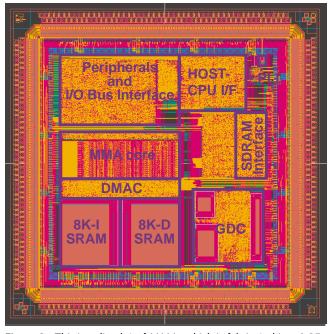

**Figure 2.** To support consumer multimedia applications like intelligent television, MMA includes many functional blocks in addition to the programmable MMA core.

#### SRAMs, Not Cache, Meet Core Bandwidth Needs

Rather than relying on caches to reduce average memory access penalties, MMA provides an 8K SRAM instruction store plus an 8K SRAM data store. Each SRAM is organized as 1K 64-bit words, and both operate at the full 180-MHz rate of the core. The instruction SRAM can provide a 64-bit dual instruction word to the core on each clock, while the data SRAM can transfer one, two, or four bytes to or from the register file in each cycle.

Unlike caches, the SRAMs must be managed by software. Transfers between the SRAMs and the local SDRAM can be performed only by the on-chip DMA controller, which is interlocked with the core. During a DMA transfer,

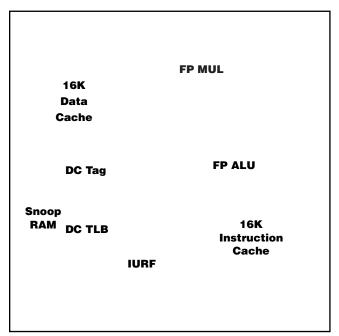

**Figure 3.** This is a die plot of MMA, which is fabricated in a 0.35-micron three-layer-metal CMOS process. The die size is 77 mm<sup>2</sup>, with 1.3 million transistors. The MMA core is only 4.3 mm<sup>2</sup> in size.

the core is stalled. The DMA controller supports normal block transfers at the maximum rate of the DRAM interface, as well as rectangle transfers, a way to realign raster-oriented video data. DMA transfers are controlled to byte boundaries, a necessary feature given the unpredictable block lengths of digital audio and video data.

In effect, MMA trades the complexity of a cache controller for added software complexity. This tradeoff would be unacceptable in a general-purpose processor, but MMA is designed to execute simpler multimedia code that can be optimized for this architecture. A similar scheme is used by Chromatic's Mpact, although Mpact's software "caches" are multiported and offer much higher net throughput.

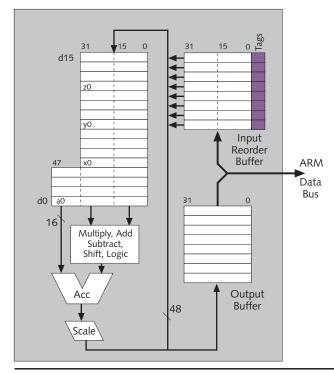

#### SDRAM Interface Sustains 1-Gbyte/s Bandwidth

Figure 2 shows the internal organization of the first MMA product. The MMA core includes the LIW engine, SRAMs, and DMA controller. The integrated SDRAM controller manages up to 32M of SDRAM operating at up to the 180-MHz pipeline rate. While current SDRAMs do not support this high speed, future parts will. At 180 MHz, the peak data rate is 1.4 Gbytes/s, but sustained rates will be lower due to bus turnaround delays and page misses.

In more realistic implementations, the SDRAM interface will run at half the core speed, or 90 MHz, yielding 720 Mbytes/s peak and about 500 Mbytes/s sustained throughput. The SDRAM interface supports four-word burst transfers and is fully pipelined, so subsequent reads to the same DRAM page do not cause wait states.

#### Integrated Peripherals Adapt MMA to TV

To support intelligent televisions, MMA includes a graphics display controller (GDC) module. In addition to interlaced and noninterlaced NTSC and VGA resolutions, the GDC also supports a "wide-VGA" mode of 860 × 480 pixels that can be used to enhance quality on high-end televisions. Such televisions offer greater horizontal than vertical resolution, so typical "square pixel" display modes like 640 × 480 do not achieve the best possible visual quality. MMA's wide-VGA support allows processor-generated content like the graphical user interface to be displayed directly in the higher resolution, while some digital video content, such as wide-screen-mode DVD playback, can be scaled to fill the wider effective screen size.

The GDC manages three display windows, each with a separate frame buffer in the local SDRAM. The windows can be positioned and overlapped arbitrarily. Frame buffers can contain pixels in the YCrCb color space for MPEG decoding, RGB for user-interface displays, or a 15-color-plus-transparency mode for processor-generated captions and simple graphics. As the screen is drawn, these pixel types are all converted to standard digital RGB using a color-space conversion engine in the GDC.

The GDC shares access to the SDRAM with the DMA controller and host processor. SDRAM refresh activity can

be synchronized to the display controller, taking place during the horizontal refresh interval. This eliminates the need for deep FIFOs in the display refresh path, since the display controller can always depend on uninterrupted access to the SDRAM during the display period of each scan line.

Other peripherals on the die include a timer, two serial I/O controllers, and a pulse-width-modulation module for motor control, plus interfaces for an audio chip and other off-chip peripheral devices. MMA does not include a RAM-DAC, however, which would have been fairly easy to add given the relatively low resolution display modes it supports.

MMA is not designed for general-purpose tasks like control and communications. Instead, it will typically be used as a coprocessor for multimedia tasks, coupled with a general-purpose host CPU like Fujitsu's SparcLite.

The first MMA implementation has a 32-bit SparcLite interface built in. In this configuration, MMA acts as a unified memory architecture (UMA) DRAM controller for SparcLite, storing the frame buffer plus code and data for both processors in the local SDRAM. A typical intelligent TV controller would consist of the MMA, a SparcLite processor, ROM, RAM, a RAMDAC, and a few analog interface components.

#### Software Development Tools

Fujitsu has made a special effort to enable third-party software development, but it has not announced specific third-party relationships. Fujitsu commissioned a full suite of development tools from Green Hills (www.ghs.com), extending the existing set of SPARC tools to include an assembler and simulator for MMA as well as an MMA-aware version of the Green Hills Multi development environment. Multi gives an MMA programmer a unified environment with separate windows for SPARC and MMA operations.

Fujitsu has also developed a version of Wind River's VxWorks (www.wrs.com) that runs on the SparcLite/MMA target system, supporting remote-control debug-

ging operations through VxServ. VxWorks runs only on the SparcLite processor; at this time, Fujitsu has no real-time OS kernel for MMA itself.

Fujitsu is developing its own set of essential software libraries for MMA. At the Forum, Fujitsu's Kamijo showed its development schedule for six library functions: MPEG decode and encode, JPEG decode and encode, JBIG (a lossless still-image compression scheme), and the V.34 modem algorithm. All of these functions are projected to be available by 1Q97.

#### Benchmarks Demonstrate MMA Performance

Kamijo showed limited benchmarks based on MPEG-1 performance. The 180-MHz MMA can decode video-only

#### For More Information

Pricing and availability for MMA have not been announced. Contact Fujitsu (San Jose, Calif.) at 408.922.9574 or on the Web at www.fujitsumicro.com.

MPEG-1 bitstreams at 118.4 frames per second (fps), suggesting that standard 30-fps MPEG-1 requires only 25.3% of the device. When standard 48-kHz audio is included, the decode rate dropped to 94.1 fps, increasing utilization for 30fps MPEG-1 to about 32%.

Although Fujitsu has not released benchmarks for DVD applications, the company says MMA will be able to perform MPEG-2 video plus Dolby AC-3 audio decoding at 30 fps, meeting the basic requirement for DVD support. This is a critical capability; without DVD capability, MMA could be relegated to the much smaller market for video karaoke players and other MPEG-1 products.

Fujitsu did not discuss performance on other multimedia tasks like V.34 modem operation, but it is unlikely that

> MMA will be able to support a V.34 modem connection while simultaneously decoding DVD content.

### PHOTO OF **SPEAKER**

Shunsuke Kamijo describes Fujitsu's first media processor at the Microprocessor Forum.

#### **Goals Determine Results**

The first MMA is shown in Figure 3. The die size is 77 mm<sup>2</sup>, fabricated in a 0.35-micron three-layer-metal process, operating at 3.3 V and packaged in a 352-ball BGA. Based on the MDR Cost Model, the estimated manufacturing cost of this part is \$30. The MMA core, a full-custom design, occupies only 4.3 mm<sup>2</sup> of the die. Even at this small size, it offers more than enough processing power for the target applications. Power consumption for the device is very low, at only 600 mW (typical). This compares very well with Trimedia's TM-1 at about 4 W, offering an advantage in consumer applications.

MMA is a well-balanced part that should compete effectively against non-programmable devices in DVD players while also working well in products that require more intelligence. Fujitsu's primary competition will come from dedicated DVD decoders from C-Cube and Oak (see page 5). Hardwired devices may be smaller and less expensive than MMA, making them a better choice for cost-sensitive DVD players, but MMA is more flexible, making it more suitable for an intelligent TV.

In addition, MMA is likely to be much less expensive than PC-oriented media processors like TM-1 due to its smaller SRAMs and lack of floating-point support and 3D acceleration, making it a good fit in the embedded multimedia applications for which it was developed.

# TurboSparc Offers Low-End Upgrade

### New Fujitsu Chip Plugs into MicroSparc-2 Systems for Performance Boost

by Linley Gwennap

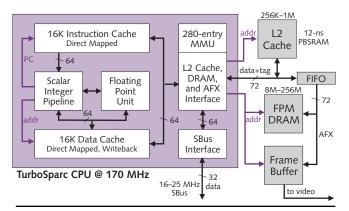

Eyeing an installed base of underpowered SparcStation 5 workstations approaching half a million units, Fujitsu has developed a new CPU as a field upgrade for those systems. The TurboSparc processor is also appropriate for new low-cost workstations. Following the MicroSparc tradition, TurboSparc is a highly integrated 32-bit processor with on-chip cache, memory, and SBus interfaces, as Figure 1 shows. The performance improvement is modest, however, moving users from the equivalent of a 486 up to a midrange Pentium. TurboSparc is shipping now, both as a standalone device and in an upgrade kit.

Fujitsu estimates the 170-MHz TurboSparc will deliver 3.5 SPECint95 and 3.0 SPECfp95 (base), although current systems need more compiler tuning to achieve these marks. If achieved, these scores would represent roughly twice the integer performance of a 110-MHz MicroSparc-2 (MS-2) and about 50% better floating-point performance. The gain over slower versions of MS-2 will be even greater. This boost makes TurboSparc attractive as a field upgrade. This performance, however, is well below that of a Pentium Pro, PowerPC 604e, or even a high-end Pentium, all of which sell for about the same price as the \$499 TurboSparc.

#### **New CPU Core Boosts Clock Speed**

Although Fujitsu builds and sells MicroSparc-2, that chip design was developed and is owned by Sun. For its upgrade chip, Fujitsu chose to develop its own CPU core, deploying a small team in San Jose (Calif.). For cost and time-to-market reasons, the TurboSparc team chose a simple scalar CPU design based on the 32-bit SPARC v8 architecture. In this regard, TurboSparc is similar to MS-2 but quite different from the superscalar 64-bit UltraSparc.

**Figure 1.** TurboSparc integrates nearly all the memory and system interfaces needed for a complete low-cost workstation.

Because of the similar throughput of the MS-2 and TurboSparc cores, the higher clock speed of the latter part provides a large part of its performance gain. TurboSparc clocks 55% faster than its predecessor. Some of this speed advantage is due to a gate shrink from 0.4-micron CMOS to 0.35-micron.

Most of the speed gain, however, comes from a new pipeline. Whereas MicroSparc-2 uses the classic five-stage RISC pipeline (see MPR 11/15/93, p. 1), TurboSparc extends it to six stages for integer instructions and eight for FP instructions. As Figure 2 shows, a new "resolve" stage, after the data-cache access, checks for any faults from the cache access before proceeding to the writeback stage. This new stage provides more time for the cache access to complete, avoiding a critical timing path. The elimination of branch folding, a feature found in MS-2, also eases the timing and helps achieve better clock speeds.

The other new stages handle FP instructions, forming an integrated integer/FP pipeline that simplifies the control logic. Most FP operations, including ALU ops and multiplication, have a four-cycle latency and thus are complete by the FR stage. FP divide and square root both process two bits per cycle and can take from 8 to 50 cycles to complete; the average is 21 cycles for single-precision operands and 35 cycles for double-precision operands. The FP unit also handles integer multiply and divide operations; multiplication has a seven-cycle latency, while division is the same as a single-precision FP division.

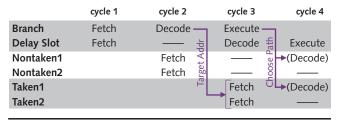

One unusual feature of the new CPU is its ability to handle branches without penalty and without prediction. The instruction cache provides two instructions per cycle, while the CPU consumes only one. On a branch, there is enough bandwidth to fetch from both the taken and nontaken paths until the branch condition is resolved, eliminating any branch penalties, as Figure 3 shows. This method avoids the complexities of branch prediction or branch

| Fetch                                                     | (F) Fetch two instructions from I-cache            |  |  |

|-----------------------------------------------------------|----------------------------------------------------|--|--|

| <b>Decode</b> (D) Decode one instruction and read operand |                                                    |  |  |

| <b>Execute</b> (E) Execute integer operation              |                                                    |  |  |

| Memory (M) Read tags and data from D-cache                |                                                    |  |  |

| Resolve (R) Check tags, abort data if L1 cache miss       |                                                    |  |  |

| Write                                                     | (W) Write result to integer register file          |  |  |

| FP Resolve                                                | (FR) Complete FP ALU or multiply (4 cycle latency) |  |  |

| FP Write                                                  | (FW) Write result to FP register file              |  |  |

**Figure 2.** TurboSparc's pipeline adds one stage to MicroSparc-2's for integer instructions and two more stages for FP instructions.

folding and is similar to the technique used by QED in the RM7000 processor (see MPR 10/28/96, p. 36).

As Figure 1 shows, TurboSparc contains 16K each of instruction and data cache. The instruction cache is the same size as in MS-2, but the data-cache size is doubled relative to that chip and is now a write-back cache rather than write-through. These caches are fairly small compared with those of recent microprocessors and are direct mapped, further reducing their hit rate. The MMU is SPARC v8 compliant. It includes a 256-entry TLB for data translations, four more entries for large data pages, a four-entry instruction TLB, and a 16-entry I/O TLB. The total number of TLB entries is four times more than in MS-2, eliminating another performance bottleneck for some applications.

#### **DRAM Interface Now Supports L2 Cache**

The second major performance enhancement from MS-2 is the addition of an external level-two cache. MicroSparc-2 is completely limited to the paltry 24K of cache that is available on the chip, relying on direct access to external DRAM for all other memory references. This shortfall creates a significant performance degradation on SPEC95 as well as on many workstation applications.

TurboSparc supports 256K–1M of direct-mapped L2 cache. This cache has the same 32-byte line size as the onchip caches and uses a write-through policy. It runs at one-half the core CPU speed, requiring 12-ns pipelined burst SRAMs for the 170-MHz processor. An access that hits in the L2 cache stalls the CPU pipeline for 12 cycles. With a 72-bit interface, it takes four cycles to return a full cache line. A one-third-speed cache is also supported, but this choice will reduce performance.

Using ×36 SRAMs, the cache tags are stored side by side with the data. Each cycle, the 72-bit interface returns 64 bits of data, 2 parity bits, and 6 tag bits. After the first two accesses, the complete 12-bit tag can be assembled and checked to see if the access has hit in the cache. This design eliminates the need for separate external cache tags (or internal tag storage). The tags cannot be checked until two cycles after the data is received, but the new R stage allows enough time to abort the writeback if the tag check fails.

DRAM accesses are started in parallel with L2-cache accesses and are aborted if the L2 cache hits. This strategy reduces the duration of a pipeline stall on an L2 cache miss by overlapping the DRAM access. The DRAM interface is configurable for page-mode DRAM of various speeds but does not handle more advanced memories such as EDO or SDRAM. These memory types are not supported in the older SparcStation systems, so Fujitsu did not bother to add them, keeping the design as simple as possible to speed its completion. With 60-ns DRAM, the CPU pipeline stalls for 24 cycles on an access to main memory.

The memory controller supports up to eight banks of 32M each, or 256M maximum. This limitation is similar to that of MicroSparc-2.

#### Price & Availability

The 170-MHz TurboSparc chip is available now at a list price of \$499 in quantities of 1,000. The 160-MHz TurboSparc upgrade kit costs \$1,500 in quantities of one. To get more information on TurboSparc, contact Fujitsu (San Jose, Calif.) at 800.866.8608 or access the Web at www.fujitsumicro.com/sparcupgrade/sparcmicro.html.

#### Sun AFX Graphics Supplements SBus Interface

Recently, Sun has added a new graphics interface called AFX. These graphics cards reside on the main memory bus instead of the pedestrian SBus, significantly improving bandwidth. AFX requires adding only a few extra control signals to the existing memory bus, which Fujitsu has done in TurboSparc. This change allows an end user to plug an AFX graphics card into a system that has been upgraded with TurboSparc.

Like MS-2, the new processor supports SBus directly on the chip. The SBus operates at 16–25 MHz, typically one-eighth of the CPU clock speed. Up to six bus masters can be connected to the 32-bit SBus. TurboSparc is fully compatible with the Macio and Slavio chips that supply basic I/O functions in the SparcStation 5 and similar systems.

The integrated memory and bus interfaces make multiprocessor configurations impossible. This fact simplified some aspects of the TurboSparc design. The cache does not support multiprocessor coherency, for example, and the CPU core does not execute certain SPARC v8 instructions for MP synchronization.

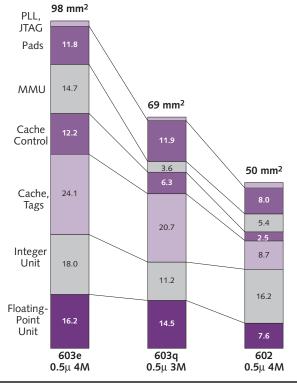

#### Manufacturing Cost Shrinks

TurboSparc is built in Fujitsu's 0.35-micron four-layer-metal CS-60ALE, keeping the die size down to 132 mm<sup>2</sup>, relatively svelte for a processor with so much integrated system logic. MicroSparc-2, by comparison, weighs in at 233 mm<sup>2</sup> using the 0.4-micron CS-55 process (see MPR 7/10/95, p. 16).

Although the gate shrink is minor, a bigger gain is seen in the metal layers: the CS-55 metal layers are from a 0.5-micron process, whereas CS-60ALE is a complete 0.35-micron process. Thus, the TurboSparc die size is about what we would expect if the MS-2 die was shrunk to the same 0.35-micron process.

**Figure 3.** On a branch, TurboSparc fetches from both the nontaken and taken paths. By cycle 4, the branch is resolved, and either instruction can be executed without penalty. (— indicates stall)

Figure 4. Fujitsu's TurboSparc combines a scalar SPARC CPU with a complete set of system interfaces. Sporting 3 million transistors, the die measures  $11.5 \times 11.5$  mm in a 0.35-micron four-layermetal CMOS process.

The transistor count of TurboSparc is slightly higher: 3.0 million, compared with 2.3 million for MS-2. Most of the increase is due to the extra 8K of cache, with the remainder in the L2 cache and AFX interfaces. The CPU core has about the same number of transistors as in MS-2. Because the physical layout of MS-2 is rather loose, Fujitsu was able to pack more transistors into the same relative die area. Figure 4 shows the TurboSparc die.

TurboSparc is packaged in a 416-contact plastic BGA. The plastic BGA saves cost compared with the old-style ceramic PGA used for MS-2, despite the extra 95 leads required by the new interfaces. Combining the savings from the plastic package and the smaller die, the MDR Cost Model estimates the cost of building TurboSparc at about \$50, a third less than the cost of MS-2. The PowerPC 603e and Pentium chips deliver similar performance at a build cost of \$30-\$40, but these chips cannot match the integrated system logic of TurboSparc.

Like MS-2, the new chip runs at 3.3 V. The maximum power dissipation is 9 W at 170 MHz, matching the maximum power of MS-2 despite the significantly higher clock speed. Fujitsu paid more attention to moderating power in the new design, adding some gated clocking to keep the chip within the same thermal envelope as its predecessor.

#### Module Upgrades MicroSparc-2 Systems