# THE INSIDERS' GUIDE TO MICROPROCESSOR HARDWARE

# **x86 Competition Thriving** Intel Alternatives Multiply and Strengthen But Struggle for Profits

# by Michael Slater

We launch our year-in-review coverage in this issue with a focus on PC processors. Next issue, we'll take a look at processors for RISCs and servers, embedded CPUs, and 3D graphics chips.

What a difference a year can make. At the start of 1998, AMD was floundering, Cyrix was proclaiming a total focus on integrated processors, and Intel's market share was around 90%. At the end of 1998, AMD's market share has more than doubled, Cyrix has returned to its standard-pinout strategy for the PC market, and Intel's market share in the fourth quarter has fallen below 80%—its lowest level since 1995.

Although AMD and Cyrix are Intel's only competitors of significance today, IDT continues to slowly gain ground with its WinChip line, and Rise has just begun shipping its low-end mP6 offering. Next year, Transmeta's processor will presumably debut, bringing to six the total number of suppliers of x86 processors for PCs. So far, Intel continues to earn spectacular profits while its competitors still struggle to achieve profitability; nevertheless, AMD and Cyrix, at least, have a good shot at stopping the red ink in 1999.

The past year saw a marked increase in the complexity of Intel's product line with the debut of the Celeron and Xeon brands. As Figure 1 shows, Cyrix has continued with two lines, integrated and standard, while the other vendors are each developing a single line. AMD will add a second line in mid-1999 with the K7.

# Celeron Off to a Shaky Start

Intel's decision to launch the Celeron brand with a cacheless version of Pentium II, code-named Covington, was the biggest blunder the company has made since its mishandling of the infamous Pentium FDIV bug. On typical integer applications, this chip's performance fell well short of that of the alternative processors at the same clock speed, including Intel's own Pentium/MMX. As a result, the Celeron brand was tarnished at birth; its relatively strong FP and MMX performance was not enough to compensate for meager performance on the applications most users spend their time running.

Because of Covington's weak performance on the most widely used benchmarks, AMD and Cyrix were able to easily position their products as superior alternatives. If Intel had not been so determined to shift the entire market away from Socket 7, it could have shipped 266-MHz Pentium/MMX processors for the entry-level segment, with a lower manufacturing cost and better performance on most applications. As with previous product transitions, Intel abandoned the old infrastructure when there was still strong demand, and its competitors gained market share as a result.

Celeron successfully pushed Pentium/MMX out of Intel's desktop product line, but it also gave AMD and Cyrix a great opportunity to gain market share. With the newer Mendocino-based Celeron, however, which includes a 128K on-chip L2 cache, Intel's performance position is vastly improved. Now that Covington is essentially gone from the

| Intel | Celeron Mendo<br>(Covington)<br>Pentium II<br>(Deschutes)<br>PII Xeon | Katmai Coppe          | rmine Willamette<br>scades Foster<br>Merced |  |  |

|-------|-----------------------------------------------------------------------|-----------------------|---------------------------------------------|--|--|

| AMD   | К6 К6-2                                                               | K7 K7S<br>K6-3 K6-3S  |                                             |  |  |

| Cyrix | MII<br>MediaGX                                                        | Jedi Jedi-370*<br>MXi | M3                                          |  |  |

| IDT   | WinChip W2                                                            | W3 W4                 |                                             |  |  |

| Rise  | mP6                                                                   | mP6-II                |                                             |  |  |

|       | 1998                                                                  | 1999                  | 2000                                        |  |  |

Figure 1. Intel divided its products into entry-level, mainstream, and workstation/server lines. AMD will add a second line with the K7, while Cyrix pursues both integrated and standard families. (Source: vendors, except \*MDR-created names; S = shrink, Cu = copper, 370 = Socket 370)

market and Intel is taking some of the restraints off Mendocino's clock speed, the taint on the Celeron brand will be overcome—with the help of few hundred million dollars in advertising.

Celeron's clock speed was limited to 333 MHz in 4Q98 purely for positioning reasons; while it could have run much faster, doing so would have cannibalized Pentium II sales and resulted in a dramatic drop in Intel's average selling price (ASP). Sources indicate Intel will launch 366- and 400-MHz Celerons early in 1999, however, giving the line a big boost. With Katmai on the horizon, Intel has apparently decided that defending its share of the basic PC market is more important than protecting the Pentium II line.

Pentium II retains a performance advantage from its larger cache, but for most users the premium isn't worth it. It will remain the high-performance PC processor of choice, in 400- and 450-MHz versions, for only two months, after which Katmai will debut and fill in the high end of the line. By fall 1999, as Table 1 shows, the market will be divided among Mendocino, Dixon, Katmai, and Coppermine, with essentially no role for today's Pentium II.

In 1999, Celeron will be differentiated by its lack of Katmai New Instructions, its smaller L2 cache, and its slower bus speed. Even the imminent 400-MHz Celeron uses a 66-MHz bus—a limitation driven primarily by positioning concerns (though there are system cost benefits to the slower bus). In mid-1999, when Katmai moves to a 133-MHz bus, Intel presumably will allow Celeron to move to a 100-MHz bus.

Celeron started out in a low-cost derivative of the Slot 1 module, but with the L2 on the chip, the module has become vestigial and will disappear in the Celeron line when Intel switches over to a 370-pin plastic PGA, which is commonly called Socket 370. The new socket, possibly in a revised form, probably will enter the Pentium II line with Coppermine.

# Katmai to Revitalize High End

The high end of Intel's desktop line has stalled at 450 MHz-a

speed Intel began shipping in August. Today's Deschutes-based Pentium II isn't likely to ever ship at a higher speed. Katmai is due to ship at 450 and 500 MHz toward the end of 1Q99, raising clock speeds a notch. Around midyear, with the debut of the Camino chip set, Katmai will make the leap to a 133-MHz system bus and a 533-MHz CPU speed. That may be the top speed Katmai achieves in 0.25-micron technology.

In the fall, Intel will roll out Coppermine, a 0.18-micron version of Katmai. We expect this processor to include 256K of on-chip L2 cache. Because the on-chip cache will run at the full processor speed, it should deliver better performance than Katmai with a 512K off-chip L2 while reducing manufacturing cost and making the Slot 1 module unnecessary. Although Intel is likely to offer Coppermine in a Slot 1 module to allow it to drop into existing system designs, its ultimate form presumably will be the 370-pin PGA first introduced for Celeron.

Coppermine should scale to much higher frequencies than Katmai. With a 133-MHz bus, the progression will be 533, 600, 667, 733, with this last speed unlikely to be reached until the first half of 2000.

Katmai and Coppermine will be very important, since without them Intel's average processor price would be in steady decline. Intel needs these chips to fill in the upper price points, and it must count on the appeal of the Katmai New Instructions to lure users to buy the high-end chips. We expect Intel to create another extension of the Pentium II brand for these chips and to heavily promote the new brand, much as it did with MMX during the Pentium/MMX rollout in 1997.

## Mobile: Last Refuge of Pentium/MMX

In the mobile environment, Intel did not have a Celeron offering in 1998, leaving Pentium/MMX to hold the low end. The mobile Pentium II packaging is relatively expensive, making it difficult to bring this product to the lowest price points, and it is also bulky. In early 1999, Intel will debut the first mobile Celeron at 266 and 300 MHz. Like Mendocino, this chip will have a 128K on-chip L2 cache, enabling it to be sold as a single chip with no module.

Surprisingly, Intel also plans to introduce a 300-MHz mobile Pentium/MMX, but this product will come and go almost entirely within the first quarter. By the second quarter, Mobile Celeron will move up to 333 MHz, and the 300-MHz version will push Pentium/MMX out of the low end.

The existing mobile Pentium II product can't go beyond its current 300-MHz speed in a 0.25-micron process without exceeding the 10-W mobile power limit. Intel's solution is a chip code-named Dixon, which integrates a 256K L2 cache on the processor chip. Due out early in 1999 in the

|                   | Pentium II          | Celeron             |                       |                       |                       |  |

|-------------------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|--|

| Feature           | Deschutes           | Mendocino           | Katmai                | Coppermine            | Dixon                 |  |

| L2 cache          | 512K                | 128K                | 512K                  | 256K                  | 256K                  |  |

|                   | off-chip            | on-chip             | off-chip              | on-chip*              | on-chip               |  |

| Extensions        | MMX                 | MMX                 | MMX, KNI              | MMX, KNI              | MMX                   |  |

| Bus Speed (1H99)  | 100 MHz             | 66 MHz              | 100 MHz               | —                     | 66 MHz                |  |

| Bus Speed (2H99)* | 100 MHz             | 100 MHz             | 133 MHz               | 133 MHz               | 66 MHz                |  |

| Max CPU (1H99)    | 450 MHz             | 400 MHz             | 533 MHz               | —                     | 366 MHz               |  |

| Max CPU (2H99)*   | 450 MHz             | 450 MHz             | 533 MHz               | 667 MHz               | 366 MHz               |  |

| Market Focus      | Midrange            | Low Cost            | High End              | High End,<br>Mobile   | Mobile                |  |

| Slot 2 Version    | Xeon                | —                   | Tanner                | Cascades              | —                     |  |

| Transistors       | 7.5 million         | 19 million          | 9 million*            | 32 million*           | 30 million*           |  |

| Process           | 0.25 micron         | 0.25 micron         | 0.25 micron           | 0.18 micron           | 0.25 micron           |  |

| Die Size          | 131 mm <sup>2</sup> | 154 mm <sup>2</sup> | 140 mm <sup>2</sup> * | 130 mm <sup>2</sup> * | 185 mm <sup>2</sup> * |  |

| Mfg Cost*         | \$65                | \$55                | \$75                  | \$50                  | \$65                  |  |

| First Shipments   | 2Q98                | 3Q98                | 1Q99                  | 3Q99                  | 1Q99                  |  |

Table 1. Intel's processor offerings in 1999 will include five different variants on the CPU core that originally appeared in Klamath and now dominates the market in the form of Deschutes. tincludes L2 cache (Source: Intel, except \*MDR estimates)

form of a 333- and 366-MHz mobile Pentium II, Dixon will mark the debut of on-chip L2 cache in the Pentium II (not Celeron) line. Bringing the cache onto the chip reduces power consumption and enables the module to be eliminated, making it an ideal mobile solution.

From a technology perspective, Dixon could replace Deschutes throughout the Pentium II line, but Intel lacks the fab capacity to move the entire desktop market to on-chip L2 cache until it has ramped up its 0.18-micron process.

There won't be a mobile Katmai; in a 0.25-micron process, it is too power hungry. In the fall, however, Coppermine will give the mobile line a big boost. Thanks to the 1.5-V supply of the 0.18-micron process, this chip should be able to achieve 600 MHz while remaining below the 10-W threshold. Coppermine also could be the first processor to support Intel's Geyserville technology, which enables the CPU to switch to a higher supply voltage and speed when connected to AC power.

#### Xeon Line Targets Servers

In addition to expanding at the low end with Celeron, Intel added a new high-end product this year: Pentium II Xeon. The initial Xeon processors use the same Deschutes CPU as other Pentium II processors but package the chip in a Slot 2 module with Intel-built SRAM chips for the L2 cache. Unlike Pentium II caches, which run at half the processor speed, the Xeon L2 cache runs at the full CPU rate. In addition to the 512K size common to Pentium II, Xeon modules are available in cache sizes of 1M and 2M.

Intel will introduce a Slot 2 (Xeon) version of Katmai, code-named Tanner, early in 1999. As with the initial Xeon processors, Tanner will use the same CPU chip as the standard Pentium II but with fast custom SRAMs for the L2 cache. The Xeon line will get another upgrade in the fall with Cascades, the Slot 2 version of Coppermine. Unlike previous Xeon parts, Cascades will have an on-chip L2 cache, eliminating the external SRAMs. For the first time, the Xeon line will use different CPU silicon than the mainstream line; Cascades will have a larger on-chip L2 cache than Coppermine (512K and 1M versions, compared with 256K for Coppermine).

#### AMD Establishes Strong Number-Two Position

Table 2 shows the diversity of chips that will be available from Intel's competitors in 1999. Of the Intel alternatives, AMD has the clear lead in clock speed; Rise and IDT trail the pack, though IDT has a design well under way that is intended to dramatically increase its clock speed.

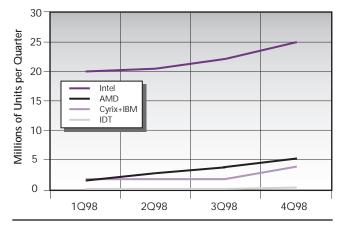

In 1997, AMD was neck-and-neck with Cyrix/IBM in x86 shipments. During 1998, however, AMD pulled clearly into the lead: not only did it ship many more units than Cyrix during the year, as Figure 2 shows, but it also moved to higher speed grades and achieved a higher ASP. Although AMD is still far short of its 30% market-share goal, it made great strides: after achieving a unit share of about 8% in 1997, it reached about 15% on a quarterly basis by the end of 1998 (12% averaged over all of 1998).

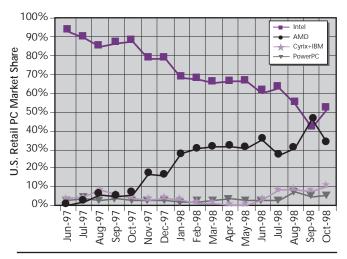

A key element in AMD's market-share gain was its tremendous strength in the U.S. retail channel, which Figure 3 illustrates. PCs based on AMD's processors began taking off in the channel in late 1997, and they even briefly exceeded Intel's market share in this channel. AMD now needs to replicate this success in other channels.

AMD's success is especially remarkable considering the difficulties the company faced earlier in the year. The transition from the 0.35- to 0.25-micron process in Fab 25 was difficult, with yields dropping to unacceptable levels. It was not until well into the second quarter that AMD was able to fully ramp up production in Fab 25, slowing the increase in K6 volume. By midyear, AMD had the fab running well and began cranking out K6-2 processors. Sources indicate AMD reached an annualized rate of more than 20 million units in 4Q98, up from 6 million at the start of the year.

AMD announced a foundry arrangement with IBM early in 1998 and originally expected to be selling IBMproduced K6-family processors by now. So far, however,

|                          | AMD                |                     | Cyrix               |                    | IDT                  |                    |                    | Rise               |                     |                     |                       |

|--------------------------|--------------------|---------------------|---------------------|--------------------|----------------------|--------------------|--------------------|--------------------|---------------------|---------------------|-----------------------|

|                          | K6-2               | K6-3                | K7                  | MII                | Jedi                 | MXi                | WinChip 2          | WinChip 3          | WinChip 4           | mP6                 | mP6 II                |

| Bus                      | Socket 7           | Socket 7            | Slot A              | Socket 7           | Socket 7             | PCI/SDRAM          | Socket 7           | Socket 7           | Socket 7            | Socket 7            | Socket 7              |

| Bus Speed                | 100 MHz            | 100 MHz             | 200 MHz             | 100 MHz            | 100 MHz              | 33/133             | 100 MHz            | 100 MHz            | 100 MHz             | 100 MHz             | 100 MHz               |

| L1 Cache                 | 64K                | 64K                 | 128K                | 64K                | 64K                  | 64K                | 64K                | 128K               | 128K                | 16K                 | 16K                   |

| L2 Cache                 | off-chip           | 256K                | off-chip            | off-chip           | off-chip             | none               | off-chip           | off-chip           | off-chip            | off-chip            | 256K                  |

| x86 Issue Rate           | 2 inst             | 2 inst              | 3 inst              | 2 inst             | 2 inst               | 2 inst             | 1 (2 MMX)          | 1 (2 MMX)          | 2 inst              | 3 inst              | 3 inst                |

| Max CPU<br>Speed (1H99)  | 450 MHz            | 500 MHz             | —                   | PR366<br>(300 MHz) | PR400<br>(350 MHz)   | 333 MHz            | 266 MHz            | 300 MHz            | —                   | PR266<br>(200 MHz)  | PR300<br>(233 MHz)    |

| Max CPU<br>Speed (2H99)* | 500 MHz            | 600 MHz             | 600 MHz             | PR400<br>(350 MHz) | PR450<br>(400 MHz)   | 366 MHz            | 300 MHz            | 333 MHz            | 500 MHz             | t                   | †                     |

| Transistors              | 9.3 million        | 21.3 million        | 22 million          | 6.5 million        | 7 million*           | 9 million          | 5.9 million        | 10 million         | 11.5 million        | 3.6 million         | 17.4 million          |

| Process                  | 0.25µ 5M           | 0.25µ 5M            | 0.25µ 5M            | 0.25µ 5M           | 0.18µ 5M             | 0.18µ 5M           | 0.25µ 5M           | 0.25µ 5M           | 0.25µ 6M            | 0.25µ 5M            | 0.25µ 5M              |

| Die Size                 | 78 mm <sup>2</sup> | 118 mm <sup>2</sup> | 184 mm <sup>2</sup> | 88 mm <sup>2</sup> | 90 mm <sup>2</sup> * | 90 mm <sup>2</sup> | 58 mm <sup>2</sup> | 75 mm <sup>2</sup> | 100 mm <sup>2</sup> | 107 mm <sup>2</sup> | 170 mm <sup>2</sup> * |

| Mfg Cost*                | \$35               | \$45                | \$105               | \$35               | \$45                 | \$65               | \$25               | \$30               | \$40                | \$45                | \$70                  |

| First Shipments          | 2Q98               | 1Q99                | 2Q99                | 2Q98               | 2Q99                 | 2Q99               | 4Q98               | 2Q99               | 4Q99                | 12/98               | 1H99                  |

Table 2. Although most of the products are focused around the Socket 7 interface, the various Intel alternative offerings show a range of CPU styles, cache architectures, speeds, and die sizes. †not enough information to predict (Source: vendors, except \*MDR estimates)

AMD has decided not to begin manufacturing at IBM, in the belief that its capacity at Fab 25 is ramping up at approximately the same rate as AMD's market share.

## Building on the K6 Core

AMD's fate in 1999 lies squarely in the hands of the K6-3, the third member of the K6 family. Adding a 256K on-chip cache to the K6-2 will enable the K6-3 (a.k.a. Sharptooth) to deliver a big performance boost. This design eliminates the major disadvantage of the Socket 7 architecture—limited cache bandwidth—and will make the chip a potent competitor not only for Intel's Mendocino (Celeron) but also for Pentium II and Katmai. Intel will seek to distinguish its products on the basis of KNI and higher clock speeds.

AMD built the first K6-3 chips early in 1998, but the chip's die size made it unattractive to put into production. AMD has been production limited, so the larger die—118 mm<sup>2</sup> vs. 78 mm<sup>2</sup> for the K6-2—would have required a cut in unit shipments. AMD has been steadily ramping up Fab 25, and in 1999 the company expects to have enough additional capacity to begin shipping the K6-3 in volume.

With the K6-2/400, AMD is only one speed grade behind Intel's top-of-the-line Pentium II-450. AMD has added two grades between 350 and 400. The K6-2/366, with a 66-MHz bus, provides an upgrade for 66-MHz motherboards and matches what will be a popular Celeron clock speed. A 380-MHz version runs with a 95-MHz bus and delivers a noticeable performance boost over the 366-MHz version (mostly due to the faster bus) for a small cost increase, creating a "premium" alternative to Intel's Celeron-366. AMD plans to ship 450-MHz K6-2 and K6-3 processors in 1Q99, with 500 MHz appearing in the second quarter.

In its 0.18-micron process, which AMD expects to begin ramping up late in 1999, the K6-3 should run at over 600 MHz, and its die size will be less than 75 mm<sup>2</sup>. At this size, the MDR Cost Model estimates that AMD's cost will be about \$45. Although the Socket 7 market will be in steep decline by the time the part ramps up in 0.18-micron technology, it could remain viable in the economy segment.

AMD plans to offer both the K6-2 and K6-3 throughout 1999. The K6-2, positioned against Celeron, will offer the lowest price at a given speed, appealing to buyers who focus on MHz and want the least expensive system. The K6-3, positioned against Pentium II and Katmai, will serve higher price points.

#### Charting Its Own Course: the AMD K7

While AMD's fate in 1999 will be determined primarily by the K6-3, the debut of the K7 will set the stage for that chip's move into the mainstream in 2000. AMD expects to sell a few million K7 processors in the second half of 1999, built in the same 0.25-micron process as the K6-2 and K6-3; volume should increase dramatically in 2000 with the shift to a 0.18micron process. With the K6-3 up against Katmai, AMD will position the K7 against Coppermine.

Figure 2. Quarterly shipments for each of the x86 PC processor suppliers showed steady growth through the year, with AMD making the biggest percentage gain. (Source: MDR estimates)

If the K7 lives up to its promises, it will dramatically change AMD's role in the market. Should the chip meet or beat the performance of Intel's Katmai, which seems quite possible, AMD would, for the first time, have a performance leadership role. If system makers had to use an AMD processor to deliver the highest performance points, it would be harder for holdouts like Dell and Gateway to remain entirely loyal to Intel. The K7 also promises to earn the highest prices AMD has received in many years for PC processors.

The K7 is a landmark processor in another respect: it is AMD's first design that does not follow an Intel bus and pinout. Having given up, as part of its Intel patent crosslicense agreement, the ability to use Intel interfaces beyond Socket 7, AMD had to switch to something else for the K7. Rather than invent a new bus, AMD chose something that already existed: Digital's (now Compaq's) EV6 (21264) bus. Dirk Meyer, the K7's design manager, previously worked at Digital designing Alpha processors, so he knew the bus. Dig-

**Figure 3.** In the U.S. retail market (about 11% of worldwide PC sales), AMD's share took off and reached nearly 50% in September, briefly eclipsing Intel's shipments in this channel. (Source: ZD Market Intelligence)

ital was thrilled to give the bus design to AMD because the K7 will spawn far more system-logic chip sets, at lower prices, than Alpha alone could ever have done.

The K7 will be packaged in what AMD calls Slot A: a module the size of a Slot 1 module and with a Slot 1 physical connector but with an entirely different bus (the EV6 bus). Like Pentium II, the module will include L2 cache RAMs connected to the processor via a backside bus; AMD plans to support L2 caches of up to 8M.

The 64-bit-wide Slot A bus runs at 200 MHz, delivering 1.6 Gbytes/s. (A P6 bus, even at 133 MHz, delivers only 1 Gbyte/s.) Using clock forwarding and point-to-point connections, the EV6 bus design can support even higher speeds; it is specified for operation up to 333 MHz.

With a non-Intel bus, AMD faces a far greater challenge than ever before to supply all the chip-set and motherboard infrastructure for its processors. In the past year, AMD succeeded in creating a 100-MHz "Super" Socket 7 infrastructure with AGP to support the K6-2, and the chip-set industry has found AMD to be a good partner. Now AMD needs to do the same with the more complex Slot A bus.

With the K7 and its successors, AMD will be driving its own infrastructure, including the system architecture. To the degree it can outdesign Intel in this arena, it could provide another dimension for differentiation. The challenge is substantial, however, and the price of failure high: if the K7 infrastructure doesn't keep up with Intel's, the processor will be crippled.

AMD demonstrated a K7 running with an AMD chip set at Comdex last month, and the company plans to deliver chip sets along with processors in 2Q99. The initial chip set will use SDRAM, but AMD plans to ship a Direct Rambus chip set by year end. VIA and ALi have proclaimed their intent to offer chip sets for the K7—an important sign of support. Other companies are rumored to be working on multiprocessor chip sets.

AMD has demonstrated a K7 running at 500 MHz, but it did not disclose any performance figures. If AMD is able to produce the chip at this speed and higher, if the core delivers on its promise of better per-clock performance than Katmai, and if the infrastructure support is ready, AMD's position could be very strong by the end of 1999.

To reach high volume, AMD needs to shrink the 184mm<sup>2</sup> K7 using its 0.18-micron process, making the shift to that process is critical to AMD's success. AMD might leap ahead of Intel's Katmai with the K7, only to be surpassed by Intel's Coppermine. With its 0.18-micron process, AMD could again regain the lead, to be leapfrogged once more by Intel's next-generation processor, Willamette, in 2000.

AMD's track record with new processes is not reassuring, however, and it also has another small item to deal with: a new fab in Dresden, Germany, which will begin pilot production early in 1999. The Dresden plant (Fab 30) will run a copper 0.18-micron process, while Fab 25 will stick with aluminum. Dresden will thus give AMD a second performance boost, expected in 1H00, after the first switch to 0.18-micron in Fab 25.

AMD says all its future PC processors will include 3DNow, but the company is considering whether to add KNI as well (which seems inevitable). A "K7-2" with KNI and an on-chip L2 cache seems a natural product for 2000. When AMD makes the switch to on-chip L2 cache for the K7 family, it will have to establish a new socket: the EV6-bus equivalent of Intel's Socket 370.

#### K6 Family Going Mobile

For years, AMD has been blocked from the mobile market by the high power consumption of its processors. With the 0.25-micron K6, AMD has been able to enter the notebook market, and it has gained design wins at Compaq and at Packard-Bell NEC. With clock speeds up to 300 MHz, the mobile K6 matches Intel's fastest mobile clock speed, and it is far less expensive. It is unquestionably weaker than Intel's offerings on FP- and MMX-intensive tasks, but that compromise is acceptable for many notebook users.

In 1999, AMD plans to step up its attack on the mobile market. Mobile versions of the K6-2 and K6-3 are both due in 1Q99, at clock speeds of at least 333 MHz. The K6-3 should be an outstanding mobile chip, especially after it is shrunk to the 0.18-micron process late in the year (which will reduce power consumption and enable higher speeds). AMD expects Socket 7 notebooks to shift to the Super 7 platform AMD has established for the desktop, with a 100-MHz bus and AGP.

#### Cyrix Strategy Evolves With National

The past year has been a difficult one for Cyrix. The company rebranded its 6x86MX as the MII but did not introduce any new products other than speed grades. The MII's top grade in 3Q98 was 300, reaching only 333 in 4Q98. In addition, Cyrix's parts are "performance rated": the MII-300 runs at 233 MHz but delivers Winstone performance comparable to that of a Pentium II-300. On applications that use much FP or MMX code, however, the MII falls far short of Pentium II. This weaker performance profile and lower clock speed have forced Cyrix to sell its chips at lower prices than AMD. Thus, Cyrix's processors have been most successful in the least expensive PCs, which today include models as low as \$399 but more typically \$599 to \$799, while AMD's K6-2 appears more frequently in PCs at \$799 and up.

Another factor that suppressed MII prices was competition with IBM; in many cases, Cyrix and IBM fought for the same customers with the same product. In September, National bought out IBM's remaining rights under the contract between the two companies to get IBM out of the MII business. IBM continued to serve a few key accounts through the end of 1998—in fact, it shipped more processors in its final two quarters than ever before. But IBM is now out of the x86 PC processor business (at least temporarily), serving Cyrix only as a foundry in limited volume. Cyrix built about 75% of its MII processors at National's South Portland, Maine, fab in 4Q98. This fab is only one-third equipped; it is currently capable of producing 10,000 wafers/month.

The MediaGX, which helped trigger the sub-\$1,000 PC phenomenon in 1997, largely disappeared from the PC market in 1998. It continues to find success in Windows terminals, point-of-sale devices, and embedded PC applications. Cyrix demonstrated at Comdex a prototype WebPad (a tablet for Web access) based on the MediaGX. This category of device ultimately will be quite significant, and Cyrix's pioneering prototype could help the MediaGX, or it successors, play an important role in this emerging segment.

Following National's acquisition of Cyrix in August 1997, the companies struggled to craft a joint strategy. National initially focused all its future plans on single-chip solutions for information appliances, seeking a rapidly growing market where Intel was not a direct competitor. While this is a fine vision, the appliance market is going to be too small in the next year or two to sustain National's efforts. So after initially saying that its next-generation CPU cores, Cayenne and Jalapeno, would be offered only as part of integrated MediaGX-style processors, Cyrix now plans to pursue both strategies: integrated processors for information appliances and nontraditional PCs as well as standard-pinout processors for conventional PCs.

#### PC Processors Pay the Bills

Cyrix plans to begin volume shipments of the MII-350, running at 270 MHz with a 90-MHz bus, in 1Q99. The MII-366, a 300-MHz core with a 100-MHz bus, is planned for 2Q99, with the MII-400 (350 MHz) following in 3Q99.

Cyrix now plans to introduce a Socket 7 version of the Cayenne core, code-named Jedi, in 2Q99, at clock speeds of 350 and 400 MHz (PR ratings of 400 and 450). This core, a third-generation refinement of the 6x86, was previously slated to appear only in the MXi, a MediaGX-style processor with a 3D graphics unit. Jedi will give Cyrix an MII family member with stronger FP and MMX performance as well as 3DNow capability. This chip is just an interim product, however; an on-chip L2 cache is needed to keep pace with Intel's Mendocino and AMD's K6-3, especially as clock speeds increase.

Cyrix declines to detail its plans for the standard-socket product line beyond Jedi, but a Cayenne processor with onchip L2 seems like the next step. Given Cyrix's avowed belief that there are no technical or legal barriers to implementing the P6 bus on its chips, and its stated commitment to provide the interfaces its customers demand, we expect Cyrix to introduce a Socket-370 version of Cayenne with an on-chip L2 in 2H99. Cyrix's next-generation core, Jalapeno, could be at the heart of a similarly configured device in 2000.

Cyrix has not yet been able to reach the mobile power range with the MII. Early in 1999, Cyrix plans to begin shipping its first mobile MII, running at 200 MHz and marketed as MII-266, with a 66-MHz bus. Using a 2.2-V supply, the part dissipates 9 W. In the second quarter, an MII-300 is planned, running at 233 MHz. Initial production of the mobile chips will come from IBM, now serving only as a foundry, using its 0.25-micron CMOS-6X3 process. National also plans to build mobile chips in its 0.18-micron CMOS-9 process.

#### Integrated Processors Seek New Markets

Cyrix's MediaGX has found its role not in PCs but in devices with embedded PCs. Cyrix shipped half a million units in 4Q98, at an average selling price probably below \$30. The MediaGX (which gained MMX capability in early 1998) is now shipping at 266 MHz; a final speed upgrade to 300 MHz is due in 1Q99.

The MXi, due to ship in April, will give the integrated line a big boost, offering a much faster CPU core (Cayenne) and a 3D graphics unit. This chip has been delayed, in part, by a switch to National's CMOS-9 process; the die was too large in CMOS-8.

A year after the MXi's debut, the M3 will upgrade the CPU core again (with Jalapeno), add a 256K on-chip L2 cache, and provide a two-channel Direct RDRAM interface. This performance-oriented integrated line is aimed at "convergence devices": consumer multimedia products that benefit from PC compatibility, such as a set-top DVD box that runs PC 3D games. In the mainstream desktop market, the MXi's fixed configuration and lack of L2 cache are likely to keep it from playing a major role. In notebooks, however, it could be more attractive.

At the same time, Cyrix is developing a separate product line that delivers less performance but higher integration. The company's first "PC on a chip" is due in mid-1999, based on the MediaGX core. Such high-integration products, which integrate the south bridge and all digital I/O functions, will continue to lag the less integrated parts by a year or so; an MXi-based single-chip PC is due in 2000.

#### IDT Serving Developing Countries

IDT began shipping its WinChip at the tail end of 1997. Its volume has ramped slowly, achieving 500,000 units in the first three quarters of 1998 and about 350,000 in the fourth quarter, ending the year at a run rate of just over 1% of the market. After initially focusing on U.S. resellers and shipping most of its early chips to Evergreen Technology as Pentium upgrade processors, IDT shifted its focus by midyear to China and Europe. In these markets, the chip's low price—less than \$40, on average—outweighs its limited clock speed and weak FP and MMX performance. WinChip's top speed is 240 MHz, using a 60-MHz bus.

WinChip 2, which began sampling midyear, adds a number of enhancements: 3DNow, dual-issue MMX, a faster floating-point unit, and several more subtle enhancements designed to boost performance. Unfortunately, this chip was slated to be produced initially in IDT's Fab 3 in San Jose, a 150-mm plant that IDT decided to shut down just as WinChip 2 was ready for production. The shift to IDT's new Fab 4 in Hillsboro, Oregon, delayed WinChip 2 production

#### x86 Year in Review

Intel rolled out Celeron with Covington (3/30/98, p. 1) (4/20/98, p. 14) and boosted it to 300 MHz (6/1/98, p. 4). Mendocino gave the Celeron line a big boost (8/24/98, p. 1). Intel disclosed plans for Socket 370 for future Celeron processors (7/13/98, p. 4).

Intel raised Pentium II clock speeds and added mobile Pentium II processors (4/20/98, p. 14). The mobile line reached 300 MHz (9/14/98, p. 5). Intel is developing a new mobile technology called Geyserville (3/30/98, p. 4).

The FTC filed suit against Intel (6/22/98, p. 8), alleging anticompetitive behavior.

Intel made especially deep and frequent price cuts (1/26/98, p. 4) (3/30/98, p. 5) (6/22/98, p. 5) (8/3/98, p. 4) (9/14/98, p. 4) (10/26/98, p. 5).

Intel shipped an OverDrive processor for Pentium Pro systems (9/14/98, p. 5) and said it doesn't plan future OverDrive processors.

Intel disclosed an overview of the Katmai New Instructions (10/5/98, p. 1) but kept the details secret.

Intel laid out its high-end processor roadmap, including the first details on Willamette (10/26/98, p. 16).

AMD announced a foundry agreement with IBM (3/9/98, p. 4) but chose not to use IBM after solving its production problems at Fab 25 (4/20/98, p. 5).

AMD rolled out the K6-2 (6/1/98, p. 16), marking the debut of 3DNow (6/1/98, p. 18). The K6-2 hit 350 MHz (9/14/98, p. 15) and then 400 MHz (12/7/98, p. 4).

AMD announced its first mobile K6 (10/5/98, p. 4). AMD disclosed the design of the K7 (10/26/98, p. 1).

**Cyrix** renamed the 6x86MX the MII (4/20/98, p. 5). It reached a performance level of PR333 (6/1/98, p. 4). Cyrix scored major design wins at Packard Bell (6/1/98, p. 4), Compaq, and IBM (11/16/98, p. 5).

Cyrix disclosed the Jalapeno core and the M3 integrated processor (11/16/98, p. 24).

Cyrix decided to continue developing processors that are Intel pin-compatible (12/7/98, p. 4).

National renewed its patent cross-license with Intel (2/16/98, p. 5) and announced plans for a single-chip PC (4/20/98, p. 4).

National ended Cyrix's agreement with IBM, putting IBM out of the PC processor market, at least temporarily (10/5/98, p. 4).

IDT signed a foundry agreement with IBM (3/30/98, p. 5) but hasn't used it.

IDT announced the WinChip 2 (6/1/98, p. 1) and laid out a roadmap to the WinChip 3 and WinChip 4 (12/7/98, p. 18).

Rise Technology launched its mP6 (11/16/98, p. 1). Transmeta remained quiet but was issued a patent that exposed some of its technology (12/7/98, p. 9). by several months; fewer than 50,000 chips will ship this year. In the first half of 1999, however, IDT expects to convert primarily to WinChip 2.

Even though it has yet to ramp up production, IDT is sampling a revision of WinChip 2, version A, which adds fractional bus multipliers. This design goes beyond the halfstep used by most other chips to offer one-third steps. This feature enables the chip to use a 100-MHz bus while running at 233 or 266 MHz. The increased bus bandwidth will help the chip compete well against other processors at this speed, despite its lack of superscalar execution (except for MMX). In 1999, however, these speed grades will be of interest only in the most cost-sensitive markets.

The WinChip family will get a small boost from the WinChip 3 (previously called the WinChip 2+), which doubles the L1 caches to 128K total. IDT estimates the performance boost from this enhancement, due in 2Q99, to be about 8% on Winstone. IDT expects to make a major push into notebook computers with the WinChip 3. WinChip 4 (formerly called WinChip 3), due in the fourth quarter, should deliver a much bigger boost; it is an entirely new design with a deeper pipeline that IDT expects to run at 400 to 500 MHz.

IDT signed an agreement with IBM for foundry services early in the year, and it said then that production would begin in the fourth quarter. Apparently the demand has not been so strong that this seems worthwhile, however; IBM has not yet begun production of WinChip. One problem for IDT may be that, at the low prices it must sell the chips, it is hard to cover the additional profit margin of an outside foundry. If demand increases significantly, however, IDT is likely to begin building chips at IBM. IDT plans to use IBM for the initial production of WinChip 4, where IBM's more advanced technology will pay off in higher clock speeds.

Like Cyrix, IDT has not announced any plans for P6bus chips but has said it will provide the interfaces its customers demand. A Socket 370 version of WinChip 4 with an on-chip L2 cache would be a natural follow-on in 2000.

IDT has backed away from its earlier plan to offer a version of WinChip 3 with an integrated north bridge. Instead, IDT plans to work with partners that have chip-set and graphics designs to create integrated products.

#### Rise Joins the Low-End Battle

The latest entrant in the x86 business is Rise Technology, which disclosed its mP6 at Microprocessor Forum in October and is just now moving from sampling to production. The first chip has a maximum clock speed of 200 MHz but is PR rated at 266. This puts it at the bottom of the range in today's PC market; only IDT suffers from as severe a clockspeed limitation. Rise is hoping for success in the emerging sub-\$1,000 notebook computer category; because Intel's mobile speeds are lower than on the desktop, the Rise chips are more competitive in that arena.

#### 8 🔷 X86 COMPETITION THRIVING

Although Rise and IDT are both focused on emerging markets for very low cost PCs, by necessity as much as by choice, they have taken very different approaches in their chip designs. IDT's WinChip is a single-issue design (with dual-issue MMX in the WinChip 2), while Rise's mP6 can decode and execute up to three instructions per clock cycle. It is still an in-order design, however, and its L1 cache is a puny 16K. And at 107 mm<sup>2</sup> in a 0.25-micron process, Rise's chip is large for a low-cost processor; its heft is apparently because of the multiple-issue design and extensive use of standard-cell layout.

So far, there have been no independent appraisals of the mP6's performance. Rise's own tests showed the chip to deliver better multimedia performance than IDT's WinChip, its main low-cost competitor, but the emerging WinChip 2 could leave Rise at the bottom of the pack. Being the number-five supplier in this market is going to be tough.

Rise plans to introduce the mP6 II, with a 256K onchip L2 cache, in 1H99. This should give the family a big performance boost, especially if Rise is able to increase the clock speed significantly, but it may do no more than keep up with advances in the processor landscape. With 256K of cache added to the portly mP6 core, the mP6 II will require 0.18-micron technology to achieve a reasonable die size.

Rise has not identified its foundry partner, but sources indicate UMC is building the mP6. It is not clear how to reconcile this with Rise's statement that it will use a foundry that has an Intel patent license, which UMC does not. (UMC was briefly in the PC processor business with another lowend design in 1994 and 1995 but withdrew in part because of a legal attack from Intel.) The licensed candidates include STMicroelectronics (formerly SGS Thomson), IBM, and Texas Instruments.

#### IBM and STMicroelectronics Out of PCs?

IBM Microelectronics and STMicroelectronics, both former partners of Cyrix, are now working together on a line of highly integrated processors for information appliances. STM currently offers its ST PC, based on a Cyrix 486 core. The next-generation CPU core will come from Metaflow, a San Diego-based design house that STM acquired from Hyundai in mid-1997. Products based on the Metaflow core should appear in 1999.

Whether STM sticks to the information-appliance market or rejoins the PC processor market as well remains to be seen. If Metaflow can produce a core that would be competitive in PCs, it will be tempting for STM to offer the chips in that higher-price market.

IBM almost surely will re-enter the PC processor market, but its strategy is not yet clear. IBM is rumored to be involved with Transmeta and could be the foundry and marketing partner for its forthcoming processor. IBM could make and sell Rise's chip, but its performance isn't high enough to make it very attractive for IBM.

#### Transmeta Still Keeping Quiet

Transmeta remains one of Silicon Valley's most secretive yet well-known startups. The first public glimmer of its technology came to light in a recently issued patent, which describes a VLIW processor that works with a software-translation layer to achieve x86 compatibility.

Until more is known about Transmeta's offering, it is impossible to say how significant it will be—or even if it will attack the mainstream PC market. As the sixth player in the PC processor market, it would be entering a crowded field, and its software-translation approach could make buyers wary. All that is clear is that a large investment has been made in the company, and it has assembled a talented team.

#### Can Intel's Competitors Succeed?

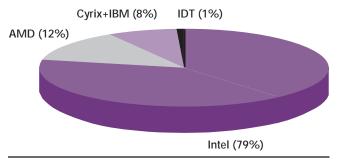

It is ironic that Intel is facing an FTC investigation at the same time that its competition is growing rapidly. Figure 4 shows Intel's unit market share for 1998. Although Intel clearly remains dominant, AMD and Cyrix have shown that it is possible for other companies to become major suppliers in certain segments (i.e., U.S. retail)—and IDT and Rise have shown that the barriers to entry are not overwhelming. The FTC must determine whether Intel's dominance is sufficiently great that it should be regulated as a monopoly, an assertion Intel will fight to the bitter end. If the FTC prevails on this fundamental issue, it will then have to decide which of Intel's business practices merit scrutiny. Although not a happy situation for Intel, it does not appear to be among the larger challenges the company faces in 1999.

So far, Intel's competitors have shown they can capture some market share, but not that they can serve it profitably or maintain their growth; successes have been transient. If AMD and Cyrix can execute on their plans, they are poised to achieve profitability in 1999. No ground will be easily held, however; Intel has been roused by its market-share loss and will fight back more vigorously, with stronger products, in 1999. The coming year will show whether AMD's and Cyrix's gains in 1998 were a trend or merely a blip.

The competitive landscape seems clearly stratified today, though shifts are inevitable. Intel is the only supplier for the fastest PCs and for nearly all x86 servers and work-

Figure 4. Although Intel's market share for 1998 x86 PC processor unit shipments remains overwhelming, AMD's slice is reaching a respectable size. (Source: MDR estimates)

stations, and it is the majority supplier in virtually all other segments. AMD covers all but the very high end of the mainstream PC market, including notebooks. Cyrix serves the economy-focused desktop segment, while IDT serves the minimum-cost international market.

In 1999, AMD, if successful in delivering on its plans, will compete across the full breadth of Intel's mobile and desktop product lines; in 2000, it might even address servers. Cyrix will remain focused on economy PCs, and it will attack the notebook space as well as the desktop. IDT hopes to move up to compete head-on with Cyrix, as does Rise. All the suppliers are hoping to make major gains in the mobile market, where Intel has had a pure monopoly for years and has established a high price umbrella. The emerging market for consumer notebooks provides a natural opportunity for suppliers of lower-cost mobile microprocessors.

The commercial PC market has remained elusive for Intel's competitors. Some "consumer" PCs are purchased by small businesses and home-office users, but the major PC makers have not used non-Intel processors in their commercial PC lines. Breaking into this market is a key challenge in 1999, especially for AMD, whose ambitions require it to succeed in multiple segments.

#### Room for Everyone?

In the second half of 1998, the demand for PC processors exceeded the supply—a situation that virtually guarantees that multiple suppliers can prosper. It seems likely, however, that during 1999 supply will catch up with and possibly over-take demand.

MDR projects 1999 shipments of about 125 million x86 processors for PCs. The 80% or so that Intel serves, at an average selling price (ASP) of around \$220, is worth more than \$20 billion. The remaining 20%, divided among Intel's competitors at an ASP of perhaps \$80, amounts to around \$2 billion.

The combined aspirations of the companies are far grander than this, however, and the non-Intel pie must grow well beyond \$2 billion if both AMD and Cyrix are to meet their goals. AMD projects that it will ship at least 20 million K6-family processors and 3 million K7 processors in 1999. Assuming an ASP of \$100 yields nearly \$2.3 billion in revenue, which would make AMD nicely profitable.

Cyrix expects to ship more than 12 million processors in 1999, about 9 million of which will be for PCs. At an ASP of perhaps \$60, the PC processors would yield just half a billion dollars in revenue. If AMD and Cyrix reach their goals, and IDT, Rise, and others ship perhaps 5 million units, the total non-Intel shipments would be around 37 million units, for a total revenue of approximately \$3 billion.

MDR estimates that Intel will ship nearly 100 million PC processors in 1999, making a grand total of more than 135 million x86 PC processors from all vendors. This figure appears to overshoot the total market, so unless there is exceptional market growth in 1999, some of these projections aren't going to be met. As long as the PC market continues to grow rapidly, there is room for three or four PC processor suppliers; whether there is room for five or six or seven is much less clear.

A nicely stratified market could allow many suppliers to coexist, but this situation is not likely to last. As AMD dramatically increases its production volume, Intel continues to add new plants, the entire industry moves to 0.18micron processes, and new suppliers enter the market, an oversupply situation seems likely—and the smaller suppliers could find life very difficult. AMD alone expects to be able to manufacture 400,000 0.18-micron wafers in 2001 enough to produce about 60 million processors the size of the K6-3.

Today, AMD is able to sell out its available fab capacity while focusing on higher speed grades. This leaves a market below AMD's, where Cyrix thrives. As Fab 25 ramps to full capacity and switches to 0.18 micron, and Fab 30 (Dresden) ramps up, AMD should have the capacity to serve the economy market as well. If this occurs, AMD is likely to become far more aggressive on price for its lower speed grades, making life much more difficult for Cyrix, IDT, and Rise.

Even Intel might attack the lower price points if its capacity gets ahead of market demand. Since the only real advantage of the competitors' chips has been price, Intel can take back market share whenever it wants by cutting its own prices. So far, it has been more profitable for Intel to leave the very low end market to others, and even to allow some of the mainstream market to be taken away.

With rapidly accelerating Celeron speeds, however, Intel appears to be fighting harder for the economy-PC market. Sources indicate Intel has also discounted its prices more aggressively than usual to regain design wins in low-cost systems, and the price floor at which Intel loses interest seems to be dropping. Should Intel become dramatically more aggressive on price, it would cause grief for AMD and all the way down the chain.

By early 2000, it is possible that Cyrix, IDT, and Rise will all have shifted to the Socket 370 infrastructure. Should this occur, the P6 bus would finally have replaced Socket 7 as a multivendor standard.

This scenario leaves AMD as the odd man out with its Slot A bus. If AMD can execute well, this situation could be a blessing in disguise, as it gets the company out of following Intel's designs at one more level. If AMD's K7 succeeds in delivering the industry's fastest PC processors, Intel's managers will have to think long and hard about how the K7 got the jump on Willamette.

Intel, of course, isn't going to take lightly the prospect of being beaten in the x86 performance game, nor is it going to give up the fast-growing economy segment. Faster, cheaper PC processors are the inevitable result.