# BIOS Writer's Guide: mP6 MICROPROCESSOR FOR WINDOWS SYSTEMS

Doc#: MKTBI6401.00 Version 1.0

All rights reserved. <sup>©</sup> 1999 Rise<sup>™</sup> Technology

Devices sold by Rise<sup>™</sup> Technology are covered by the warranty and patent indemnification provisions appearing in it's Terms of Sale only. Rise<sup>™</sup> Technology makes no warranty, express or implied or by description regarding information set forth herein or regarding the freedom of the described devices from patent infringement. Rise<sup>™</sup> Technology Company reserves the right to discontinue production and change specifications and prices at any time and without notice.

Rise<sup>™</sup> Technology assumes no responsibility for the use of any circuitry other than circuitry embodied in a Rise<sup>™</sup> Technology product. No other circuits, patents or licensees are implied.

Rise<sup>™</sup> Technology products are not authorized for use as components in life systems or as part of life support devices.

Products, brand and corporate names used in this publication are for identification purposes only and may be trademarks of their respective companies.

This document contains information about a product under development at Rise<sup>™</sup> Technology Company and is intended to assist in evaluating this product. This is not a released product and specifications are subject to change without notice.

# **Table of Contents**

| INTRODUCTION                                                                                                                                                                                              | 5                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| CPUID                                                                                                                                                                                                     | 5                   |

| CPU SPEED DETECTION                                                                                                                                                                                       | 6                   |

| PERFORMANCE RATING                                                                                                                                                                                        | 6                   |

| VERSION/STEPPING SPECIFIC CONFIGURATION                                                                                                                                                                   | 7                   |

| CONTROL REGISTER CR4                                                                                                                                                                                      | 8                   |

| RISE <sup>™</sup> mP6 <sup>™</sup> PROCESSOR RESET AND INIT STATES                                                                                                                                        | 8                   |

| SYSTEM MANAGEMENT MODE                                                                                                                                                                                    |                     |

| 8.1 SMM STATE—SAVE AREA 8.2 SMM INITIAL REGISTER VALUES 8.3 SMM REVISION IDENTIFIER 8.4 I/O INSTRUCTION RESTART 8.5 AUTO HALT RESTART 8.6 BACK—TO—BACK SMI INTERRURTS WHEN USING I/O INSTRUCTION RESTART. | 9<br>11<br>12<br>12 |

| APPENDIX A - MACHINE-SPECIFIC CODE FOR RISE <sup>™</sup> mP6 <sup>™</sup> CONFIGURATION SETTING                                                                                                           | .14                 |

# **List of Tables**

|          | CPUID RETURN VALUES WITH EAX == 0                                      |    |

|----------|------------------------------------------------------------------------|----|

|          | CPUID EAX RETURN VALUES WITH EAX == 1                                  | _  |

| _        | CPUID EDX RETURN VALUES WITH EAX == 1 PERFORMANCE RATING LOOKUP TABLE* | _  |

|          | RISE ™ mP6™ PROCESSOR ARCHITECTURAL STATE AFTER RESET OR INIT          |    |

|          | SMM STATE—SAVE AREA MAP                                                |    |

| TABLE 7. | REGISTER INITIALIZATION IN SMM                                         | 11 |

|          | SMM REVISION IDENTIFIER FIELDS                                         |    |

| TABLE 8. | SMM REVISION IDENTIFIER FIELDS                                         | 12 |

|          |                                                                        |    |

|          |                                                                        |    |

#### Introduction

The Rise<sup> $^{\text{M}}$ </sup>  $mP6^{^{\text{M}}}$  processor is a sixth generation processor optimized for low–power, high-performance multimedia Windows<sup> $^{\text{M}}$ </sup> applications. The innovative Rise  $^{\text{M}}$   $mP6^{^{\text{M}}}$  processor is the first superscalar, superpipelined, Pentium<sup> $^{\text{R}}$ </sup> MMX\* compatible processor featuring 3 integer units, 3–way superscalar MMX technology, and a fully pipelined floating point unit. The innovative circuitry of the Rise  $^{\text{M}}$   $mP6^{^{\text{M}}}$  processor maximizes processing per clock cycle while requiring minimal power consumption – providing an ideal choice for cost–effective, power–efficient desktop and mobile Windows\* 95, Windows\* 98, and Windows NT\* systems.

This document is intended for BIOS and operating system software developers and contains information required to implement system support for the Rise  $^{\text{TM}}$  processor.

#### **CPUID**

The CPUID instruction should be used to detect the Rise  ${}^{\text{TM}}$  processor and the model–specific features supported. Unsupported features should not be used by the BLOS, operating system, or by the application software. The Rise  ${}^{\text{TM}}$  processor return values for the CPUID instruction are shown in Tables 1 through 3. The Intel P55C processor return values are included in the tables for comparison.

When the BIOS identifies the processor, if the processor is a Rise

- mP6<sup>™</sup> processor, its name appears as "Rise(tm) mR6 (tm) xxx processor"

- mP6<sup>™</sup> II processor, its name appears as "Rise(tm) mP6 II(tm) xxx processor"

- where xxx is the rated performance number (refer to Table 4A or 4 B).

TABLE 1. CPUID RETURN VALUES WITH EAX == 0

| REGISTER    | Rise <sup>™</sup> <i>mP6</i> <sup>™</sup> | P55C         |

|-------------|-------------------------------------------|--------------|

| BAX         | 1                                         | 1            |

| EBX:ECX:EDX | RiseRiseRise                              | GenuineIntel |

TABLE 2. CPUID EAX RETURN VALUES WITH EAX == 1

| PROCESSOR                                       | [13:12]<br>Type ID | [11:8]<br>Family ID | [7:4]<br>Model ID | [3:0]<br>Stepping ID |

|-------------------------------------------------|--------------------|---------------------|-------------------|----------------------|

| Rise <sup>™</sup> mP6 <sup>™</sup> (0.25 um)    | 0                  | 5                   | 0                 | Varies               |

| Rise <sup>™</sup> mP6 <sup>™</sup> (0.18 um)    | 0                  | 5                   | 2                 | Varies               |

| Rise <sup>™</sup> mP6 <sup>™</sup> II (0.25 um) | 0                  | 5                   | 8                 | Varies               |

| Rise <sup>™</sup> mP6 <sup>™</sup> II (0.18 um) | 0                  | 5                   | 9                 | Varies               |

| P55C                                            | 0                  | 5                   | 4                 | Varies               |

TABLE 3. CPUID EDX RETURN VALUES WITH EAX == 1

| EDX Bits — Meaning                      | RISE <sup>™</sup> mP6 <sup>™</sup> | P55C            | Notes      |

|-----------------------------------------|------------------------------------|-----------------|------------|

| 0 — Floating Point Unit on Chip (FPU)   | 1                                  | 1               |            |

| 1 — VM86 Extensions (VME)               | 0                                  | 1               |            |

| 2 — Debugging Extensions (DE)           | 0                                  | 1               |            |

| 3 — Page Size Extensions (PSE)          | 0                                  | 0               |            |

| 4 — Time Stamp Counter (TSC)            | 1                                  | 1               |            |

| 5 — Model Specific Registers (MSR)      | 0                                  |                 |            |

| 6 — Physical Address Extensions (PAE)   | 0                                  | \(\frac{1}{2}\) |            |

| 7 — Machine Check Exception (MCE)       | 0                                  | \\\\\\          |            |

| 8 — CMPXCHG8B instruction (CX8)         | 0 ( )                              | 1               | <u>\_1</u> |

| 9 — APIC supported                      | 0                                  | ) >1            | 2          |

| 10:11 — RESERVED                        | ( / / /                            | <u> </u>        |            |

| 12 — Memory Type Range Registers (MTRR) | / 6/                               | 0               |            |

| 13 — PTE Global Flag (PGE)              | 0                                  | 0               |            |

| 14 — Machine Check Architecture (MCA)   | 0                                  | 0               |            |

| 15 — Conditional Move supported (CMOV)  | 0                                  | 0               |            |

| 16:22 — RESERVED                        | -                                  | -               |            |

| 23 — MMX supported                      | 1                                  | 1               |            |

| 24:31 — RESERVED                        | -                                  | -               |            |

#### Notes:

- The CMPXCHG8B instruction is supported and always enabled on the Rise<sup>™</sup>mP6<sup>™</sup> processor; however, as specified in an erratum for early versions of Windows NT\* 4.0, the default CPUID function bit is set to 0.

- Pentium processor multiprocessing capabilities are not supported on the Rise™ mP6™ processor.

# **CPU Speed Detection**

The Rise  $^{\text{TM}}$   $mP6^{\text{TM}}$  processor supports the Time Stamp Counter and the RDTSC instruction. BIOS algorithms may use this facility to measure timed operations for CPU speed detection. During system boot, BIOS detects and displays the speed/ratio for the processor.

# **Performance Rating**

A lookup table that references the processor operating frequency to a performance rating number should be incorporated into the speed detection algorithm. Tables 4A and 4B respectively list the current performance ratings of the Rise  $^{\text{TM}}$  mP6 $^{\text{TM}}$  processor and the Rise  $^{\text{TM}}$  mP6 $^{\text{TM}}$ II processor.

TABLE 4A. mP6<sup>™</sup> PERFORMANCE RATING LOOKUP TABLE\*

| Bus Speed | Bus Ratio | Rated Performance |

|-----------|-----------|-------------------|

| 66        | 2:1       | 133               |

| 75        | 2:1       | 150               |

| 83        | 2:1       | 166               |

| 95        | 2:1       | 233               |

| 100       | 2:1       | 266               |

| 95        | 2.5:1     | 333               |

| 100       | 2.5:1     | 366               |

| 95        | 3:1       | 380               |

| 100       | 3:1       | 400               |

| 95        | 3.5:1     | 433               |

| 100       | 3.5:(     | 466               |

TABLE 4B. mP6™ II PERFORMANCE RATING LOOKUP TABLE\*

| Bus Speed | Bus Ratio | Rated Performance |

|-----------|-----------|-------------------|

| 66        | 2:1       | 133               |

| 75        | 2:1       | 150               |

| 83        | 2:1       | 166               |

| 95        | 2:1       | 233               |

| (100)     | 2:1       | 266               |

| 95        | 2.5:1     | 333               |

| 100       | 2.5:1     | 366               |

| 95        | 3:1       | 380               |

| 100       | 3:1       | 400               |

| 95        | 3.5:1     | 433               |

| 100       | 3.5:1     | 466               |

<sup>\*</sup> Rated performance levels for the Rise <sup>™</sup> mP6<sup>™</sup> processors are based on the specified bus speeds and clock multipliers. Using different bus speeds and multipliers to achieve the same core frequency may not result in the same level of performance.

# **Version / Stepping Specific Configuration**

For the production version of the Rise  $^{\text{TM}}$  mP6 $^{\text{TM}}$  processor, no stepping–specific initialization is required.

#### **Control Register CR4**

The Pentium® processor introduced a new control register (CR4) for controlling many of its new model—specific architectural features. The Rise  $^{\text{TM}} PP6^{^{\text{TM}}}$  processor provides a CR4 register compatible with the Pentium processor; however, it does not implement all of the model—specific features that can be controlled through the CR4 register. The CPUID instruction described in Section 0 should be used to determine the features supported by the Rise  $^{\text{TM}} mP6^{^{\text{TM}}}$  processor.

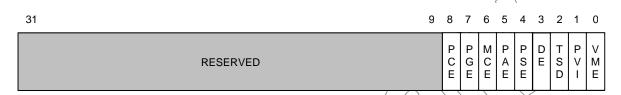

Figure 1. Control Register CR4 Bit Assignments

Bits VME, PVI, PSE, MCE, PGE and PCE are not supported on the Rise  $^{\text{TM}}P6^{\text{TM}}$  processor. These six bits return a value of 0 when read and although they cannot be set, no GP exception occurs on attempts to set them.

The **DE** bit is reserved on the Rise  ${}^{\text{TM}} mP6^{\text{TM}}$  processor. The return value when this bit is read and its response to attempts to set it are both undefined; however, no GP exception occurs on attempts to set or clear it.

# Rise<sup>™</sup> mP6<sup>™</sup> Processor Reset and Init States

The state of each register of the Rise mp6 processor after a RESET or INIT is listed in Table 5.

TABLE 5. RISE mp6 PROCESSOR ARCHITECTURAL STATE AFTER RESET OR INIT

| REGISTER                     | RESET State                                                                          | INIT State <sup>1</sup> | NOTES |

|------------------------------|--------------------------------------------------------------------------------------|-------------------------|-------|

| EFLAGS                       | 00000002H                                                                            |                         | 2     |

| EIP                          | 0000FFF0H                                                                            |                         |       |

| cs                           | Selector = F000H<br>Base = FFFF0000H<br>Limit = FFFFH<br>AR = Present, R/W, Accessed |                         |       |

| SS, DS, ES, FS, GS           | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W, Accessed |                         |       |

| EAX                          | 00000000H                                                                            |                         | 3     |

| EDX                          | 0000050xH                                                                            |                         | 4     |

| EBX, ECX, ESI, EDI, EBP, ESP | 00000000H                                                                            |                         |       |

| GDTR, IDTR                   | Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W                               |                         |       |

| LDTR, Task Register          | Selector = 0000H                                                                     |                         |       |

| REGISTER                | RESET State                                            | INIT State <sup>1</sup> | NOTES |

|-------------------------|--------------------------------------------------------|-------------------------|-------|

|                         | Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W |                         |       |

| FPU Stack ST7-ST0       | 00000000000000000000000000000000000000                 | Unchanged               |       |

| FPU Control Word        | 0040H                                                  | Unchanged               |       |

| FPU Status Word         | 0000H                                                  | Unchanged               | \     |

| FPU Tag Word            | 5555H                                                  | Unchanged               |       |

| FPU Instruction Pointer | 00000000000H                                           | Unchanged               | 1     |

| FPU Data Pointer        | 00000000000H                                           | Unchanged               |       |

| CR0                     | 60000010H                                              |                         | 5     |

| CR2, CR3, CR4           | 00000000Н                                              | $\wedge$                |       |

| DR7                     | 00000400H                                              |                         |       |

| DR6                     | FFFF0FF0H                                              |                         |       |

| DR0, DR1, DR2, DR3      | 00000000H                                              |                         |       |

| Data and Code Cache     | Invatid                                                | Unchanged               |       |

| TLBs                    | Invalid                                                | Invalid                 |       |

| TSC                     | (0)                                                    | Unchanged               |       |

#### Notes:

- 1. Unless otherwise specified, the INIT state is the same as the RESET state.

- 2. Software should not depend on the states of the 10 most significant bits of the EFLAGS register following a reset.

- 3. The EAX register contains the results of the Built In Self Test (BIST) when invoked. If EAX = 00000000H then BIST completed successfully. If EAX is non-zero then BIST failed.

- 4. The EDX register contains the Rise ™mP6™ processor identification and revision information.

- 5. The CD and NW flags are unchanged following INIT, bit 4 is set to 1, and all other bits are cleared.

### **System Management Mode**

The System Management Mode (SMM) of the Rise  $^{\text{TM}}P6^{\text{TM}}$  processor is functionally identical to that of the Pentium processor. SMM handlers should not rely on the availability of any Pentium processor model—specific registers or features that are not supported by the Rise  $^{\text{TM}}P6^{\text{TM}}$  processor. The CPUID instruction should be used to determine the model—specific features available.

#### 8.1 SMM State-Save Area

When the Rise<sup>™</sup>mP6<sup>™</sup> processor enters SMM, it writes the processor state information into the SMM state—save area of SMRAM. The SMM state—save map area is located in SMRAM between addresses [SMBASE + 8000H + 7FFFH] and [SMBASE + 8000H + 7E00H]. Table 6 lists the information contained within the SMM state—save area. Processor state information not listed in Table 6 is not automatically saved nor restored by the processor. It is the responsibility of the SMM handler to save and restore any additional state information that it alters during execution.

TABLE 6. SMM STATE-SAVE AREA MAP

| OFFSET<br>(Added to SMBASE + 8000H) | REGISTER                             | WRITABLE |

|-------------------------------------|--------------------------------------|----------|

| 7FFCH                               | CR0                                  | No       |

| 7FF8H                               | CR3                                  | No       |

| 7FF4H                               | EFLAGS                               | Yes      |

| 7FF0H                               | EIP                                  | Yes      |

| 7FECH                               | EDI                                  | Yes      |

| 7FE8H                               | ESI                                  | Yes      |

| 7FE4H                               | EBP                                  | Yes      |

| 7FE0H                               | ESP                                  | Yes      |

| 7FDCH                               | EBX                                  | Yes      |

| 7FD8H                               | EDX                                  | Yes      |

| 7FD4H                               | ECX                                  | Yes      |

| 7FD0H                               | EAX                                  | Yes      |

| 7FCCH                               | DR6                                  | No       |

| 7FC8H                               | DR7                                  | No       |

| 7FC4H                               | VR )                                 | No       |

| 7FC0H                               | LDTR Base                            | No       |

| 7FBCH                               | GS                                   | No       |

| 7FB8H                               | FS                                   | No       |

| 7FB4H                               | DS                                   | No       |

| 7FB0H                               | SS                                   | No       |

| <b>YFACH</b>                        | CS                                   | No       |

| 7FA8H                               | ES                                   | No       |

| 7FA7H – 7F98H                       | RESERVED                             | No       |

| 7F94H                               | IDT Base                             | No       |

| 7F92H                               | IDT Limit (Word)                     | No       |

| 7F91H – 7F8CH                       | RESERVED                             | No       |

| 7F88H                               | GDT Base                             | No       |

| 7F86H                               | GDT Limit (Word)                     | No       |

| 7F85H – 7F04H                       | RESERVED                             | No       |

| 7F02H                               | Auto HALT Restart Field (Word)       | Yes      |

| 7F00H                               | I/O Instruction Restart Field (Word) | Yes      |

| 7EFCH                               | SMM Revision Identifier Field        | No       |

| OFFSET<br>(Added to SMBASE + 8000H) | REGISTER                    | WRITABLE |

|-------------------------------------|-----------------------------|----------|

| 7EF8H                               | SMBASE Field                | Yes      |

| 7EF7H – 7EF4H                       | RESERVED                    | No       |

| 7EF0H                               | Restart EIP                 | No       |

| 7EEFH – 7EE8H                       | RESERVED                    | No       |

| 7EE4H                               | CR4                         | No       |

| 7EE0H                               | CR2                         | No       |

| 7ED8H                               | TSS Descriptor              | No       |

| 7ED0H                               | LDT Descriptor              | No       |

| 7EC8H                               | GS Descriptor               | No       |

| 7EC0H                               | FS Descriptor               | No       |

| 7EB8H                               | DS Descriptor               | No       |

| 7EB0H                               | SS Descriptor               | No       |

| 7EA8H                               | CS-Descriptor CS-Descriptor | No       |

| 7EA0H                               | ES Descriptor               | No       |

| 7E9FH – 7E00H                       | RESERVED                    | No       |

# 8.2 SMM Initial Register Values

The initial state of each processor register upon entry to SMM is listed in Table 7.

TABLE 7. REGISTER INITIALIZATION IN SMM

| REGISTER                     | INITIAL CONTENTS                                   | NOTES |

|------------------------------|----------------------------------------------------|-------|

| General-purpose registers    | Undefined                                          |       |

| EFLAGS                       | 00000002H                                          |       |

| EIP                          | 00008000H                                          |       |

| CS Selector                  | SMM Base shifted right 4 bits (default 3000H)      | 1     |

| CS Base                      | SMM Base (default 00030000H)                       | 1     |

| CS Limit                     | FFFFH (4 GBytes)                                   | 1     |

| DS, ES, FS, GS, SS Selectors | 0000H                                              | 1     |

| DS, ES, FS, GS, SS Bases     | 00000000Н                                          | 1     |

| DS, ES, FS, GS, SS Limits    | FFFFH (4 GBytes)                                   | 1     |

| CR0                          | Bits 0, 2, 3 and 31 are cleared; others unmodified |       |

| DR6                          | Unpredictable                                      |       |

| DR7                          | 00000400H                                          |       |

Notes:

1. Attr=Preset. R/W. Accessed, G=1, D=0, AVL=0, DPL=0

#### 8.3 SMM Revision Identifier

The SMM Revision Identifier is used to ascertain the version and extensions of SMM being used and is located at offset 7EFCH in the SMM state—save area. Table 8 shows the SMM Revision Identifier Fields and associated Rise  $^{\text{TM}}$  processor default values. I/O Instruction Restart and SMBase Relocation are always enabled on the Rise  $^{\text{TM}}$  processor.

**TABLE 8. SMM REVISION IDENTIFIER FIELDS**

| BITS 31-18 | BIT 17              | BIT 16                  | BITS 15-0          |

|------------|---------------------|-------------------------|--------------------|

| RESERVED   | SMM Base Relocation | I/O Instruction Restart | SMM Revision Level |

| 0          | 1                   |                         | 0002H              |

#### 8.4 I/O Instruction Restart

The I/O Instruction Restart Field, located at offset 7F00H in the SMM state—save area, controls an I/O instruction restart. If the I/O Instruction Restart Field contains the value 00FFH during an RSM instruction, then the value restored in the EIP register is the value found in the Restart EIP Field of the SMM state—save area. This restored EIP points to the I/O instruction that received the SMI request, and the processor automatically re—executes the trapped I/O instruction. However, if the I/O Instruction Restart Field contains the value 0000H during an RSM instruction, then the value restored in the EIP register is located in the EIP Field in the SMM state—save area. This information is tabulated below.

|   | Value of I/O Instruction Field | Origin of Value Stored in EIP Register    |

|---|--------------------------------|-------------------------------------------|

| / | 00FFh                          | Restart EIP Field of SMM State–Save Area  |

|   | Ø000H                          | EIP Register Field of SMM State–Save Area |

I/O Instruction Restart is always enabled on the Rise  ${}^{\text{TM}}P6^{\text{TM}}$  processor. When the processor enters SMM, a value of 0000H is always written to the I/O Instruction Restart Field. It is the responsibility of the SMM handler to examine the state of the processor and to determine if an I/O instruction restart is required.

#### 8.5 Auto Halt Restart

The Auto Halt Restart Field, located at offset 7F02H in the SMM state—save area, is loaded with a value of 0001H if the processor was in the HALT state when the SMI occurred. If the processor was not in HALT state, a value of 0000H is saved. Upon exit of SMM, the processor examines the Auto Halt Restart Field. If the Auto Halt Restart Field contains a value of 0001H, the Restart EIP is restored to the EIP register and the processor re—executes the HALT instruction upon exit of SMM. However, if the Auto Halt Restart Field contains 0000H, then the value from the EIP field is restored to the EIP register and the processor begins execution at the instruction following the HALT. If the SMM Handler routine clears this flag, the processor begins execution with the instruction following the HALT instruction.

#### 8.6 Back-to-Back SMI Interrupts When Using I/O Instruction Restart

To avoid program error, the SMM handler must be able to identify back-to-back SMI interrupts on I/O instructions when I/O Instruction Restarting is being used. Setting the I/O Instruction Restart Field value to 00FFH during the second of the back-to-back executions of the SMM handler causes the EIP value to be set.

# Appendix A – Machine–Specific Code for Rise<sup>m</sup>P6<sup>m</sup> Configuration Setting

The following code should be included in the system BIOS to properly support feature validation of the production steppings of the Rise  ${}^{\text{TM}}P6^{\text{TM}}$  processor. Include it in the non–compressed area so that it is available to vendors for easy modification to facilitate validation of different bit settings.

```

mP6 Msr Setup Req

;Routine:

For configuration setup of mP6 family

; Purpose:

;Comment:

This routine should be used to do configuration setup on mP6

;Inputs:

None

;Outputs:

None

Public

mP6 Msr Setup Req

mP6_Msr_Setup_Reg Proc Near

pushad

mov

eax, 6363452Ah

ecx, 3231206Ch

mov

edx, 2A32313Ah

mov

cpuid

eax, 63634523h

mov

ecx, 32315F6Ch

mov

edx, 2333313Ah

mov

cpuid

popad

ret

mP6_Msr_Setup_Reg endp

```