# 32K x 8 Synchronous SRAM

#### **Features**

- Synchronous 32K x 8 SRAM

- Supports 33-MHz 486 cache systems with zero wait states

- · Clock-to-output time

- -20 ns into 30 pF

- · Synchronous self-timed write

- TTL-compatible inputs and outputs

- Easy memory expansion with <del>OE</del> feature

#### **Functional Description**

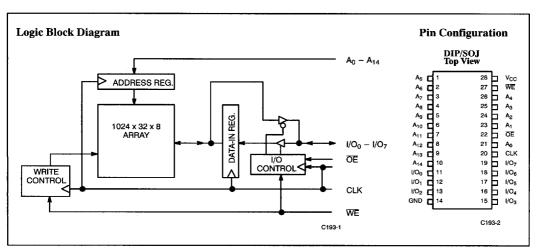

The CY7C193 is a synchronous 32K x 8 SRAM designed to allow zero-wait-state cache designs, both write back and write through, in microprocessor-based systems with 33-MHz bus speeds. The SRAM has a fast clock-to-output time of 20 ns into a load of 30 pF. The address, data, and WE

signals are all synchronous, while the  $\overline{OE}$  signal is asynchronous.

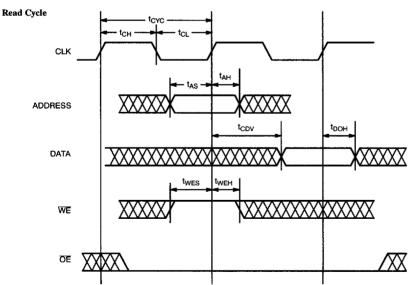

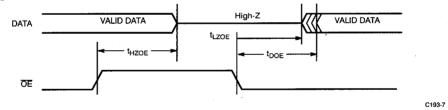

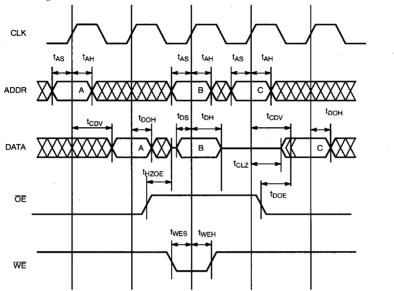

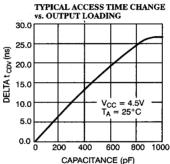

If WE is sampled HIGH at the rising edge of CLK (signifying a read cycle), the address is captured in the on-chip address register. The data is then driven out a maximum of 20 ns later (if the load on the data lines is 30 pF) allowing ample time for the data to be set up to the next rising edge of the clock in a 33-MHz cache system. If the load on the data lines is less than 30 pF, the clock-to-output time will be faster than 20 ns. See the derating curve at the end of the datasheet for details. The output data can also be controlled asynchronously by OE. The data I/O lines will switch from outputs to inputs (i.e., to the high-impedance state) within 7 ns of OE going HIGH. Valid data will be driven back out within 10 ns of OE going LOW again.

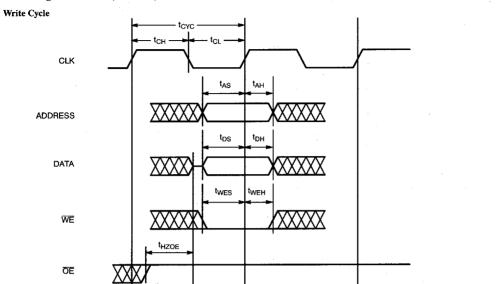

If the WE signal is sampled LOW at the rising edge of CLK (signifying a write cycle), the address is captured in the on-chip address register and the data to be written is captured in the data-in register. The CY7C193 then performs a synchronous self-timed write of the data to the specified location. The data I/O lines should be put into the high-impedance state by bringing  $\overline{\text{OE}}$  HIGH before the data to be written is driven in to the SRAM.

Although the CY7C193 is ideally suited for 33-MHz 486-based cache systems, it is very useful in many other applications as well. The synchronous address and data interface, along with the synchronous self-timed write feature, simplify designs of almost any system.

### **Selection Guide**

|                                |            | 7C193-20 |

|--------------------------------|------------|----------|

| Maximum Access Time (ns)       |            | 20       |

| Maximum Operating Current (mA) | Commercial | 160      |

2-193

2589662 0014892 422

| Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested.) |

|-------------------------------------------------------------------------------------------------|

| Storage Temperature $-65^{\circ}$ C to $+150^{\circ}$ C                                         |

| Ambient Temperature with Power Applied $-55^{\circ}$ C to $+125^{\circ}$ C                      |

| Supply Voltage to Ground Potential (Pin 28 to Pin 14)0.5V to +7.0V                              |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                           |

| Output Current into Outputs (LOW) |

|-----------------------------------|

| Static Discharge Voltage          |

| Latch-Up Current                  |

# **Operating Range**

| Range      | Ambient<br>Temperature | $v_{cc}$ |  |

|------------|------------------------|----------|--|

| Commercial | 0°C to +70°C           | 5V ± 5%  |  |

### Electrical Characteristics Over the Operating Range

| Parameter       | Description                                 | Test Conditions                                              | 7C193-20 |                          |      |

|-----------------|---------------------------------------------|--------------------------------------------------------------|----------|--------------------------|------|

|                 |                                             |                                                              | Min.     | Max.                     | Unit |

| V <sub>OH</sub> | Output HIGH Voltage                         | $V_{CC} = Min., I_{OH} = -4.0 \text{ mA}$                    | 2.4      |                          | V.   |

| V <sub>OL</sub> | Output LOW Voltage                          | $V_{\rm CC}$ = Min., $I_{\rm OL}$ = 8.0 mA                   |          | 0.4                      | V    |

| $V_{IH}$        | Input HIGH Voltage                          |                                                              | 2.2      | V <sub>CC</sub><br>+0.3V | V.   |

| V <sub>IL</sub> | Input LOW Voltage                           |                                                              | -0.5     | 0.8                      | V    |

| I <sub>IX</sub> | Input Load Current                          | $GND \le V_I \le V_{CC}$                                     | -5       | +5                       | μА   |

| I <sub>OZ</sub> | Output Leakage Current                      | $GND \le V_O \le V_{CC}$ , Output Disabled                   | -5       | +5                       | μА   |

| I <sub>OS</sub> | Output Short Circuit Current <sup>[1]</sup> | $V_{CC} = Max., V_{OUT} = GND$                               |          | -300                     | mA   |

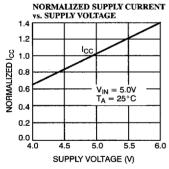

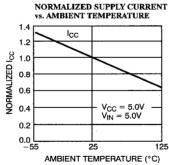

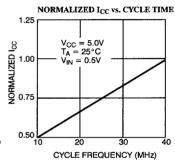

| I <sub>CC</sub> | V <sub>CC</sub> Operating Supply Current    | $V_{CC} = Max.$ , $I_{OUT} = 0$ mA, $f = f_{MAX} = 1/t_{RC}$ |          | 160                      | mA   |

#### Capacitance<sup>[2]</sup>

| Parameter        | Description        | Test Conditions                                 | Max. | Unit |

|------------------|--------------------|-------------------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25$ °C, $f = 1$ MHz,<br>$V_{CC} = 5.0$ V | . 8  | pF   |

| C <sub>OUT</sub> | Output Capacitance | VCC = 5.0V                                      | 8    | pF   |

### **AC Test Loads and Waveforms**

C193-4

Equivalent to:

THÉVENIN EQUIVALENT

167 $\Omega$ OUTPUT • • 1.73V

### Notes:

- Not more than one output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

- 2. Tested initially and after any design or process changes that may affect these parameters.

# Switching Characteristics Over the Operating Range[3]

|                   |                                                | 7C193-20  |     | Unit |  |

|-------------------|------------------------------------------------|-----------|-----|------|--|

| Parameter         | Description                                    | Min. Max. |     |      |  |

| tcyc              | Clock Cycle Time                               | 30        |     | ns   |  |

| t <sub>CH</sub>   | Clock Pulse Width High                         | 11        |     | ns   |  |

| t <sub>CL</sub>   | Clock Pulse Width Low                          | 11        |     | ns   |  |

| tCDV              | Clock Rise to Data Output Valid                |           | 20  | ns   |  |

| t <sub>DOH</sub>  | Data Output Hold after Clock Rise              | 3         |     | ns   |  |

| tAS               | Address Setup Before Clock Rise                | 5         |     | ns   |  |

| t <sub>AH</sub>   | Address Hold After Clock Rise                  | 1         | -   | ns   |  |

| twes              | WE Setup Before Clock Rise                     | 5         |     | ns   |  |

| tweH              | WE Hold After Clock Rise                       | 1         |     | ns   |  |

| t <sub>DS</sub>   | Data Input Setup Before Clock Rise             | 5         |     | ns   |  |

| t <sub>DH</sub>   | Data Input Hold After Clock Rise               | 1         |     | ns   |  |

| t <sub>DOE</sub>  | OE Low to Output Valid                         |           | . 9 | ns   |  |

| t <sub>HZOE</sub> | OE High to Output High-Z <sup>[4, 5]</sup>     |           | 7   | пs   |  |

| t <sub>WEHZ</sub> | WE Sampled Low to Output High-Z <sup>[4]</sup> |           | 10  | ns   |  |

| tLZOE             | OE LOW to Low-Z <sup>[5]</sup>                 | 0         |     |      |  |

| t <sub>CLZ</sub>  | Clock Rise to Low-Z                            | 8         |     |      |  |

#### Notes:

- Notes:

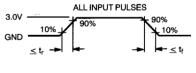

3. Test conditions assume signal transition time (t<sub>r</sub>, t<sub>f</sub>) of 3 ns or less, timing reference level of 1.5V, input pulse level of 0 to 3.0V, and outputs loading perspecified I<sub>OH</sub>/I<sub>OL</sub>, outputs loaded with 30 pF per (a) in AC Test Loads and Waveforms.

- t<sub>HZOE</sub> and t<sub>WEHZ</sub> are specified with 5 pF capacitive load per (b) in AC Test Loads and Waveforms. Transition is measured ±500 mV from steady state voltage.

- At any given temperature and voltage condition, t<sub>HZOE</sub> is less than t<sub>LZOE</sub> and t<sub>WEHZ</sub> is less than t<sub>CLZ</sub> for any given device.

# **Switching Waveforms**

C193-5

C193-6

# Switching Waveforms (continued)

# **OE** Timing

# Switching Waveforms (continued)

### Read-Write-Read Timing

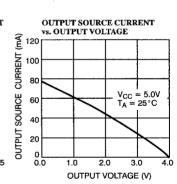

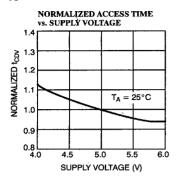

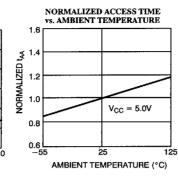

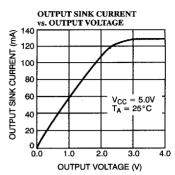

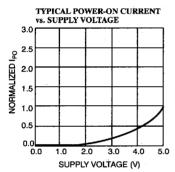

# Typical DC and AC Characteristics

C193-8

# Typical DC and AC Characteristics (continued)

# **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package<br>Type              | Operating<br>Range |

|---------------|---------------|-----------------|------------------------------|--------------------|

| 20            | CY7C193-20PC  | P21             | 28-Lead (30)-Mil) Molded DTP | Commercial         |

|               | CY7C193-20VC  | V21             | 28-Lead Molded SOJ           |                    |

Shaded area contains preliminary information.

Document #: 38-00254-A