# **RadiSys ARTIC960 Co-Processor Platforms**

# Hardware Technical Reference

RadiSys Corporation 5445 NE Dawson Creek Drive Hillsboro, OR 97124 (503) 615-1100 FAX: (503) 615-1150 www.radisys.com September 1999 Before using this information and the product it supports, be sure to read all the information in Appendix D, Notices .

EPC, INtime, and RadiSys are registered trademarks of RadiSys Corporation.

<sup>†</sup> All other trademarks, registered trademarks, service marks, and trade names are the property of their respective owners.

September 1999

© Radisys Corporation 1999. All rights reserved.

© Copyright International Business Machines Corporation 1998. All rights reserved.

Note to U.S. Government Users—Documentation related to restricted rights—Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp. All rights reserved.

# **About this Guide**

This publication contains technical reference information for the RadiSys ARTIC960 PCI Co-Processor Platform and RadiSys ARTIC960 PCI Co-Processor Platform.

The objectives of this publication are to:

- Describe the various units of the co-processor platform

- Explain the interaction of the units on the co-processor platform

- Explain the technical details of the options and interfaces of the co-processor platform

- Provide descriptions and data related to the co-processor platform configuration, component layout, circuitry, functions, hardware interfaces, and programming considerations.

Detailed programming information for the co-processor platform can be found in the *RadiSys ARTIC960 Co-Processor Platforms Programmer's Guide and Reference*.

# **Guide contents**

The following lists the contents of this Guide.

| Chapter |                                                               | Description                                                                                                                                                                       |  |

|---------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | Introduction to the RadiSys<br>ARTIC960 Co-Processor Platforn | Provides a brief introduction to the co-processor<br>platform and serves as a quick reference to the<br>major hardware components, subsystems,<br>interfaces, and specifications. |  |

| 2       | Co-Processor<br>Platform Components                           | Covers the co-processor platform hardware in detail. It begins with a high-level discussion and progresses downward to specific registers.                                        |  |

| 3       | Memory Protection Subsystem                                   | Provides an in-depth discussion of the memory protection hardware that is external to the 80960 processor.                                                                        |  |

| 4       | Error Checking and Correction<br>(ECC) Subsystem              | Describes the implementation of the error detection<br>and correction scheme, and provides details of the<br>registers associated with this function.                             |  |

| 5       | Timer Subsystem                                               | Discusses the interval timers.                                                                                                                                                    |  |

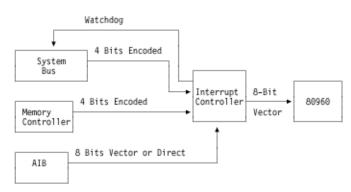

| 6       | Interrupt Controller Subsystem                                | Describes the interaction of the controller with the Application-Specific Integrated Circuits, the AIB, and the 80960 processor.                                                  |  |

| Ch | apter                                                    | Description                                                                                                                                                                                                                                                                   |

|----|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | CFE Local Bus Subsystem and<br>AIB Interface Description | Provides details of Local Bus operation, specifically<br>addressing the request sequence, bus arbitration,<br>bursting, timeout, parity, and interrupts. This<br>chapter also describes CFE Local Bus and ROM<br>Bus signals, and lists the AIB connector pin<br>assignments. |

| 8  | Micro Channel<br>Interface Subsystem                     | Describes the major functions of the Micro Channel<br>Interface Chip, provides details of the registers<br>associated with the Micro Channel, and discusses<br>overall Bus Master operation.                                                                                  |

| 9  | PCI Interface Subsystem                                  | Describes the major functions of the PCI System<br>Bus Interface Chip, provides details of the registers<br>associated with the PCI, and discusses overall Bus<br>Master operation.                                                                                           |

| 10 | Miscellaneous Registers                                  | Covers the registers associated with the<br>implementation of miscellaneous co-processor<br>platform functions, such as ROM write enable,<br>memory presence detect, and so forth.                                                                                            |

| 11 | Debug Features                                           | Provides details of the tool that is built into the co-processor platform for use during the debug phase of code development.                                                                                                                                                 |

| 12 | ROM Support                                              | Describes the power-on self-test (POST) process<br>and error reporting for the co-processor platform<br>hardware, as well as initialization, setup, and<br>interface structures for downloading and executing<br>the AIB's ROM POST and supervisor task routines.             |

| 13 | 4-Port Multi-Interface Application<br>Interface board    | Describes the architecture for this AIB and contains<br>specifications, interface design criteria, cabling<br>information, and software implementation details.                                                                                                               |

### Appendices

The appendices provide additional information about ARTIC960.

| Appendix |                                         | Description                                                                   |  |

|----------|-----------------------------------------|-------------------------------------------------------------------------------|--|

| A        | Acronym Glossary                        | Contains a listing of the acronyms used in this publication.                  |  |

| В        | Co-Processor<br>Platform Registers      | Contains a listing of these registers, sorted by abbreviation and by address. |  |

| С        | 4-Port Multi-Interface<br>AIB Registers | Contains a listing of these registers, sorted by abbreviation and by address. |  |

### Who Should Read this Book

The information in this publication is both introductory and for reference use. It is intended for hardware and software designers, programmers, engineers, and anyone with a knowledge of electronics and/or programming who wishes to understand the use and the operation of the co-processor platform.

It is assumed that the reader is familiar with the co-processor platform, as well as the computer system in which it is installed, the applications in use, and programming.

Therefore, terminology is not explained herein, except for terms that may be specially implemented.

### **Notational conventions**

This manual uses the following conventions:

- Unless noted otherwise, *RadiSys ARTIC960 Co-Processor Platform* is used to denote both the ARTIC960 and the ARTIC960 PCI adapters. Throughout this publication, the ARTIC960 Co-Processor Platform is also referred to as the *co-processor platform* or the *base card*.

- All counts in this document are assumed to start at zero.

- All bit numbering conforms to the industry standard of the most significant bit having the highest bit number.

- All numeric parameters and command line options are assumed to be decimal values unless otherwise noted.

- To pass a hexadecimal value for any numeric parameter, the parameter should be prefixed by **0x** or **0X**. The numeric parameters **16**, **0x10**, and **0X10** are all equivalent.

- All representations of bytes, words and double words are in the Intel format.

- Utilities all accept the ? switch as a request for help with command syntax.

- Screen text and syntax strings appear in this font.

- All numbers are decimal unless otherwise stated.

- Bit 0 is the low-order bit. If a bit is set to 1, the associated description is true unless otherwise stated.

Notes indicate important information about the product.

Tips indicate alternate techniques or procedures that you can use to save time or better understand the product.

The globe indicates a World Wide Web address.

Cautions indicate situations that may result in damage to data or the hardware.

ESD cautions indicate situations that may cause damage to hardware via electro-static discharge.

Warnings indicate situations that may result in physical harm to you or the hardware.

# Where to get more information

You can find out more about ARTIC960 from these sources:

• World Wide Web: RadiSys maintains an active site on the World Wide Web. The site contains current information about the company and locations of sales offices, new and existing products, contacts for sales, service, and technical support information. You can also send e-mail to RadiSys using the web site.

When sending e-mail for technical support, please include information about both the hardware and software, plus a detailed description of the problem, including how to reproduce it.

To access the RadiSys web site, enter this URL in your web browser: http://www.radisys.com

Requests for sales, service, and technical support information receive prompt response.

• **Other**: If you purchased your RadiSys product from a third-party vendor, you can contact that vendor for service and support.

### **Reference Publications**

You may need to use one or more of the following publications for reference:

- Operating and Installation documentation provided with your computer system.

- IBM Operating System/2 (OS/2) documentation

- IBM Advanced Interactive Executive (AIX) documentation

- RadiSys ARTIC960 Co-Processor Platform Guide to Operations

- RadiSys ARTIC960 PCI Co-Processor Platform Guide to Operations.

These manuals contain a description of the co-processor platform, instructions for physically installing the adapter, procedures for installing and setting up the operating system, configuration information, parts listings, and a Symptom-to-FRU Index Supplement.

- Application Interface Board Supplement(s) to RadiSys ARTIC960 Co-Processor Platforms Guide to Operations. Each Supplement contains a description of an IBM-developed AIB, instructions for installing the AIB Cable, interface connector information, and interface cable details.

- Application Interface Board Hardware Maintenance Libraries. Each AIB Library contains one or more wrap plugs that are used during diagnostic testing to wrap selected interface lines of an IBM-developed AIB and the associated Interface Cable. Also included are removal and replacement procedures for field-replaceable units (FRUs), parts listings, and a Symptom-to-FRU Index Supplement. Most AIB Libraries include a diagnostic diskette that is used to isolate a symptom to a failing FRU.

# RadiSys ARTIC960 Developer's Kit—Content

The Developer's Kit is a set of publications and programs designed to help ARTIC960 AIB software developers develop for the ARTIC960 platform. The following items make up the Developer's Kit:

- *RadiSys ARTIC960 Co-Processor Platforms Hardware Technical Reference* presents technical details of the adapter's system, options, and hardware interfaces. It provides descriptions and data related to the card configuration, functions, hardware interfaces, and programming considerations.

- *RadiSys ARTIC960 Co-Processor Platforms Programmer's Guide and Reference* provides an overview of both the adapter kernel support and the operating system support. It also describes the associated processes and utilities, as well as each of the services provided by the system unit support and the adapter kernel support.

- *RadiSys ARTIC960 Co-Processor Platforms Application Interface Board Developer's Guide* provides the hardware and the software developer with AIB design requirements, and a collection of productivity tools to aid in the development of an AIB.

- A set of operating system packages, each containing sample programs and utilities to support the development of system unit and adapter applications. These packages are to be used with the *RadiSys ARTIC960 Co-Processor Platforms Programmer's Guide* and the *RadiSys ARTIC960 Co-Processor Platform Application Interface Board Developer's Guide*.

- You can obtain these publications in PostScript format from the World Wide Web (WWW) at:

http://ww.radisys.com/products/artic/

If you do not have access to the WWW, or you cannot print PostScript files, you can obtain these publications from the no-fee Developer's Assistant Program (DAP), which also provides technical question-and-answer (Q&A) services supported by telephone and E-mail, as explained under Developer's Assistance Program.

# **Developer's Assistance Program**

In addition to the *Developer's Kit*, further programming and hardware development assistance is provided by the RadiSys ARTIC960 Developer's Assistance Program (DAP). The DAP will provide, via phone and electronic communications, on-going technical support—such as sample programs, debug assistance, and access to the latest microcode upgrades.

You can get more information or activate your *free* RadiSys ARTIC960 DAP membership by contacting us.

By telephone, call (561) 454-3200.

By E-mail, send to artic@radisys.com.

# Contents

# Chapter 1: Introduction to the RadiSys ARTIC960 Co-Processor Platform

| Product Description                                                         | 1  |

|-----------------------------------------------------------------------------|----|

| Processing Power                                                            | 2  |

| Software                                                                    | 2  |

| Compatibility                                                               | 2  |

| Performance                                                                 | 3  |

| Diagnostics                                                                 | 4  |

| Hardware Components                                                         | 5  |

| Hardware Considerations                                                     | 6  |

| Functional Subsystems                                                       | 6  |

| Physical Interfaces                                                         | 7  |

| Specifications                                                              | 7  |

| Chapter 2: Co-Processor Platform Components                                 |    |

| Functional Block Diagram                                                    | 10 |

| Microprocessor                                                              | 10 |

| Characteristics                                                             | 10 |

| Programming Considerations                                                  | 11 |

| Reset                                                                       | 11 |

| 80960 Addressable Registers                                                 | 11 |

| Memory                                                                      | 16 |

| Dynamic Random-Access Memory (DRAM)                                         | 16 |

| Read-Only Memory (ROM)                                                      | 16 |

| Serial EPROM                                                                | 17 |

| DRAM/ROM Memory Map                                                         | 17 |

| Memory Controller Chip (ASIC)                                               | 20 |

| Functional Summary                                                          | 20 |

| System Bus Interface Chip                                                   | 20 |

| Micro Channel Interface Chip Application-Specific Integrated Circuit (ASIC) | 21 |

| PCI System Bus Interface Chip                                               | 21 |

| Chapter 3: Memory Protection Subsystem                                      |    |

| Memory Protection Map                                                       | 23 |

| Local Bus Memory Protection Map                                             | 24 |

| Page Table Entries and Page Tables                                          | 25 |

| Page Table Entries                                                          | 25 |

| Page Tables                                                                 | 26 |

| Page Table Entry Caching                                                    | 26 |

| Operating Sequence                                                          | 27 |

| Memory Protection Performance                                               | 27 |

| Memory Protection Registers                                                 | 27 |

| Memory Protection Enable Register (MPER)                                    | 27 |

| Task Page Table Base Register (TPTBR)                                       | 29 |

| Register Format:                                                             | 29 |

|------------------------------------------------------------------------------|----|

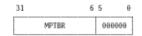

| System Bus Slave Page Table Base Register (MPTBR)                            | 29 |

| Task Protection Address Trap Register (TPATR)                                | 30 |

| Task Protection Status Register (TPSTAT)                                     |    |

| Local Bus Protection Address Trap Register (LPATR)                           |    |

| Local Bus Protection Status Register (LPSTAT)                                |    |

| Chapter 4: Error Checking and Correction (ECC) Subsystem                     |    |

| ECC Errors                                                                   | 34 |

| Single-bit ECC Error Address Trap Register (SBATR)                           |    |

| Single-Bit ECC Error Register (SBECCR)                                       |    |

| ECC Address Trap Register (ECCATR)                                           |    |

| ECC Status Register (ECCSTAT)                                                |    |

| Force ECC Error Register (FEER)                                              |    |

| Chapter 5: Timer Subsystem                                                   |    |

| Programming Considerations                                                   | 39 |

| Timer Control Register (TCR0-4)                                              |    |

| Timer Preset Register (TPR0-4)                                               |    |

| Timer Present Value Register (TPV0-4)                                        |    |

| Timer Command Register (TCMD0-4)                                             |    |

| Timer Interrupts                                                             |    |

| Chapter 6: Interrupt Controller Subsystem                                    |    |

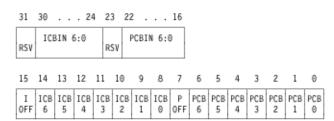

| Programming Considerations                                                   | 45 |

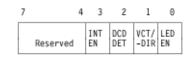

| Enable/Detect Register (EDR)                                                 |    |

|                                                                              | 40 |

| Chapter 7: CFE Local Bus Subsystem and AIB Interface Description             |    |

| CFE Local Bus and ROM Bus Signal Descriptions.                               |    |

| CFE Local Bus (AIB Interface) Signals                                        |    |

| AIB ROM Bus Signals                                                          |    |

| Other Interface Signals                                                      |    |

| Local Bus Memory Map                                                         |    |

| Local Bus Arbitration                                                        |    |

| Preemption and Termination of Bus Ownership by the System Bus Interface Chip |    |

| Local Bus Parity                                                             |    |

| Local Bus Exceptions                                                         |    |

| Local Bus Timeout                                                            |    |

| Local Bus Exception Handling                                                 |    |

| Local Bus Registers                                                          |    |

| Local Bus Parity/Exception Register (LBPE)                                   |    |

| Micro Channel                                                                |    |

| PCI                                                                          |    |

| Local Bus Exception Address Trap Register (LEXATR)                           |    |

| Local Bus Exception Status Register (LEXSTAT)                                |    |

| Special Arbitration Register (SPAR)                                          |    |

| Processor Configuration Register (PROC_CFG)                                  |    |

| Micro Channel                                                                |    |

| PCI                                                                          |    |

| Local Bus Configuration Register (LBCFG)                                     |    |

| AIB Connector Pin Assignments                                                | 63 |

# Chapter 8: Micro Channel Interface Subsystem

| Micro Channel Interface Chip Signal Description             | 66 |

|-------------------------------------------------------------|----|

| Micro Channel Addressable Ports/Registers                   | 68 |

| Program Option Select (POS)/Configuration/Subaddressing     | 68 |

| POS Registers                                               | 68 |

| POS_Setup1 Register (POS_SETUP1)                            | 70 |

| POS Setup Register 2 (POS_SETUP2)                           | 74 |

| Configuration Register 1 (CONF1)                            | 77 |

|                                                             | 77 |

| Configuration Register 3 (CONF3)                            | 78 |

| Processor Configuration Register (PROC_CFG) (Micro Channel) | 78 |

| Processor Configuration Register (PROC_CFG) (PCI)           | 80 |

| Extended POS Base Address Register (XPOS)                   | 81 |

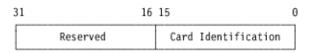

| Card Identification (CRDID)                                 | 82 |

| POS Subaddressing                                           | 82 |

| I/O Check Reporting and Parity Function                     | 83 |

| Asynchronous Data Parity Check Description                  | 84 |

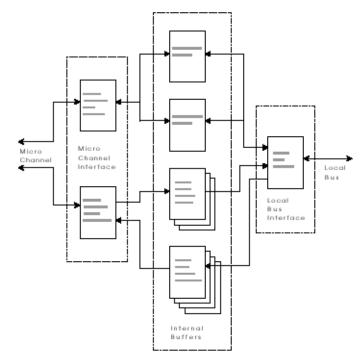

| Bus Master Channel Functional Description                   | 84 |

| Overall Operation                                           | 85 |

| Bus Operation                                               | 86 |

| Appended I/O Operations                                     | 87 |

| Posted Status Operations                                    | 87 |

| Linked List Chaining                                        | 88 |

| Modes of Operation                                          | 89 |

| Stopping the Channel                                        | 91 |

| Bus Master Registers                                        | 92 |

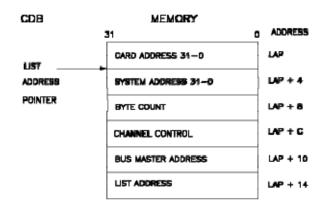

| Bus Master Channel Descriptor Block (BMCDB)                 | 92 |

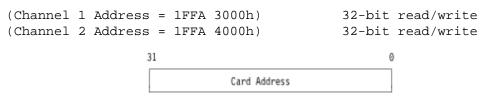

| Card Address Register (CAR)                                 | 92 |

| System Address Register (SAR)                               | 92 |

| Byte Count Register (BCR)                                   | 93 |

| Channel Control Register (CCR)                              | 93 |

|                                                             | 95 |

| List Address Pointer (LAP) Register                         | 96 |

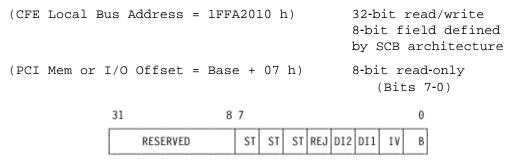

| Bus Master Status Register, BMSTAT1 (2)                     | 97 |

| Bus Master Command Register, BMCMD1 (2)                     | 99 |

| Shared Memory 1                                             | 00 |

|                                                             | 00 |

|                                                             | 00 |

|                                                             | 01 |

|                                                             | 02 |

|                                                             | 02 |

| Slave I/O Access to Local Bus Address Space 1               | 02 |

| Slave I/O Registers                                         | 03 |

|                                                             | 03 |

| -                                                           | 03 |

|                                                             | 05 |

|                                                             | 05 |

|                                                             | 06 |

|                                                             | 06 |

| SCB Registers                                      | 107 |

|----------------------------------------------------|-----|

| Command Port (COMMAND)                             | 107 |

| Attention Port (ATTN)                              | 107 |

| Subsystem Control Port (SCP)                       | 110 |

| Interrupt Status Port (ISP)                        | 111 |

| Command Busy Status Port (CBSP)                    |     |

| Source Identification Register (SIR)               |     |

| Miscellaneous Micro Channel Registers              |     |

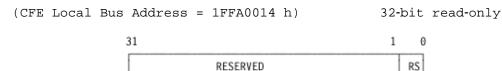

| Reset Status Register (RSR)                        |     |

| Non-Maskable Interrupt Register (NMI)              |     |

| System Bus Interface Chip Interrupts               |     |

|                                                    | 110 |

| Chapter 9: PCI Interface Subsystem                 | 110 |

| PCI System Bus Interface Chip Signal Description   |     |

| PCI System Bus Interface Chip Register Description |     |

| Programming Considerations                         |     |

| PCI Bus Configuration Registers                    |     |

| Serial EPROM Extension Register (SEER)             |     |

| Device/Vendor ID (DEVID)                           |     |

| Host Status/Command Register (HSCR)                |     |

| Class Code/Revision ID Register (CCRID)            | 126 |

| Host Miscellaneous Functions Register (HMFR)       | 127 |

| I/O Base Address Register (IOBAR)                  | 128 |

| Host Memory Base Address Register (HMBAR)          | 128 |

| Memory Mapped I/O Base Address Register (MMBAR)    | 129 |

| Subsystem ID (SSID)                                | 130 |

| Expansion ROM Base Address Register (XRBAR)        | 130 |

| Latency/Grant/Interrupt Register (LGIR)            | 131 |

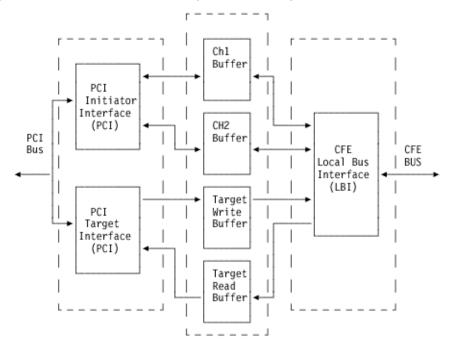

| Bus Master Channel Functional Description          | 132 |

| General Operation                                  | 132 |

| DMA Thresholds                                     | 133 |

| Flow of Operation                                  | 133 |

| Channel Priority on the CFE Local Bus              |     |

| Channel Priority on the PCI Bus                    |     |

| Bus Operation                                      |     |

| Posted Status Operations                           |     |

| Linked List Chaining                               |     |

| Modes of Operation                                 |     |

| Stopping the Channel                               |     |

| Bus Master Registers                               |     |

| Bus Master Channel Descriptor Block (BMCDB)        |     |

| Card Address Register (CAR)                        |     |

| System Address Register (SAR)                      |     |

| Byte Count Register (BCR)                          |     |

| Channel Control Register (CCR)                     |     |

| Bus Master Address Register (BMAR)                 |     |

| List Address Pointer (LAP)                         |     |

| Bus Master Status Register (BMSTAT1 (2))           |     |

| Bus Master Command Register (BMCMD1 (2))           |     |

| System Byte Count Register (SBCR)                  |     |

| System Dyte Count Register (SDCR)                  | 14/ |

| PCI Memory Windows to CFE Address Space                       | 147 |

|---------------------------------------------------------------|-----|

| Expansion ROM Window                                          | 147 |

| Full Memory Window                                            | 147 |

| CFE Read Prefetching                                          | 148 |

| Bursting/Non-Bursting CFE Addresses                           | 149 |

| Slave Memory Register                                         | 149 |

| Local Bus Base Address Register (LBBAR)                       | 149 |

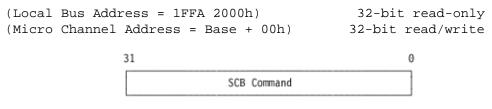

| Subsystem Control Block (SCB) Support                         | 150 |

| Locate Mode                                                   | 150 |

| Move Mode                                                     | 151 |

| Interrupts                                                    | 151 |

| Exceptions                                                    | 151 |

| PCI Slave (Target) Features                                   | 151 |

| Host-Slave Base Address Register (HSBR)                       | 153 |

| Reading and Writing Registers                                 | 154 |

| Memory Data Register (MDATA)                                  | 154 |

| CFE Base Address Register (CFEBAR)                            |     |

| PCI Master (Initiator) Features                               | 155 |

| System Errors (-SERR)                                         | 156 |

| SCB Registers                                                 |     |

| Command Port (COMMAND)                                        | 156 |

| Attention Port (ATTN)                                         | 157 |

| Subsystem Control Port (SCP)                                  |     |

| Interrupt Status Port (ISP)                                   | 159 |

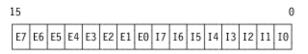

| Register Format                                               | 159 |

| Command Busy Status Port (CBSP)                               | 161 |

| Source Identification Register (SIR)                          | 162 |

| Miscellaneous PCI Functions and Registers                     | 163 |

| Reset Status Register (RSR) (PCI)                             | 163 |

| Non-Maskable Interrupt Register (NMI)                         |     |

| System Bus Interface Chip Interrupts                          |     |

| Chapter 10: Miscellaneous Registers                           |     |

| Programming Considerations                                    | 167 |

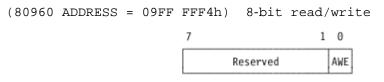

| AIB ROM Write Enable Register (AWE)                           |     |

| Base ROM Write Enable Register (BWE)                          |     |

| Enable/Detect Register (EDR)                                  |     |

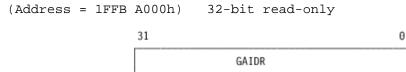

| Memory Controller Chip Gate Array ID Register (GAIDR)         |     |

| Micro Channel Interface Chip Gate Array Identification (GAID) |     |

| System Bus Interface Chip Gate Array Identification (GAID)    |     |

| Interrupt Controller Version Register (IVR)                   |     |

| Memory Presence Detect Low Register (MPL)                     |     |

| Memory Presence Detect High Register (MPH)                    |     |

| Memory Configuration Register (MCR)                           |     |

| Chapter 11: Debug Features                                    |     |

| Serial Debug Port                                             |     |

| Hardware Requirements for Debug Cable                         |     |

| Serial Debug Port Interrupts                                  |     |

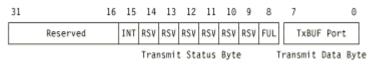

| Transmitter Buffer Port (TxBUF)                               |     |

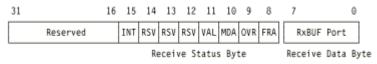

| Receiver Buffer Port (RxBUF)                                  |     |

|                                                               |     |

| Port Configuration Register (PCR)                                     | 176 |

|-----------------------------------------------------------------------|-----|

| Chapter 12: ROM Support                                               |     |

| Main Initialization Structures                                        | 177 |

| Initialization Boot Record (IBR)                                      |     |

| Process Control Block (PRCB)                                          |     |

| Secondary Initialization Structures                                   |     |

| Fault Table Structure                                                 |     |

| 80960Cx Reset Conditions                                              | 181 |

| Adapter Initialization and POST                                       | 181 |

| Preliminary POST                                                      | 182 |

| Main POST                                                             | 186 |

| Final Adapter Initialization                                          | 188 |

| Error Reporting                                                       | 189 |

| ISP Error Codes                                                       | 190 |

| ROMStatus Word Definitions                                            | 191 |

| AIBStatus Word (under Base ROM Control)                               | 192 |

| Error Code Breakdown                                                  | 192 |

| Base ROM I/F Structures                                               | 201 |

| Packet Memory Map (RadiSys ARTIC960 Co-Processor Platform ROM Anchor) | 201 |

| Rom_Table Structure                                                   | 203 |

| Struct MEM (pointed by MemInfoPtr in ROM_TABLE)                       | 204 |

| Struct IO (pointed by IOInfoPtr in ROM_TABLE)                         | 205 |

| Struct SUCommands (pointed by CommandPtr in ROM_TABLE)                | 205 |

| Struct RIC_Except (pointed by ExceptionPtr in ROM_TABLE)              | 206 |

| System Unit Notification of Error                                     | 206 |

| Struct RIC_RDTEntry (pointed by *HWResTabPtr in ROM_TABLE)            | 207 |

| Struct VPD (pointed by VPD_ptr in ROM_TABLE)                          | 208 |

| Struct MCAT (pointed by MCAT_Ptr in ROM_TABLE)                        |     |

| Struct Debug (pointed by DB_Area in ROM_TABLE)                        |     |

| Struct BaseOptions (pointed by BaseOptions in ROM_TABLE)              |     |

| Struct RomPostStatus (pointed by RomPostStat pointer in ROM_TABLE)    |     |

| Struct IntID (pointed by IntID pointer in Base ROM_TABLE)             |     |

| AIB Structures Used by the Base ROM                                   |     |

| AIB ROM Signature Block                                               |     |

| Struct AIB_ROM_ANCHOR                                                 |     |

| Vital Product Data Block                                              |     |

| AIB Processor Binding Block                                           |     |

| AIB Hardware Resource Table                                           |     |

| Kernel Structures Used by Base ROM (Boot Strap Loader)                |     |

| System Unit Commands                                                  |     |

| Load Process Command                                                  |     |

| Fill Command                                                          |     |

| Set Process Entry Command                                             |     |

| Start a Process Command                                               |     |

| Kernel Input Structure                                                |     |

| Kernel Structure Used by the Kernel through the ROM Table             |     |

| Set Control Block Anchor                                              | 218 |

| Data Rates                                                                  | . 219 |

|-----------------------------------------------------------------------------|-------|

| Optional Cable Assemblies                                                   |       |

| Hardware Implementation                                                     |       |

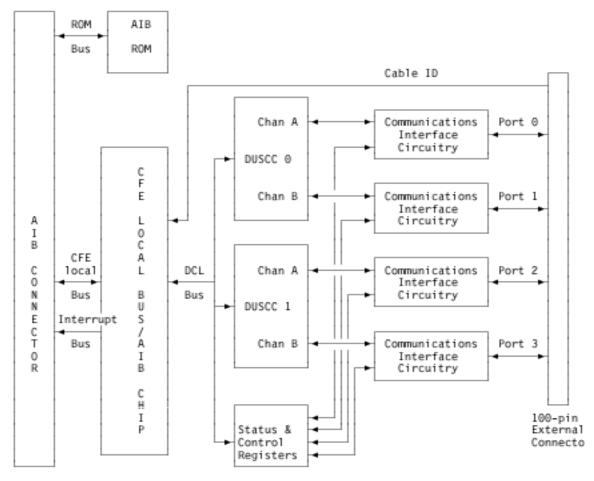

| Card Architecture                                                           |       |

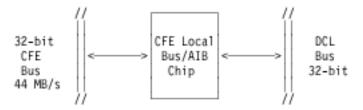

| CFE Local Bus/AIB Interface Chip                                            |       |

| Status and Control Registers                                                | . 223 |

| AIB Specifications                                                          |       |

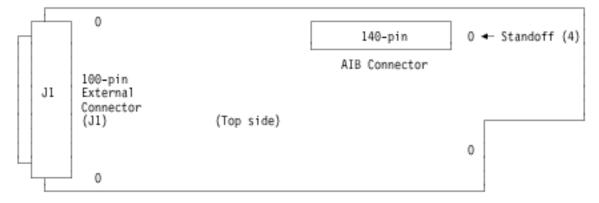

| 100-Pin External Connector                                                  |       |

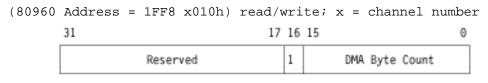

| CFE Local Bus/AIB Interface Chip DMA Controller                             | . 226 |

| Channel Descriptor Table (CDT)                                              |       |

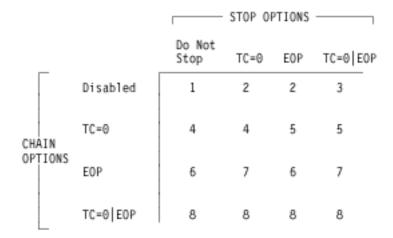

| Linked List Chaining (LLC)                                                  | . 228 |

| Linked List Chaining/Stopping Matrix                                        | . 229 |

| DMA Interrupts                                                              |       |

| DMA Performance                                                             |       |

| 4-Port Multi-Interface AIB Interrupt Controller Subsystem                   | . 232 |

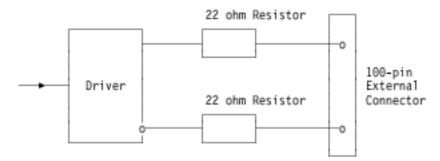

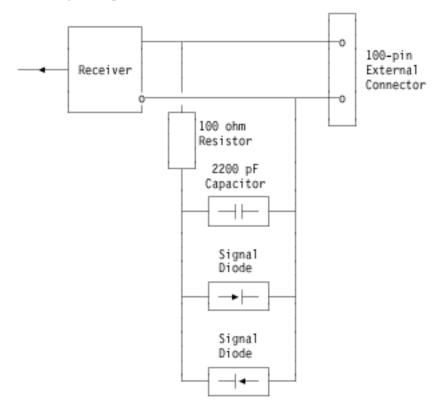

| Electrical Interface Design                                                 |       |

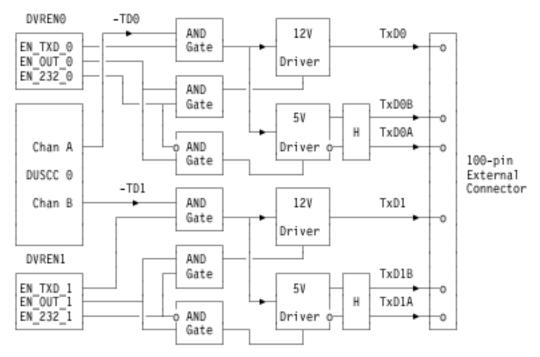

| Drivers/Receivers Signals                                                   |       |

| Drivers/Receivers Controls                                                  |       |

| Homologation Design                                                         |       |

| Driver/Receiver Block Diagrams                                              |       |

| X.21 State Detection                                                        |       |

| Block Diagram                                                               |       |

| X.21 State Detection Circuit Description                                    |       |

| AIB Cable Assemblies                                                        |       |

| Cable Configurations                                                        |       |

| D-Shell Connectors                                                          |       |

| Pin Assignments (Listed by Cable Assembly)                                  |       |

| User Cables                                                                 |       |

| AIB Wrap Plugs                                                              |       |

| 100-Pin Wrap Plug                                                           |       |

| Cable Wrap Plugs                                                            |       |

| Software Implementation                                                     |       |

| Interrupts and Direct Memory Access (DMA)                                   |       |

| AIB Addressable Memory and Registers                                        |       |

| AIB ROM                                                                     |       |

| DCL Bus Devices                                                             |       |

| Software Interface                                                          |       |

| CFE Local Bus/AIB Interface Chip Registers                                  |       |

| DMA Registers                                                               |       |

| AIB Address 1/2 Register (AIB_ADDR 1/2)                                     |       |

| AIB_OP1 Data Register (AIB_OP1)                                             |       |

| AIB_OP2 Data Register (AIB_OP2)                                             |       |

| Channel Control Register (CCR)                                              |       |

|                                                                             |       |

| Chain Pointer Register (CPR)<br>DMA Channel Command Registers (DCCR)        |       |

|                                                                             |       |

| DMA FIFO Residual Count Register (DFRC)                                     |       |

| DMA Interrupt Status Registers (DISR)<br>Global DMA Command Register (GDCR) |       |

|                                                                             | . 20  |

# Chapter 13: 4-Port Multi-Interface Application Interface board

| CFE Local Bus Configuration Register (LBCR)                  |     |

|--------------------------------------------------------------|-----|

| Memory Pointer Register (MPR)                                | 269 |

| Transfer Count Register (TQC)                                | 269 |

| Interrupt Registers                                          | 270 |

| AIB INT0 End-of-Interrupt (EOI0) Command                     | 270 |

| AIB INT1 End-of-Interrupt (EOI1) Command                     | 271 |

| Interrupt Initialization Register (IIR)                      | 271 |

| Interrupt Mask Register (IMR)                                | 273 |

| Interrupt Status Register (ISR)                              | 274 |

| DCL Registers                                                | 275 |

| DCL Command/Status Register (ACSR)                           | 275 |

| Chip Select Definition Registers (CSD0-4)                    |     |

| DMA Acknowledge Pulse Width Registers (DAPW0-7)              |     |

| Miscellaneous Registers                                      |     |

| LED Enable Register (LER)                                    |     |

| Presence Detect Register (PDR)                               |     |

| FPGA Registers                                               |     |

| FPGA Status and Control Registers                            |     |

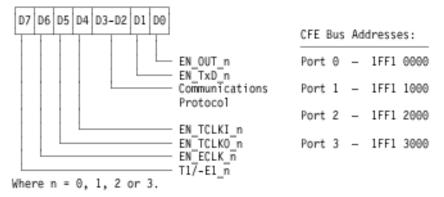

| Port 0–3 Driver Enable Registers (DVREN0–3)                  |     |

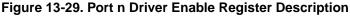

| Port 0–3 Interrupt Enable Registers (INTEN0–3)               |     |

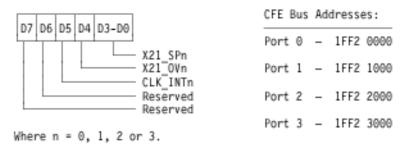

| X.21 Pattern Detect Registers                                |     |

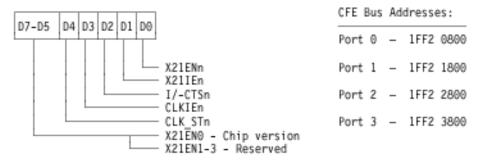

| Port 0–3 X.21 Enable Registers (X21EN0–3)                    |     |

| Port 0–3 X.21 Pattern Status Registers (X21ST0–3)            |     |

| Hardware Notes                                               |     |

| Signetics SC26C562 DUSCCD Interrupt Timings                  |     |

| Signetics SC26C562 DUSCC CCR Register                        |     |

| Signetics SC26C562 DUSCC RTS Output in X.21 Applications     |     |

| CFE Local Bus/AIB Interface Chip AIB Reset Output            |     |

| Programming Restrictions                                     |     |

| Critical Registers                                           |     |

| RadiSys ARTIC960 Co-Processor Platform                       |     |

| Interrupt Controller Enable/Detect Register (EDR)            |     |

| CFE Local Bus/AIB Interface Chip                             |     |

| Interrupt Mask Register (IMR)                                |     |

| AIB Address 1/2 Register (AIB_ADDR 1/2)                      | 289 |

| DCL INT0 and INT1 End-of-Interrupt Registers (EOI0 and EOI1) |     |

| Signetics SC26C562 DUSCC                                     |     |

| Channel Mode Register 2 (CMR2)                               |     |

| Pin Configuration Register (PCRA/B)                          |     |

| Output and Miscellaneous Register (OMRA/B)                   |     |

| Interrupt Control Register (ICR)                             |     |

| Other Restrictions                                           |     |

| X.21 Interface                                               |     |

| X.21 Protocol                                                |     |

|                                                              |     |

| DUSCC Signal Assignment                                      |     |

| DUSCC Pin Programming<br>X 21 Pattern Detection              |     |

| X.21 Pattern Detection                                       |     |

| AIB ROM Description                                          |     |

| AIB ROM Structures                                           |     |

| AIB ROM Signature Block                                      | 295 |

| AIB ID                                           | 295 |

|--------------------------------------------------|-----|

| AIB ROM Binding Block                            | 296 |

| AIB ROM Power-On Self Test (POST)                | 296 |

| AIB ROM POST Execution                           | 296 |

| Miscellaneous Test                               | 297 |

| General Register Test                            | 297 |

| Asynchronous Polled Transfer Mode Test           | 298 |

| Asynchronous Interrupt Transfer Mode Test        | 299 |

| Asynchronous DMA Transfer Mode Test              | 300 |

| HDLC/SDLC Transfer Mode Test                     | 302 |

| BISYNC Transfer Mode Test                        | 304 |

| DMA Start/Stop Test Using DCCR                   | 306 |

| DMA Start/Stop Test Using GDCR                   | 307 |

| AIB ROM INIT Execution                           | 309 |

| Error Reporting                                  | 309 |

| AIBStatus Word                                   | 309 |

| Error Code Breakdown                             | 310 |

| Specifications Relevant to Supported Interfaces  | 317 |

| Appendix A: Acronym Glossary                     | 319 |

| Appendix B: Co-Processor Platform Registers      |     |

| Sorted by Abbreviation                           | 321 |

| Sorted by Address                                | 324 |

| Appendix C: 4-Port Multi-Interface AIB Registers |     |

| Sorted by Abbreviation                           | 327 |

| Sorted by Address                                |     |

| Appendix D: Notices                              |     |

|                                                  |     |

| Index                                            | 333 |

# Figures

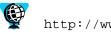

| Figure 2-1. Co-Processor Platform Block Diagram                         | 10  |

|-------------------------------------------------------------------------|-----|

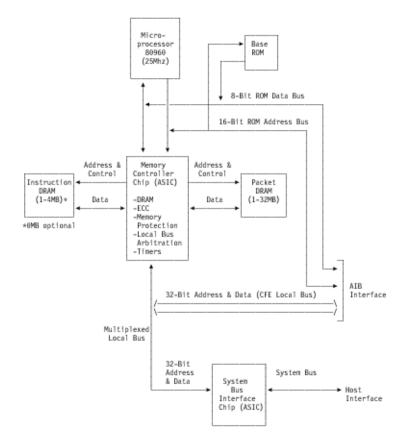

| Figure 2-2. Reset Delay Timing                                          | 11  |

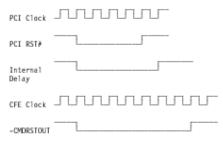

| Figure 2-3. Co-Processor Platform Memory Map (as viewed from the 80960) | 18  |

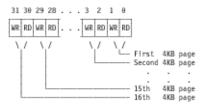

| Figure 3-1. Page Table Entry Format                                     | 25  |

| Figure 3-2. Sample Page Tables                                          | 26  |

| Figure 4-1. Memory Controller Chip Check-Bit Generation                 |     |

| Figure 4-2. Memory Controller Chip FEER Values                          | 37  |

| Figure 6-1. Co-Processor Platform Interrupt Controller                  |     |

| Figure 8-1. Intermediate Buffering                                      |     |

| Figure 8-2. Linked List Chaining                                        | 89  |

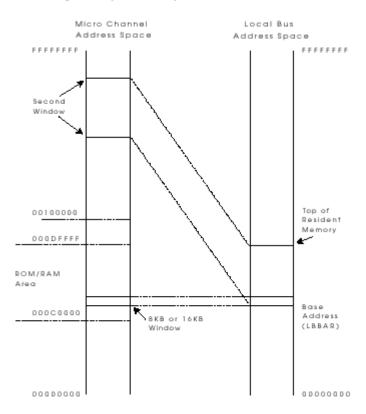

| Figure 8-3. Shared Memory Windows                                       |     |

| Figure 9-1. PCI Bus Intermediate Buffering                              | 132 |

| Figure 9-2. Linked List Chaining                                        | 136 |

| Figure 9-3. Shared Memory Windows                                       |     |

| Figure 12-1. AIB ROM VPD Structure                                      |     |

| Figure 13-1. Card Architecture                                          |     |

| Figure 13-2. Card Layout of the 4-Port Multi-Interface AIB—Top Side     |     |

| Figure 13-3. 100-Pin Connector Pinout                                   |     |

| Figure 13-4. Linked List Chaining                                       |     |

| Figure 13-5. CCR Chaining/Stopping Matrix                               |     |

| Figure 13-5. CFE Local Bus/AIB Interface Chip Bus Interface             |     |

| Figure 13-6. Homologation Circuit for Balanced Drivers                  |     |

| Figure 13-7. Homologation Circuit for Balanced Receivers                |     |

| Figure 13-8. TxD Block Diagram                                          |     |

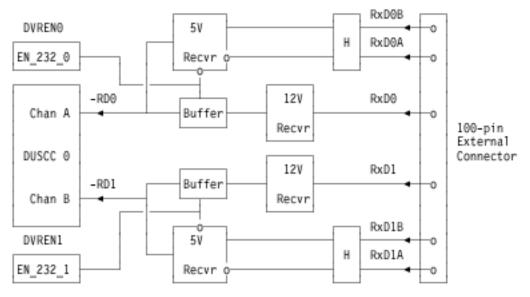

| Figure 13-9. RxD Block Diagram                                          |     |

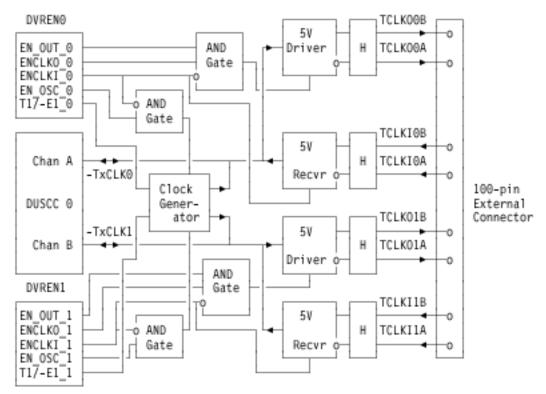

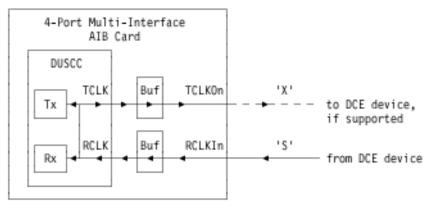

| Figure 13-10.TxCLK Block Diagram                                        |     |

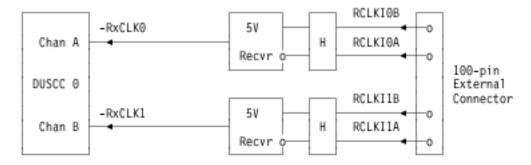

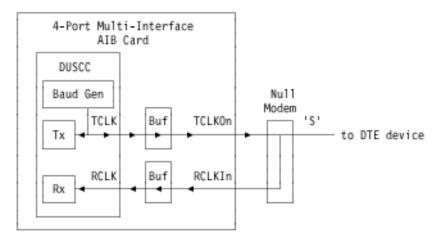

| Figure 13-11.RxCLK Block Diagram                                        |     |

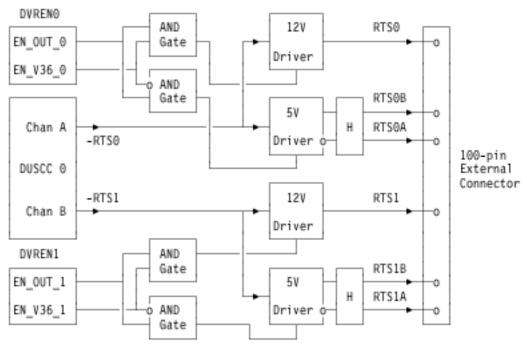

| Figure 13-12.RTS Block Diagram                                          |     |

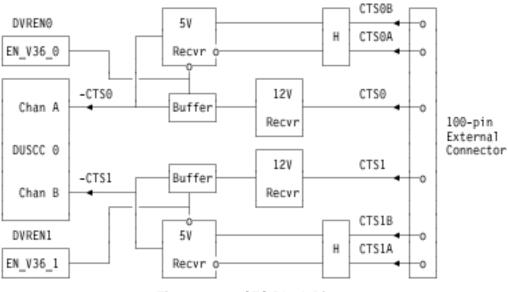

| Figure 13-13.CTS Block Diagram                                          |     |

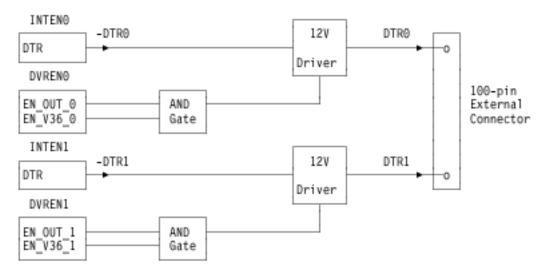

| Figure 13-14.DTR Block Diagram                                          | 240 |

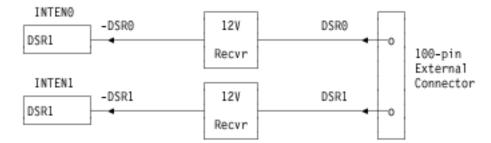

| Figure 13-15.DSR Block Diagram                                          |     |

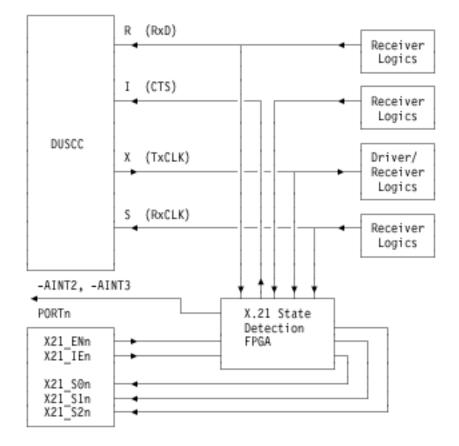

| Figure 13-16.X.21 State Detection Block Diagram                         |     |

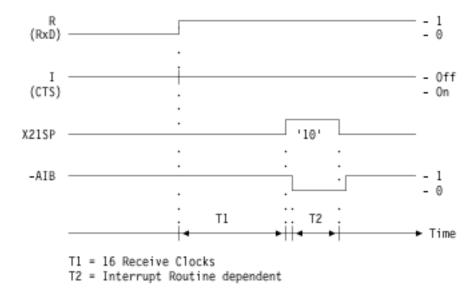

| Figure 13-17.Detection of Remote Ready                                  |     |

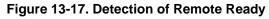

| Figure 13-17.Detection of Remote Uncontrolled Not Ready                 |     |

| Figure 13-19.Detection of Remote Controlled Not Ready                   |     |

| Figure 13-20.Detection of DCE Connection in Progress                    |     |

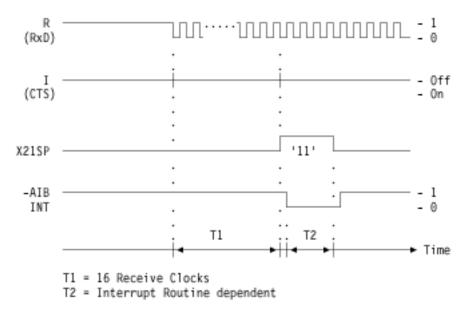

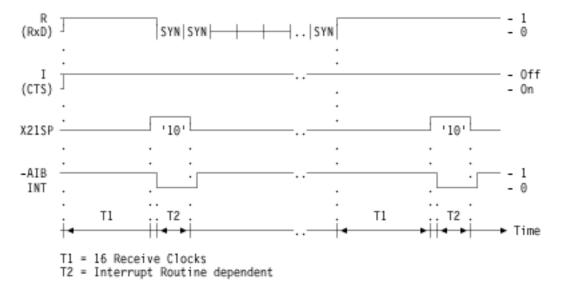

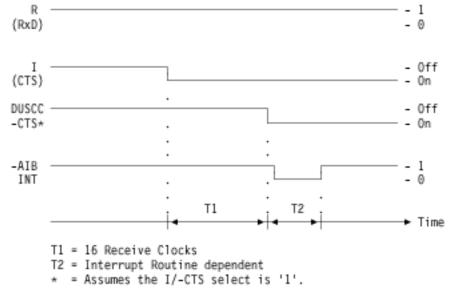

| Figure 13-21.Detection of DCE Ready for Data                            |     |

| Figure 13-22.Detection of DTE Call Request                              |     |

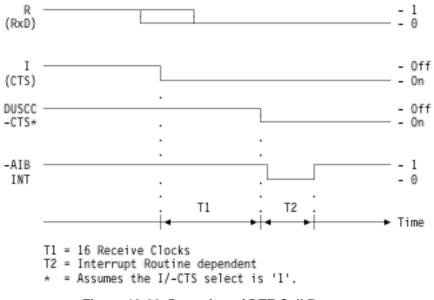

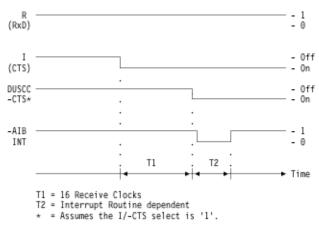

| Figure 13-23.Detection of DTE Call Accepted                             |     |

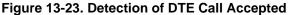

| Figure 13-24.Detection of Remote Clear                                  |     |

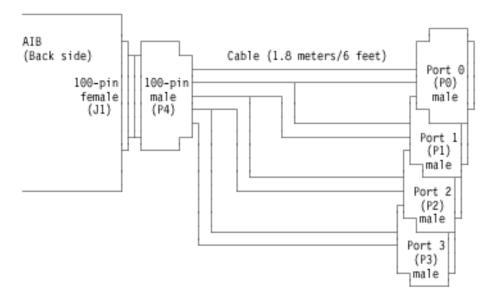

| Figure 13-25.AIB Cable Assembly                                         |     |

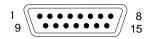

| Figure 13-26.15-Pin D-Shell Connector                                   |     |

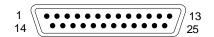

| Figure 13-27.25-Pin D-Shell Connector                                   |     |

|                                                                         |     |

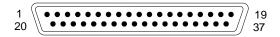

| Figure 13-28.37-Pin D-Shell Connector                                   |     |

| Figure 13-29.Port n Driver Enable Register Description                  |     |

| Figure 13-30.Port n Interrupt Enable Register Description               |     |

| Figure 13-31.Port n X.21 Enable Register Description                    |     |

| Figure 13-32.Port n X.21 Pattern Status Register Description            |     |

| Figure 13-33.X.21 DTE Operation                                         |     |

| Figure 13-34.X.21 DCE Operation — Low Speed                             |     |

| Figure 13-35.X.21 DCE Operation — High Speed                            |     |

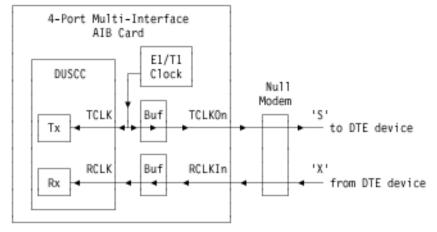

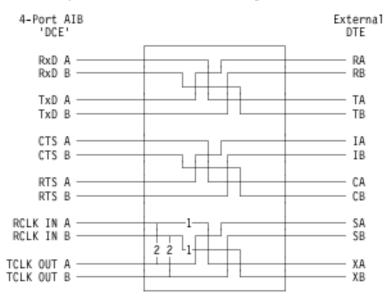

| Figure 13-36.Null Modem Connections                                     | 294 |

# Tables

| Table 1-1.               | Micro Channel Interface Chip Bus Master Performance (in MB/s)                       | 4  |

|--------------------------|-------------------------------------------------------------------------------------|----|

| Table 1-2.               | PCI Bus Master Performance (MB/sec)                                                 | 4  |

| Table 1-3.               | RadiSys ARTIC960 Co-Processor Platform (Micro Channel) Dimensions                   | 7  |

| Table 1-4.               | RadiSys ARTIC960 Co-Processor Platform (Micro Channel) Environment                  | 7  |

| Table 1-5.               | RadiSys ARTIC960 Co-Processor Platform (Micro Channel) Electrical                   | 7  |

| Table 1-6.               | RadiSys ARTIC960 PCI Co-Processor Platform (Micro Channel) Dimensions               | 8  |

| Table 1-7.               | RadiSys ARTIC960 PCI Co-Processor Platform (Micro Channel) Environment              | 8  |

| Table 1-8.               | RadiSys ARTIC960 PCI Co-Processor Platform (Micro Channel) Electrical               | 8  |

| Table 2-1.               | -                                                                                   | 12 |

| Table 2-2.               |                                                                                     | 13 |

| Table 2-3.               |                                                                                     | 13 |

| Table 2-4.               |                                                                                     | 13 |

| Table 2-5.               | -                                                                                   | 13 |

| Table 2-6.               |                                                                                     | 14 |

| Table 2-7.               |                                                                                     | 14 |

| Table 2-8.               |                                                                                     | 14 |

| Table 2-9.               | -                                                                                   | 15 |

| Table 2-10.              |                                                                                     | 15 |

| Table 2-11.              |                                                                                     | 17 |

| Table 2-12.              |                                                                                     | 19 |

| Table 3-1.               |                                                                                     | 24 |

| Table 3-2.               |                                                                                     | 24 |

| Table 3-3.               |                                                                                     | 25 |

| Table 5-1.               |                                                                                     | 12 |

| Table 6-1.               |                                                                                     | 14 |

| Table 7-1.               |                                                                                     | 19 |

| Table 7-1.<br>Table 7-2. |                                                                                     | 51 |

| Table 7-2.<br>Table 7-3. |                                                                                     | 51 |

| Table 7-3.<br>Table 7-4. | -                                                                                   | 52 |

| Table 7-4.<br>Table 7-5. |                                                                                     | 53 |

| Table 7-5.<br>Table 7-6. |                                                                                     | 57 |

|                          |                                                                                     |    |

| Table 7-7.<br>Table 8-1. |                                                                                     | 53 |

|                          |                                                                                     | 56 |

| Table 8-2.<br>Table 8-3. |                                                                                     | 58 |

|                          | 1                                                                                   | 33 |

| Table 8-4.               |                                                                                     | 92 |

| Table 8-5.               | SCB Register Access Summary                                                         |    |

| Table 8-6.               | Attention Codes                                                                     |    |

| Table 8-7.               | Interrupt Identifier Codes                                                          |    |

| Table 9-1.               | PCI System Bus Interface Chip Pin Description – PCI Signals (Alphabetical Order) 11 |    |

| Table 9-2.               | PCI System Bus Interface Chip Pin Description—Miscellaneous                         |    |

| Table 9-3.               | Miscellaneous Registers                                                             |    |

| Table 9-4.               | CFE Configuration Registers                                                         |    |

| Table 9-5.               | PCI Configuration Registers                                                         |    |

| Table 9-6.               | SCB Registers                                                                       |    |

| Table 9-7.               | DMA Channel Registers.                                                              |    |

| Table 9-8.               | BMCDB Local Bus Register Map                                                        |    |

| Table 9-9.               | Supported PCI Bus Commands 14                                                       | 19 |

| Table 9-10.  | Burst/Non-Burst Address Map                                      | 149 |

|--------------|------------------------------------------------------------------|-----|

| Table 9-11.  | SCB Register Access Summary                                      | 150 |

| Table 9-12.  | Prefetch Operation                                               | 152 |

| Table 9-13.  | Read Commands                                                    | 156 |

| Table 9-14.  | Attention Codes                                                  | 158 |

| Table 9-15.  | Interrupt Identifier Codes                                       | 160 |

| Table 9-16.  | CFE Local Bus Interrupt Sources                                  | 165 |

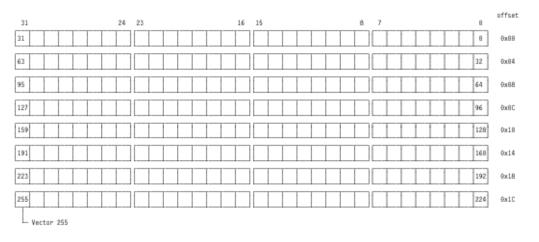

|              | Debug Port Interrupt Vector Assignment                           | 174 |

|              | ISP Fatal Error Codes                                            | 190 |

|              | LED Flashing Sequences                                           | 190 |

|              | ROMStatus Word (Base Card POST Errors)                           | 193 |

|              |                                                                  | 199 |

|              | AIBStatus Word                                                   | 200 |

|              | ROM Usage of Lower 1MB of Packet Memory                          |     |

|              | ROM Table Structure                                              | 203 |

|              | MEM Structure                                                    | 205 |

|              |                                                                  | 205 |

|              | SUCommands Structure                                             | 205 |

|              | RIC_Except Structure                                             | 206 |

|              | RIC_RDTEntry Structure                                           |     |

|              | MCAT Structure                                                   | 200 |

|              | Debug Structure                                                  | 209 |

|              | BaseOptions Structure                                            | 209 |

|              | RomPostStatus Structure                                          | 210 |

|              | Electrical Characteristics                                       | 210 |

|              | Environmental Characteristics                                    |     |

|              | Physical Characteristics                                         | 224 |

|              | •                                                                |     |

|              | 100-Pin External Connector (J1)                                  |     |

|              | CFE Local Bus/AIB Interface Chip Channel Descriptor Table (CDT)  |     |

|              | CFE Local Bus/AIB Interface Chip DMA Channel Vector Assignment   |     |

|              | Interrupt Vector Assignment                                      |     |

|              | Drivers/Receivers                                                |     |

|              | D-Shell Connectors Pin Assignment                                | 248 |

|              | D-Shell Connectors Pin Assignments for the AIB Cable             | 250 |

|              | AIB 100-Pin Wrap Plug                                            | 252 |

|              | Wrap Plugs for AIB Cable Connectors P0-P3                        | 252 |

|              | 4-Port Multi-Interface AIB Interrupts and DMA                    | 254 |

|              | AIB ROM Memory Map on the RadiSys ARTIC960 Co-Processor Platform |     |

|              | DCL Bus Memory Map                                               | 255 |

|              | FPGA Memory Map                                                  | 256 |

|              | CMOS DUSCC DCL Memory Map (Part 1 of 2)                          | 256 |

|              | CMOS DUSCC DCL Memory Map (Part 2 of 2)                          | 257 |

|              |                                                                  | 258 |

|              | CFE Local bus/AIB Interface Chip Interrupt Registers             | 259 |

| Table 13-21. | CFE Local Bus/AIB Interface Chip DCL Registers                   | 259 |

|              |                                                                  | 260 |

| Table 13-23. | AIBStatus Errors (AIB POST)                                      | 311 |

| Table 13-24. | Communication Standards Specifications                           | 317 |

| Table B-1.   | Co-Processor Registers (Sorted by Abbreviation)                  | 321 |

| Table B-2.   | Co-Processor Registers (Sorted by Address)                       |     |

# Introduction to the RadiSys ARTIC960 Co-Processor Platform

This chapter provides a brief description of the RadiSys ARTIC960 Co-Processor Platform, and serves as a quick reference guide to the major hardware components, functional subsystems, physical interfaces, and specifications.

# **Product Description**

The RadiSys ARTIC960 Co-Processor Platforms are 1-slot, add-in, I/O adapters for IBM 32-bit Micro Channel or PCI systems. The main engine for the co-processor is the Intel 80960C-Series microprocessor, which serves to off-load the system unit microprocessor of chores typically associated with I/O tasks. On-board storage includes from 1 to 16 megabytes (MB) of 80960 *packet* dynamic random-access memory (DRAM) and 1MB of *instruction* DRAM. The co-processor is capable of supporting up to 32MB of packet DRAM when it becomes available. A special order is required to configure the co-processor with 0 or 4MB of instruction DRAM.

The co-processor is shipped with 1MB of instruction memory and without packet memory. At least 1MB of packet memory must be installed for the platform to function. (Presently, plug-in packet memory modules are available in increments of 1, 4, 8, and 16MB.) If the instruction DRAM is not installed, the packet DRAM acts as both a data buffer and an instruction storage area for the 80960.

Also included are 128 kilobytes (KB) of read-only storage for the platform's power-on self-test (POST) and bootstrap loader. The RadiSys ARTIC960 PCI Co-Processor Platform also uses a 128-byte serial EPROM for the platform's configuration data. (A functional block diagram of the co-processor is shown in Figure 2-1.)

External support functions for the 80960 include five hardware timers, a high-performance Micro Channel interface, and a separate communications I/O bus (CFE Local Bus). This bus is consistent with the definition of the Common Front End (CFE) bus architecture.

The co-processor complies with the SCB (Subsystem Control Block) Move Mode architecture.

Communication-specific support is accomplished by the attachment of an application interface board (AIB). This is the same concept that is used on the IBM Realtime Interface Co-Processor Portmaster Adapter/A product; however, Portmaster Adapter Interface Boards (IBs) and the co-processor AIBs are not plug compatible. The AIB must contain all communication-specific hardware, such as the protocol chip and/or electrical interface drivers. In general, the AIB handles a mix of layer 1 and 2 functions, with a mix of layer 2 and 3 functions being handled by the 80960 base card microprocessor.

### **Processing Power**

The co-processor provides processing power through the on-board 80960C-Series processor. This enables the host processor to off load most processing chores.

Several co-processors, each containing a different type of AIB, can be installed in a computer to support attachment to a variety of devices such as:

- Various serial communications protocols

- Local area network (LAN) attachments

- Direct access storage devices (DASD)

- Small computer system interface (SCSI)

- Specialized application technology

- Realtime multitasking devices.

### Software

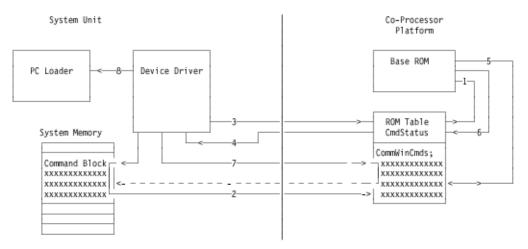

The software provided with the co-processor is segmented into two parts. The part that runs on the platform itself is called the *kernel*, and the portion that runs on the host computer is called *system unit support*.

The kernel is actually a collection of executables that provide the following capabilities:

- Realtime multi-tasking kernel

- System unit-to-adapter process communications

- Adapter-to-adapter process communications.

The system unit support is a collection of operating system executables that provide:

- Adapter status and configuration information

- System unit-to-adapter process communications

- Application loader

- Adapter dump facility

- Debug facilities.

### Compatibility

The RadiSys ARTIC960 Co-Processor Platform is a follow-on product to the IBM Realtime Interface Co-Processor Portmaster Adapter/A, and both operate in a Micro Channel environment. The RadiSys ARTIC960 PCI Co-Processor Platform is a follow-on product to the RadiSys ARTIC960 Co-Processor Platform, but it operates in a PCI environment. Because the micro processor changed in the first case and the system bus changed in the latter case, microcode written for either of the follow-on products may not be 100% compatible.

Some level of compatibility may be possible for those Postmaster applications written in "C" language. Refer to the *RadiSys ARTIC960 Co-Processor Platforms Programmer's Guide and Reference* for more information on programming features.

The RadiSys ARTIC960 Co-Processor Platform is intended to be compatible with 32-bit Micro Channel-based computers systems, including: IBM Personal System/2 Computers (excluding the Model 8570), IBM Industrial Computers (excluding the Model 7561), and RISC System/6000 Computers. The platform is designed to fit into only 32-bit card slots.

The RadiSys ARTIC960 PCI Co-Processor Platform is intended to be compatible with any full-length, 5V PCI slot in PCI-compliant systems; however, the PCI co-processor adapter may not configure in systems with COMPAQ or Award BIOS, and may not configure in IBM systems with previous-level BIOS.

### Performance

### **Memory Performance**

For applications requiring up to 5 megabytes-per-second (MB/s) of I/O throughput, a single memory bus architecture is chosen to reduce cost. An application requiring the full 5 MB/s communication bandwidth should consume roughly 30% of the 80960 Local Bus bandwidth. This would reduce the effective million instructions-per-second (MIP) rate of the 80960 from about 15 MIPs to 10 MIPs. This option, which must be special-ordered, requires that the instruction DRAM be removed from the co-processor.

To support data rates from 5MB/s up to 20MB/s and still have sufficient processing bandwidth available to support these rates, the co-processor is configured in a dual memory bus architecture. In this case, the instruction DRAM allows the 80960 to execute in parallel with I/O activity on the platform's Local Bus. The tradeoff of cost versus performance can be made by the specific application requirement. The application would determine how many MIPs are necessary to support a particular data rate.

On the 80960 bus, the Memory Controller Chip supports 3-1-1-1-0 cycles (36MB-per-second) to either memory. Up to four word bursts (quad word aligned) are supported. The Memory Controller Chip also supports 3-1-1-1 read cycles (2-1-1-1-1 write cycles) from the Local Bus to packet memory (4-1-1-1-1 to instruction memory). However, the Local Bus may burst more than four words. This translates to the following rates:

- 33 MB/s for 4-word bursts

- 40 MB/s for 8-word bursts

- 44 MB/s for 16-word bursts.

### Micro Channel-to-Local-Bus Performance

The Micro Channel Interface Chip interfaces a high-speed, 80MB/s Micro Channel interface to a high-speed Local Bus. This Local Bus has a **maximum** theoretical bandwidth of 100MB/s. Data rates achieved by the Micro Channel Interface Chip on the Local Bus are dependent on the size of the transfer and the speed of the Local Bus slave. Assuming a 64-byte burst to a zero-wait-state slave, the data rate is 84MB/s. For memory or slaves requiring wait states, the data rate may be much lower.

The data rate sustained on the Micro Channel is also dependent on the speed of the Local Bus slave. With the intermediate data buffering provided internal to the Micro Channel Interface Chip, 80MB/s can be sustained for an absolute minimum of 128 bytes.

Table 1-1 shows the maximum throughput between the Local Bus and the Micro Channel for Bus Master accesses, assuming 40 or 80MB/s streaming data on the Micro Channel, and 50MB/s (1 wait state) or 100MB/s (0 wait states) Local Bus accesses.

| Micro Channel Speed | Local Bus Speed | Throughput |  |

|---------------------|-----------------|------------|--|

| 40                  | 50              | 32         |  |

| 80                  | 50              | 41         |  |

| 40                  | 100             | 40         |  |

| 80                  | 100             | 55         |  |

Table 1-1. Micro Channel Interface Chip Bus Master Performance (in MB/s)

### **PCI-to-Local-Bus Performance**

The PCI System Bus Interface Chip interfaces a synchronous, 132-MB/sec PCI bus interface to a high-speed local bus. The local bus has a maximum theoretical bandwidth of 100 MB/sec. Data rates achieved by the PCI System Bus Interface Chip on the local bus are dependent on the size of the transfer and the speed of the local bus slave. For memory or slaves requiring wait states, the data rate may be much lower.

The data rate sustained on the PCI bus also is dependent on the speed of the local bus slave. With the intermediate data buffering provided internal to the PCI System Bus Interface Chip, 132MB/sec can be sustained for an absolute minimum of 128 bytes.

Table 1-2 shows the maximum measured throughput between the CFE local bus and the PCI bus for Bus Master channel accesses, assuming a zero wait state target on the PCI bus, for the CFE local bus operating at 25 MHz for 1-wait-state and 0-wait-state slaves.

| CFE Local Bus Speed (MHz, ws) | Throughput |

|-------------------------------|------------|

| 25,0                          | 90MB/sec   |

| 25,1                          | 35MB/sec   |

### Table 1-2. PCI Bus Master Performance (MB/sec)

- 0 wait states cannot be used when accessing base card memory. Refer to "Memory Performance" for an explanation of memory access rates.

- These numbers are for general reference. Several variables can influence the actual throughput, which may be higher or lower based on these variables.

### **Diagnostics**

The ROM-resident power-on diagnostics are initiated automatically with each power-on sequence of the computer system containing the co-processor. (Refer to *Adapter Initialization and POST* on page 181 for a detailed description of the ROM-resident power-on diagnostics.)

The power-on diagnostics contained on the Micro Channel Startup/Option Diskette or on the PCI OS/2 Support Diskette verify correct operation of the co-processor and perform tests of the following:

- 80960 microprocessor

- Timer

- System Bus

- Memory Protection

- Local Bus

- Memory

- Debug Port.

# **Hardware Components**

- Microprocessor (80960C)

- 25MHz operation

- 3-1-1-1 burst operation to DRAM

- Vectored interrupt support.

- Memory (DRAM and ROM)

- Packet memory (DRAM SIMM) 1 to 16MB, 1 to 3 wait states

- Instruction memory (DRAM SOJ modules) 1 or 4MB, 1 to 3 wait states

- ROM, 128KB, 6 wait states.

- Micro Channel Interface Chip

- Micro Channel Bus Master interface chip

- 64-bit, 100-nanosecond streaming data master and slave on Micro Channel

- 80960 bursting bus interface to CFE Local Bus.

- PCI System Bus Interface Chip

- Two Bus Master channels, addressable from the CFE Local Bus

- Slave write buffer (128 bytes) for better PCI utilization

- Slave prefetch read buffer (128 bytes) for better PCI utilization

- Support of access to the CFE Local Bus address space from both PCI I/O and memory address spaces

- PCI data and address parity support

- Memory Controller Chip

- Two independent DRAM controllers (up to 32MB each)

- 80960C-Series interface

- 25MHz operation

- 32-bit CFE Local Bus interface

- Local Bus arbiter

- Memory protection unit

- Supports 3-1-1-1 memory read cycles; 2-1-1-1 memory write cycles

- ECC generation and checking for both DRAMs

- Five hardware timers

- Asynchronous Serial Debug Port

- Optional AIBs.

# **Hardware Considerations**

### RadiSys ARTIC960 Co-Processor Platform (Micro Channel)

The RadiSys ARTIC960 Co-Processor Platform supplies a clock signal (25MHz) to the AIB. This signal **must** be terminated at all times. Normally, the AIB circuitry terminates this signal.

The RadiSys ARTIC960 Co-Processor Platform has a two-pin jumper (J3), which provides an on-card resistance-capacitance (RC) termination for the clock. If you do not have an AIB installed, you should make certain that jumper J3 is between positions 2 and 3 to terminate the clock signal on the RadiSys ARTIC960 Co-Processor Platform.

When an AIB is installed, this jumper must be moved to positions 1 and 2, which is a "no-connect" position for the on-card termination circuitry, and allows the termination to take place using the AIB circuitry.

Damage to the Memory Controller Chip and/or the Micro Channel Interface Chip could occur if the termination is not used when the co-processor is powered up without an AIB attached.

### RadiSys ARTIC960 PCI Co-Processor Platform

The RadiSys ARTIC960 PCI Co-Processor Platform supplies a 25 MHz clock to the AIB. This clock signal, at all times, must be terminated. It is the responsibility of the AIB to terminate this signal.

The RadiSys ARTIC960 PCI Co-Processor Platform offers additional write protection for the base card ROM through the use of a 3-pin jumper (P4). When the jumper is in positions 2 and 3, all writes are enabled. When the jumper is in positions 1 and 2, writes are disabled.

To take advantage of the 80960CF data cache, the processor bus is wired to the Memory Controller Chip to allow the use of the 80960CF data cache. See 809ADD for information on how this mapping works.

# **Functional Subsystems**

- Memory Protection

- Error Checking and Correction

- Timer

- Interrupt Controller

- CFE Local Bus

- System Bus Interface

- Debug

- AIB Interface.

# **Physical Interfaces**

- Co-processor platform to host computer

- Co-processor platform to AIB.

# **Specifications**