## VolantPCI Component Specification Version 1.01

Document Number BOC-PCI-09003

August 1, 1997

# Preface

This document describes the functions of the VolantPCI VLSI component. VolantPCI provides an efficient means of interfacing serial communication chips and other peripheral components to a high-speed bursting local bus. VolantPCI uses a dual-bus structure, containing eight independent DMA channels, with linked-list chaining and automatic appended I/O operations.

# Contents

| 1.0 VolantPCI Component Overview                 |    |

|--------------------------------------------------|----|

| 1.1 General                                      |    |

| 1.2 Performance                                  |    |

| 1.3 RAS Highlights                               |    |

| 1.4 VolantPCI Block Diagram                      |    |

| 1.5 VolantPCI Signal Description                 | 10 |

| 1.5.1 PCI Bus Signals                            |    |

| 1.5.2 VolantPCI AIB Bus Signals                  |    |

| 1.5.3 VolantPCI Interrupt Controller Signals     | 14 |

| 1.5.4 VolantPCI Test                             |    |

| 1.5.5 VolantPCI Miscellaneous Signals            | 15 |

| 1.6 Vero Compatibility                           | 16 |

| 1.6.1 Interrupts                                 | 16 |

| 1.6.2 AIB Bus                                    | 16 |

| 1.6.3 DMA                                        | 16 |

| 1.6.4 Setup/Configuration                        | 17 |

| 1.6.5 PIO's                                      | 17 |

| 1.6.6 Multi-Master Mode                          | 17 |

| 1.7 VolantPCI Register Address Map               |    |

| 1.7.1 Register Reset States                      |    |

| 1.7.2 DMA Registers                              |    |

| 1.7.3 PCI Bus Related Registers                  |    |

| 1.7.4 Interrupt Related Registers                |    |

| 1.7.5 AIB Bus Related Registers                  |    |

| 1.7.6 Miscellaneous Registers                    |    |

|                                                  |    |

| 2.0 VolantPCI DMA Controller                     |    |

| 2.1 General                                      |    |

| 2.2 DMA FIFO                                     |    |

| 2.3 Channel Descriptor Register Set              |    |

| 2.3.1 Channel Control Register (CCR)             |    |

| 2.3.2 DMA Channel Command Registers (DCCR)       |    |

| 2.3.3 Memory Pointer Register (MPR)              |    |

| 2.3.4 Transfer Count Register (TCR)              |    |

| 2.3.5 Chain Pointer Register (CPR)               |    |

| 2.3.6 AIB Address 1/2 Register (AIB_ADDR 1/2)    |    |

| 2.3.7 AIB_OP1 DATA Register (AIB_OP1)            |    |

| 2.3.8 AIB_OP2 DATA Register (AIB_OP2)            |    |

| 2.3.9 DMA Interrupt Status Registers (DISR)      |    |

| 2.3.10 Enhanced Status Pointer Register (ESP)    |    |

| 2.4 Linked List Chaining (LLC)                   |    |

| 2.4.1 Modes of List Chaining                     |    |

| 2.4.2 Linked List Chaining/Stopping              |    |

| 2.4.3 Adding CDB's to a Chain                    |    |

| 2.5 DMA Miscellaneous Registers                  |    |

| 2.5.1 AIB Bus Global DMA Command Register (GDCR) |    |

| 2.5.2 DMA FIFO Residual Count registers (DFRC)   | 20 |

| 2.5.3 DMA Buffer Data registers (DBD)            |    |

|                                                  |    |

| 3.0 VolantPCI Interrupts                         | 40 |

| 3.1 General                                           | 41 |

|-------------------------------------------------------|----|

| 3.2 Interrupt Sources                                 | 41 |

| 3.2.1 DMA Interrupts                                  | 41 |

| 3.2.2 AIB Interrupts                                  | 41 |

| 3.2.3 AIB ERROR Interrupt                             | 41 |

| 3.2.4 PIO Interrupts                                  | 41 |

| 3.2.5 Interrupt Priorities                            | 42 |

| 3.3 Programmable Options                              |    |

| 3.3.1 Interrupt Initialization register (IIR)         |    |

| 3.3.2 Interrupt Mask register (IMR)                   |    |

| 3.3.3 Interrupt Status register (ISR)                 |    |

| 3.3.4 AIB Error Interrupt Mask register (EIMR)        |    |

| 3.4 Interrupt Commands                                |    |

| 3.4.1 AIB INT0/1 End-of-Interrupt (EOI0/1) commands   |    |

| 3.4.2 Interrupt Vector Register (IVR)                 |    |

|                                                       |    |

| 4.0 VolantPCI AIB Bus Interface                       | 51 |

| 4.1 General                                           |    |

| 4.1.1 AIB Arbiter                                     |    |

| 4.2 AIB Initialization registers                      |    |

| 4.2.1 Chip Select Definition registers (CSD0-3)       |    |

| 4.2.2 DMA Acknowledge Pulse Width Registers (DAPW)    |    |

| 4.2.2 DMA Acknowledge Fulse width Registers (DAT W)   |    |

| 4.2.5 AID Dus Configuration Register (ACR)            | 57 |

| 5.0 PCI Bus Interface                                 | 50 |

| 5.1 PCI Bus Operation                                 |    |

| 5.2 PCI Bus target                                    |    |

| e e                                                   |    |

| 5.2.1 AIB bus access                                  |    |

| 5.2.2 Internal Registers Accesses                     |    |

| 5.3 PCI Bus Master                                    |    |

| 5.3.1 Internal Arbitration for the PCI Bus            |    |

| 5.3.2 Multiple VolantPCI Chips on the PCI Bus         |    |

| 5.4 PCI Bus Configuration Registers                   |    |

| 5.4.1 Device/Vendor ID (DEVID)                        |    |

| 5.4.2 Host Status/Command Register (HSCR)             |    |

| 5.4.3 Class Code/Revision ID Register (CCRID)         |    |

| 5.4.4 Host Miscellaneous Functions Register (HMFR)    |    |

| 5.4.5 Register Base Address Register (REGBAR)         |    |

| 5.4.6 AIB Base Address Register (AIBBAR)              |    |

| 5.4.7 Subsystem ID (SSID)                             |    |

| 5.4.8 Latency/Grant/Interrupt Register (LGIR)         | 67 |

|                                                       |    |

| 6.0 VolantPCI Miscellaneous Registers                 |    |

| 6.1.1 Configuration Register (CFGR)                   |    |

| 6.1.2 LED Enable Register (LER)                       |    |

| 6.1.3 Clock Timer Register (CTR)                      | 71 |

| 6.2 Programmable I/O Control Registers                |    |

| 6.2.1 PIO Configuration Registers (PIOCFG)            |    |

| 6.2.2 PIO Status Registers (PIOSTAT)                  |    |

| 6.2.3 Serial EPROM Register (SER)                     | 74 |

|                                                       |    |

| Appendix A. VolantPCI Pin Name/Number Cross Reference | 77 |

|                                                       |    |

| Appendix B. PIO Functional Diagrams                   | 81 |

|                                                       |    |

| Appendix C. VolantPCI Electrical Specifications           | 83 |

|-----------------------------------------------------------|----|

| C.1 Absolute Maximum Ratings                              | 83 |

| C.2 Operating Conditions                                  | 83 |

| C.3 Recommended Connections                               | 83 |

| C.3.1 Decoupling                                          | 83 |

| C.4 Specifications for the PCI Bus Interface              | 84 |

| C.5 DC Specifications                                     | 84 |

| C.5.1 DC Specifications for the AIB Bus and Misc. Signals | 84 |

| C.6 AC Timing Specifications                              | 85 |

| C.6.1 PCI Bus Timings                                     | 85 |

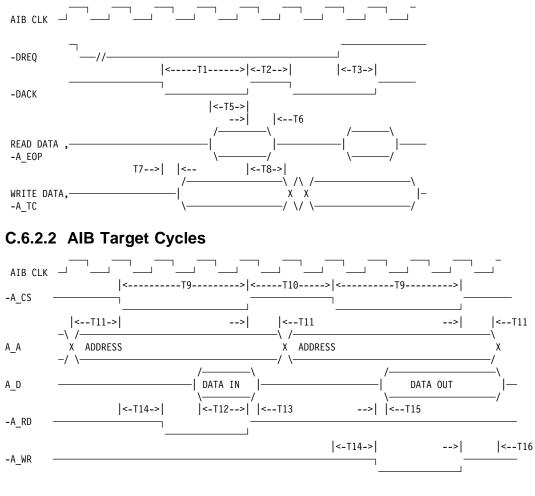

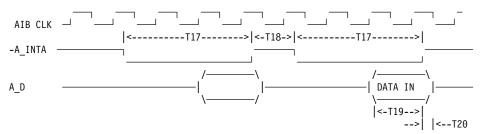

| C.6.2 AIB Bus Timings                                     | 85 |

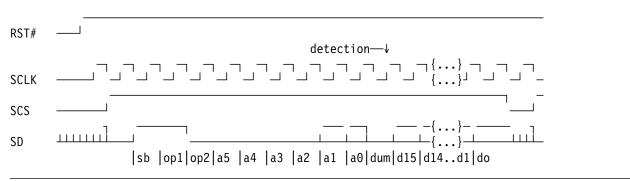

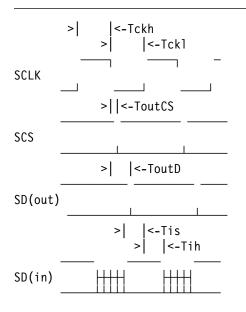

| C.6.3 VolantPCI Serial EPROM Interface Timing             | 87 |

| Appendix D. VolantPCI Test Information                    | 89 |

| D.1 JTAG TAP Controller Features                          | 89 |

| D.1.1 Boundary Scan                                       | 89 |

| D.2 Scan Testing                                          | 95 |

| D.3 RAM Isolation Testing                                 | 95 |

| D.4 Driver Tri-State                                      | 96 |

| Appendix E. Volant Errata                                 | 97 |

# Figures

| 1.  | Major Functional Blocks in VolantPCI                               | 10 |

|-----|--------------------------------------------------------------------|----|

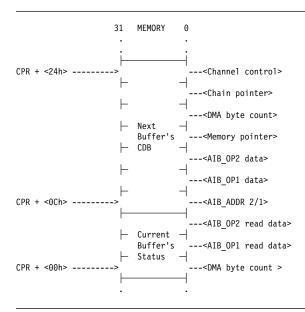

| 2.  | Linked List Chaining: Vero Compatibility Mode                      | 35 |

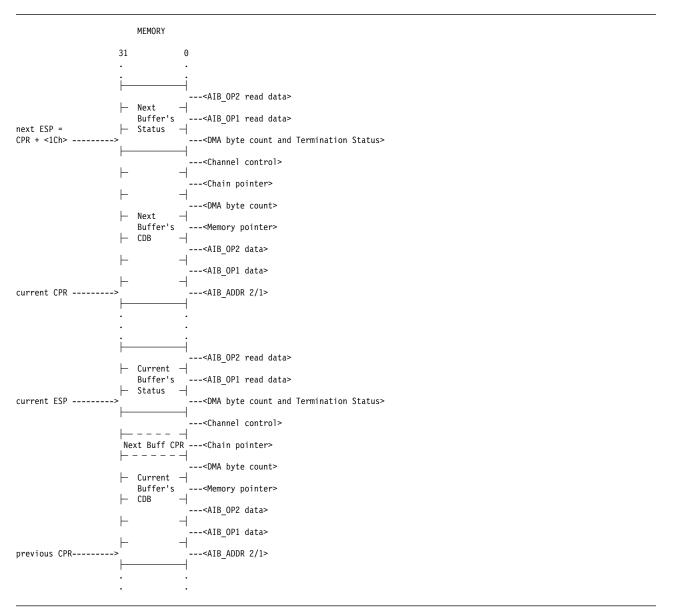

| 3.  | Linked List Chaining: VolantPCI Enhanced Status Mode List Chaining | 37 |

| 4.  | PCI Bus Address to AIB Address Map                                 | 51 |

| 5.  | Connecting two VolantPCI chips using Multi-Master                  | 60 |

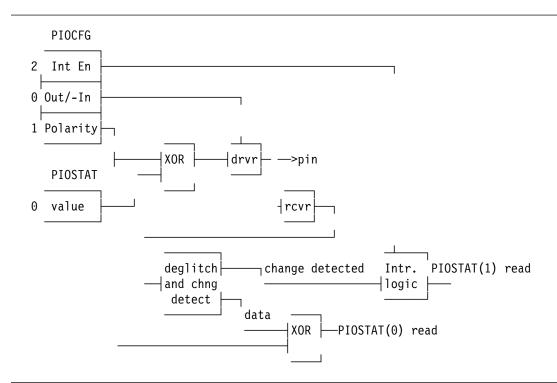

| 6.  | Input/Output PIO                                                   | 81 |

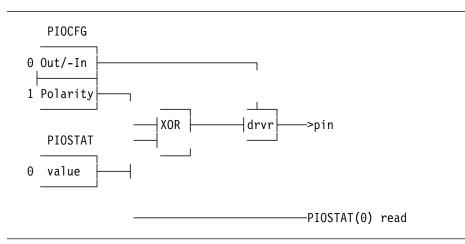

| 7.  | Output-Only PIO                                                    | 81 |

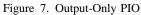

| 8.  | Output-Only w/clock PIO                                            | 82 |

| 9.  | SEPROM read timing                                                 | 87 |

| 10. | SCLK, SCS, SD timing                                               | 88 |

|     |                                                                    |    |

# Tables

| 1.  | PCI bus specific signals                         | 11 |

|-----|--------------------------------------------------|----|

| 2.  | VolantPCI AIB Bus Signals                        | 13 |

| 3.  | VolantPCI Interrupt Controller Signals           | 14 |

| 4.  | VolantPCI Clocks and Test                        | 14 |

| 5.  | VolantPCI Miscellaneous Signals                  | 15 |

| 6.  | VolantPCI Reset Conditions                       | 18 |

| 7.  | VolantPCI DMA Register Set                       | 19 |

| 8.  | PCI Bus Registers                                | 19 |

| 9.  | VolantPCI Interrupt Related Registers            | 20 |

| 10. | VolantPCI AIB Bus Registers                      | 20 |

| 11. | VolantPCI Miscellaneous Registers                | 20 |

| 12. | VolantPCI DMA Channel Descriptor Table Registers | 22 |

| 13. | VolantPCI DMA Channel Vector Assignment          | 42 |

| 14. | VolantPCI Maximum Ratings (referenced to Vss)    | 83 |

| 15. | VolantPCI Operating Conditions                   | 83 |

| 16. | VolantPCI AIB Bus and Misc. Signals              | 84 |

| 17. | Timings                                          | 86 |

| 18. | VolantPCI Serial EPROM Interface Timings         | 88 |

| 19. | VolantPCI JTAG Interface                         | 89 |

| 20. | VolantPCI JTAG Interface                         | 89 |

| 21. | VolantPCI Scan Chains                            | 95 |

| 22. | RAM Testing                                      | 95 |

|     |                                                  |    |

## **1.0 VolantPCI Component Overview**

## 1.1 General

The major highlights of VolantPCI are listed below:

- Custom ASIC using LSI's 3.3v, LCB600K 0.6µ technology

- Eight-channel DMA controller

- One Sixteen-byte data buffer per channel

- PCI Local Bus interface

- One Application Interface Bus (AIBs)

- Support of Linked List Chaining

- Support of AIB I/O operations

- 32 General Purpose Input/Output Pins (PIO)

- 3.3V operation

- 208 PQFP

- up to 33 Mhz operation

- JTAG Support

VolantPCI interfaces a high-speed PCI Bus to one independent Application Interface Bus (AIB). Eight DMA channels provide support for transfers between the Local Bus and the AIB.

Each DMA channel supports Linked List Chaining, the ability for the channel to auto-initialize its registers from a predefined list in PCI address space. Each DMA also has the ability to append I/O operations within the list chain operation.

### 1.2 Performance

Each DMA channel is capable of supporting zero-wait-state data transfers to the PCI Bus for a maximum of 4 four-word transfers, or a peak throughput of 57 MBytes/sec at 25 Mhz, 75 Mbytes/sec at 33 Mhz (assuming AWDDDDT). VolantPCI rearbitrates for the Local Bus after each DMA channels' access.

Performance for DMA list chaining is slightly higher than for DMA data transfers. (Chaining operations burst up to 7 words.)

VolantPCI also accesses the AIB bus as a Bus Master. The AIB bus can support 4-state (160 ns at 25 Mhz and 121 ns at 33 Mhz) bus cycles to 8-bit devices, or a maximum rate of 6.25 MBytes/sec at 25 Mhz and 8.3 MBytes/sec at 33 Mhz (50 - 66 MBits/sec).

**Sustained Throughput** The following factors influence the amount of data throughput sustained between the PCI Bus and one of the AIBs:

- AIB device cycle time

- AIB device buffer size

- Frequency of linked list chaining

- Frequency of DMA executed AIB I/O operations (AIB OP's)

- PCI Bus utilization by other master devices

- The frequency of AIB Interrupt Acknowledge cycles

## 1.3 RAS Highlights

VolantPCI provides the following RAS support:

- · Local Bus address and data parity generation and checking

- Gate Array ID (CCRID) register, providing a revision level for VolantPCI.

- JTAG Chip Testing Support

Note that VolantPCI does not generate or check parity for its internal structures.

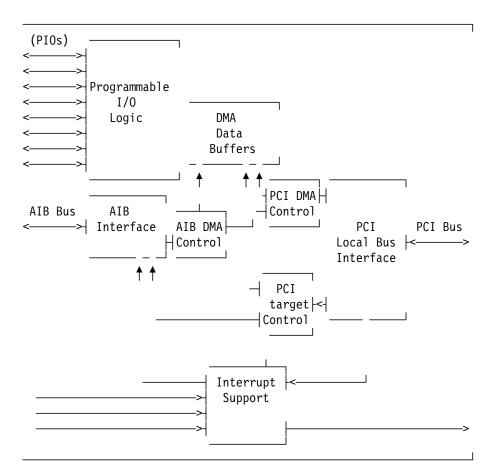

## 1.4 VolantPCI Block Diagram

Figure 1. Major Functional Blocks in VolantPCI

## 1.5 VolantPCI Signal Description

The following tables provide a description of each signal in the VolantPCI module. See Appendix A, "VolantPCI Pin Name/Number Cross Reference" on page 77 for module pin number information.

## 1.5.1 PCI Bus Signals

| Name    | Type Description |                                                                                                                                                                                                                                                                        |  |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FRAME#  | I/O<br>PCI       | <b>Cycle Frame</b> indicates the beginning and duration of a PCI access. This signal is driven by VolantPCI as an initiator and received as a target.                                                                                                                  |  |

| IRDY#   | I/O<br>PCI       | <b>Initiator Ready</b> indicates the initiator's ability to complete the current data phase of the transaction. This signal is driven by VolantPCI as an initiator and received by VolantPCI as a target.                                                              |  |

| TRDY#   | I/O<br>PCI       | <b>Target Ready</b> indicates the target's ability to complete the current data phase of the transaction. This signal is driven by VolantPCI as a target and received by VolantPCI as an initiator.                                                                    |  |

| STOP#   | I/O<br>PCI       | <b>Stop</b> indicates the current target is requesting the initiator to stop the current transaction. This signal is driven by VolantPCI as a target and received by VolantPCI as an initiator.                                                                        |  |

| pAD31:0 | I/O<br>PCI       | Address/Data Bits 31-0 are used by the PCI initiator to address memory and I/O targets. These signals are also used to select the VolantPCI chip for target operations.                                                                                                |  |

| CBE3:0# | I/O<br>PCI       | <b>Bus Command/Byte Enables</b> are driven by VolantPCI as a master and received as a target. During the address cycle they contain the bus command. During data cycles they are used as byte enables and determine which bytes of data are valid for each data cycle. |  |

| PAR     | I/O<br>PCI       | <b>PCI Parity bit</b> provides a single bit of even parity across AD(31:0) and CBE(3:0)#. It is driven by the device supplying address or data and checked by the device receiving the address or data.                                                                |  |

| IDSEL   | I                | <b>Initialization Device Select</b> selects VolantPCI during configuration read and write transactions.                                                                                                                                                                |  |

| DEVSEL# | I/O<br>PCI       | <b>Device Select</b> is driven by VolantPCI to indicate that VolantPCI is selected as a target. This signal is received by VolantPCI as an initiator to indicate that a device has been selected.                                                                      |  |

| PERR#   | I/O<br>PCI       | <b>Parity Error</b> is used to report data parity errors during all PCI transactions (except Special Cycle). VolantPCI asserts this signal when detecting a parity error on received data, and receives this signal when driving data.                                 |  |

| SERR#   | O<br>PCI         | <b>System Error</b> is used to signal catastrophic errors. It is driven, when enabled, if an address parity error is detected.                                                                                                                                         |  |

| CLK     | I                | <b>Clock</b> provides timing for all transactions on the PCI Bus and internal functions.                                                                                                                                                                               |  |

| INTA#   | O<br>PCI         | <b>Interrupt</b> is driven active when VolantPCI requires interrupt service by the system. This driver is open-drain.                                                                                                                                                  |  |

| RST#    | I                | <b>PCI Reset</b> when driven active immediately causes VolantPCI to tri-state all of its PCI drivers. All VolantPCI functions are reset and do not operate until this line is released.                                                                                |  |

| REQ#    | O<br>PCI         | Request is driven active when VolantPCI desires access to the bus as a master.                                                                                                                                                                                         |  |

| Table 1 (Page 1 of 2). PCI bus specific signals |      |                                                                                            |  |

|-------------------------------------------------|------|--------------------------------------------------------------------------------------------|--|

| Name                                            | Туре | Description                                                                                |  |

| GNT#                                            | Ι    | <b>Grant</b> indicates to VolantPCI that it has been granted master access to the PCI Bus. |  |

## 1.5.2 VolantPCI AIB Bus Signals

| Name      | Туре | ype Description                                                                                                                                                                                                                                                                                                |  |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| a_A17:2   | 0    | AIB Address(17-2)                                                                                                                                                                                                                                                                                              |  |

|           |      | These pins function as the 16-bit address bus during an AIB bus cycle. All DMA data transfers use implicit addressing of the I/O device with the DACK signals and therefore these signals are unknown during DMA cycles.                                                                                       |  |

|           |      | The bits are numbered from 17 to 2 to simplify conversion of PCI Bus addresses to AIB bus addresses. All access to the AIB must be byte accesses to byte-aligned addresses.                                                                                                                                    |  |

| a_D7:0    | I/O  | AIB Data(7-0)                                                                                                                                                                                                                                                                                                  |  |

|           |      | These pins function as the 8-bit data bus during an AIB bus cycle. These pins are outputs during writes and inputs during reads.                                                                                                                                                                               |  |

| -aWR      | 0    | -AIB Write is driven low during a write operation to an AIB target device.                                                                                                                                                                                                                                     |  |

| -aRD      | 0    | -AIB Read is driven low during a read operation to an AIB target device.                                                                                                                                                                                                                                       |  |

| -aCS3:0   | 0    | -AIB Chip Select(3-0) are driven active when a valid address decode is detected for the address ranges defined in the CSD0-3 registers.                                                                                                                                                                        |  |

| -aRESET   | 0    | -AIB Reset is used to reset the AIB bus. It is driven active/inactive synchronous to the RST# input signal from the PCI Bus, and can also be driven active by writing the ACR register to reset AIB devices.                                                                                                   |  |

| -aERROR   | I    | -AIB Error input is driven by AIB logic when any defined critical error occurs.<br>This will cause vector #232 (E8h) to be generated. (see 3.2.3, "AIB ERROR<br>Interrupt" on page 41).                                                                                                                        |  |

| aCLK      | 0    | AIB Clock is the AIB Bus reference clock.                                                                                                                                                                                                                                                                      |  |

|           |      | This clock is equal in frequency to the local bus clock. See 4.2.3, "AIB Bus Con-<br>figuration Register (ACR)" on page 57.                                                                                                                                                                                    |  |

| -aDREQ7:0 | Ι    | -DMA Request(7-0) are the 8 DMA request signals that AIB bus devices use to request DMA service. These signals are asynchronous inputs and should be driven inactive in response to the device receiving the corresponding DACK signal.                                                                        |  |

| -aDACK7:0 | 0    | <b>-DMA Acknowledge(7-0)</b> are the 8 DMA acknowledge signals that the DMA controller drives to the AIB Bus when the corresponding DREQ is being serviced.<br>The duration of these signals are programmable within the DAPW registers. See 4.2.2, "DMA Acknowledge Pulse Width Registers (DAPW)" on page 56. |  |

| -aEOPTC   | I/O  | <b>-DMA End-of-Process/Terminal Count</b> is a synchronous signal used for termi-<br>nation of the DMA channels on a bus. This signal is an output " <b>TC</b> " for DMA<br>transmit channels, and an input " <b>EOP</b> " for DMA receive channels.                                                           |  |

|           |      | As an output, TC is driven active synchronous with the data DACK transfer on which a DMA terminal count condition occurs.                                                                                                                                                                                      |  |

|           |      | As an input, EOP is received synchronously with the data DACK and can<br>optionally cause a DMA channel to flush the current buffer, stop, interrupt, or<br>chain.                                                                                                                                             |  |

## 1.5.3 VolantPCI Interrupt Controller Signals

| Table 3. VolantPCI Interrupt Controller Signals |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| -aINT3:0                                        | Ι    | <ul> <li>-AIB Interrupts(3-0) are four separate interrupt input signals that are driven active by devices on the AIB bus when interrupt service is requiredA_INT(1-0) can be optionally programmed to require the interrupting device to supply an 8-bit interrupt vector when the corresponding INTACK signal is driven active. Otherwise these inputs can be used as direct interrupt inputs with the vector being automatically supplied by the VolantPCI chip.</li> <li>When operating -AIB_INT(0) or -AIB_INT(1) in interrupt acknowledge mode, the interrupt must be cleared at its source, AND the appropriate EOI to the interrupt controller must be issued, or interrupts below that prioritization level will be locked out (see 3.4.1, "AIB INT0/1 End-of-Interrupt (EOI0/1) commands" on page 48).</li> </ul> |  |

| -aINTACK1:0                                     | 0    | -AIB Interrupt Acknowledge(1-0) function as the interrupt acknowledge for the AIB_INT(1-0) signals when the AIB_INT(1-0) signals are programmed in vectored mode.         When a device uses the -AIB_INT(1-0) signals and the VolantPCI chip is programmed to request an external vector, it must be capable of responding to the corresponding -AIB_INTACK(1-0) signal by driving an 8-bit interrupt vector on lines D(7-0) during the interrupt acknowledge cycle.                                                                                                                                                                                                                                                                                                                                                      |  |

## 1.5.4 VolantPCI Test

| Table 4. VolantPo | Table 4. VolantPCI Clocks and Test |                                                                                                                                                                                                           |  |

|-------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name              | Vame Type Description              |                                                                                                                                                                                                           |  |

| JTAG-TDI          | Ι                                  | <b>Serial Test Data IN</b> is used during JTAG chip testing. This pin should be pulled up to Vdd external to the chip during normal operation.                                                            |  |

| JTAG-TDO          | 0                                  | Serial Test Data Out is used during JTAG chip testing.                                                                                                                                                    |  |

| JTAG-TCK          | Ι                                  | <b>Test Clock</b> is used during JTAG chip testing. This pin should be pulled up to Vdd external to the chip during normal operation.                                                                     |  |

| JTAG-MOD          | Ι                                  | <b>Test MODE</b> is used during JTAG testing of the chip. This pin should be pulled up to Vdd external to the chip during normal operation.                                                               |  |

| JTAG-RST#         | Ι                                  | <b>Test Logic Reset</b> is used during JTAG testing of the chip. This pin should be pulled down to Vss external to the chip during normal operation.                                                      |  |

| ScanMuxSel#       | Ι                                  | <b>Scan Mux Select</b> is used by the chip manufacturer to test the chip. This pin should be pulled up to Vdd external to the chip during normal operation.                                               |  |

| ScanTestEn#       | Ι                                  | <b>Scan Test Enable</b> is used by the chip manufacturer to test the chip. This pin should be pulled up to Vdd external to the chip during normal operation.                                              |  |

| PTSTOUT           | 0                                  | <b>P Test Output</b> is used by the chip manufacturer to test the chip. This pin must be left unconnected.                                                                                                |  |

| IDDTST            | I                                  | <b>IDD Test</b> is used by the chip manufacturer to test the chip. When driven high, all chip outputs are tri-stated. This pin should be pulled down to Vss external to the chip during normal operation. |  |

## 1.5.5 VolantPCI Miscellaneous Signals

| Name      | Туре      | Description                                                                                                                                                                                                                                                                                                     |  |

|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -LED_EN   | 0         | <b>-LED Enable</b> is a signal dedicated to enabling an external light emitting diode for diagnostic purposes. (see 6.1.2, "LED Enable Register (LER)" on page 70).                                                                                                                                             |  |

| REFCLK    | Ι         | <b>Reference Clock</b> is an input clock signal. It is used to allow software to determine the PCI CLK speed (see 6.1.3, "Clock Timer Register (CTR)" on page 71). It is also the clock used to generate the various programmable output clocks (see 6.2.1, "PIO Configuration Registers (PIOCFG)" on page 72). |  |

| PIO0(3-0) | I/O       | <b>AIB Port 0 Programmable I/O(3-0)</b> provide 4 independent programmable I/O signals.                                                                                                                                                                                                                         |  |

| PIO0(7-4) | O<br>t.s. | AIB Port 0 Programmable I/O(7-4) provide 4 independent programmable output signals.                                                                                                                                                                                                                             |  |

| PIO1(3-0) | I/O       | <b>AIB Port 1 Programmable I/O(3-0)</b> provide 4 independent programmable I/O signals.                                                                                                                                                                                                                         |  |

| PIO1(7-4) | O<br>t.s. | AIB Port 1 Programmable I/O(7-4) provide 4 independent programmable output signals.                                                                                                                                                                                                                             |  |

| PIO2(3-0) | I/O       | AIB Port 2 Programmable I/O(3-0) provide 4 independent programmable I/O signals.                                                                                                                                                                                                                                |  |

| PIO2(7-4) | O<br>t.s. | AIB Port 2 Programmable I/O(7-4) provide 4 independent programmable output signals.                                                                                                                                                                                                                             |  |

| PIO3(3-0) | I/O       | <b>AIB Port 3 Programmable I/O(3-0)</b> provide 4 independent programmable I/O signals.                                                                                                                                                                                                                         |  |

| PIO3(7-4) | O<br>t.s. | AIB Port 3 Programmable I/O(7-4) provide 4 independent programmable output signals.                                                                                                                                                                                                                             |  |

| MMI       | I         | <b>Multi-Master In</b> is a daisy-chain input connected to another chips MMO signal.<br>If not using Multi-Master mode then it must be connected to its own MMO signal.                                                                                                                                         |  |

| ММО       | 0         | <b>Multi-Master Out</b> is a daisy-chain output connected to another chips MMI signal.<br>If not using Multi-Master mode then it must be connected to its own MMI signal.                                                                                                                                       |  |

| SED       | I/O       | <b>Serial Eprom Data</b> can be connected to the Data In (DI) and Data Out (DO) of a three-wire serial EPROM chip (e.g. Microchip 93C06). This pin has a weak internal pull-up. It should be pulled-up externally to Vdd by approx. $10k\Omega$ .                                                               |  |

| SECS      | 0         | <b>Serial Eprom Chip Select</b> can be connected to the Chip Select (CS) pin of a three-wire serial EPROM chip (e.g. Microchip 93C06).                                                                                                                                                                          |  |

| SECLK     | 0         | <b>Serial Eprom Clock</b> can be connected to the Clock (CLK) pin of a three-wire serial EPROM chip (e.g. Microchip 93C06).                                                                                                                                                                                     |  |

| Vss       |           | All Vss pins should be connected to a ground plane.                                                                                                                                                                                                                                                             |  |

| Vdd       |           | All Vdd pins should be connected to a 3.3V power plane.                                                                                                                                                                                                                                                         |  |

## 1.6 Vero Compatibility

VolantPCI is intended to be highly software compatible with the functions performed by the Vero chip on the four/eight-port JUNO AIB cards. It is **not** intended to be a drop in replacement for Vero with a PCI Bus replacing the CFE Local Bus. Some Vero configuration registers will not be fully compatible with VolantPCI and many features have been added. The following lists which register groups have programming considerations (refer to the individual register description sections for more detail):

### 1.6.1 Interrupts

The PCI bus defines a single interrupt pin versus the 8-bit vector defined for Vero. When an interrupt is pending, VolantPCI will activate its pin. Software should then read the IVR (3.4.2, "Interrupt Vector Register (IVR)" on page 49) to determine the vector for the interrupt and branch to the appropriate handler. The vectors read in the IVR are the same values used for Vero's vector.

The DISR (2.3.9, "DMA Interrupt Status Registers (DISR)" on page 33) has changed to handle the additional errors due to the PCI Bus. PERR# has been mapped to Exception, parity errors remains the same and master and target abort errors have been added.

When operating in interrupt vector mode, there will no longer be a defined range for each vector or conversion of out-of-range vectors to the highest vector. VolantPCI will ignore the vector FFh (which is returned from the DUSCC when no interrupt is pending).

A bit in the IVR is equivalent to the INTA# pin and indicates an interrupt is pending in VolantPCI.

The EOI will now operate as either a write or read command. (Previously it was only a write command.) This is being done because it is possible that PCI bridge chips could post the EOI write command which would not allow a deterministic time between the EOI and the interrupt clearing to the PCI Bus. The user can now use the read EOI (which cannot be posted) to have a deterministic timing.

### 1.6.2 AIB Bus

- The bus now only supports 8-bit devices (vs. 8, 16 and 32)

- The bus is demultiplexed (16 address bits, 8 data bits)

- The READY and DEN signals have been deleted

- The separate EOP signals have been combined to a single pin.

- Parity support has been removed.

### 1.6.3 DMA

- DMA CCR Register

- EOP no longer supported on Transmit channels (TC is supported)

- Asynchronous DMA no longer supported. All DMA activity is synchronized to DREQ

- Asynchronous EOP has been deleted.

- Port size is fixed at 8-bit.

- Added "write value read on first AIBOP masked by AIBOP2 data".

- AIB OPs on Transmit channels are no longer supported

- Chip can be configured to write DMA status at end of current CDB Status which includes byte count, OP data and termination status (TC, EOP, etc.)

- Added "flush FIFO" bit to 2.3.2, "DMA Channel Command Registers (DCCR)" on page 26.

- Fixed support of 64kB byte count.

- Added "quick start" and "do not chain if CPR=0" to allow simpler and faster chain control.

- Added 2.3.10, "Enhanced Status Pointer Register (ESP)" on page 34.

- Changed definition of 2.5.2, "DMA FIFO Residual Count registers (DFRC)" on page 39.

- DMA Queuing is no longer supported

### 1.6.4 Setup/Configuration

- 4.2.2, "DMA Acknowledge Pulse Width Registers (DAPW)" on page 56 (reduced to one for Tx, one for Rx) had some bits redefined or eliminated.

- Presence Detect Registers (deleted)

- 4.2.1, "Chip Select Definition registers (CSD0-3)" on page 53 changed.

- PCI Bus configuration is now required. For address compatibility, the registers and AIB address space may be programmed to the same address they occupied on ARTIC960 Adapter.

- LBCR deleted.

- 6.1.1, "Configuration Register (CFGR)" on page 69 added.

### 1.6.5 PIO's

A total of 32 programmable I/O pins have been added. Half of these are fully programmable for input/output, polarity and interrupt. The other half are output-only with programmable polarity (four of which can be programmed to output a divided version of REFCLK).

These are not program compatible with the FPGAs used on previous Vero-based daughter cards.

#### 1.6.6 Multi-Master Mode

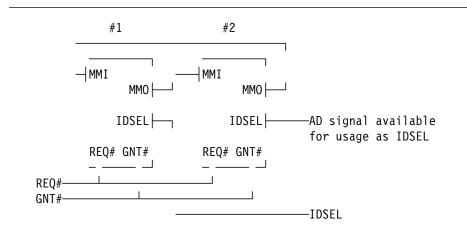

Multiple VolantPCI chips can be connected to a single PCI Bus request/grant signal pair without additional glue logic. See 5.3.2, "Multiple VolantPCI Chips on the PCI Bus" on page 60 for more details.

## 1.7 VolantPCI Register Address Map

The memory map of all registers addressable within the VolantPCI module is shown below. Detailed information is found in the indicated section. Each register is four byte aligned in the address space as noted.

Reserved bit locations in a register must always be written as '0' when programming a register. These bits are undefined. Users should not rely on reserve bits reading back as '0'.

### 1.7.1 Register Reset States

At the end of each register description section, the register's RESET conditions are shown. There are several different reset conditions. Some registers may have only one reset condition while others may have two or three. The following table describes the names and the function of each reset condition.

| Table 6. VolantPCI Reset Conditions |                                                                                                                                                                                                                                                                              |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset Condition                     | Description                                                                                                                                                                                                                                                                  |  |

| CHIP RESET                          | CHIP RESET will reset the entire chip. This reset is active<br>when the RST# signal is active. This condition overrides<br>all other pending conditions within the chip and automat-<br>ically forces all logic to its RESET state.                                          |  |

| DMA RESET                           | A DMA RESET resets DMA channel related registers and logic. This reset condition is activated by either a write to the GDCR (see 2.5.1, "AIB Bus Global DMA Command Register (GDCR)" on page 37) or the DCCR (see 2.3.2, "DMA Channel Command Registers (DCCR)" on page 26). |  |

| AIB RESET                           | There is a separate AIB RESET for the AIB Bus. This reset affects AIB Bus related registers and associated logic. The AIB RESET is activated by writing to the ACR (see 4.2.3, "AIB Bus Configuration Register (ACR)" on page 57).                                           |  |

|                                     | <b>Note:</b> Currently there are no AIB bus related registers that are affected by this reset. Only the AIB RESET pin is affected.                                                                                                                                           |  |

A 'U' in the "Reset Conditions" section means undefined, and an 'S' means the value stays the same as before the reset command.

## 1.7.2 DMA Registers

**Note:** An 'n' in an address represents the channel number (0-7).

| Table 7. VolantPCI DMA Register Set               |                   |                |

|---------------------------------------------------|-------------------|----------------|

| Section, Name                                     | Address<br>Offset | Access<br>Type |

| 2.3.6, AIB Address 1/2 Register (AIB_ADDR 1/2)    | +n000h            | r/w            |

| 2.3.7, AIB_OP1 DATA Register (AIB_OP1)            | +n004h            | r/w            |

| 2.3.8, AIB_OP2 DATA Register (AIB_OP2)            | +n008h            | r/w            |

| 2.3.3, Memory Pointer Register (MPR)              | +n00Ch            | r/w            |

| 2.3.4, Transfer Count Register (TCR)              | +n010h            | r/w            |

| 2.3.5, Chain Pointer Register (CPR)               | +n014h            | r/w            |

| 2.3.1, Channel Control Register (CCR)             | +n018h            | r/w            |

| 2.3.2, DMA Channel Command Registers (DCCR)       | +n020h            | r/w            |

| 2.3.9, DMA Interrupt Status Registers (DISR)      | +n028h            | ro             |

| 2.5.2, DMA FIFO Residual Count registers (DFRC)   | +n02Ch            | ro             |

| 2.3.10, Enhanced Status Pointer Register (ESP)    | +n038h            | r/w            |

| 2.5.3, DMA Buffer Data registers (DBD)            | +n100h-<br>+n10Ch | r/w            |

| 2.5.1, AIB Bus Global DMA Command Register (GDCR) | +8000h            | r/w            |

## 1.7.3 PCI Bus Related Registers

| Table 8. PCI Bus Registers                          |                  |                |

|-----------------------------------------------------|------------------|----------------|

| Section, Name                                       | Config<br>Offset | Access<br>Type |

| 5.4.1, Device/Vendor ID (DEVID)                     | +00h             | ro             |

| 5.4.2, Host Status/Command Register (HSCR)          | +04h             | r/w            |

| 5.4.3, Class Code/Revision ID Register (CCRID)      | +08h             | ro             |

| 5.4.4, Host Miscellaneous Functions Register (HMFR) | +0Ch             | r/w            |

| 5.4.5, Register Base Address Register (REGBAR)      | +10h             | r/w            |

| 5.4.6, AIB Base Address Register (AIBBAR)           | +14h             | r/w            |

| 5.4.7, Subsystem ID (SSID)                          | +2Ch             | ro             |

| 5.4.8, Latency/Grant/Interrupt Register (LGIR)      | +3Ch             | r/w            |

## 1.7.4 Interrupt Related Registers

| Table 9. VolantPCI Interrupt Related Registers       |                   |                |

|------------------------------------------------------|-------------------|----------------|

| Section, Name                                        | Address<br>Offset | Access<br>Type |

| 3.3.1, Interrupt Initialization register (IIR)       | +8010h            | r/w            |

| 3.3.2, Interrupt Mask register (IMR)                 | +8014h            | r/w            |

| 3.3.3, Interrupt Status register (ISR)               | +8018h            | r/w            |

| 3.3.4, AIB Error Interrupt Mask register (EIMR)      | +801Ch            | r/w            |

| 3.4.1, AIB INT0/1 End-of-Interrupt (EOI0/1) commands | +9000h<br>+A000h  | r/w            |

| 3.4.2, Interrupt Vector Register (IVR)               | +F000h            | r/w            |

## 1.7.5 AIB Bus Related Registers

| Table 10. VolantPCI AIB Bus Registers               |                   |                |  |  |  |

|-----------------------------------------------------|-------------------|----------------|--|--|--|

| Section, Name                                       | Address<br>Offset | Access<br>Type |  |  |  |

| 4.2.1, Chip Select Definition registers (CSD0-3)    | +B000h-<br>+B00Ch | r/w            |  |  |  |

| 4.2.2, DMA Acknowledge Pulse Width Registers (DAPW) | +B030h,<br>+B038h | r/w            |  |  |  |

| 4.2.3, AIB Bus Configuration Register (ACR)         | +C000h            | r/w            |  |  |  |

## 1.7.6 Miscellaneous Registers

| Table 11. VolantPCI Miscellaneous Registers |                   |                |

|---------------------------------------------|-------------------|----------------|

| Section, Name                               | Address<br>Offset | Access<br>Type |

| 6.1.2, LED Enable Register (LER)            | +D004h            | r/w            |

| 6.1.1, Configuration Register (CFGR)        | +D008h            | r/w            |

| 6.1.3, Clock Timer Register (CTR)           | +D00Ch            | ro             |

| 6.2.1, PIO Configuration Registers (PIOCFG) | +D100h-<br>+D137h | r/w            |

| 6.2.2, PIO Status Registers (PIOSTAT)       | +D200h-<br>+D237h | r/w            |

| 6.2.3, Serial EPROM Register (SER)          | +F100h            | r/w            |

## 2.0 VolantPCI DMA Controller

## 2.1 General

The functions of the DMA portion of the VolantPCI module are highlighted below.

- 8 independent DMA channels (any channel may operate as transmit or receive)

- split bus implementation (8-bit AIB Bus to 32-bit Local Bus)

- support of 16-bit Address, 8-bit Data AIB Bus devices

- 16 byte fifo per channel

- 16 byte burst capability on Local Bus for Data

- 3 Write / 7 Read List Chain Operation on Local Bus for Chaining

- 32-bit 4GB addressability on Local Bus

- 16-bit 64KB addressability on AIB Bus for AIB OP's

- separate DREQ and DACK signals for each DMA channel

- programmable DACK cycle time for transmit and receive DACK cycles

- 64KB byte count capability

- Descriptor Table for each channel

- Linked list chaining of buffers on all channels

- Chaining support for end-of-process and terminal count condition

- Automatic storage of residual transfer count and termination status on chain event

- Automatic storage of AIB OP reads on chain event

- Up to two programmable auto I/O operations on chain event (Receive DMA channels only)

- Six interrupt sources for each channel

Each channel is controlled by a Channel Descriptor Table (CDT) register set. The program normally writes a block of the CDT register values to memory resident structures called Channel Descriptor Blocks (CDB's). The program then writes the starting address of a CDB to the Chain Pointer Register (CPR) with bit 0 set to '1'. At this point, the CDB is automatically fetched from memory and loaded into the CDT. With the linked list chain option, once the DMA channel is started, the CDBs can be automatically fetched by the DMA channel's state machine. Alternatively, the CDT registers can be programmed directly.

Once enabled, a channel will service DMA requests from the AIB Bus until one of a number of programmable conditions is reached. If the DMA channel is programmed to stop on one of these conditions, the channel can be re-enabled with a write to the Channel Control Register (CCR). Any condition that can stop the channel can also interrupt the PCI Bus. Also, the channel has the ability to interrupt without stopping the channel. All of the options are programmable in the CCR and are described later.

Devices on the AIB bus assert two types of requests: Transmit (TR) and Receive (RR).

Once a Transmit channel is started, the DMA controller arbitrates for control of the Local Bus, and when granted control, bursts up to 16 bytes of data from memory into that channel's FIFO. The data is then transferred to the requesting device across the AIB Bus until the FIFO is empty. This allows data transfer to the AIB device to occur in the background of Local Bus activity.

For a receive DMA channel, the DMA controller will receive up to 16 bytes of data across the AIB Bus. It then arbitrates for control of the Local Bus. Once granted, the DMA controller bursts all data into memory. This, again, allows data transfer from the AIB device to occur in the background of Local Bus activity.

## 2.2 DMA FIFO

As mentioned above, data transfer from Local Bus to AIB Bus is not direct, but rather, is buffered in a set of fifos. There is a 16 byte deep fifo associated with each DMA channel that acts as an intermediate storage area for data. The fifos support high speed access so that all accesses to the Local Bus will move data into and out of the fifos instead of directly to the AIB Bus, which might support only slower devices. This allows all Local Bus DMA data transfer initiated by VolantPCI to be high speed bursted accesses.

The fifos are configured such that AIB Bus accesses and Local Bus accesses can occur simultaneously for different channels. A DMA channel can be performing a read or write on the AIB Bus, while at the same time, another channel is performing a read or write on the Local Bus.

## 2.3 Channel Descriptor Register Set

Table 12 on page 22 shows the organization of the channel descriptor table (CDT) registers for one of the DMA channels. This table is duplicated for each of the 8 DMA channels. Each register is fully addressable on the PCI Bus.

| Table 12. VolantPCI DMA Channel Descriptor Table Registers |                                  |            |  |  |

|------------------------------------------------------------|----------------------------------|------------|--|--|

| Register<br>Name                                           | Register Function                | Valid Bits |  |  |

| CCR                                                        | Channel Control Register         | 31-0       |  |  |

| CPR                                                        | Chain Pointer Register           | 31-2       |  |  |

| TCR                                                        | Transfer Count Register          | 15-0       |  |  |

| MPR                                                        | Memory Pointer Register          | 31-0       |  |  |

| AIB_OP2                                                    | AIB OP2 Data Register            | 7-0        |  |  |

| AIB_OP1                                                    | AIB OP1 Data Register            | 7-0        |  |  |

| AIB_ADDR2                                                  | AIB OP2 Address Register         | 31-16      |  |  |

| AIB_ADDR1                                                  | AIB OP1 Address Register         | 15-0       |  |  |

| ESP                                                        | Enhanced Status Pointer Register | 31-2       |  |  |

**Note:** The ESP is not part of a CDB and normally is never written by software. The exceptions would be: 1) when running in Enhanced Status Mode List Chaining and the first CDB is programmed directly, 2) diagnostics and other test code.

### 2.3.1 Channel Control Register (CCR)

#### 2.3.1.1 Description:

The CCR register controls the operational personality for a DMA channel.

#### 2.3.1.2 Register Addressing

| DMA Cha                         | nnel                       | Address Offset                                           |                                                                                                              |  |  |  |

|---------------------------------|----------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| 0<br>1<br>2<br>3<br>4<br>5<br>6 | +(<br>+(<br>+(<br>+(<br>+( | 01018h<br>02018h<br>03018h<br>04018h<br>05018h<br>05018h | (read/write)<br>(read/write)<br>(read/write)<br>(read/write)<br>(read/write)<br>(read/write)<br>(read/write) |  |  |  |

| 7                               | +(                         | 07018h                                                   | (read/write)                                                                                                 |  |  |  |

#### 2.3.1.3 Register Format

| 31         | 30                            |            |          |                               | 26       | 25       | 24                                       | 23       | 22   | 21<br>A] | 20                         | 19       | 18<br>A] | 17<br>17   | 16         |

|------------|-------------------------------|------------|----------|-------------------------------|----------|----------|------------------------------------------|----------|------|----------|----------------------------|----------|----------|------------|------------|

|            |                               | Rese       | erve     | ed                            |          | Rese     | erve                                     | Rese     | erve | wr       |                            | C        |          | atior      | n  <br>    |

| GEN<br>STA |                               | Rese       | erve     | ed                            |          | x        | x                                        | <br>X    | x    | WR<br>1  | WR<br>0                    | 0P<br>#2 | 0P<br>#1 | # 0<br>I/0 |            |

| st         | 14<br>annel<br>oppir<br>tions | ng         | int      | 11<br>Ianne<br>Cerru<br>otior | ıpt      | cł       | 8<br>nanne<br>nain <sup>.</sup><br>otior | ing      | 6    | 5<br>(   | 4<br>char<br>lefir<br>opti | nitio    | 2<br>on  | 1          | 0          |

| STP<br>2   | STP S                         | STP 1<br>0 | INT<br>2 | INT<br>1                      | INT<br>0 | LCH<br>2 | LCH<br>1                                 | LCH<br>0 | Rsv  | /d.      | EOP<br>DIR                 | Rsv      | /d.      | +T/<br>-R  | EN/<br>DIS |

#### 2.3.1.4 Bit Descriptions

- Bit 31. General purpose status bit. This bit can be used for any application dependent purpose. It has no function internal to the chip. It is updated by I/O writes, and during list chaining fetches.

- Bits 30-22. Reserved. Always write these bits to '0'.

- Bits 21-20. These two bits are encoded to indicate what data will be written to the AIB Bus on the second of two AIB OP's, if the first of the two AIB OP's is a read.

| WR1 | WR0 |                                                  |

|-----|-----|--------------------------------------------------|

|     |     |                                                  |

| 0   | 0   | Write the value of AIB_OP2 Data Register         |

| 0   | 1   | Write the value that was read on first OP        |

| 1   | 0   | Write the complement of value read on first OP   |

| 1   | 1   | Write the value that was read on first OP masked |

|     |     | by the value of AIB_OP2 Data Register            |

• Bit 19. AIB OP #2, read or write. This bit is coupled with bits 16 and 17. It defines the second I/O operation to the AIB Bus after a chain event to be a read or write. If the operation is a write, the data written is defined by bits 20 and 21 of the CCR. If the operation is a read, the data will be stored in memory.

- 0 = Read, 1 = Write

• Bit 18. AIB OP #1, read or write. This bit is coupled with bits 16 and 17. It defines the first I/O operation to the AIB Bus after a chain event to be a read or write. If the operation is a write, the data written is defined by bits of the AIB\_OP1 register. If the operation is a read, the data will be stored in memory.

- 0 = Read, 1 = Write

• Bits 17-16. Number of I/O operations to AIB Bus upon chain event. These two bits are encoded to provide the DMA controller with the ability to execute up to 2 discrete I/O operations to the AIB Bus following the recognition of a chain event. The address to which the first I/O operation occurs is defined by bits 0-15 in the AIB\_ADDR 1/2 register. The address to which the second I/O operation occurs is define by bits 16-31 in the AIB\_ADDR 1/2 register.

Note: AIB OPs are supported only on Receive DMA channels. Write these as '00' for transmit channels.

00 = No I/O operation upon chain event.

01 = One I/O operation upon chain event.

10 = Two I/O operations upon chain event.

11 = Reserved.

• Bit 15-13. Encoded DMA channel stopping options. Bit 15 is always '0'.

| STP1 | STP1 | STP0 | Stopping Option             |

|------|------|------|-----------------------------|

|      |      |      |                             |

| 0    | 0    | 0    | Do not stop                 |

| 0    | 0    | 1    | TC=0                        |

| 0    | 1    | 0    | EOP (Receive Channels Only) |

| 0    | 1    | 1    | TC=0 "or" EOP               |

| 1    | Х    | Х    | Reserved                    |

When a channel is stopped, the CCR enable/disable bit is reset. Also, a chaining condition takes precedence over a stopping condition if both occur at the same time since the chaining condition causes a new CCR enable/disable bit to be fetched from memory.

- **Note:** When the 'Do not stop' option is selected and the channel is programmed as a transmit channel, the TCR must be initialized with a value of multiple of 16 bytes.

- Bit 12-10. Encoded DMA interrupt options. Bit 12 is always '0'.

Error interrupts are not separately maskable in the CCR. To eliminate error related DMA interrupts, detection of the error inputs (PERR and Parity) should be disabled in the appropriate registers.

INT2 INT1 INT0 Interrupt Option ---- ---- ---------0 0 0 Normal Termination Interrupts disabled 0 0 1 TC=0 0 1 EOP (Receive Channels Only) 0 TC=0 "or" EOP (Receive Channels Only) 0 1 1 1 Х Х Reserved

• Bit 9-7. Encoded list chaining enabling options.

| LCH2 | LCH1 | LCH0 | Chaining Option                       |

|------|------|------|---------------------------------------|

|      |      |      |                                       |

| 0    | 0    | 0    | Disabled                              |

| 0    | 0    | 1    | TC=0                                  |

| 0    | 1    | 0    | EOP (Receive Channels Only)           |

| 0    | 1    | 1    | TC=0 "or" EOP (Receive Channels Only) |

| 1    | 0    | 0    | Reserved                              |

| 1    | 0    | 1    | Reserved                              |

| 1    | 1    | 0    | Reserved                              |

| 1    | 1    | 1    | NOP                                   |

The chaining NOP selection only functions when it is chained in. AIB OPS will not occur for a NOP.

VolantPCI will not chain if the CPR register for the channel points to 00000000h.

- Bit 6-5. Reserve. Always write this to 0.

- **Note:** These bits were used in the Vero chip. Bits '6-5' set the Port Size for the DMA transfer. VolantPCI has a fixed 8-bit port size for all DMA channels.

- Bit 4. This bit, when '0', enables the EOP(TC) as an output pin. This is the normal mode for Tx channels. When set to '1', the pin is an input. This mode should be used for Tx channels when the user does not want a TC indication to the external device. This mode ('1') **must** be used for all Rx channels (EOP detection can be disabled using other CCR bits).

- Bit 3-2. Reserve. Always write this to 0.

**Note:** These bits were used in the Vero chip. Bit '3' enabled the Asynchronous EOP option. Bit '2' enabled the Asynchronous DMA option. These Vero options are not supported in the VolantPCI chip.

• Bit 1. +Transmit/-Receive indicator. This bit indicates if the DMA channel is a Transmit Channel "1", or a Receive Channel "0". For receive channels, data transfer is **from AIB Bus** to Local Bus. For transmit channels, data transfer is from Local Bus to AIB Bus.

Previous Vero based ARTIC cards allocated the channels as follows:

TRANSMIT CHANNELS: 2,3,6,7 RECEIVE CHANNELS: 0,1,4,5

• Bit 0. +Enable/-disable channel.

- 0 = DMA Channel Disabled

- 1 = DMA Channel Enabled

This bit reflects the status of the DMA channel. When enabled, the DMA channel can be stopped by writing this bit to a '0', however, this operation is dangerous because the other CCR bits will also be written. The DMA channel should be stopped by writing to the DCCR (see 2.3.2, "DMA Channel Command Registers (DCCR)" on page 26).

This bit is updated during list chaining.

Note: This bit will not read back '0' unitl the DMA channel has actually stopped.

The dummy CDB along with bit 31 of the CCR used to determine the DMA channel's status (running, chaining, etc.) for Vero is no longer required to ensure that the channel is stopped.

#### 2.3.1.5 Reset Conditions

CHIP RESET:

U000 0000 00UU UUUU 0000 0000 0001 00U0

DMA RESET:

S000 0000 00SS SSSS 0SS0 SSSS S00S 00S0

### 2.3.2 DMA Channel Command Registers (DCCR)

#### 2.3.2.1 Description:

The DCCR supports three commands. One allows for the bit manipulation of the CCR enable/disable bit. This bit allows CCR bit 0 to be set/reset without affecting the other CCR bits. A second command allows internal logic to be reset to a known state if an error condition causes a channel to stop before completion. Also, a third command is available for receive DMA channels only. This command forces the receive fifos to be flushed to local bus memory. A separate command register exists to control each DMA channel.

The command to enable a channel should not be issued with the same write that releases the channel from a reset command.

#### 2.3.2.2 Register Addressing

| DMA Channel | Address | Offset       |

|-------------|---------|--------------|

| 0           | +00020h | (read/write) |

| 1           | +01020h | (read/write) |

| 2           | +02020h | (read/write) |

| 3           | +03020h | (read/write) |

| 4           | +04020h | (read/write) |

| 5           | +05020h | (read/write) |

| 6           | +06020h | (read/write) |

| 7           | +07020h | (read/write) |

#### 2.3.2.3 Register Format

| 31 |          | 3 | 2   | 1   | 0   |

|----|----------|---|-----|-----|-----|

|    | Reserved |   | FRF | RES | DIS |

#### 2.3.2.4 Bit Descriptions

- Bit 31-3. Reserved. Always write these bits to '0'.

- Bit 2. Flush Receive Fifo. (Receive Channels Only)

Setting this bit to a '1' forces the residual bytes held in the receive DMA channel's fifo to be flushed to local bus memory. When the bytes are flushed, the FRF bit will reset back to '0'. The FRF command is only valid for receive channels when the channel is stopped. Writes to this bit are blocked when the DIS bit = '1' (channel is running). Users should stop the channel by writing to the DIS bit and verify that the channel is stopped (DIS = '0') before flushing the fifo.

- Bit 1. Reset channel command. Setting this bit to '1' causes a channel to be reset as shown by the Reset Command for each register. The channel is held in the reset state until the bit is set back to '0'.

- -1 = Reset Active

- 0 = Reset Inactive

- Bit 0. Disable channel command. Bit 0 = 0 defines the command to disable the channel. Bit 0 = 1 defines the command to enable the channel. Bit 0 of the CCR, if read, will reflect an enable or disable command if it is issued through the DCCR.

- -1 = DMA Channel Enable

- 0 = DMA Channel Disable

- **Note:** When stopping the channel, a write to this bit causes the DMA channel to complete any pending operations and then stop. This bit should be read to verify that the channel is stopped since there may be a delay between the writing of this bit to stop the channel, and when the DMA channel actually stops.

#### 2.3.2.5 Reset Conditions

CHIP RESET:

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

#### 2.3.3 Memory Pointer Register (MPR)

#### 2.3.3.1 Description:

The MPR contains the 32-bit Local Bus address of the next data byte to be DMA'ed. There are no alignment restrictions on the address programmed into this register.

Note: This register must be written before the TCR is written when directly programming a DMA transfer.

#### 2.3.3.2 Register Addressing

| DI | MA Ch | annel | Address | Offset       |

|----|-------|-------|---------|--------------|

|    | 0     |       | +0000Ch | (read/write) |

|    | 1     |       | +0100Ch | (read/write) |

|    | 2     |       | +0200Ch | (read/write) |

|    | 3     |       | +0300Ch | (read/write) |

|    | 4     |       | +0400Ch | (read/write) |

|    | 5     |       | +0500Ch | (read/write) |

|    | 6     |       | +0600Ch | (read/write) |

|    | 7     |       | +0700Ch | (read/write) |

|    |       |       |         |              |

#### 2.3.3.3 Register Format

| 31 |                | 0 |

|----|----------------|---|

|    | Memory Pointer |   |

#### 2.3.3.4 Bit Descriptions

• Bits 31-0. PCI Bus Address.

#### 2.3.3.5 Reset Conditions

| CHIP RESET: | UUUU |

|-------------|------|------|------|------|------|------|------|------|

| DMA RESET:  | SSSS |

### 2.3.4 Transfer Count Register (TCR)

#### 2.3.4.1 Description:

Bits 0-15 contain the current DMA transfer count in bytes. Values from 0000h to FFFFh can be programmed. This allows DMA transfers of from '1' (0001h) to '64KB' (0000h) to be transferred. This register is automatically saved into memory when a chain event occurs. This is shown in Figure 2 on page 35.

The Terminal Count (TC) condition occurs when the Transfer Count decrements to zero.

#### 2.3.4.2 Register Addressing

Address Offset DMA Channel \_\_\_\_\_ 0 +00010h (read/write) +01010h (read/write) 1 2 +02010h (read/write) 3 +03010h (read/write) 4 +04010h (read/write) 5 +05010h (read/write) +06010h (read/write) 6 7 +07010h (read/write)

#### 2.3.4.3 Register Format

| 31       | 16 15 |               | 0 |

|----------|-------|---------------|---|

| Reserved | DM    | IA Byte Count |   |

#### 2.3.4.4 Bit Descriptions

• Bits 31-16. Reserved. Always write these bits to '0'.

- Bits 15-0. Transfer count in bytes (1 to 64K).

- **Note:** A zero value equals a count of 64k. For future compatibility it is suggested that the value of 00010000h be used for 64k transfers.

#### 2.3.4.5 Reset Conditions

| CHIP RESET: | 0000 | 0000 | 0000 | 0000 | UUUU | UUUU | UUUU | UUUU |

|-------------|------|------|------|------|------|------|------|------|

| DMA RESET:  | 0000 | 0000 | 0000 | 0000 | SSSS | SSSS | SSSS | SSSS |

**Note:** Vero compatible code may write these bit to a non-zero value. All new code should write these bits as '0'.

### 2.3.5 Chain Pointer Register (CPR)

#### 2.3.5.1 Description:

The CPR contains the 32-bit address pointer that points to the memory location where the DMA controller will fetch the CDB for the next buffer when a chain event occurs. The lower 2 bits of this register will always read '00' forcing the chain pointer to be 4 byte aligned. The following two conditions define a chaining event.

- 1. terminal count has been reached and list chaining for terminal count is enabled in the CCR,

- 2. an End-Of-Process condition has occurred and list chaining for end-of-process is enabled in the CCR.

When writing this register, if a '1' is written to bit 0 and the channel is stopped, the channel will start and immediately chain from the address written. This allows the DMA to be started with a single write. If the channel is running, the CPR will be replaced. **The CPR must only be written if the channel is stopped or this register currently contains 0000000h. Also, software should never start a chain to address 0 by writing 00000001h to this register.** See 2.4.2, "Linked List Chaining/Stopping" on page 36.

#### 2.3.5.2 Register Addressing

DMA Channel Address Offset

#### 2.3.5.3 Register Format

31

2

1

0

Chain Pointer

0

ST

#### 2.3.5.4 Bit Descriptions

- Bits 31-2. Chain Pointer Address

- Bit 1. Reserved. This bit always reads '0'.

- Bit 0. Chain and start. If when writing the CPR this bit is written as a '1' and the channel is stopped, the channel will immediately chain to the address written. If the channel is running this bit is ignored. This bit always reads '0'.

#### 2.3.5.5 Reset Conditions

| CHIP RESET: | UUUU | UU00 |

|-------------|------|------|------|------|------|------|------|------|

| DMA RESET:  | SSSS | SS00 |

### 2.3.6 AIB Address 1/2 Register (AIB\_ADDR 1/2)

#### 2.3.6.1 Description: