# **Am79C81A**

# **CMOS RAM Buffer Controller (RBC)**

#### DISTINCTIVE CHARACTERISTICS

- Total memory buffer management

- 16-bit address bus supports 64K words (32 bits wide) with the Am79C82A Data Path Controller (DPC)

- Programmable registers and pointers

- DMA arbitration between the Data Path Controller (DPC), Node Processor (NP), Memory full and empty notification and Host

- Supports transmit link list addressing

- 12.5-MHz byte clock

- TTL-Compatible I/O

- Single +5-V supply

- 145-lead pin grid array package

#### **GENERAL DESCRIPTION**

The Am79C81A RAM Buffer Controller (RBC), along with the Am79C82A Data Path Controller (DPC), manages Buffer Memory to implement a FIFO (first-in, first-out) data structure, simplifying the design of any high-

speed interface. This CMOS device has TTL-compatible input and output pins which provide a straightforward interface to other external devices. Diagnostic information is also accumulated and reported by the RBC.

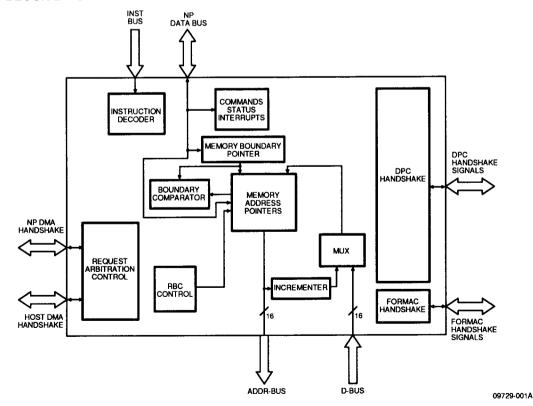

#### **BLOCK DIAGRAM**

Publication # 09729 Rev. C Amendment /0

Issue Date: February 1989

#### Note:

The word "frame" is used in the SUPERNET data sheets to describe three different groups of information.

1) One group is passed over the network media and has the following structure:

|   | T) One group is passed over the frether media and the |                    |                  |                        |                   |             |                         |                  |                 |

|---|-------------------------------------------------------|--------------------|------------------|------------------------|-------------------|-------------|-------------------------|------------------|-----------------|

| - | Frame<br>Preamble                                     | Start<br>Delimiter | Frame<br>Control | Destination<br>Address | Source<br>Address | Information | Frame Check<br>Sequence | End<br>Delimiter | Frame<br>Status |

The others are stored in buffer memory and structured as follows:

A) Transmit frame:

|            |         |             |         |             |             | l i     |

|------------|---------|-------------|---------|-------------|-------------|---------|

| 1          | Frame   | Destination | Source  |             | Frame Check |         |

| Descriptor | Control | Address     | Address | Information | Sequence    | Pointer |

B) Receive frame:

|     | Descriptor | Frame<br>Control | Destination<br>Address | Source<br>Address | Information | Frame Check<br>Sequence |

|-----|------------|------------------|------------------------|-------------------|-------------|-------------------------|

| , - |            |                  |                        |                   |             |                         |

# **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS           | 1      |

|---------------------------------------|--------|

| GENERAL DESCRIPTION                   | 1      |

| BLOCK DIAGRAM                         | 1      |

| CONNECTION DIAGRAM                    | 4      |

| PIN DESIGNATIONS                      | 5<br>7 |

| LOGIC SYMBOL                          | 7      |

| ORDERING INFORMATION                  | 8      |

| PIN DESCRIPTIONS                      | 9      |

| FUNCTIONAL DESCRIPTION                | 15     |

| Functional Overview                   | 15     |

| Overview of User-Accessible Resources | 16     |

| Programmable Resources                | 16     |

| Hardwired Resources                   | 17     |

| Buffer Memory Operation               | 17     |

| Memory Pointers                       | 18     |

| Receive FIFO                          | 18     |

| Transmit Chain Queue                  | 19     |

| RBC-NP Interaction                    | 21     |

| NP Hardwired DMA Requests             | 21     |

| RBC Programming                       | 24     |

| Instruction Set                       | 25     |

| Mode Register (MODE)                  | 30     |

| Static Status Register (STAT)         | 31     |

| Dynamic Status Register (DSTS)        | 32     |

| RBC-DPC Interaction                   | 33     |

| Received Data                         | 34     |

| Data To Be Transmitted                | 38     |

| RBC-Host Interaction                  | 40     |

| Host Requests                         | 40     |

| ABSOLUTE MAXIMUM RATINGS              | 41     |

| OPERATING RANGES                      | 41     |

| DC CHARACTERISTICS                    | 42     |

| CAPACITANCE                           | 42     |

| SWITCHING CHARACTERISTICS             | 43     |

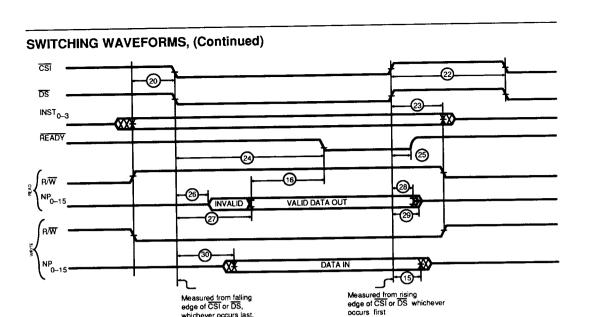

| SWITCHING WAVEFORMS                   | 46     |

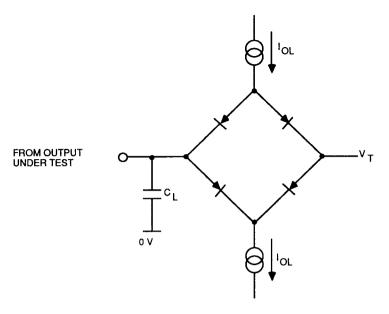

| SWITCHING TEST CIRCUITS               | 52     |

| SWITCHING TEST WAVEFORMS              | 52     |

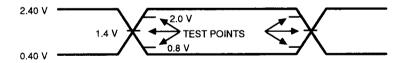

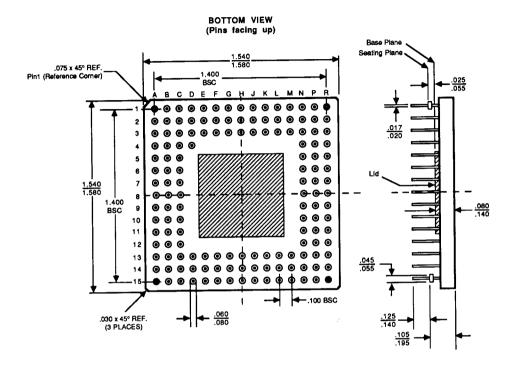

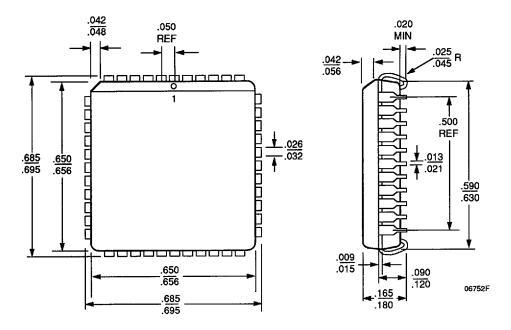

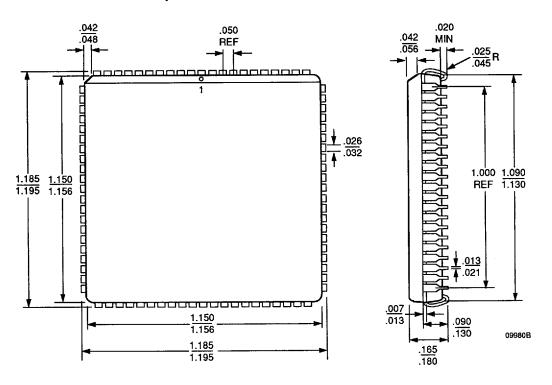

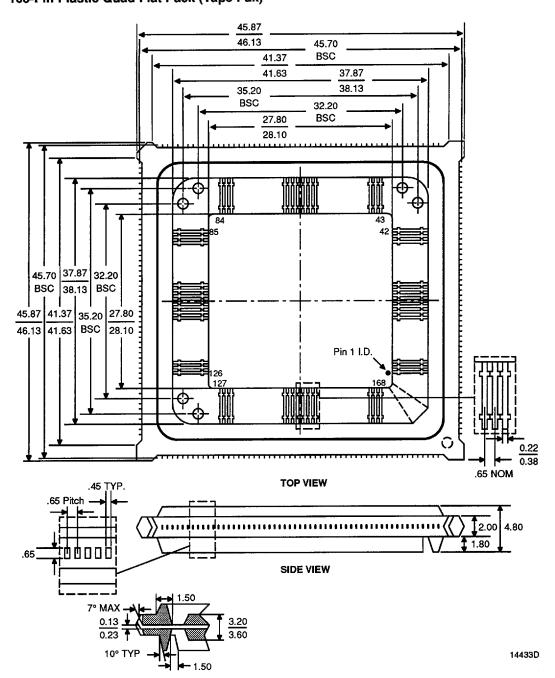

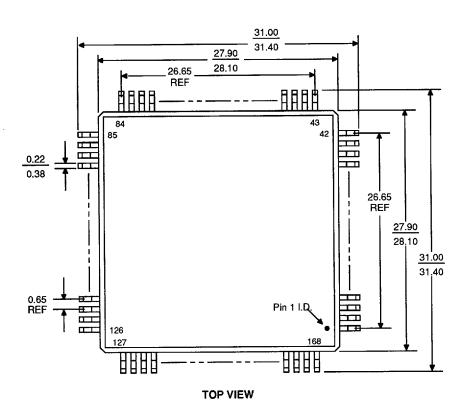

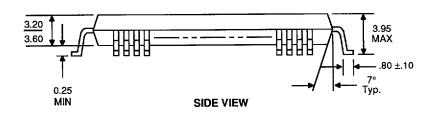

| PHYSICAL DIMENSIONS                   | 53     |

Am79C81A 2-3

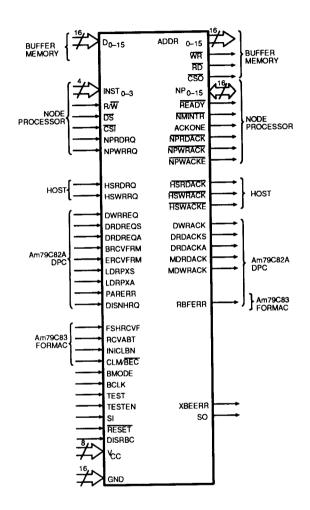

# CONNECTION DIAGRAM PGA Bottom View (Pins facing up)

|     | A       | В      | С     | D     | Ε    | F    | G    | н     | J      | к      | L     | м     | N       | Р       | R       |    |

|-----|---------|--------|-------|-------|------|------|------|-------|--------|--------|-------|-------|---------|---------|---------|----|

| , [ | NC NC   | vcc    | csi   | DS    | NP14 | NP11 | NP9  | NP8   | NP6    | NP3    | NP1   | NPO   | NMINTR  | NC      | CLM/BEC | 1  |

| 2   | NC      | INSTO  | BMODE | NC    | NP15 | NP12 | NP10 | NC    | NP7    | NP4    | NP2   | BCLK  | vcc     | NC      | NC      | 2  |

| 3   | INST3   | INST2  | INST1 | READY | GND  | NP13 | GND  | GND   | vcc    | NP5    | GND   | NC    | NC      | NC      | RCVABT  | 3  |

| 4   | DISRBC  | HSRDRQ | ₽∕W   | •     |      |      |      |       |        |        |       |       | GND     | FSHRCVF | NC      | 4  |

| 5   | HSRDACK | NPRDRQ | RESET |       |      |      |      |       |        |        |       |       | DWRREQ  | DRDREGS | NC      | 5  |

| 6   | NPRDACK | HSWRRQ | GND   |       |      |      |      |       |        |        |       |       | DRDREQA | BRCVFRM | ERCVFRM | 6  |

| 7   | vcc     | NPWRRQ | ASWRA | CK    |      |      |      |       |        |        |       |       | GND     | LDRPXS  | LDRPXA  | 7  |

| 8   | NPWRAC  | R GND  | GND   |       |      |      | (E   | Botto | om Vie | w)     |       |       | DISNHRQ | vcc     | NC      | 8  |

| 9   | NC      | NC     | TESTE | N     |      |      |      |       |        |        |       |       | GND     | DRDACKS | DRDACKA | 9  |

| 10  | NPWACK  | Ē TEST | GND   |       |      |      |      |       |        |        |       |       | DWRACK  | ACKONE  | PARERR  | 10 |

| 11  | NC      | HSWACK | Œ so  |       |      |      |      |       |        |        |       |       | GND     | MDRDACK | MDWRACK | 11 |

| 12  | Si      | NC     | vcc   |       |      |      |      |       |        |        |       |       | XBEERR  | RBFERR  | INICLBN | 12 |

| 13  | NC      | D15    | D12   | D9    | GND  | D4   | D1   | GND   | ADDR12 | ADDR9  | ADDR6 | ADDR4 | ADDR1   | WR      | RD      | 13 |

| 14  | NC      | D14    | D11   | D8    | D6   | D3   | NC   | GND   | ADDR13 | ADDR10 | ADDR7 | GND   | ADDR2   | vcc     | ĈŜO     | 14 |

| 15  | NC      | D13    | D10   | D7    | D5   | D2   | D0   | vcc   | ADDR14 | ADDR11 | ADDR8 | ADDR5 | ADDR3   | ADDR0   | ADDR15  | 15 |

|     |         | В      | С     | D     | E    | F    | G    | н     | J      | К      | L     | М     | N       | Р       | R       |    |

09729-002A

# PIN DESIGNATIONS

(Sorted by Pin Number)

| Pin        |                   | Pin  |                  | Pin  |                    | Pin  |                   |

|------------|-------------------|------|------------------|------|--------------------|------|-------------------|

| No.        | Pin Name          | No.  | Pin Name         | No.  | Pin Name           | No.  | Pin Name          |

|            | NC                | C-7  | HSWRACK          | H-13 | GND                | N-10 | DWRACK            |

| A-1<br>A-2 | NC<br>NC          | C-8  | GND              | H-14 | GND                | N-11 | GND               |

| A-2<br>A-3 | INST3             | C-9  | TESTEN           | H-15 | Vcc                | N-12 | XBEERR            |

| A-3<br>A-4 | DISRBC            | C-10 | GND              | J-1  | NP6                | N-13 | ADDR <sub>1</sub> |

| A-5        | HSRDACK           | C-11 | so               | J-2  | NP7                | N-14 | ADDR <sub>2</sub> |

| A-6        | NPRDACK           | C-12 | Vcc              | J-3  | Vcc                | N-15 | ADDR <sub>3</sub> |

| A-7        | Vcc               | C-13 | D12              | J-13 | ADDR12             | P-1  | NC                |

| A-8        | NPWRACK           | C-14 | D <sub>11</sub>  | J-14 | ADDR13             | P-2  | NC                |

| A-9        | NC                | C-15 | D10              | J-15 | ADDR <sub>14</sub> | P-3  | NC                |

| A-10       | NPWACKE           | D-1  | DS               | K-1  | NP3                | P-4  | FSHRCVF           |

| A-11       | NC                | D-2  | NC               | K-2  | NP4                | P-5  | DRDREQS           |

| A-12       | SI                | D-3  | READY            | K-3  | NPs                | P-6  | BRCVFRM           |

| A-13       | NC                | D-4  | <b>GUIDE PIN</b> | K-13 | ADDR <sub>9</sub>  | P-7  | LDRPXS            |

| A-14       | NC                | D-13 | D <sub>9</sub>   | K-14 | ADDR <sub>10</sub> | P-8  | Vcc               |

| A-15       | NC                | D-14 | D8               | K-15 | ADDR <sub>11</sub> | P-9  | DRDACKS           |

| B-1        | Vcc               | D-15 | <b>D</b> 7       | L-1  | NP <sub>1</sub>    | P-10 | ACKONE            |

| B-2        | INST <sub>0</sub> | E-1  | NP <sub>14</sub> | L-2  | NP <sub>2</sub>    | P-11 | MDRDACK           |

| B-3        | INST2             | E-2  | NP15             | L-3  | GND                | P-12 | RBFERR            |

| B-4        | HSRDRQ            | E-3  | GND              | L-13 | ADDR 6             | P-13 | WR                |

| B-5        | NPRDRQ            | E-13 | GND              | L-14 | ADDR 7             | P-14 | Vcc               |

| B-6        | HSWRRQ            | E-14 | D 6              | L-15 | ADDR 8             | P-15 | ADDR₀             |

| B-7        | NPWRRQ            | E-15 | D 5              | M-1  | NP <sub>0</sub>    | R-1  | CLM/BEC           |

| B-8        | GND               | F-1  | NP11             | M-2  | BCLK               | R-2  | NC                |

| B-9        | NC                | F-2  | NP <sub>12</sub> | M-3  | NC                 | R-3  | RCVABT            |

| B-10       | TEST              | F-3  | NP13             | M-13 | ADDR 4             | R-4  | NC                |

| B-11       | <b>HSWACKE</b>    | F-13 | D <sub>4</sub>   | M-14 | GND                | R-5  | NC                |

| B-12       | NC                | F-14 | Dз               | M-15 | ADDR 5             | R-6  | ERCVFRM           |

| B-13       | D15               | F-15 | D <sub>2</sub>   | N-1  | NMINTR             | R-7  | LDRPXA            |

| B-14       | D14               | G-1  | NP9              | N-2  | Vcc                | R-8  | NC                |

| B-15       | D13               | G-2  | NP10             | N-3  | NC                 | R-9  | DRDACKA           |

| C-1        | CSI               | G-3  | GND              | N-4  | GND                | R-10 | PARERR            |

| C-2        | BMODE             | G-13 | D <sub>1</sub>   | N-5  | DWRREQ             | R-11 | MDWRACK           |

| C-3        | INST <sub>1</sub> | G-14 | NC               | N-6  | DRDREQA            | R-12 | INICLBN           |

| C-4        | R/W               | G-15 | Do               | N-7  | GND                | R-13 | RD                |

| C-5        | RESET             | H-1  | NP8              | N-8  | DISNHRQ            | R-14 | CSO               |

| C-6        | GND               | H-2  | NC               | N-9  | GND                | R-15 | ADDR15            |

|            |                   | H-3  | GND              |      |                    |      |                   |

# PIN DESIGNATIONS (Sorted by Pin Name)

| Pin                      |                   | Pin          |                  | Pin  |                   | Pin  |          |

|--------------------------|-------------------|--------------|------------------|------|-------------------|------|----------|

| No.                      | Pin Name          | No.          | Pin Name         | No.  | Pin Name          | No.  | Pin Name |

|                          |                   | D 45         | D13              | B-2  | INST <sub>0</sub> | C-5  | RESET    |

| P-10                     | ACKONE            | B-15         | D13              | C-3  | INST <sub>1</sub> | A-12 | SI       |

| P-15                     | ADDR <sub>0</sub> | B-14<br>B-13 | D14<br>D15       | B-3  | INST2             | C-11 | SO       |

| N-13                     | ADDR1             | N-8          | DISNHRQ          | A-3  | INST3             | B-10 | TEST     |

| N-14                     | ADDR2             | N-0<br>A-4   | DISRBC           | R-7  | LDRPXA            | C-9  | TESTEN   |

| N-15                     | ADDR3             | R-9          | DRDACKA          | P-7  | LDRPXS            | A-7  | Vcc      |

| M-13                     | ADDR4<br>ADDR5    | P-9          | DRDACKS          | P-11 | MDRDACK           | B-1  | Vcc      |

| M-15                     |                   | N-6          | DRDREQA          | R-11 | MDWRACK           | C-12 | Vcc      |

| L-13                     | ADDR6<br>ADDR7    | P-5          | DRDREQS          | N-1  | NMINTR            | H-15 | Vcc      |

| L-14                     | ADDR/             | D-1          | DS               | M-1  | NPo               | J-3  | Vcc      |

| L-15<br>K-13             | ADDR <sub>9</sub> | N-10         | DWRACK           | L-1  | NP <sub>1</sub>   | N-2  | Vcc      |

| K-13<br>K-14             | ADDR10            | N-5          | DWRREQ           | L-2  | NP <sub>2</sub>   | P-14 | Vcc      |

| K-14<br>K-15             | ADDR11            | R-6          | ERCVFRM          | K-1  | NP <sub>3</sub>   | P-8  | Vcc      |

| J-13                     | ADDR12            | P-4          | FSHRCVF          | K-2  | NP4               | P-13 | WR       |

| J-13<br>J-14             | ADDR12            | B-8          | GND              | K-3  | NP5               | N-12 | XBEERR   |

| J-1 <del>4</del><br>J-15 | ADDR14            | C-10         | GND              | J-1  | NP6               | A-1  | NC       |

| R-15                     | ADDR15            | C-6          | GND              | J-2  | NP7               | A-11 | NC       |

| M-2                      | BCLK              | C-8          | GND              | H-1  | NPs               | A-13 | NC       |

| C-2                      | BMODE             | E-13         | GND              | G-1  | NPs               | A-14 | NC       |

| P-6                      | BRCVFRM           | E-3          | GND              | G-2  | NP10              | A-15 | NC       |

| R-1                      | CLM/BEC           | G-3          | GND              | F-1  | NP11              | A-2  | NC       |

| C-1                      | CSI               | H-13         | GND              | F-2  | NP <sub>12</sub>  | A-9  | NC       |

| R-14                     | <del>cso</del>    | H-14         | GND              | F-3  | NP <sub>13</sub>  | B-12 | NC       |

| G-15                     | D <sub>0</sub>    | H-3          | GND              | E-1  | NP14              | B-9  | NC       |

| G-13                     | D <sub>1</sub>    | L-3          | GND              | E-2  | NP <sub>15</sub>  | D-2  | NC       |

| F-15                     | D <sub>2</sub>    | M-14         | GND              | B-5  | NPRDRQ            | G-14 | NC       |

| F-14                     | D <sub>3</sub>    | N-11         | GND              | B-7  | NPWRRQ            | H-2  | NC       |

| F-13                     | D4                | N-4          | GND              | A-6  | NPRDACK           | M-3  | NC       |

| E-15                     | D <sub>5</sub>    | N-7          | GND              | A-10 | NPWACKE           | N-3  | NC       |

| E-14                     | D <sub>6</sub>    | N-9          | GND              | A-8  | NPWRACK           | P-1  | NC       |

| D-15                     | D7                | D-4          | <b>GUIDE PIN</b> | R-10 | PARERR            | P-2  | NC       |

| D-14                     | Ds                | A-5          | HSRDACK          | C-4  | R/W               | P-3  | NC       |

| D-13                     | D9                | B-4          | HSRDRQ           | P-12 | RBFERR            | R-2  | NC       |

| C-15                     | D10               | B-6          | HSWRRQ           | R-3  | RCVABT            | R-4  | NC       |

| C-14                     | D <sub>11</sub>   | B-11         | HSWACKE          | R-13 | RD                | R-5  | NC       |

| C-13                     | D12               | C-7          | HSWRACK          | D-3  | READY             | R-8  | NC       |

|                          |                   | R-12         | INICLBN          |      |                   |      |          |

Am79C81A

09729-003A

Am79C81A

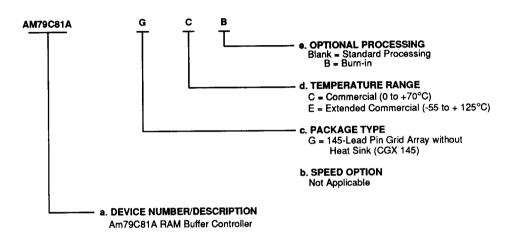

#### ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Combinations |                     |  |  |  |  |  |  |  |

|--------------------|---------------------|--|--|--|--|--|--|--|

| AM79C81A           | GC, GCB, GE,<br>GEB |  |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTIONS

# **Buffer Memory Interface**

All output pins which interface to the Buffer Memory can be forced into the high-impedance state by bringing the DISRBC signal HIGH.

# ADDR<sub>0-15</sub> Address Bus (Output; Three State)

The Address bus transmits the addresses which access the Buffer Memory. One of the six possible address pointers are selected for output on this bus; the address selected depends on the result of the request arbitration logic. Each memory transfer lasts for two BCLK cycles, and the addresses are valid for two cycles. When no memory transfer is taking place, the value on these lines is all bits HIGH (FFFF Hex).

## **CSO**

# Chip Select Output (Output; Three State, Active LOW)

When  $\overline{\text{CSO}}$  is LOW, a memory transfer takes place. In cases where a "buffer full" error occurs, the  $\overline{\text{CSO}}$  signal becomes LOW, as in normal transfers, but no actual writing of memory occurs because the  $\overline{\text{WR}}$  signal stays HIGH. For each memory access,  $\overline{\text{CSO}}$  is LOW for two clock periods.

# D<sub>0</sub>-15 Data Bus (Inputs)

This bus is used to read pointers into the RBC from frames stored in buffer memory. The purpose of the pointers is to support the chain transmit scheme. This data is loaded into the RBC when LDRPXS (A) is HIGH.

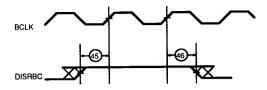

#### DISRBC

# Disable RBC (Input; Active HIGH)

DISRBC is used to force the Buffer Memory interface signals (ADDR-bus,  $\overline{CSO}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ) into the high-impedance state for initialization testing purposes only. It is not designed for use during normal FDDI operation; its misuse may cause serious network errors. Before DISRBC goes HIGH, every memory access should be complete, and no requests should be pending. The Node Processor (NP) can still load and read RBC internal pointers and registers while DISRBC is active. DISRBC is synchronous to BCLK and can stay HIGH as long as necessary.

# RD

# Read Signal (Output; Three State, Active LOW)

When  $\overline{RD}$  and  $\overline{CSO}$  are LOW, data is read from the Buffer Memory. For each memory access,  $\overline{RD}$  is LOW for 1.5 clock periods. Since the read operation is not destructive, the first attempt to read the memory when the receive or transmit FIFOs are empty is not prevented (as with the  $\overline{WR}$  signal).

\*SUPERNET is a trademark of Advanced Micro Devices, Inc.

# WR

# Write Signal (Output; Three State, Active LOW)

When WR and CSO are LOW, data is written into the Buffer Memory, either from the DPC or from external logic on the D-bus. If the RBC attempts to service a write request while the receive or transmit FIFOs (configured in Buffer Memory by the RBC) are full, the WR signal will not switch LOW, which prevents any overwriting of data. WR is asserted for one clock period.

# Node Processor (NP) Interface

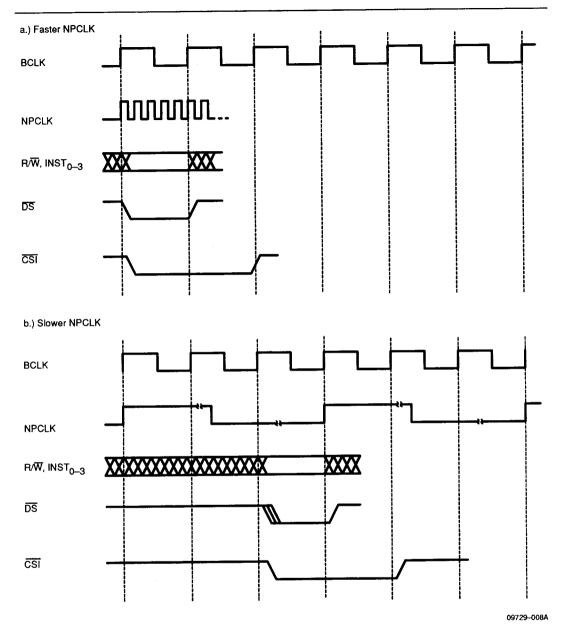

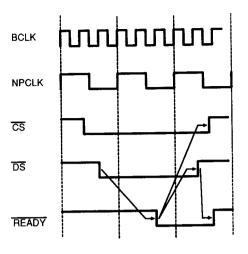

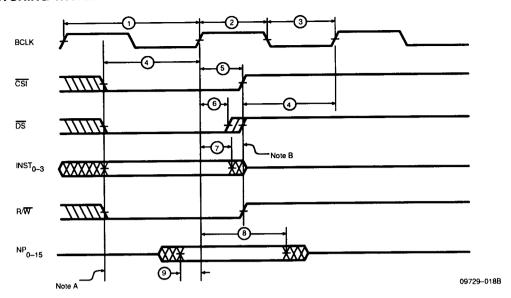

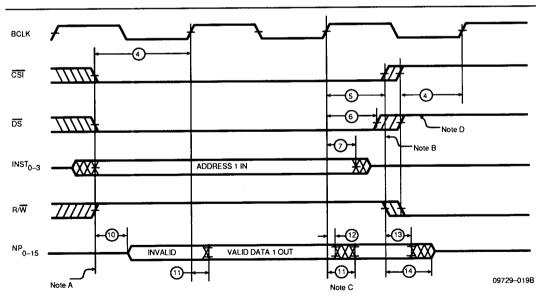

The NP may run synchronous to BCLK or may be clocked at a different frequency. In the synchronous mode (BMODE pin is HIGH), the RBC expects to see signals from the NP active for an integral number of BCLK cycles. In the asynchronous mode (BMODE is LOW), the READY line is used as a handshake signal with the NP. The INST<sub>0-3</sub> lines (R/W,  $\overline{DS}$ , and  $\overline{CSI}$ ) should all be active until the RBC drives the READY line LOW.

#### **BMODE**

#### **Bus Mode (Input)**

The BMODE pin should be tied HIGH when the NP operates synchronously with the SUPERNET\* chip-set. In asynchronous operation, BMODE must be tied LOW. BMODE only affects the handshake on the  $\overline{\rm DS}$ ,  $\overline{\rm CSI}$ , and READY lines.

## CSI

#### Chip Select Input (Input; Active LOW)

The  $\overline{CSI}$  pin indicates whether the NP has selected the RBC to execute an instruction. Internal execution of instructions is permitted only if  $\overline{CSI}$  and  $\overline{DS}$  are both LOW (these two signals are "ANDed" internally), and the instruction belongs to the RBC. When  $\overline{CSI}$  is HIGH, the INST<sub>0-3</sub> lines are ignored and the NP-bus is set to the high-impedance state.

#### $\overline{\mathsf{DS}}$

#### Data Strobe (Input; Active LOW)

DS is used for defining the presence of data on the NPbus when the NP is asynchronous to the BCLK (BMODE is LOW). In this case, the DS behaves much like the data strobes on slave devices connected to standard microprocessors. When R/W and CSI are LOW, a write operation is in progress from the NP to the RBC on the NP-bus; DS should go LOW whenever the data to be written is valid. DS should stay LOW (and the data on the NP-bus should stay valid) until the RBC takes the READY line LOW. In the case of a read operation, when R/W is HIGH and CSI is LOW, the NP forces DS LOW whenever it is ready to accept the read data. Subsequently, the RBC provides valid data and also asserts READY LOW. The NP can take DS HIGH any time after the RBC drives READY LOW. Until DS is brought HIGH, the RBC continues to provide valid data on the NP-bus. When the NP is synchronous to the BCLK, DS should be LOW for only one clock cycle per instruction.

#### INST<sub>0-3</sub>

#### Instruction Lines (Inputs)

These four instruction lines are typically connected to the NP address bus. Along with the R/W pin, they provide instructions to the RBC. Some are executed by the RBC while others are used in conjunction with the NP0-31 lines to read or load various registers internal to the RBC. These instructions are valid whenever  $\overline{\rm DS}$  and  $\overline{\rm CSI}$  are both active. When the NP runs on a clock synchronous to BCLK (as indicated by the BMODE pin being HIGH), the INST lines, as well as  $\overline{\rm DS}$  and  $\overline{\rm CSI}$ , should be active for an integral number of clock cycles. When the NP runs asynchronous to the BCLK (as indicated by the BMODE pin being LOW), the INST0-3 lines, as well as  $\overline{\rm DS}$  and  $\overline{\rm CSI}$ , should be active until READY becomes active (LOW).

#### **NMINTR**

# Non-Maskable Interrupt (Output; Open-Drain, Active LOW)

NMINTR is asserted when an error occurs during the RBC operation. This signal is used to interrupt the NP, and will stay LOW until the NP recognizes the interrupt by reading the status register.

#### NP0-15

#### Node Processor Bus (Input/Output; Three State)

The NP-bus carries the data for initializing, reading, or writing the various registers and pointers in the RBC. This bus can be used by the NP for reading or writing independent of the activities of the RBC. The NP-bus is an output whenever a read instruction is provided to the RBC; i.e., when R/W is HIGH and both  $\overline{CSI}$  and  $\overline{DS}$  are LOW. The NP-bus is an input when a write instruction is given to the RBC (R/W,  $\overline{CSI}$ , and  $\overline{DS}$  are LOW). When either  $\overline{CSI}$  or  $\overline{DS}$  become HIGH, the NP-bus is in the high-impedance state.

#### NPRDACK

#### NP Read Acknowledge (Output; Active LOW)

The NPRDACK signal indicates that an NP DMA request (initiated using the NPRDRQ pin) is being serviced. The NP can use NPRDACK as a signal to latch the memory data into an external register when it becomes available during the latter part of the transfer. For each request, NPRDACK is LOW for the entire two-cycle memory transfer.

#### **NPRDRQ**

#### NP Read Request (Input; Active HIGH)

NPRDRQ is a DMA request from the NP to the RBC. This signal selects the memory address register pointer as the source of the address with which to access the Buffer Memory. When the RBC services this request it asserts NPRDACK. This operation constitutes a complete handshake. The NPRDRQ request can be either a pulse or a level signal. If it is a pulse, it should be wide enough for one BCLK transition to occur (and meet the setup times), but small enough so that two BCLK transitions do not occur. For each such pulse request, one NPRDACK is generated, lasting two BCLKs. Subsequent pulses for

more requests should be generated only after the NPRDACK is generated by the RBC. If the NPRDRQ signal is level, it switches HIGH and stays at the HIGH level. The RBC constantly services this request (after arbitrating) and indicates this activity using NPRDACK. If NPRDRQ is switched LOW at any time in the window of NPRDACK, one more service is generated.

#### **NPWACKE**

# NP Write Acknowledge Enable (Output; Active LOW)

NPWACKE has the same function as NPWRACK, except that it is driven LOW only for the last half of the first clock cycle and the entire second clock cycle in a two-cycle memory transfer. The NPWACKE signal can be used by external logic to enable the memory data bus.

#### NPWRACK

#### NP Write Acknowledge (Output; Active LOW)

The NPWRACK signal indicates that an NP DMA request (initiated using the NPWRRQ pin) is being serviced. The NP can use NPWRACK as a signal to enable data onto the Buffer Memory data bus D<sub>0-31</sub>. For each request, NPWRACK is LOW for the entire two-cycle memory transfer.

#### **NPWRRQ**

#### NP Write Request (input; Active HIGH)

The NPWRRQ is a DMA request from the NP to the RBC. NPWRRQ selects the memory address register pointer as the source of the address with which to access the Buffer Memory. When the RBC services this request, it asserts NPWRACK for two BCLK cycles.

# READY

## Read Line (Output; Open Drain, Active LOW)

READY is a handshake signal when the RBC is in asynchronous mode. When the BMODE pin is HIGH, READY is also HIGH and cannot be used. When BMODE is LOW, the NP runs asynchronous to the BCLK, and READY indicates whether an instruction has been acted upon. In the case of a write instruction, READY goes LOW after the data is clocked into the RBC. In the case of a read instruction, READY goes LOW after the RBC supplies valid data on the NP-bus. Typically, the RBC takes between three and four BCLK cycles to assert READY after the NP asserts DS. READY stays LOW as long as DS and CSI stay LOW.

#### RESET

#### Reset (Input; Active LOW)

RESET is a hardware reset which initializes the internal state machines in the RBC and places the command and status registers in a pre-defined state. This signal can be asserted asynchronously at any point in the RBC operation, but should stay LOW for at least a period of four BCLK cycles. RESET can be forced HIGH asynchronously at any time after that period. Typically, the RESET input signal is connected to a power-on-reset circuit and also to a reset switch. A hardware reset is a

necessary first step which ensures that the RBC is in a known state prior to any operations taking place on the NP-bus. Subsequent resets to the RBC can be software-driven using the reset instruction provided in the instruction set.

#### R/W

#### Read/Write (Input)

When R/ $\overline{W}$  is LOW, data is written into one of the RBC's registers or an instruction is executed. When R/ $\overline{W}$  is HIGH, data is read from an RBC register onto the NP-bus. R/ $\overline{W}$  should be controlled in the same manner that INST<sub>0-3</sub> are.

#### Miscellaneous

#### **BCLK**

#### Byte Clock (Input)

BCLK is the main clock which runs the RBC. All transactions between the RBC, DPC, FORMAC, and ETX are synchronous with this clock. Transactions between these chips and the Node Processor are also synchronous with this clock when BMODE is HIGH. The skew of BCLK when it is distributed to the RBC, DPC, and FORMAC should be as small as possible.

#### SI

## Shift Scan Input (input)

This pin is used for factory testing. During normal operation SI must be left unconnected.

#### SO

#### Shift Scan Output (Output)

This pin is used for factory testing. During normal operation SO must be left unconnected.

#### TEST

#### Test (Input; Active HIGH)

When HIGH, the TEST pin forces the RBC into the test mode, in which various internal points are monitored on the SO pins. This logic may be used for incoming testing; the TEST pin should be tied to ground for normal operation.

#### **TESTEN**

#### Test Enable (Input; Active HIGH)

This pin is used for factory testing. For normal operation, TESTEN should be tied to ground.

## Host Processor Interface

## **HSRDACK**

#### Host Read Acknowledge (Output; Active LOW)

The HSRDACK signal indicates that a Host DMA request (initiated using the HSRDRQ pin) is being serv-

iced. HSRDACK is not generated if a receive "buffer empty" error is detected and the RBC is not in the page mode (MPAGE = 0). For each Host read request, HSRDACK is asserted for two clock cycles.

#### **HSRDRQ**

## Host Read Request (Input; Active HIGH)

The HSRDRQ is a DMA request from the Host to the RBC. The RBC selects the read pointer (RPR), which contains the beginning address of the receive FIFO, to be placed onto the 16-bit address bus. When the RBC services this request, it asserts HSRDACK. The operation of the HSRDRQ and HSRDACK pair is exactly the same as that of the NPRDRQ and NPRDACK pair.

#### **HSWRRQ**

## Host Write Request (Input; Active HIGH)

The HSWRRQ is a DMA request from the Host to the RBC. The RBC selects the write pointer (WPX), which contains the beginning address of the transmit FIFO in Buffer Memory, to be placed onto the 16-bit address bus. When the RBC services this request, it asserts HSWRACK. The operation of the HSWRRQ and HSWRACK pair is exactly the same as that of the NPWRRQ and NPWRACK pair.

#### **HSWACKE**

# Host Write Acknowledge Enable (Output; Active LOW)

HSWACKE has the same function as HSWRACK, and its timing is the same as NPWACKE. The HSWACKE signal is used by external logic to enable the memory data bus.

#### **HSWRACK**

# Host Write Acknowledge (Output; Active LOW)

The HSWRACK signal indicates that a Host DMA request (initiated using the HSWRRQ pin) is being serviced. HSWRACK is not generated if a transmit "buffer full" error is detected and the RBC is not in the page mode (MPAGE = 0). For each Host write request, HSWRACK is LOW for two clock cycles.

# Data Path Controller (DPC) Interface

#### **ACKONE**

#### Acknowledge One (Output; Active HIGH)

ACKONE indicates the completion of the first BCLK cycle of a two-cycle memory transfer for reads or writes. ACKONE is generated for all transfers, whether they involve the DPC, the NP, or the Host. In cases where the Buffer Memory becomes full, the actual transfer may not take place because the  $\overline{\text{WR}}$  signal is not active. ACKONE still switches HIGH to indicate this attempted transfer.

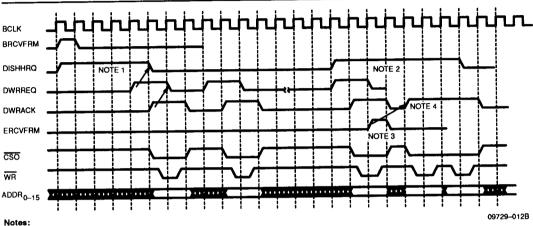

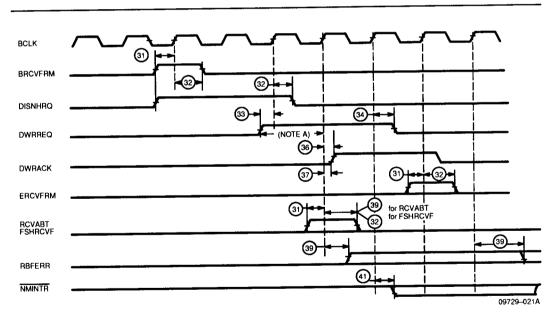

#### BRCVFRM

# Beginning of Received Frame (Input; Active HIGH)

Originating at the DPC, this signal indicates to the RBC that the following DWRREQ refers to the first long word of a received frame. Then, depending on the state of the MSLNSTM bit programmed in the mode register, the RBC will decide whether to skip the first location for the frame status. BRCVFRM forces the RBC into the receive state, and is asserted as soon as the DPC begins receiving a frame. BRCVFRM is synchronous with the BCLK and lasts for one clock cycle.

#### DISNHRQ

#### Disable NP and Host Request (Input; Active HIGH)

DISNHRQ prevents the RBC from servicing the pending NP and Host read or write requests. When this signal is active, only the DPC can access the Buffer Memory through the RBC, thus guaranteeing the DPC access to the total memory bandwidth. Even with DISNHRQ active, however, the NP can still communicate with the RBC using the instruction lines. If DISNHRQ becomes HIGH when the RBC is in the middle of an NP or Host service, the present service is completed and then further NP and Host requests are frozen. These requests remain pending and are serviced when DISNHRQ is released. DISNHRQ is synchronous to BCLK and lasts as long as the DPC wants to keep the RBC function for itself.

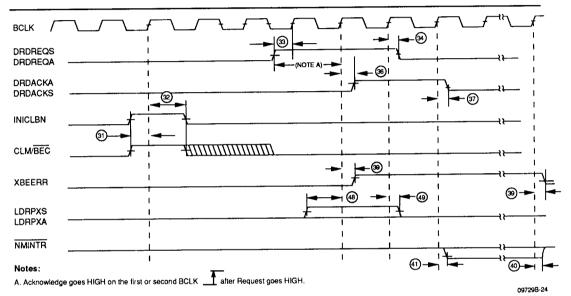

#### **DRDACKA**

# DPC Read Acknowledge for A-Frame (Output; Active HIGH)

Similar to DRDACKS, DRDACKA pairs with DRDREQA to transmit one long word of an A-frame from the transmit Buffer Memory. This signal is synchronous to BCLK and lasts for two BCLK cycles for each request.

#### **DRDACKS**

# DPC Read Acknowledge for S-Frame (Output; Active HIGH)

DRDACKS is a handshake signal from the RBC which advises the DPC that its DRDREQS is being serviced. Simultaneous with the output of this signal, the address bus becomes stable and CSO and RD are asserted. The latter operation enables the DPC to read one long word from the transmit queue in Buffer Memory. DRDACKS is synchronous with BCLK and lasts for two clock cycles. Together, DRDACKS and DRDREQS constitute a complete handshake between the RBC and the DPC for reading one long word of data from memory.

#### DRDREQA

#### DPC Read Request for A-Frame (Input; Active HIGH)

When the DPC is transmitting an A-frame from the asynchronous transmit queue in Buffer Memory, DRDREQA is used in place of DRDREQS. The RBC signifies that this request has been serviced by asserting DRDACKA. As with a synchronous frame, the DPC will not assert DRDREQA simultaneously with DRDREQS or DWRREQ.

#### DRDREQS

# DPC Read Request for S-Frame (Input; Active HIGH)

When the DPC needs to read a long word (for an S-frame) from the synchronous transmit queue in Buffer Memory, it sends a DRDREQS to the RBC. DRDREQS is the second-highest priority request (DWRREQ is the highest). DRDREQS is synchronous to BCLK, and lasts until the RBC services it, which the RBC signifies by asserting DRDACKS. The DPC will not assert DWRREQ or DRDREQA at the same time as DRDREQS.

#### **DWRACK**

# DPC Write Acknowledge (Output; Active HIGH)

The DWRACK signal indicates that the DWRREQ sent to the RBC is being serviced. Simultaneous with the output of this signal, the address bus becomes stable and CSO and WR are asserted. The latter operation allows the DPC to write data from its D-bus into the receive Buffer Memory. For each DWRREQ, one DWRACK is generated and lasts for two clock cycles. The operation of DWRREQ and DWRACK forms a complete handshake between the DPC and RBC, and effectively writes one long word of data into the Buffer Memory. During normal operation, the RBC expects to have its DWRACK asserted within (at most) two clock cycles after it receives DWRREQ, since this request always gets highest priority. If the DPC does not receive DWRACK two clock cycles after DWRREQ, it may generate a receive abort, assuming that something is wrong with the RBC, or that its FIFO buffer is too full to receive more data from the FORMAC.

#### **DWRREQ**

#### **DPC Write Request (Input; Active HIGH)**

DWRREQ is a signal from the DPC to the RBC which requests a memory write cycle for the receiving frame. While in the receive mode, the DPC asserts DWRREQ when it wants to write a long word to the Buffer Memory. DWRREQ is the highest priority request and will be serviced ahead of any other pending requests. DWRREQ lasts until the RBC services its request. The DPC ensures that only one of DWRREQ, DRDREQS, and DRDREQA are asserted at a time.

#### **ERCVFRM**

#### End of Received Frame (Input; Active HIGH)

ERCVFRM is asserted when the DPC detects the end of a received frame. The RBC uses this signal to write the frame status and length (if it is in the write mode, MSLNSTM = 1). ERCVFRM forces the RBC out of the receive mode, and should be asserted after the DPC sees a DWRACK for the last word of the received frame. ERCVFRM is synchronous with BCLK and lasts one clock cycle. Together with BRCVFRM, it marks the boundaries for one complete frame reception.

#### LDRPXA

#### Load RPX for A-Frame (Input; Active HIGH)

This signal is analogous to LDRPXS to support the chain transmit scheme for A-frames. It pairs with DRDREQA and DRDACKA, and is used to load the RPXA pointer.

LDRPXA is valid only when the RBC is programmed in the chain transmit mode (MENCHN = 1).

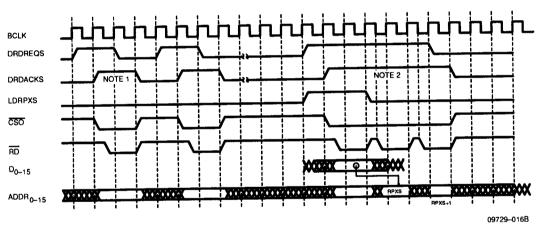

#### **LDRPXS**

## Load RPX for S-Frame (Input; Active HIGH)

LDRPXS is a signal from the DPC which instructs the RBC to load data from the 16-bit D-bus to its RPXS pointer. This signal is given to support the chain transmit scheme of the DPC. LDRPXS is synchronous with the system clock, and is forced HIGH and inactive in the same manner as DRDREQS. When servicing DRDREQS with LDRPXS, the RBC enables its address bus (as always with DRDREQS) to load the lower 16 bits of the Buffer Memory data bus Do-15 into the RPXS pointer. In this way, the RBC can perform a jump to the next frame location in memory (linked list scheme). LDRPXS is valid only when the RBC is programmed in the chain transmit mode (MENCHN = 1).

#### **MDRDACK**

# MDR Read Acknowledge (Output; Active HIGH)

The MDRDACK signal indicates that an NP read request instruction (INPRDNI, INPRDWI) is being serviced. For each read request instruction, MDRDACK is driven HIGH for the entire two-cycle memory transfer.

#### **MDWRACK**

## MDR Write Acknowledge (Output; Active HIGH)

The MDWRACK signal indicates that an NP write request instruction (INPWRWI) is being serviced. For each write request instruction, MDWRACK is driven HIGH for the entire two-cycle memory transfer.

#### **PARERR**

#### Parity Error (Input; Active HIGH)

The PARERR signal, originating from the DPC parity check logic, indicates that a parity error has been detected in the present read or write transaction on the Dbus. If the parity error occurs during NP or Host service, the RBC generates an interrupt to the NP and waits until the NP clears the error before further servicing requests of that type. If the parity error occurs during a DPC read or write service, the RBC also sets the appropriate status bit and interrupts the NP, but continues to service subsequent DPC requests. PARERR is asserted immediately after the ACK signal of the request becomes inactive. It is synchronous with BCLK and lasts for one clock cycle.

#### RBFERR

## Receive Buffer Full Error (Output; Active HIGH)

The RBC asserts RBFERR to notify the DPC and the FORMAC that the receive queue in Buffer Memory is full. The receive queue is defined as "full" when the receive read pointer (RPR) and the receive write pointer (WPR) have met and the DPC still attempts further DWRREQs. Depending on the status of the page mode bit programmed in the RBC, the assertion of RBFERR can have two different results:

- 1) If MPAGE = 1 (RBC is in page mode) and a receive buffer full error is detected, the RBC asserts RBFERR for only two clock cycles and continues to operate as if no error had occurred.

- 2) If MPAGE = 0 and a receive buffer full error is detected then:

- a) the RBC generates an interrupt to the NP;

- b) the RBC asserts RBFERR until the error is cleared by the NP:

- c) the RBC will not generate a DWRACK while RBFERR is asserted, preventing an overwrite of old data by new data. The WPR is locked at the point where the buffer full error occurred; and

- d) RBFERR forces the RBC out of the receive mode.

# Fiber Optic Ring Media Access Controller (FORMAC) Interface

#### CLM/BEC

#### Claim or Beacon (Input)

When INICLBN is HIGH, the state of CLM/BEC determines which mode (claim or beacon) will be initialized. The INICLBN and CLM/BEC "truth table" follows:

| INICLBN | CLM/BEC | Meaning               |

|---------|---------|-----------------------|

| 0       | 0       | Claim/beacon inactive |

| Ō       | 1       | Claim/beacon inactive |

| 1       | 0       | Transmit beacon frame |

| 1       | 1       | Transmit claim frame  |

To initialize claim mode, the FORMAC forces CLM/BEC HIGH simultaneously with INICLBN. CLM/BEC must stay HIGH for one BCLK cycle while INICLBN is HIGH. To initialize the beacon mode, CLM/BEC must be LOW when INICLBN becomes HIGH.

#### **FSHRCVF**

#### Flush Received Frame (Input; Active HIGH)

The FSHRCVF instructs the RBC to "flush" a received frame; i.e., to purge the frame from Buffer Memory. If FSHRCVF becomes HIGH while the RBC is servicing a DWRREQ, the RBC will stop servicing that request and will reset the WPR pointer back to the beginning of the frame. Generally, a flush is the result of an unmatched address frame in the FORMAC address detection logic. FSHRCVF identifies the end of a flushed frame and forces the RBC out of the receive state. The FORMAC does not allow FSHRCVF to be HIGH when the RBC is not in the receive state. FSHRCVF is synchronous with BCLK and is HIGH for one clock cycle.

#### INICLBN

#### Initialize Claim/Beacon (Input; Active HIGH)

The FORMAC uses this pin to force the RBC into the claim or beacon mode. (For more information about claim/beacon, please refer to the Am79C83 FORMAC data sheet.) Together with the CLM/BEC pin, INICLBN instructs the RBC to load the claim or beacon address to

the synchronous transmit pointer (RPXS). A claim or beacon frame is subsequently read from this location and transferred to the FORMAC. INICLBN is HIGH for one clock cycle, and is used only when the RBC is in the chain transmit mode (i.e., when the programmed command bit MENCHN is HIGH).

#### **RCVABT**

#### Receive Abort (Input; Active HIGH)

The RCVABT signal provides a means for the FORMAC to notify the RBC that the received frame has been aborted due to an error. RCVABT is synchronous to BCLK, and is HIGH for one clock cycle. If RCVABT is HIGH for one or more cycles while a DWRREQ is being serviced, the next pending request is not serviced. Depending on the state of the MSLNSTM command bit, the RBC will set its WPR pointer back to the beginning of the frame for the aborted status, or it will wait for the next incoming frame. For an aborted frame, RCVABT denotes the end of the frame and forces the RBC out of the receive state.

# Interface with External Logic

#### **XBEERR**

#### Transmit Buffer Empty Error (Output; Active HiGH)

The RBC generates XBEERR to notify the outside logic that the transmit buffer has become empty. XBEERR is used only when the RBC is programmed in the transmit FIFO mode (MENCHN = 0), since in the non-FIFO mode (MENCHN = 1), the RBC never checks for full or empty errors. Like RBFERR, XBEERR behaves differently de-

pending on the status of the page mode bit programmed in the RBC:

- 1) If MPAGE = 1 (RBC is in page mode) and a transmit buffer empty error is detected, then the RBC asserts XBEERR for only two clock cycles and continues to operate as if nothing happened.

- 2) If MPAGE = 0 and a transmit buffer empty error is detected, then:

- a) the RBC generates an interrupt to the NP;

- b) the RBC asserts XBEERR until the error is cleared by the NP; and

- c) the RBC will not generate a DRDACKS while XBEERR is asserted, preventing a reading of erroneous data. The RPXS is locked at the point where the transmit buffer empty error occurs.

Since the DPC supports the non-FIFO transmit buffer only, XBEERR is used only when the RBC is used as a stand-alone chip.

## **Power Supply**

#### **GND**

#### Ground (Inputs)

There are sixteen GND pins. They must all be connected to the power return.

#### VCC

#### Power (Inputs)

There are eight VCC pins. They must all be connected to a  $+5-V \pm 5\%$  supply.

# FUNCTIONAL DESCRIPTION Functional Overview

The RBC generates addresses within FIFOs in Buffer Memory for the frames being received and for the frames to be transmitted. It also controls the DMA transfer of data to and from the Buffer Memory. The received frames are taken from the FORMAC, converted from 8-bit to 32-bit words by the DPC, and stored in a simple receive FIFO in the Buffer Memory. The NP checks the frame to ensure that it is good; then, the data is transferred from the FIFO to the VO buffer of the Host or NP.

The frames to be transmitted are transferred from the Host or NP I/O to one of two chain FIFOs in Buffer Memory for FDDI transmission. One chain FIFO is used for Sframes (referred to as synchronous frames in the standard) and one chain FIFO is used for A-frames (referred

to as asynchronous frames in the standard). The data is transferred from the Buffer Memory to the FORMAC when transmission is permitted.

Note: The words "synchronous" and "asynchronous" as used in the FDDI standards refer to classes of transmission service and have nothing to do with transmitted signals or the synchronization of these signals. All frames are converted to electrical signals for transmission using the same format. There is only one kind of transmission over the media; therefore, S-frames and A-frames are terms used in this manual to avoid confusion.

The memory can also have byte parity (each byte has a parity bit) as an option.

The functions of the RBC can be summarized as follows:

# 1) NP interaction with the RBC:

- a) Through the instruction lines and the NP-bus, the NP can:

- 1) Initialize the ten user-visible pointers of the RBC;

- 2) Program the mode register of the RBC to fit its particular need;

- 3) Read and clear the status reported by the RBC; and

- Generate software requests to read or write to the memory.

The above functions are totally independent from those below. However, if the NP tries to initialize a pointer which is being used by the RBC, the RBC will have priority.

b) Through NP read or write request pins, the NP can have access to the Buffer Memory (either the receive or transmit buffer). One common pointer (MAR) is reserved for this function.

# 2) Host interaction with the RBC:

- a) The Host can write to the transmit buffer via a write request to the RBC. The WPX pointer is used for the Host write.

- b) The Host can read the received frames from the receive buffer via a read request to the RBC. The RPR pointer is reserved for the Host read.

## 3) DPC interaction with the RBC:

- a) The DPC stores the received frames in the receive buffer by sending write requests to the RBC. The RBC uses the WPR pointer to serve this request.

- b) The DPC transmits frames from the transmit buffer by sending read requests to the RBC. The RPXA pointer is used for asynchronous frames and the RPXS pointer is used for synchronous frames.

All memory access requests sent to the RBC are serviced on a first-come, first-served basis. However, if the NP, the Host, and the DPC attempt to access the memory at the same time, then the RBC has the responsibility of arbitrating them according to a predefined priority:

- 1) First priority = DPC requests

- 2) Second priority = NP requests

- 3) Third priority = Host requests

# **Overview of User-Accessible Resources**

#### **Programmable Resources**

#### Instruction Set

The NP can issue software commands to the RBC through the  $R/\overline{W}$ , INST<sub>0-3</sub>, and NP<sub>0-31</sub> lines. INST<sub>0-3</sub> are normally driven by the address lines of the NP.

#### Mode Register (MODE)

The mode register is 8 bits wide, and can be written to and read by the NP. This register allows the NP to program the RBC to fit certain system requirements. This register determines the modes of operation of the RBC. On reset, the register is initialized so that all bits are inactive. The NP can then load the required values into the register using the ILDMOD instruction. Register contents remain unchanged until the NP loads in a new value or the chip is reset. Contents of this register and the dynamic status register can be read with the IRDMDDS instruction.

#### Status Registers (STAT and DSTS)

The two status registers can be read by the NP on the NP-bus. These registers store the status bits generated by the RBC. These bits, when HIGH, will generate an interrupt to the NP. The two status registers differ in the manner in which they are cleared; each type is explained below:

Static (autocleared) Status Register (8 Bits): this

register contains RBC status bits which are automatically cleared when the NP reads them unless an external

event causes a bit to be set at the same time. In such a

case, the new setting overrides the autoclear so that no status is lost. This register is read with the IRDSTAT instruction.

2) Dynamic Status Register (8 Bits): this register contains fatal error status bits which disable the operation related to the error. The NP can read this register, but the read does not autoclear it. The clearing of one or more status bits in this register can be accomplished only through a specific dynamic-status-clear instruction (using the ICLDSTS instruction accompanied by appropriate bits on the NP<sub>8-15</sub> lines) given by the NP. This register and the mode register can be read by using the IRDMDDS instruction.

#### Memory Pointers

The main purpose of the RBC is to make the random-access Buffer Memory function as a set of first-in, first-out (FIFO) buffers: one for received data and one or two for transmitted data.

The RBC stores incoming frames in the receive buffer in sequential order, automatically wrapping around to the start of the buffer when it reaches the end of the buffer.

The RBC buffers transmit data in one of two ways, depending on the state of the MENCHN bit in the mode register. When the RBC is used with the Am79C82A DPC in FDDI applications, the MENCHN bit is normally set to logic "1" (chain mode) so that the RBC manages transmit data as two linked lists, one for S-frames and one for A-frames. When the RBC is used as a stand-alone FIFO controller, the MENCHN bit is set to logic "0" (FIFO mode) so that the RBC manages transmit data as a single sequential FIFO just like the receive buffer.

To manage these buffers, the RBC has ten pointer registers that can be read or written by the NP using the RBC instruction set. Each of these registers contain a 16-bit address of a memory location (word) in external RAM. In FDDI applications using the DPC, the external memory is organized as 32-bit-wide words (plus an optional 4 bits for parity).

The ten pointer registers in the RBC visible to the user are:

1) SAR: Start address for receive FIFO

2) EAR: End address for receive FIFO

3) ACP: Address to claim pointer (in chain mode) or start address for transmit FIFO

(in FIFO mode)

4) RPCB: Read pointer for claim or beacon transmit frames (in chain mode) or end

address for transmit FIFO (in FIFO mode)

5) WPR: Write pointer for receive frames

6) RPR: Read pointer for receive frames

7) WPX: Write pointer for transmit frames

7) WPX: Write pointer for transmit frames

8) RPXA: Read pointer for asynchronous transmit frames

9) RPXS: Read pointer for synchronous transmit frames except for claim or beacon

transmit frames (in chain mode)

10) MAR: Memory address register for NP access

The FIFO buffers can be located anywhere in the 64K memory address space. For the receive buffer, the SAR and EAR define the limits of the space allocated to the FIFO, while the RPR and WPR point to the beginning and end of the valid data in the FIFO. Since the read and write pointer registers increment automatically after they are used, the start address (SAR) should be less than the end address (EAR).

In the FIFO mode (MENCHN = 0), the transmit FIFO is defined in the same way using ACP and RPCB to mark the limits of the space allocated to the FIFO, and RPXS and WPX to mark the beginning and end of the valid data in the FIFO. The RPXA pointer can be used as a random-access pointer that is automatically incremented after each access, but does not automatically wrap around from RPCB to ACP or from EAR to SAR.

The RBC can also be compatible with larger memory requiring an address bus wider than 16 bits. In this case, the NP should program the RBC in the page mode and the 16-bit address bus from the RBC will be connected to the least significant bits of the memory address.

#### **Hardwired Resources**

Using the BMODE pin, the RBC can interface with either a synchronous or asynchronous Node Processor. When BMODE is tied HIGH, the RBC can interface with a synchronous NP. In this case, the  $\overline{CSI}$  pin indicates the presence of data on the NP-bus; the  $\overline{DS}$  pin indicates the presence of an instruction from the NP instruction line. When BMODE is tied LOW, the NP clock is asynchronous with the RBC clock. In this case, the  $\overline{DS}$  and  $\overline{CSI}$  pins can be connected together, and become LOW when the NP issues an instruction to the RBC, and the READY line signifies that the RBC received the message from the NP.

# **Buffer Memory Operation**

The Buffer Memory is a key part of an FDDI node. It has to accept data at a high rate and transfer it immediately to make room for more data.

The NP assigns the Buffer Memory addresses for each frame of data to be transmitted. The NP also assigns the Buffer Memory space to be used for the receive FIFO

and initializes the RBC pointer registers. For received data, the RBC furnishes the Buffer Memory addresses for reads and writes and increments the pointer after each service, wrapping around when the end of the FIFO is reached. For frames to be transmitted, the RBC increments the pointer after each long word in the frame is accessed. At the end of the frame, the RBC uses the pointer value in the frame to point to the address of the next frame. The RBC also arbitrates DMA requests for DMA data transfer to and from the Host, NP, and DPC. This section discusses the Buffer Memory addressing. The DMA requests from the Host, NP, and DPC to the RBC are discussed in the sections that follow.

To manage the addressing, the RBC has ten registers which are used as memory pointers. For the data being received from the media, a simple FIFO is created within the Buffer Memory by the NP. The RBC manages this FIFO after the NP has created and initialized it. Frames are stored sequentially in contiguous locations in this simple FIFO.

Because FDDI applications provide two categories of data to be transmitted (A-frames and S-frames), two separate chain queues are created by the NP in the Buffer Memory. One chain queue is used for storing A-frames and the other queue FIFO is used for storing A-frames.

Chain queues differ from simple RBC-managed FIFOs in the Buffer Memory addressing scheme used. Each frame in a chain queue contains a pointer to the address of the next frame. These frame addresses are generally assigned by the NP. The words within a frame are stored in contiguous locations. In a chain queue the frames need not be assigned to contiguous locations in Buffer Memory.

In a simple FIFO, the RBC increments a pointer register to assign the addresses sequentially to the frames. When the end of the FIFO (EAR) is reached, the RBC places the SAR value into the pointer, thus wrapping around.

After a description of the memory pointers, this section discusses the operation of simple FIFOs. This is followed by a discussion of the chain queues used for transmission.

#### **Memory Pointers**

The RBC contains ten pointer registers used as address pointers. The RBC uses four of these pointers to make a FIFO within the Buffer Memory to handle the data received from the media through the DPC. For storing frames to be transmitted, three of the remaining pointers are used to read from and write to a pair of chain queues. Each frame in a chain queue has a pointer that points to the location of the next frame. These pointers within the frames have been assigned Buffer Memory addresses by the NP.

The ten visible address pointers in the RBC are 16 bits wide and can be written into or read from by the NP using the NP-bus and instruction lines. Each pointer contains an address of a memory location of the external Buffer Memory RAM. The memory is organized as 64K long words, 32 bits wide (36 bits if parity is used). Each address accesses this complete long word of 32 bits (36 bits with parity).

The ten pointers in the RBC visible to the user are:

1) SAR: Start address for receive FIFO

2) EAR: End address for receive FIFO

3) ACP: Address of claim pointer (ACP + 1: Address of beacon pointer)

4) RPCB: Read pointer for claim or beacon frames

5) WPR: Write pointer for receive frames

6) RPR: Read pointer for receive frames

7) WPX: Write pointer for transmit S-frames or

A-frames

8) RPXA: Read pointer for transmit A-frames 9) RPXS: Read pointer for transmit S-frames

except claim or beacon frames

(after INICLBN HIGH)

10) MAR: Memory address register for random

access

Most of these pointers are self-explanatory. The others are described below:

RPCB automatically stores the current contents of ACP when INICLBN is HIGH. RPCB is the pointer used by the DPC (with the DRDREQS pin) to read the S-frame chain queue, so that claim or beacon frames will be transmitted.)

WPR is the pointer used by DPC with pin DWRREQ for writing to the receive FIFO.

RPR is the pointer used by the Host with pin HSRDRQ for reading from the receive FIFO (the FIFO for frames received from the media through DPC).

WPX is the pointer used by the Host (using the HSWRRQ pin) to write S-frames and A-frames into the respective chain FIFOs in the Buffer Memory for transmission by the media. For each frame to be written by the Host, the WPX is set by the NP to point to either the A-frame chain queue or the S-frame chain queue. Therefore, the Host must communicate to the NP the category of each frame.

RPXS is the pointer used by the DPC (used with the DRDREQS pin) to read the S-frame chain queue for frames to transmit (except claim or beacon frames).

RPXA is the pointer used by DPC (used with the DRDREQA pin) to read the A-frame chain queue for frames to transmit.

The NP controls the MAR, a random-access pointer that can point to any location in the entire memory, irrespective of whether it is within a FIFO or not. The NP can typically use this for housekeeping functions in the memory.

The RBC automatically increments the WPX, WPR, RPR, RPXA, and RPXS registers after each use except when the limits are reached in a simple FIFO, or when the DPC requests the RBC to load in a new value from the memory when operating in the chain FIFO mode. These registers cannot be simultaneously loaded or written by the NP and the RBC. If this occurs, then the RBC has priority, and the status bit SNLSLD is set, creating a non-maskable interrupt (NMINTR) pin is LOW).

#### Receive FIFO

For received data, the NP creates a simple FIFO in Buffer Memory using pointers SAR, EAR, WPR, and RPR. The RBC operates the FIFO, advancing the pointers and wrapping around when the upper limit of the FIFO is reached (Figure 1 shows the FIFO). SAR and EAR define the limits of the receive FIFO. Since these pointers address a 32-bit-long word, the FIFO can begin or end only on a long-word boundary. Since the pointers in the RBC are designed to increment, the start address (SAR) should be smaller in magnitude than the ending address (EAR). With these requirements in mind, this FIFO can be configured anywhere in Buffer Memory within the 64K long-word address space.

# SAR FRAME A (TO HOST I/O OR NP I/O) WPR (FROM DPC) EAR

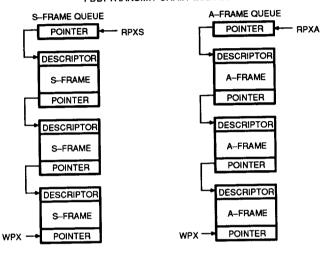

#### FDDI TRANSMIT CHAIN QUEUES

09729-004A

Figure 1. FiFOs and Queues in Buffer Memory

To initialize the receive FIFO, the WPR and RPR pointers are set to the same value anywhere within the receive FIFO. This indicates an empty condition of the FIFO. The NP does this initialization using the load instructions for the corresponding pointers. Once initialized, the RBC gets control of the memory buffer, and the transfer of frames between the media and the Host can begin. The frames are transferred to and from the Buffer Memory in long-word increments (32-bit words).

When data is being received from the media, the DPC generates the write request to the RBC for each word to be stored in the Buffer Memory. The WPR pointer is used in this operation. After writing a long word, the RBC increments WPR to point to the next location to be written in the receive FIFO (or sets it to SAR if EAR has been reached). Upon a read request from the Host, the RBC uses RPR similarly to read a received frame from the receive FIFO and transfer it to the Host.

The RBC also detects the full and empty conditions of the receive FIFO which may occur during the operation. In either condition, the pointer which caused the error to be

generated is locked up and not moved forward until the NP recognizes the error and resets the appropriate bit in the dynamic status register, using the ICLDSTS instruction accompanied by a logic "1" on the appropriate bit on the NP-bus (see Table 4).

## **Transmit Chain Queues**

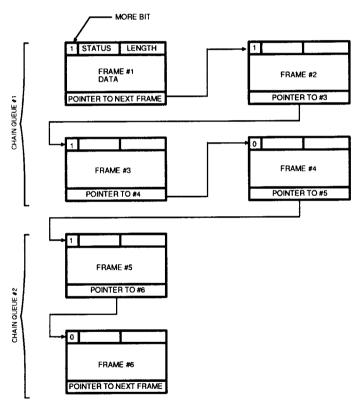

FDDI allows the transmission of two categories of frames: S-frames and A-frames. These transmit frames are stored in two separate chain queues in the Buffer Memory, one for each category of frames. Each chain queue is accessible on a first-in, first-out basis. The NP creates and maintains the two chains (see Figure 1). Each frame in each chain ends with a pointer to the start of the next frame in that chain.

The transmit chain queues do not require initialization of boundary pointers since the address space for each S-frame and A-frame in the Buffer Memory is assigned by the NP. The RPXS and RPXA pointers are initialized by the NP to point to the first frame in each of the two chain queues. Each time that either the NP or Host wants to add frames to either the A-frame chain queue or the S-

frame chain queue, the NP must first set the WPX pointer in the RBC to point to the address assigned to the next frame in the correct chain queue.

For FDDI operation, the NP must initialize the RBC to run in chain queue mode by setting the mode bit MENCHN = 1. Chain queue mode applies to transmit only. Receive is always in simple FIFO mode.

Each time data is placed into the S-frame or A-frame chain queue (in FDDI operation), the NP must issue an IENXMTS or IENXMTA to the DPC to enable the DPC to transmit data. This enables the DPC to transmit data until it reads a frame in which the MORE bit in the descriptor has a value of zero. After a frame has been written into the Buffer Memory it cannot be altered. However, additional frames with the MORE bit = 1 in all but the last new frame may be added to either chain. The enable command may be pipelined so that two (but not more than

two) enable commands are waiting to be serviced at the same time (see Figure 2).

The FORMAC determines whether to send an S-frame or A-frame on the basis of the THT and the T-late flag. The DPC uses DRDREQS to request an S-frame and issues DRDREQA to request an A-frame. Two read pointers (RPXS and RPXA) are maintained by the RBC to aid the DPC in reading frames from the two chain FIFOs.

The RBC can use the same transmit write pointer (WPX) to let the Host write to either of the two chain queues since this pointer is set by the NP. The NP knows whether the frame is an S-frame or A-frame, and can set the pointer to the correct chain.

Pointers to the beginning and end of Buffer Memory are not needed in chain mode. The NP is responsible for knowing what address space is available.

09729-005B

Figure 2. Chain Queues in Buffer Memory

#### **RBC-NP Interaction**

NP requests can be generated through direct hardwired signals, or by programming, using the RBC instruction set. The NP can access the Buffer Memory through the DMA (D-bus) using request pins and the MAR register. It can also access the RBC and Buffer Memory using the NP-bus and RBC instructions placed on the INST0-3 and  $R/\overline{W}$  lines.

Although NP requests can be generated in several ways, only one address pointer, MAR, is provided in the RBC for all NP services. Therefore, the user must limit the generation of NP requests to only one source at a time.

NP requests have the second highest priority in arbitration and are serviced unless a DPC request is also present. A mode bit called MENNPRQ is provided in the mode register to enable or disable the NP pin requests. If an NP pin request and instruction request are presented simultaneously, then the instruction request is serviced. If NP read and write requests are presented simultaneously, then neither one is serviced. The NP DMA requests have priority over Host DMA requests.

#### **NP Hardwired DMA Requests**

The NP has access to the Buffer Memory (including the

receive and transmit FIFOs) through NP read or write DMA request pins and the D-bus. One RBC pointer (MAR) is used for this function.

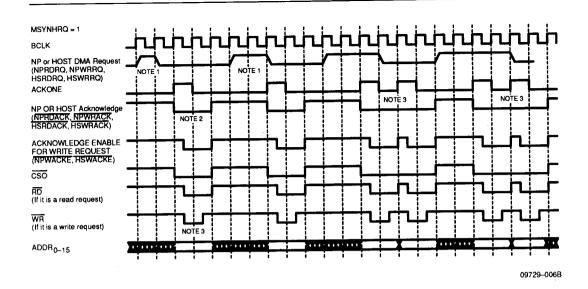

DMA requests for reading or writing are made on two pins, NPRDRQ and NPWRRQ, respectively. When these are being serviced, the appropriate signal, NPRDACK or NPWRACK, becomes LOW for the duration of the transfer. Also, for the write request, NPWACKE becomes LOW for 1-1/2 clock periods in the middle of the transfer. Simultaneously, the MAR value is placed on the ADDR-bus.

For a read, the NP transfers the Buffer Memory data through the D-bus to the NP memory. For a write, the NP provides the write data on the D-bus (from the NP memory). After the service, the MAR increments to point to the next higher location. The MAR is not restricted by the limits of any FIFO and always increments to the next location. When it reaches its highest value of all ones (FFFF in hex), it is cleared to a value of all zeros.

The NPRDRQ and NPWRRQ pins are typically used by the NP for block transfer of data to or from the memory using DMA. Less frequent or smaller transfers are typically made by the NP using the software instruction requests. The pin requests should be disabled during the NP instruction requests.

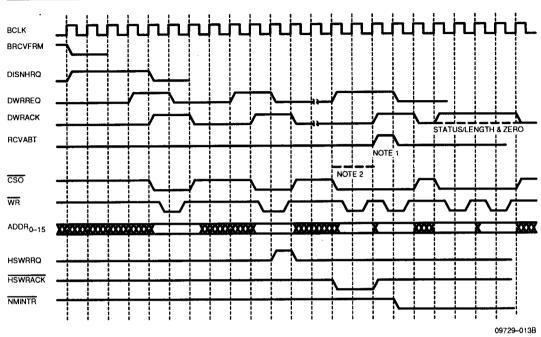

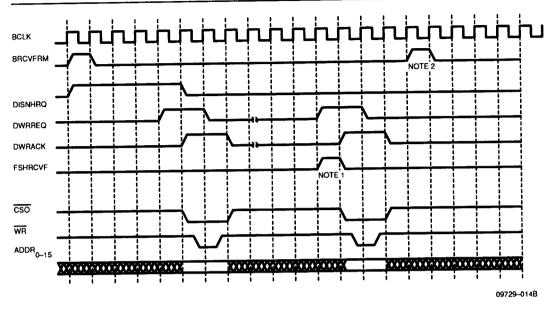

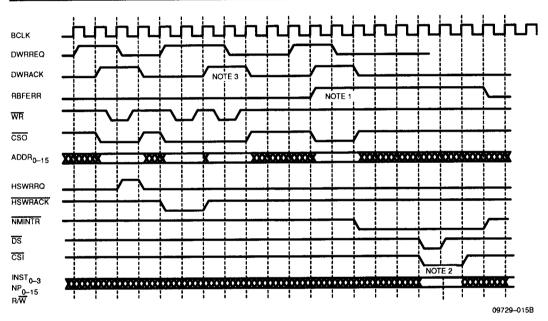

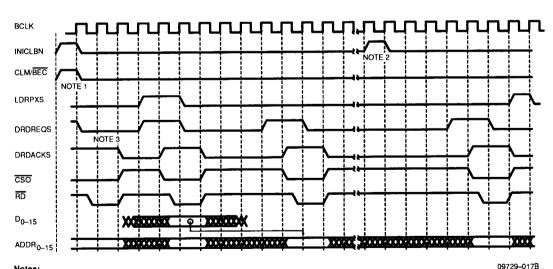

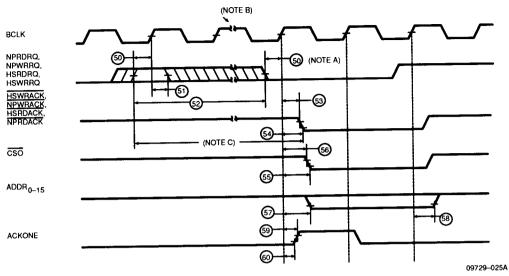

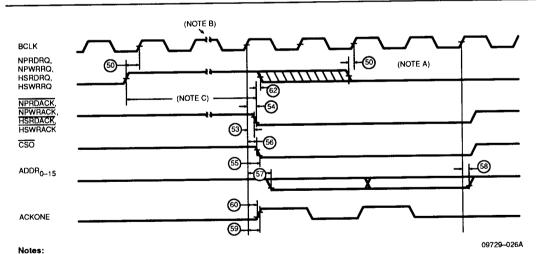

Figure 3. NP or Host DMA Request and Acknowledgement

Definitions: A) Request HIGH for one or two BCLK ↑ is considered a "Pulse Request."

B) Request HIGH for three or more BCLK ↑ is considered a "Level Request."

#### Notes:

- 1) For each "Pulse Request," the RBC acknowledges one memory access.

- 2) Each memory access is two BCLK cycles long.

| Memory Read                                                                      | Memory Write                                                                                 |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| CSO, ADDR <sub>0-15</sub> , NPRDACK, and HSRDACK are active for two BCLK cycles. | CSO, ADDR <sub>0-15</sub> , NPWRACK, and HSWRACK are active for two BCLK cycles.             |

| RD is active for the last half of the first BCLK and the entire second BCLK      | WR is active for the last half of the first BCLK and the first half of the second BCLK cycle |

- 3) For "Level Requests" when the RBC has no request pending from any other source, the subse quent acknowledge can be continuous as shown. Under this condition, request HIGH for (2n-1) or (2n) BCLK cycles generates (n) acknowledges (where n ≥ 2). xxxACK and ACKONE may ANDed together to count the number of requests acknowledged.

- 4) If MSYNHRQ = 0, then acknowledge (ACKONE, NP, or Host Acknowledge, Acknowledge Enable) becomes active one BCLK cycle later.

- 5) If MSYNHRQ = 0, the request is considered a "Pulse Request" if (one BCLK + 20 ns) < pulse width < (two BCLK cycles)</p>

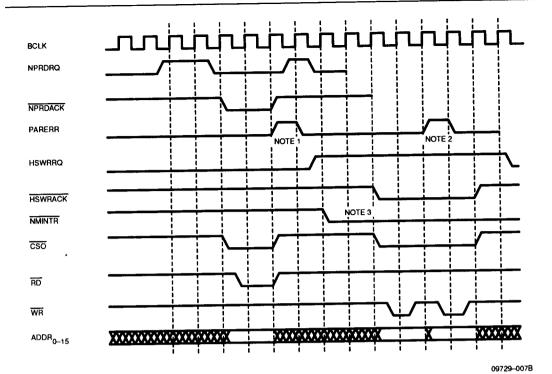

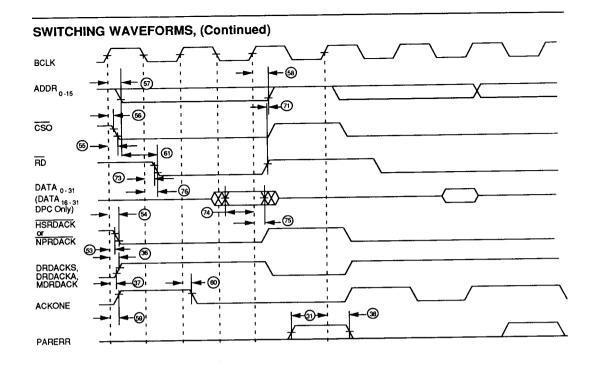

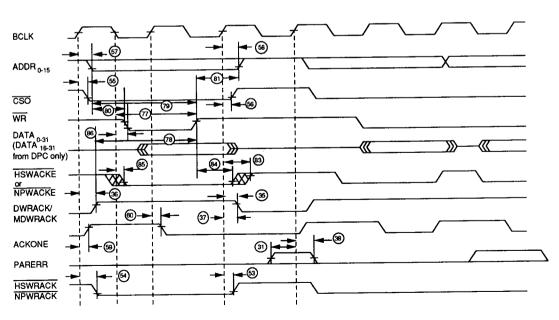

Notes:

- 1. PARERR active right after the acknowledgement (which means that the read or write access just done has a parity error) causes further requests of the same type to be ignored.

2. However, if the request is level, even though the parity error occurs for the previous acknowledgement, it takes one extra acknowledgement before the RBC can stop servicing the request.

3. Parity error always asserts NMINTR pin. Parity error for NP or Host DMA request is a dramatic event, so the RBC locks the pointer which causes the error and waits for the Node Processor to recognize and clear the error. On the other hand, parity error in DPC read/write request or NP read/write request through instructions does not lock the pointer but only sets the status bit and causes a non-maskable interrupt.

Figure 4. Parity Error in NP or Host DMA Service

#### **RBC Programming**

Programming is performed by the NP using the instruction set and the mode bit set of the RBC. The instruction set is used not only to load and read the internal registers of the RBC, but also to change the state of the RBC.

All of the RBC programming is done by the NP using

INST<sub>0-3</sub>, R/ $\overline{W}$ , and the NP-bus. The NP<sub>0-15</sub> bus is used for transferring data to and from the Buffer Memory by way of the MDRU and MDRL registers in the DPC and the D-bus. The NP-bus is also used to transfer pointer register and mode register values to and from the RBC, and to read the status registers. The instruction set is listed in Table 1.

Table 1. RBC Instruction Set

| Instruction<br>Mnemonic | R/W        | INST <sub>3</sub> | INST <sub>2</sub> | INST <sub>1</sub> | (LSB)<br>INST <sub>0</sub> | NP <sub>0-15</sub>    | Function                       |

|-------------------------|------------|-------------------|-------------------|-------------------|----------------------------|-----------------------|--------------------------------|

| Software Res            | ent.       |                   |                   |                   |                            |                       |                                |

| IRESET                  | 0          | 0                 | 0                 | 0                 | 0                          | XXXX                  | Software Reset                 |

| Instructions            | to Load at | nd Read RR        | C Pointer I       | Registers:        |                            |                       |                                |

| ILDRPXS                 | 0          | 0                 | 0                 | 0                 | 1                          | wwww                  | Load RPXS                      |

| IRDRPXS                 | 1          | ŏ                 | Ö                 | Ö                 | 1                          | RRRR                  | Read RPXS                      |

| ILDRPXA                 | ò          | ŏ                 | Ö                 | 1                 | 0                          | www                   | Load RPXA                      |

| IRDRPXA                 | 1          | Ŏ                 | Ō                 | 1                 | 0                          | RRRR                  | Read RPXA                      |

| ILDRPR                  | Ò          | Ö                 | Ö                 | 1                 | 1                          | wwww                  | Load RPR                       |

| IRDRPR                  | 1          | ŏ                 | ŏ                 | 1                 | 1                          | RRRR                  | Read RPR                       |

| ILDWPX                  | Ö          | Ö                 | 1                 | 0                 | 1                          | wwww                  | Load WPX                       |

| IRDWPX                  | 1          | ŏ                 | 1                 | 0                 | 1                          | RRRR                  | Read WPX                       |

| ILDWPR                  | o<br>O     | Ŏ                 | 1                 | 1                 | 0                          | wwww                  | Load WPR                       |

| IRDWPR                  | 1          | ŏ                 | 1                 | 1                 | 0                          | RRRR                  | Read WPR                       |

| ILDACP                  | ò          | ŏ                 | 1                 | 1                 | 1                          | wwww                  | Load ACP                       |

| IRDACP                  | 1          | ŏ                 | 1                 | i                 | 1                          | RRRR                  | Read ACP                       |

| ILDSAR                  | ò          | 1                 | o<br>O            | Ò                 | Ö                          | wwww                  | Load SAR                       |

| IRDSAR                  | 1          | i                 | Ö                 | Ŏ                 | Ŏ                          | RRRR                  | Read SAR                       |

| ILDRPCB                 | Ö          | i                 | Ö                 | Ŏ                 | 1                          | wwww                  | Load RPCB                      |

| IRDRPCB                 | 1          | i                 | ŏ                 | Õ                 | 1                          | RRRR                  | Read RPCB                      |

| ILDEAR                  | Ö          | i                 | ŏ                 | 1                 | Ò                          | wwww                  | Load EAR                       |

| IRDEAR                  | 1          | 1                 | ŏ                 | i                 | Ö                          | RRRR                  | Read EAR                       |

| ILDMAR                  | Ö          | Ó                 | 1                 | Ó                 | Ŏ                          | WWWW                  | Load MAR                       |

| IRDMAR                  | 1          | 0                 | 1                 | 0                 | 0                          | RRRR                  | Read MAR                       |

|                         |            |                   |                   |                   |                            |                       |                                |

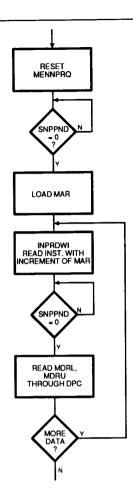

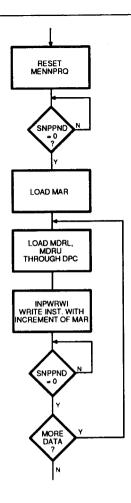

| Instructions            |            |                   |                   |                   | IS:                        | xxxx                  | Read memory without            |

| INPRDNI                 | 0          | 1                 | 0                 | 1                 | 1                          | * * * *               | incrementing MAR               |

| IN IDIA IDIA I          | •          |                   | 1                 | 0                 | 1                          | $x \times x \times x$ | Write memory and               |

| INPWRWI                 | 0          | 1                 |                   | U                 | ,                          | ^ ^ ^ ^               | increment MAR                  |

|                         | _          |                   | 4                 |                   | 0                          | $x \times x \times$   | Read memory and                |

| INPRDWI                 | 0          | 1                 | 1                 | 1                 | U                          | ^ ^ ^ ^               | increment MAR                  |

| Instructions            | Using the  | Mode Regi         | ster:             |                   |                            |                       |                                |

| ILDMOD                  | 0          | 1                 | 1                 | 0                 | 0                          | wwww                  | Load mode                      |