# High-Performance SCSI Protocol Chip

### PRELIMINARY

#### SCSI Interface

- Asynchronous Transfers Up To 3 Mbytes/Second

- Synchronous Transfers

Up To 5 Mbytes/Second

With An 8-Byte Offset

- Both Initiator And Target Roles Supported

- Automatic Arbitration, Selection, And Reselection

- Automatic Response To Selection And Reselection

- Parity Generation And Checking

- Integrated 48 mA Drivers And Receivers

- Supports SCSI Bus Differential Option With External Drivers And Receivers

- 24-Bit DMA Byte Counter

#### Microprocessor And Buffer Interface

- Up To 20 Mbyte/Second Memory Data Transfer Rate (100 ns Buffer Cycle Time)

- 8-Bit And 16-Bit Buffer Data Bus

- Parity Generation And Checking

- All Interrupts Maskable

- Separate Buffer And Microprocessor Data Bus

- Multiplexed And Nonmultiplexed Microprocessor Addressing Modes

- Direct Access To SCSI

Data From Microprocessor

© Copyright Adaptec, Inc. 1987, 1988. All rights reserved. The information contained in this data sheet is subject to change without notice. No part of this document may be copied or reproduced in any form without prior written consent from Adaptec, Inc.

## CONTENTS

| OVERVIEW                                                             | 3  |

|----------------------------------------------------------------------|----|

|                                                                      | 4  |

| FUNCTIONAL OVERVIEW                                                  | 6  |

| Microprocessor Interface And Input/Output Control                    |    |

| SCSI Bus Interface Control And Handshake                             |    |

| Parity Logic                                                         | 9  |

| SCSI Select And Reselect Control                                     |    |

| Memory Interface Control And Handshake                               |    |

| General Purpose Input/Output Port                                    |    |

| Eight-Byte FIFO                                                      | 12 |

| PIN DESCRIPTIONS                                                     |    |

| REGISTER DESCRIPTIONS                                                |    |

| Register Conditions On Reset                                         |    |

| Internal Register Descriptions                                       |    |

| Detailed Register Descriptions                                       |    |

| FUNCTIONAL DESCRIPTION AND OPERATION                                 | 42 |

| Microprocessor Interface                                             |    |

| Power-On Reset And Chip Initialization                               |    |

| SCSI Interface                                                       |    |

| Single-Ended Interface Option                                        |    |

| Differential SCSI Interface Control                                  | 45 |

| SCSI Arbitration And Selection Or Reselection                        |    |

|                                                                      |    |

| SCSI Data Transfer (Initiator And Target Modes)                      |    |

| DMA Transfer—Asynchronous SCSI                                       |    |

| DMA Transfer—Synchronous SCSI<br>Automatic PIO Mode Of Data Transfer |    |

| Microprocessor Controlled PIO                                        |    |

| Microprocessor Conitolied PiO                                        |    |

| DMA Transfer                                                         |    |

| Microprocessor Controlled Memory Read/Write                          |    |

| General Purpose I/O (GP I/O) Ports                                   |    |

| Port A                                                               |    |

| Port B                                                               |    |

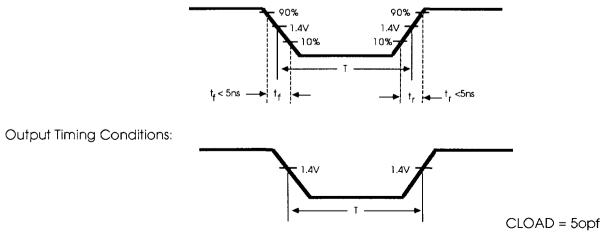

| AC/DC TIMING PARAMETERS                                              | 63 |

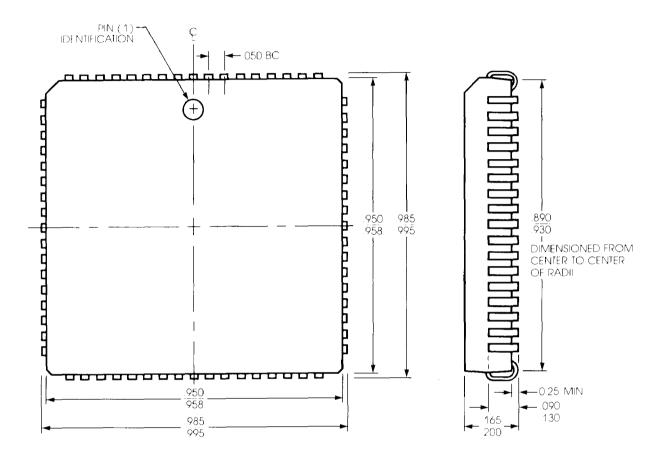

| PACKAGING INFORMATION                                                |    |

### **OVERVIEW**

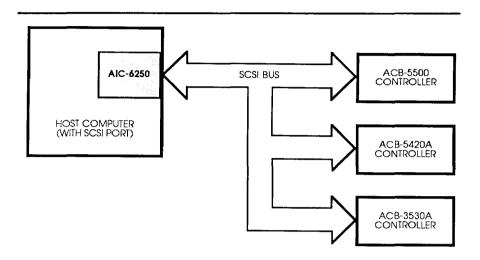

The Small Computer Systems Interface (SCSI) defines an I/O channel (bus) used for interfacing host computers (via host adapters), controller boards and peripheral devices with embedded controllers. The SCSI specification defines electrical characteristics, mechanical specifications and the software protocol for devices attaching to the SCSI bus. For a typical SCSI bus configuration, see Figure 1.

The following is a list of key features provided in the SCSI specification:

- Up to eight devices on the bus (Each device may be an initiator or target or both)

- Software protocol (command structures and message system)

- Low-cost single-ended drivers and receivers (allowing cable lengths up to six meters)

- Optional differential drivers and receivers (allowing cable lengths up to 25 meters)

- A two-wire asynchronous handshake protocol

- An optional synchronous transfer protocol with a variable offset

- Odd-data parity

For more information on the SCSI architecture, refer to the ANSI standard X3.131–1986.

### INTRODUCTION

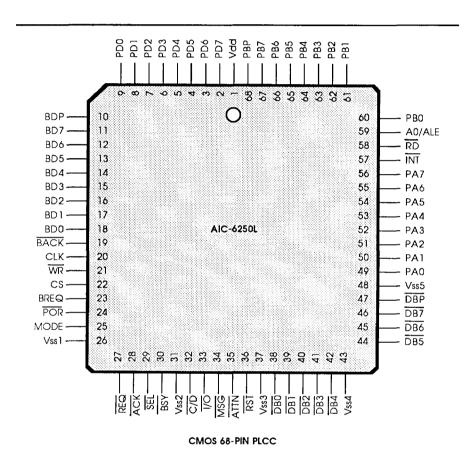

The Adaptec AIC-6250 High-Performance SCSI Protocol Chip provides all the functions necessary to implement a high-performance SCSI interface on a host computer or a peripheral device. The AIC-6250 integrates an eight-byte internal FIFO, SCSI bus control, two general purpose ports and memory interface control, into one 68-pin PLCC package. The AIC-6250 also provides application flexibility by being designed to work with either the host microprocessor.

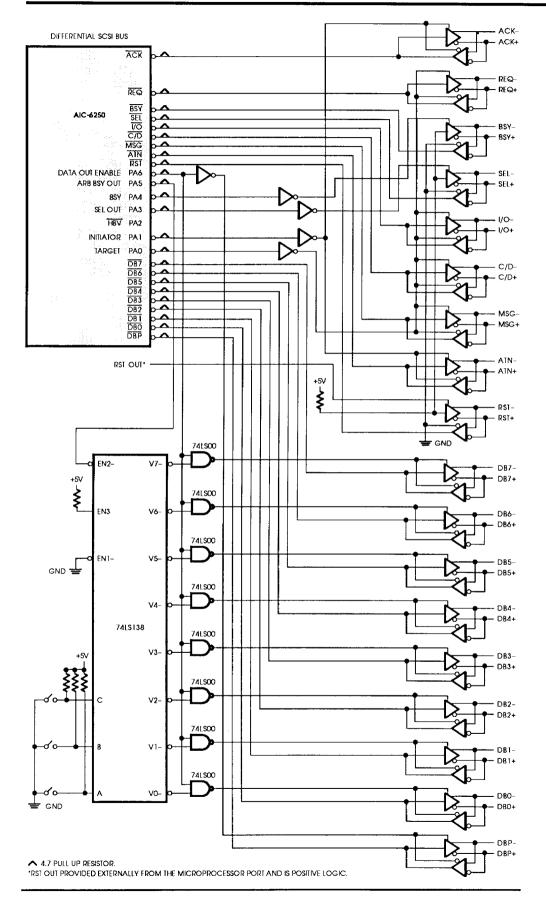

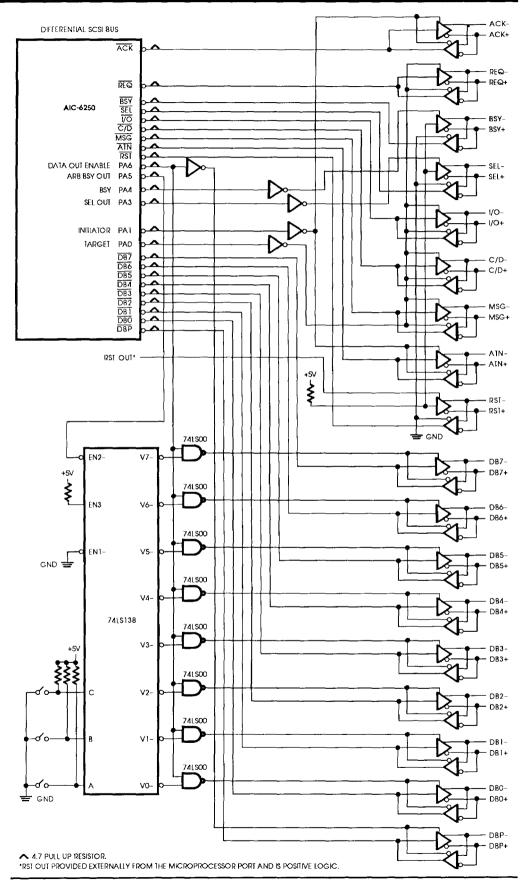

The AIC-6250 provides 48 mA open collector drivers for the single-ended SCSI bus interface. For the differential SCSI bus, all the control signals required to control external drivers and receivers are provided.

The AIC-6250 supports both the SCSI bus initiator and target roles. The SCSI bus Initiator is the device which initiates an operation on the SCSI bus. The operation is initiated by:

- 1. Waiting for a bus free condition.

- 2. Arbitrating for control of the bus.

- 3. Selecting the device from which the activity is requested.

- 4. Sending the command descriptor block, defining the activity which is to occur.

During this sequence of events, the initiator has control of the bus only during the Arbitration and Selection phases. Once Selection is complete, the target device takes control of the bus by driving the signals which establish the appropriate phase, and initiating the Information transfer through asserting and deasserting the REQ signal. By supporting both the SCSI bus initiator and Target roles, the AIC-6250 may be easily used in any SCSI bus configuration (see Figure 1 for a typical SCSI bus configuration). The register set of the AIC-6250 has been implemented to allow the same software subroutines to manage both initiator and target roles. This adds to the flexibility of the part by making such operations as host-to-host or device-initiated operations (copy command), easy to implement.

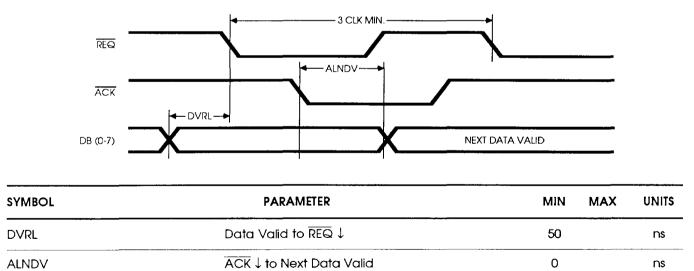

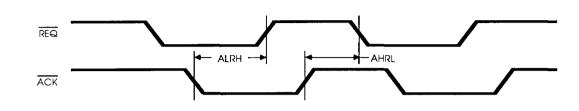

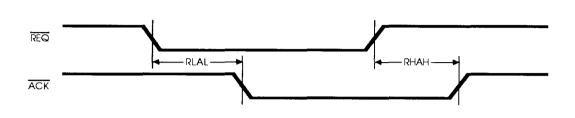

The AIC-6250 also supports both the asynchronous and synchronous methods of information transfer on the SCSI bus. Asynchronous transfer is a two-wire handshake protocol where the target device drives the SCSI REQ signal, and the initiator device drives the SCSI ACK signal. Synchronous transfer is similar to the asynchronous transfer, but the  $\overline{REQ}$ and ACK signals may be offset by an offset count up to the size of the internal FIFO (a performance advantage is realized with a FIFO up to eight bytes). The AIC-6250 has an eightbyte FIFO, allowing a REQ to ACK offset of up to eight bytes during synchronous transfer. This offset, combined with the high speed of the AIC-6250, provides a synchronous transfer rate of up to 5 Mbytes per second. For asynchronous transfer, the AIC-6250 provides high-speed data transfer with SCSI bus data transfer rates up to 3 Mbytes per second. To increase the overall system performance, the eight-byte FIFO in the AIC-6250 is used as a speed matching buffer between the SCSI bus and the system memory when the AIC-6250 is being used in the asynchronous mode. This increases the system performance by making the SCSI bus data transfer rate independent of the host data transfer rate; thus, allowing data to be buffered in the AIC-6250 and to burst into system memory when access to system memory is given.

The maximum system performance is a function of both the speed of data transfer on the SCSI bus as well as the speed of the memory DMA Transfer. The AIC-6250 has broken the bottleneck for the memory DMA Transfer by providing a maximum DMA Transfer speed, with a 16-bit bus interface, of 20 Mbytes per second.

For lower bandwidth systems, the eight-bit only bus may be implemented. The upper eight bits are configured as a general purpose I/O port. In the eight-bit memory bus mode, the AIC-6250 has a maximum DMA speed of 10 Mbytes per second.

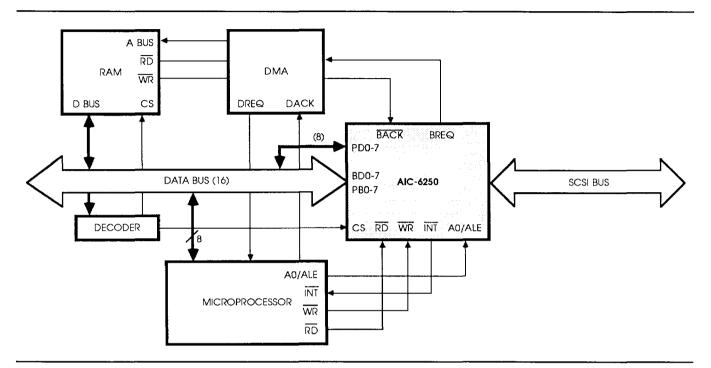

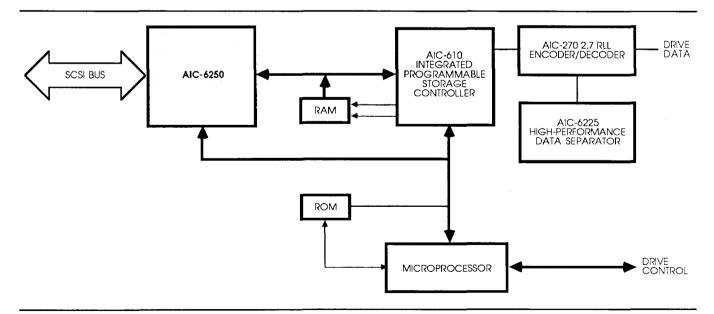

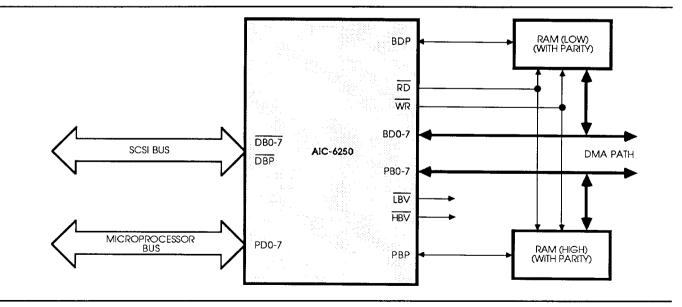

See Figure 2 for a block diagram of a typical host Implementation using a 16-bit memory bus. See Figure 3 for a typical controller design block diagram using a local support microprocessor.

FIGURE 2. BLOCK DIAGRAM OF A TYPICAL HOST IMPLEMENTATION USING A 16-BIT MEMORY BUS

FIGURE 3. BLOCK DIAGRAM OF A TYPICAL SCSI DRIVE CONTROLLER DESIGN USING A LOCAL MICROPROCESSOR

### FUNCTIONAL DESCRIPTION

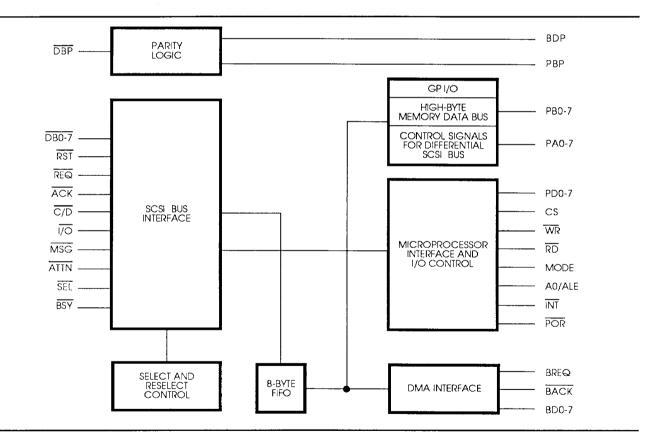

Internal to the AIC-6250 are seven main functional blocks:

- 1. Microprocessor interface and Input/Output control

- 6. General purpose Input/Output ports

- 2. SCSI bus interface control and handshake

- Figure 4 shows the major functional blocks of the AIC-6250.

- 3. Parity logic

- 4. SCSI Select and Reselect control

- 5. Memory interface control and handshake

.

### Microprocessor Interface And Input/Output Control

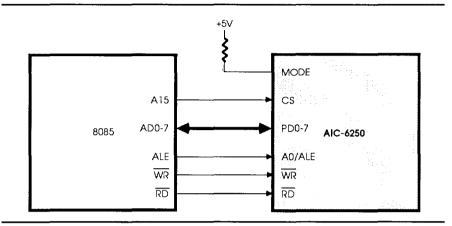

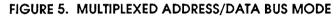

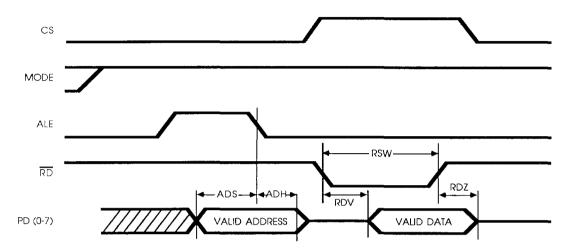

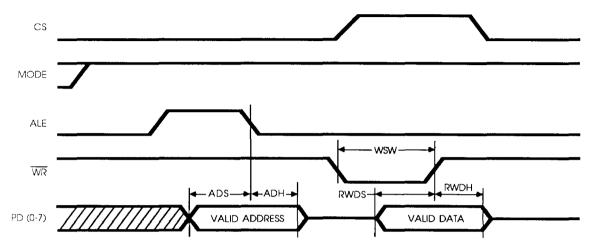

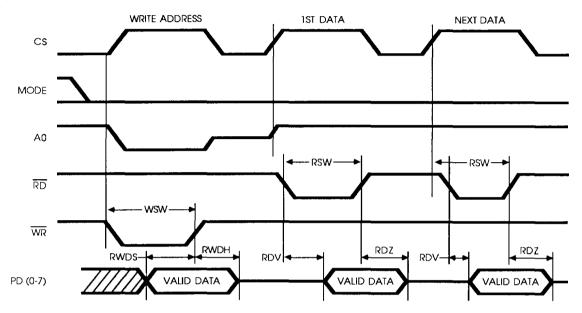

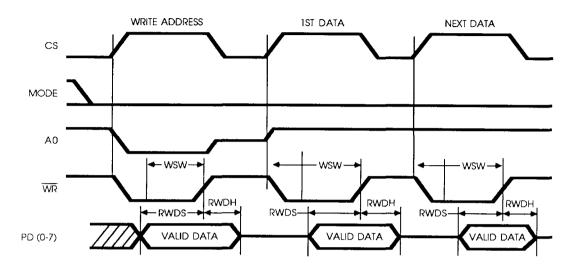

The microprocessor interface will support either an eight-bit multiplexed bus, such as that found on the Intel family of processors, or a nonmultiplexed bus, such as that found in the Motorola family of processors. The mode of operation (which type of microprocessor interface is used) is selected through the MODE signal (pin 25) of the chip. See Figure 5 for an example of a multiplexed address/data bus and Figure 6 for an example of a nonmultiplexed address and data bus design using the AIC-6250.

The AIC-6250 decodes addresses from  $00_{\rm H}$  to  $0F_{\rm H}$ . In order to prevent erroneous operation, no other addresses are decoded.

The AIC-6250 also allows the microprocessor access to SCSI data or memory data through its internal registers without any external hardware.

FIGURE 6. NONMULTIPLEXED (SEPARATE) ADDRESS/DATA BUS MODE

### SCSI Bus Interface Control And Handshake

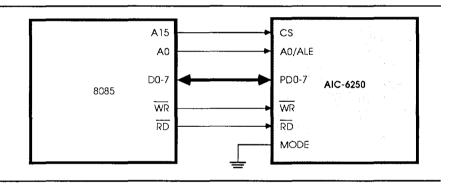

The SCSI bus interface control block includes the 48 mA drivers and receivers for the single-ended SCSI bus option. This eliminates the need for external drivers and receivers. The SCSI bus interface block also provides the logic to implement the target or initiator modes of SCSI bus operation. Figure 7 shows the AIC-6250 connections for the singleended SCSI bus.

The SCSI bus interface control and handshake block also implements both asynchronous and synchronous transfer, as well as three different data transfer methods. The available data transfer methods are as follows:

- 1. DMA Transfer,

- 2. Automatic SCSI bus handshake (Automatic PIO), or,

- 3. Microprocessor controlled SCSI bus PIO handshake (Manual PIO).

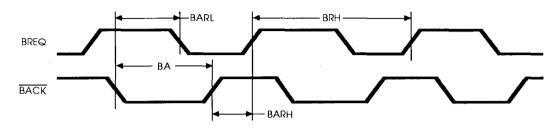

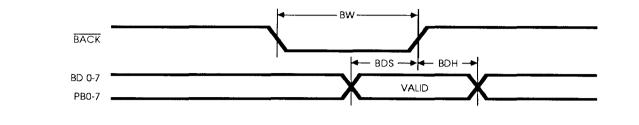

DMA Transfer; DMA Transfer is a "hands off" method of transferring information (commands, data or messages). When the DMA Transfer method is used, both the SCSI bus and the memory handshake are performed automatically by the AIC-6250. The memory interface handshake (BREQ/BACK) is asynchronous and transfers a byte/word of data in the 8-bit/16-bit mode, respectively, per handshake. DMA transfer is the only method of data transfer which may be used with synchronous transfer. For maximum SCSI bus transfer rates in the synchronous transfer mode, the FIFO allows up to an eightbyte offset, except for initiator inbound data transfer, where the maximum offset is seven. In the asynchronous transfer mode, DMA transfer uses the FIFO as a speed matching buffer between the host bus and the SCSI bus to increase the overall system performance.

Included in the AIC-6250 is a 24-bit DMA Byte Counter, allowing data transfers of up to 16 Mbytes in length. To ease the handling of disconnection/reconnection, or error conditions, the DMA Counter is decremented for each byte that is transferred across the SCSI bus. This is independent of the number of bytes which may be in the FIFO, or the offset count, when using synchronous transfer.

Automatic PIO: Automatic PIO requires the microprocessor to intervene once each byte time. After completion of the information transfer, an interrupt will be generated, or the microprocessor can mask out the microprocessor interrupt and poll for the completion of transfer. This method of information transfer requires the microprocessor to also read/write the data to/from the SCSI Data Register. Automatic PIO may not be used with synchronous transfer and does not utilize the FIFO in the asynchronous mode. Microprocessor Controlled PIO: Microprocessor controlled PIO gives the microprocessor complete control over the SCSI REQ or ACK signal (depending on whether the AIC-6250 is supporting the SCSInitiator or target role). This method of data transfer requires the microprocessor to also read/write the data to/from the SCSI Data Register. Microprocessor controlled PIO may not be used with synchronous transfer and does not utilize the FIFO in the asynchronous mode.

When in the initiator mode, all SCSI bus transfers and transfer methods may be set up in advance of the transfer, with the exception of the microprocessor controlled PIO handshake. In addition, by predicting the next phase (using the expected phase function by setting the expected phase in the SCSI Signal Register), the AIC-6250 improves system performance by reducing the software overhead time to respond to a phase. This feature saves the microprocessor from waiting for a phase to be valid with the REQ signal set, then proceeding with the information transfer. This allows the host to immediately begin information transfer once the SCSI bus phase matches the expected phase and the REQ signal is asserted.

### **Parity Logic**

The parity logic generates and optionally checks SCSI bus odd parity during information transfer on the SCSI bus, as well as automatically generating and optionally checking odd oarity on memory data. While parity generation and checking is automatically performed, the generation of an interrupt in the event of a parity error is optional.

When parity checking is enabled and a parity error is detected on a memory transfer, the AIC-6250 will halt the transfer immediately and interrupt the microprocessor. The microprocessor must then perform the appropriate error recovery action. In order to continue the transfer, parity error should be reset by disabling the En Parity bit. When the 16-bit memory transfer mode is being used, the AIC-6250 will generate and check parity on both the high and the low bytes of data with one parity bit for each byte.When parity checking is enabled and a parity error is detected on a SCSI bus transfer, the transfer will continue until transfer count equals zero or the transfer is terminated by the microprocessor.

The AIC-6250 generates parity on the SCSI bus also; however, flow through parity is not supported.

### SCSI Select And Reselect Control

The SCSIselect and reselect control provides the logic to perform the SCSI bus arbitration scheme, implemented by most SCSI systems, as well as automatic response to selection and reselection.

The AIC-6250 will automatically look for the SCSI BUS FREE phase. When the BUS FREE phase is detected and enable selection is active, the AIC-6250 will arbitrate for control of the SCSI bus. If arbitration is won, the AIC-6250 will proceed to the SELECTION or RESELECTION phase.

The SCSI selection timeout may be accomplished by starting a timer from an interrupt which occurs when arbitration has been won and the AIC-6250 asserts the SCSI SEL signal.

The completion of the automatic arbitration and selection/reselection process is indicated by an interrupt.

### Memory Interface Control And Handshake

The AIC-6250 will work well with a DMA control device to improve overall system performance by transferring data to or from the system bus at very high data rates. The DMA interface of the AIC-6250 is capable of achieving data transfer speeds of up to 20 Mbytes per second when used in the 16-bit mode (a two-byte transfer every 100 nanoseconds), as shown in Figure 9.

By interfacing the eight-byte FIFO directly with the DMA interface, the FIFO is used as a speed matching buffer when the chip is used in the asynchronous mode. This allows the data transfer rates of the system bus and the SCSI bus to be loosely coupled.

Memory data transfer may occur through one of two ways:

1. Automatically when in the DMA transfer mode: When transferred through the DMA mode, the data comes from the SCSI bus, through the FIFO and into memory (although the AIC-6250 does not generate any addresses for the data to be transferred to). This method of information transfer does not require any microprocessor intervention during the data transfer.

2. The microprocessor must read/ write the memory when transferring data using Automatic PIO: When the microprocessor uses the AIC-6250's ability to read/write the memory, the microprocessor must:

- Confirm no DMA activity is occurring

- Set up HBV and LBV signals in Port A for 16-bit memory data (not required for 8-bit).

- Set transfer direction and read/ write the information to/from the appropriate register

- Request a memory cycle.

Using the capability of the AIC-6250 to directly read/write memory, eliminates the need for additional hardware to allow the microprocessor to transfer directly to or from memory.

### General Purpose Input/Output Port

The AIC-6250 provides two general purpose I/O ports, Port A and Port B.

In the default state, Port A is an input or an output/input port. In this mode, all bits may be used as inputs or as outputs. When used as an output port, the values last written to the output port may be read at any time.

When the AIC-6250 is programmed to operate in the 16-bit memory interface mode, Port A, Bits 2 and 7, function as the HBV (High Byte Valid) and LBV (Low Byte Valid) signals used in conjunction with DMA odd-byte transfers. They are enabled as outputs, regardless of the mode of Port A selected.

Port A may also alternatively be used for the differential SCSI bus control as shown in Figure 8. When Port A is used as the differential SCSI bus control, all other bits (except Bit 7 and Bit 2 which perform the LBV and HBV functions) are automatically controlled by the AIC-6250 for the differential SCSI bus. in this mode, the functions of the various pins of Port A are as follows:

PA7 LBV PA6 Data Out Enable PA5 <u>ARB BSY</u> Out PA4 <u>BSY Out</u> PA3 <u>SEL Out</u> PA2 HBV PA1 Initiator PA0 Target

Figure 8 shows Port A being used as the differential SCSI bus interface control logic. Since the SCSI RST Out signal is not being provided by the Port A control logic, it must be externally provided by a microprocessor port.

FIGURE 8. DIFFERENTIAL SCSI BUS CONTROL WITH PORT A

Port B has two uses, as follows:

1. In the default state, Port B is an input or an output/input port. In this mode, all bits may be used as inputs or as outputs. (When used as an output port, the values last written to the output port may be read at any time.)

2. Alternatively, Port B may be used as the upper byte of the 16-bit memory bus. When Port B is used as the high byte of the memory data transfer, the AIC-6250 will not assert the BREQ signal until two bytes of data are in the FIFO unless odd start or odd end condition is present. The AIC-6250 can transfer two bytes of data to or from the system data bus once every 100 ns, providing a 20 Mbyte/second transfer rate. System performance is therefore increased through no loss of system data bus bandwidth. Figure 9 shows the AIC-6250 configured for a 16-bit memory interface.

NOTE: Pin 68 is the Parity bit for the high byte of data passed through Port B.

### **Eight-Byte FIFO**

The eight-byte FIFO allows an eightbyte offset (for maximum Synchronous SCSI bus performance) when the AIC-6250 is used in the synchronous transfer mode except for initiator inbound transfers where the maximum offset is seven. When used in the asynchronous transfer mode, with a DMA transfer, the eight-byte FIFO works as a speed matching buffer between the SCSI bus and the memory.

FIGURE 9. 16-BIT MEMORY INTERFACE USING PORT B

### PIN DESCRIPTIONS

| SYMBOL | PIN   | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |       |      | BUFFER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BDP    | 10    | 1/0  | BUFFER DATA PARITY: Buffer Data Parity is always generated, but checking is<br>optional. Buffer Data Parity Checking is enabled by setting the Enable<br>Memory Parity Error Interrupt bit in the Interrupt Mask Register 1 (Bit 4 of<br>Register 06) to 1.                                                                                                                                                                                                             |

| BD0-7  | 11-18 | 1/0  | BUFFER DATA BUS BITS 0-7: Byte parallel data lines to/from the buffer.<br>NOTE: Port B provides the upper eight bits for the 16-bit bus configuration.                                                                                                                                                                                                                                                                                                                  |

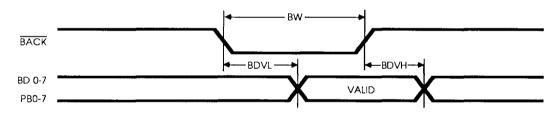

| BREQ   | 23    | 0    | BUFFER REQUEST: This signal is used with the $\overline{BACK}$ signal to provide memory cycle requests.                                                                                                                                                                                                                                                                                                                                                                 |

| BACK   | 19    | Ι    | BUFFER ACKNOWLEDGE: Used to indicate a memory transfer cycle is active.<br>During data transfers from memory to the SCSI bus, the rising edge of this signal<br>is used to latch the data. During data transfers from the SCSI bus to memory, this<br>signal is used to enable data onto the memory bus.                                                                                                                                                                |

|        | i ,   |      | MICROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PD0-7  | 2-9   | I/O  | PROCESSOR DATA BUS BITS 0-7: Used for bidirectional data transfer between the microprocessor and the AIC-6250.                                                                                                                                                                                                                                                                                                                                                          |

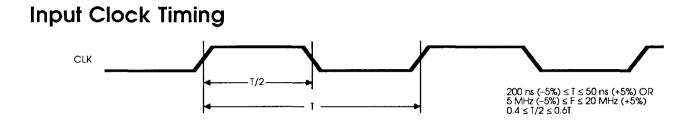

| CLK    | 20    | I    | CLOCK: Used for a clock input between 5 MHz and 20 MHz with higher clock<br>rates providing higher transfer rates. When the input clock frequency is higher thar<br>10 MHz, the Clock Frequency Mode bit (Bit 2, Register 08) must be set to 1 to<br>ensure correct SCSI bus timing in the Arbitration and Selection or Reselection<br>phases. NOTE: For maximum arbitration and selection performance, the clock<br>input should be 10 MHz or 20 MHz.                  |

| WR     | 21    | ł    | WRITE: With CS active, on the rising edge of this signal, data is strobed from the microprocessor bus to the specified register in the chip.                                                                                                                                                                                                                                                                                                                            |

| CS     | 22    | I    | CHIP SELECT: This signal allows microprocessor access to/from the chip when active.                                                                                                                                                                                                                                                                                                                                                                                     |

| POR    | 24    | I    | POWER ON RESET: When this signal is driven low for a minimum of 50 ns, the chip<br>is reset. The software reset latch will remain active until it is cleared by the<br>microprocessor. To clear the reset latch, the microprocessor must set Bit 0 of<br>Register 08 to 0. When POR is active, bidirectinal pins will be tri-stated.                                                                                                                                    |

| MODE   | 25    | 1    | <ul> <li>MODE: This pin allows the AIC-6250 to be used easily with microprocessor's having either a multiplexed address/data bus or a nonmultiplexed address/data bus.</li> <li>High: The microprocessor data bus supports multiplexed data and addresses with A0 used as the ALE input.</li> <li>Low: The microprocessor data bus is used for data only with A0 used as address line 0. All registers must be addressed indirectly by the Address Register.</li> </ul> |

| SYMBOL  | PIN | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                     |

|---------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     |      | MICROPROCESSOR INTERFACE (Continued)                                                                                                                                                                                                                                                                                                                                                  |

| INT     | 57  | 0    | INTERRUPT: This active low open drain output signal indicates an interrupt is pending. The interrupt condition is described in Interrupt Mask Register 0 (Register 03) and Interrupt Mask Register 1 (Register 06).                                                                                                                                                                   |

| RD      | 58  | 1    | READ: $\overline{\text{RD}}$ and CS active cause the data from the specified register to be read onto the Processor Data Lines (PD0-7).                                                                                                                                                                                                                                               |

| A0/ALE  | 59  |      | ADDRESS 0/ADDRESS LATCH ENABLE: When MODE is low, this pin is address line 0 (A0). In this case, the address of the desired register is loaded into the Address Register during a write cycle. When MODE is high, this control signal is the ALE input.                                                                                                                               |

|         |     |      | SCSI INTERFACE                                                                                                                                                                                                                                                                                                                                                                        |

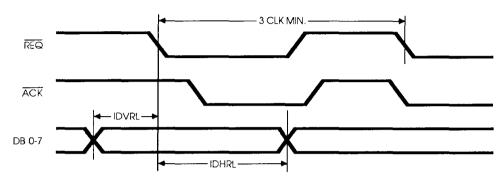

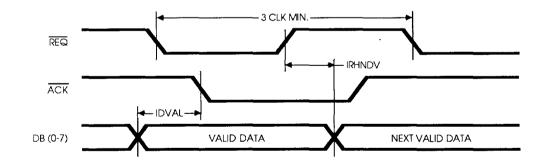

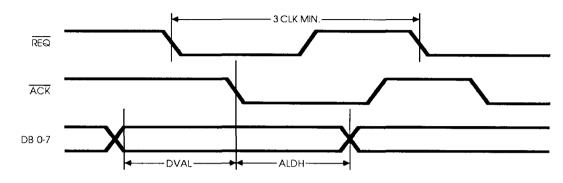

| REQ     | 27  | I/O  | REQUEST: This active low signal is used with the $\overline{ACK}$ signal to perform the SCSI bus handshake protocol. This signal is an input when the chip is operating in the Initiator mode, and is an output when the chip is operating in the target mode.                                                                                                                        |

| ACK     | 28  | 1/0  | ACKNOWLEDGE: This active low signal is used with the REQ signal to perform<br>the SCSI bus handshake protocol. This signal is an output when the chip is<br>operating in the Initiator mode, and is an input when the chip is operating in the<br>target mode.                                                                                                                        |

| SEL     | 29  | I/O  | SELECT: This bidirectional active low signal carries the SCSI selection signal. The signal is used in the SCSI selection and reselection process.                                                                                                                                                                                                                                     |

| BSY     | 30  | 1/0  | BUSY: This bidirectional active low signal carries the SCSI BSY signal. When $\overrightarrow{\text{BSY}}$ is active, the SCSI bus is being used.                                                                                                                                                                                                                                     |

| Ē/D     | 32  | I/O  | COMMAND/DATA: The $\overline{C}/D$ line is low when command information is on the SCSI bus, and is high when data is on the SCSI bus. In the Initiator mode, this signal is an input. In the target mode, this signal is an output.                                                                                                                                                   |

| 1/0     | 33  | 1/0  | INPUT/OUTPUT: This signal is driven by the target and controls the direction of information transfer on the SCSI bus with respect to the initiator. The I/O line is low when information is input to the Initiator. The I/O line is high when information is output from the initiator. In the initiator mode, this signal is an input. In the target mode, this signal is an output. |

| MSG     | 34  | I/O  | MESSAGE: The MSG line is low during a MESSAGE phase on the SCSI bus. In the<br>Initiator mode, this signal is an input. In the Target mode, this signal is an<br>output.                                                                                                                                                                                                              |

| <br>ΑΠΝ | 35  | I/O  | ATTENTION: The ATTN line is driven low to signal to the Target that there is a message to be transferred. In the Initiator mode, this signal is an output. In the Target mode, this signal is an input.                                                                                                                                                                               |

| SYMBOL | PIN                | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                    |      | SCSI INTERFACE (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RST    | 36                 | I/O  | SCSI BUS RESET: This bidirectional active low signal will drive $\overline{\text{RST}}$ low on the SCSI bus when the SCSI Reset Out bit is set in Control Register 1 (Bit 1, Register 08). When this pin is driven low externally, it indicates to the chip that there is another SCSI device forcing a $\overline{\text{RST}}$ condition on the SCSI bus. This condition is internally latched by the chip and may be cleared by asserting $\overline{\text{POR}}$ (pin 24) or a Chip Software Reset (Bit 0, Register 08). |

| DB0-7  | 38-46              | I/O  | DATA BITS 0-7: These active low signals carry 8-bit bidirectional data on the SCSI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DBP    | 47                 | I/O  | DATA BUS PARITY: This active low signal carries Odd Parity on the SCSI bus data.<br>Parity is always generated, but Parity Checking may be disabled by setting to 0<br>the Enable SCSI Parity Error Interrupt in Interrupt Mask Register 1 (Bit 1, Register<br>06).                                                                                                                                                                                                                                                         |

|        |                    |      | PORT INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PA0-7  | 49-56              | I/O  | PORT A BITS 0-7: This eight-bit port may be used as an eight-bit read or<br>write port. It may also be used for differential SCSI bus control. Bit 7 and Bit 2<br>function as the LBV and HBV signals used for handling the 16-bit memory data<br>bus mode.                                                                                                                                                                                                                                                                 |

| PB0-7  | 60-67              | I/O  | PORT B BITS 0-7: This eight-bit port may be used in two ways:<br>General Purpose Port: As a general purpose Input or Output port.<br>16-Bit Memory Data Bus: Port B may also be used as the upper eight bits of<br>the 16-bit memory bus. Parity may be enabled if this port is used as a memory<br>bus.                                                                                                                                                                                                                    |

| PBP    | 68                 | 1/0  | PORT B PARITY: Port B Buffer Data Parity bit. Buffer Data Parity is always<br>generated (when Port B is used as the high byte of memory transfer), but<br>checking is optional. Buffer Data Parity Checking is enabled by setting to 1 the<br>Enable Memory Parity Error Interrupt bit in Interrupt Mask Register 1 (Bit 4,<br>Register 06).                                                                                                                                                                                |

|        |                    |      | POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vcc    | 1                  | PWR  | +5 Volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Vss    | 26,31,<br>37,43,48 | GND  | GROUND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### **REGISTER DESCRIPTIONS**

The AIC-6250 has 16 registers which provide the flexibility and programmability to handle both the SCSI interface and also the interface to the local buffer memory and the controlling processor. These are listed in Table 1 for quick reference and are described in detail in the following sections.

#### **Register Conditions On Reset**

The AIC-6250 essentially has two modes <u>of reset</u>; i.e., the Power On <u>Reset (POR)</u> and the SCSI Reset (SCSI RST) which could be asserted through software on the SCSI bus.

Registers 00, 01, 02, 09, 0A, 0B, 0C, and 0F are not affected by any reset condition and their content is unknown on power up. At other times, it would depend on the activity which preceded the reset action. Also, these registers are relevant only when some activity has been initiated.

Registers 04, 06, 0D and 0<u>E are</u> reset (to inactive zeros) by the POR only.

Registers 05 and 09 are reset (to inactive zeros) by both the POR or SCSI RST. On reset, the state of Register 05(R) would be XX110000. The other registers have multiple conditions as outlined below.

Register 03 is reset to zero by the POR; however, Bit 6 (<u>ARB</u>/SEL Start) would be reset by SCSI RST also.

Register 07 (R), Bits 0,1 are unaffected, while Bits 2-7 are reset by POR. Bits 2,3,5 are also reset and Bit 7 is set to '1' by the SCSI RST condition. Bit 4 will be set to '1' if EN BUS FREE DETECT INT (Reg 06, Bit 2) is set to '1'. Register 07 (<u>W</u>), all bits except Bit 6, are reset by POR, while Bits 3-5 would also be reset by SCSI RST.

Register 08 (R), Bits 0-5, are reset by POR, while Bits 0-2 are reset by SCSI RST also. The state of Bits 3-5 on reset will be '0.' Bit 6 will be '1', Bit 7 will normally be '1' as determined by BACK\*BREQ

Register 08 (W), Bit 5, is a 'don't care.' Bits 1-7 are reset by POR, Bit 0 is set to '1', while Bit 7 is also reset by SCSI RST.

#### TABLE 1. REGISTER SUMMARY

| DMA BYTE COUNT (R/W)<br>00 (L) 01 (M) 02 (H) |                |   |                 |   |   |                 |

|----------------------------------------------|----------------|---|-----------------|---|---|-----------------|

| 7                                            | 27             | 7 | 215             |   | 7 | 2 <sup>23</sup> |

| 6                                            | 26             | 6 | 214             |   | 6 | 222             |

| 5                                            | 2 <sup>5</sup> | 5 | 2 <sup>13</sup> |   | 5 | 2 <sup>21</sup> |

| 4                                            | 24             | 4 | 212             |   | 4 | 2 <sup>20</sup> |

| 3                                            | 2 <sup>3</sup> | 3 | 211             |   | 3 | 2 <sup>19</sup> |

| 2                                            | 2²             | 2 | 210             |   | 2 | 218             |

| 1                                            | י2             | 1 | 2 <sup>9</sup>  |   | 1 | 217             |

| 0                                            | 2 <sup>0</sup> | 0 | 2 <sup>8</sup>  | I | 0 | 216             |

#### 05 DMA CNTRL (W)

7 RESERVED 6 RESERVED 5 RESERVED 4 RESERVED RESERVED 3 ODD XFER START 2 1 TRANSFER DIR 0 DMA XFER EN

- 07 CONTROL REG 0 (W)

- P MEM CYCLE REQ 7

- P MEM R/W 6

- 5 TARGET MODE

- 4 EN PORT A INP OR OUT

- 3 SCSI INTERFACE MODE

- 2 SCSI ID 2

- 1 SCSLID 1

- SCSI ID 0 Ω

#### 09 SCSI SIGNAL REG (W)

| 7 | SCSI C/D OUT        |

|---|---------------------|

| 6 | SCSI I/O OUT        |

| 5 | SCSI MSG OUT        |

| 4 | SCSI ATN OUT        |

| 3 | SCSI SEL OUT        |

| 2 | SCSI BSY OUT        |

| 1 | SCSI ACK OUT (INIT) |

|   |                     |

- SCSI REQ OUT (TGT) 1

- 0 RESERVED

| OD PORT | A | (R/W) |

|---------|---|-------|

|         |   |       |

| 7 | PORT A BIT 7/IBV |

|---|------------------|

| 6 |                  |

| 5 | PORT A BIT 5     |

| 4 | PORT A BIT 4     |

| 3 | PORT A BIT 3     |

| 2 | PORT A BIT 2/HBV |

| 1 | PORT A BIT 1     |

| 0 | PORT A BIT O     |

| 4<br>3<br>2<br>1<br>0 | EN ERROR INT<br>EN CMD DONE INT<br>EN SEL OUT INT<br>EN RESEL INT<br>EN SELECT INT |

|-----------------------|------------------------------------------------------------------------------------|

| 06                    | REV CNTRL (R)                                                                      |

| 4<br>3                | RESERVED<br>RESERVED<br>RESERVED<br>RESERVED<br>RESERVED<br>REVISION<br>REVISION   |

| 08                    | STATUS REG 1 (R)                                                                   |

| 7<br>6                | MEM CYCLE CMPL<br>RESERVED                                                         |

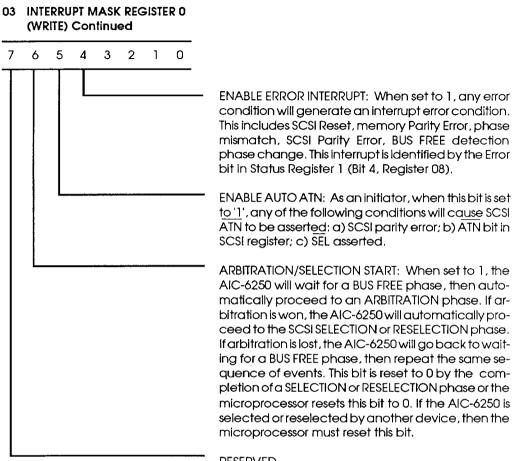

03 INT MSK REG (W)

7 RESERVED 6 ARB/SEL START 5 EN AUTO ATN

SCSI RST IN 5 4 ERROR CMD DONE 3 2 SEL OUT RESELECTED SELECTED Ω

1

7

#### OA SCSI ID DATA (R/W) SCSI ID/DATA 7 SCSI ID/DATA 6 6 5 SCSI ID/DATA 5 SCSI ID/DATA 4 4 3 SCSI ID/DATA 3 2 SCSI ID/DATA 2 1 SCSI ID/DATA 1 Ω SCSI ID/DATA 0

OE PORT B (R/W) 7 PORT B BIT 7 7 PORT B BIT 6 6 6 PORT B BIT 5 5 5 PORT B BIT 4 4 4 3 PORT B BIT 3 3 PORT B BIT 2 2 2

PORT B BIT 1

PORT B BIT 0

1

0

| 04 OFFSET CNTRL (W)                                                                                                                                                                                                                                                                               | 05 FIFO STATUS (R)                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>7 RESERVED</li> <li>6 SYNC XFER RATE BIT 2</li> <li>5 SYNC XFER RATE BIT 1</li> <li>4 SYNC XFER RATE BIT 0</li> <li>3 OFFSET BIT 3</li> <li>2 OFFSET BIT 2</li> <li>1 OFFSET BIT 1</li> <li>0 OFFSET BIT 0</li> </ul>                                                                    | <ul> <li>7 TEST SIGNAL</li> <li>6 TEST SIGNAL</li> <li>5 OFFSET COUNT ZERO</li> <li>4 FIFO EMPTY</li> <li>3 FIFO FULL</li> <li>2 FIFO COUNTER BIT 2</li> <li>1 FIFO COUNTER BIT 1</li> <li>0 FIFO COUNTER BIT 0</li> </ul>                 |

| 06 INT MSK REG 1 (W)                                                                                                                                                                                                                                                                              | 07 STATUS REG 0 (R)                                                                                                                                                                                                                        |

| <ul> <li>7 RESERVED</li> <li>6 EN SCSI REQ ON INT</li> <li>5 EN SCSI RST INT</li> <li>4 EN MEM PARITY ERR INT</li> <li>3 EN PHASE MISMATCH INT</li> <li>2 EN BUS FREE DETECT INT</li> <li>1 EN SCSI PARITY ERR INT</li> <li>0 EN PHASE CHANGE INT(INIT)</li> <li>0 EN ATN ON INT (TGT)</li> </ul> | <ul> <li>7 SCSI RST OCCURRED</li> <li>6 MEMORY PARITY ERR</li> <li>5 PHASE MISMATCH ERR</li> <li>4 BUS FREE DETECT</li> <li>3 SCSI PARITY ERR</li> <li>2 SCSI REQ ON</li> <li>1 SCSI PHASE CHG/ATN</li> <li>0 DMA BYTE CNT ZERO</li> </ul> |

| 08 CONTROL REG 1 (W)                                                                                                                                                                                                                                                                              | 09 SCSI SIGNAL REG (R)                                                                                                                                                                                                                     |

| <ul> <li>AUTO SCSI PIO REQ</li> <li>EN 16-BIT MEM BUS</li> <li>RESERVED (0' ONLY)</li> <li>EN PORT B INP OR OUT</li> <li>PHASE CHANGE MODE</li> <li>CLK FREQ MODE</li> <li>SCSI RST OUT</li> <li>CHIP S/W RESET</li> </ul>                                                                        | 7 SCSI C/D IN<br>6 SCSI I/O IN<br>5 SCSI MSG IN<br>4 SCSI ATN IN<br>3 SCSI SEL IN<br>2 SCSI BSY IN<br>1 SCSI REQ IN<br>0 SCSI ACK IN                                                                                                       |

| OB SOURCE/DEST ID (R)                                                                                                                                                                                                                                                                             | OC MEMORY DATA (R/W)                                                                                                                                                                                                                       |

| 7 ID 7<br>6 ID 6<br>5 ID 5<br>4 ID 4<br>3 ID 3<br>2 ID 2<br>1 ID 1<br>0 ID 0                                                                                                                                                                                                                      | <ul> <li>7 MEM DATA 7</li> <li>6 MEM DATA 6</li> <li>5 MEM DATA 5</li> <li>4 MEM DATA 4</li> <li>3 MEM DATA 3</li> <li>2 MEM DATA 2</li> <li>1 MEM DATA 1</li> <li>0 MEM DATA 0</li> </ul>                                                 |

| OF SCSI LATCH DATA (R)                                                                                                                                                                                                                                                                            | OF SCSI BSY RST (TGT) (W)                                                                                                                                                                                                                  |

| 7 SCSI LATCHED DATA 7                                                                                                                                                                                                                                                                             | FOR A TARGET, A WRITE TO                                                                                                                                                                                                                   |

SCSI LATCHED DATA 6

SCSI LATCHED DATA 5

SCSI LATCHED DATA 4

SCSI LATCHED DATA 3

SCSI LATCHED DATA 2

SCSI LATCHED DATA 1

SCSI LATCHED DATA 0

1

0

FOR A TARGET, A WRITE TO THIS REGISTER WILL RESET THE SCSI BSY OUT AND THE SCSI BUS WILL ENTER A BUS FREE PHASE.

#### Internal Register Descriptions

#### 00 DMA BYTE COUNT, LOW (READ/WRITE)

READ: DMA Byte Count, low-order byte. WRITE: DMA Byte Count, low-order byte.

#### 01 DMA BYTE COUNT, MIDDLE (READ/WRITE)

READ: DMA Byte Count, middle byte. WRITE: DMA Byte Count, middle byte.

#### 02 DMA BYTE COUNT, HIGH (READ/WRITE)

READ: DMA Byte Count, high-order byte. WRITE: DMA Byte Count, high-order byte.

Registers 0-2 determine the number of bytes to be transferred during SCSI data transfer (synchronous or asynchronous) when the DMA Transfer method is used. The DMA Byte Count is decremented by one after each byte of data is transferred on the SCSI bus. By decrementing this counter when a byte is transferred on the SCSI bus, there is no need to determine the number of bytes remaining in the FIFO when a transfer is abnormally terminated. The SCSI bus data transfer will be terminated when the value of Registers 0-2 is zero. The 24-bit counter allows data transfers up to 16 Mbytes without a DMA wrap.

All three registers should be loaded for each DMA operation. The higher-order registers should be loaded with zeros if needed to ensure there is not a residual value from the last operation.

To speed data transfer, the AIC-6250 uses memory prefetch. During a transfer from memory to the SCSI bus, this means the DMA Address Pointer and the DMA Byte Counter in the DMA chip will be incremented when the data is transferred from memory, before the actual SCSI bus data transfer takes place. When SCSI bus data transfer is abnormally terminated, Registers 0-2 will contain the count of the bytes which have not been transferred across the SCSI bus. In this event, the correct value of the DMA controllers Address Pointer must be calculated from the original pointer and the remining byte count in the DMA Byte Count Registers, to restore the number of bytes which have yet to be transferred on the SCSI bus.

Through special logic, the AIC-6250 will stop the memory prefetch when the number of bytes in the FIFO, plus the number of bytes already transferred on the SCSI bus, sums to the total transfer length. This prevents the prefetch from requesting too many bytes from memory.

### **Detailed Register Descriptions**

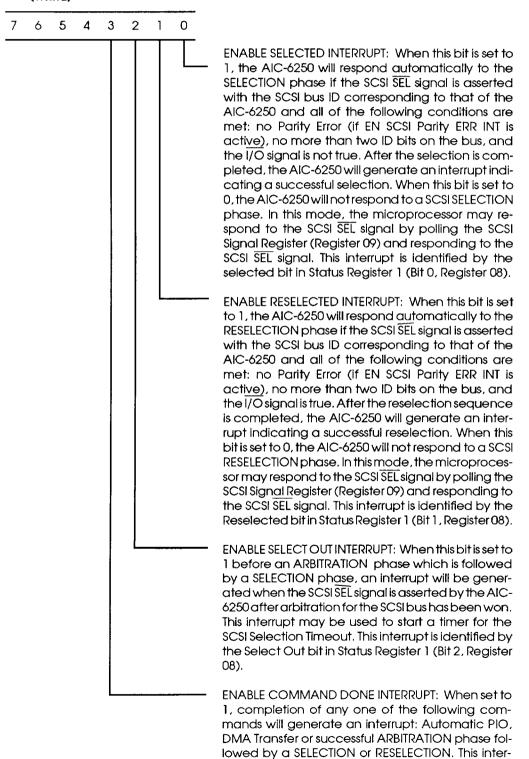

#### 03 INTERRUPT MASK REGISTER 0 (WRITE)

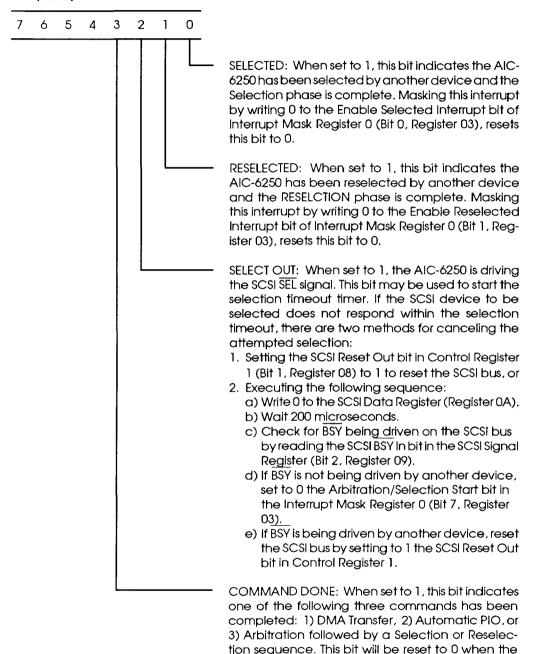

ruptisidentified by the Command Done bit in Status

Register 1 (Bit 3, Register 08).

RESERVED.

Writing a zero to Bits 0 and 1 of this register will reset the selected or reselected interrupt status in Status Register 1 (Register 08), causing the interrupt status to be lost. Therefore, after the interrupt signal to the microprocessor is asserted, the microprocessor must first read Status Register 1 (Register 08) to get the interrupt status before writing to this register.

Both Bits 0 and 1 may be set to 1, enabling the AIC-6250 to respond to either a selection or a reselection.

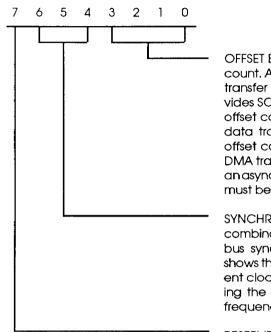

04 OFFSET COUNTER (WRITE ONLY)

OFFSET BITS: These bits set the DMA transfer offset count. An offset count of zero allows asynchronous transfer only. An offset count of one to eight provides SCSI bus synchronous transfer. The maximum offset count is eight. In initiator mode for inbound data transfer, the maximum offset is seven. The offset count must always be set before using the DMA transfer method. Therefore, when performing an asynchronous DMA of information, the offset bits must be set to 0.

SYNCHRONOUS TRANSFER RATE BITS: These bits, in combination with the clock frequency, set the SCSI bus synchronous transfer rate. The table below shows the synchronous transfer rate for three different clock frequencies. The equation for determining the synchronous transfer rate for other clock frequencies is also shown below.

RESERVED.

| SYNCHRONOUS TRANSFER RATE | C<br>20 MHz | LOCK FREQUENC<br>10 MHz | Y<br>5 MHz |

|---------------------------|-------------|-------------------------|------------|

| 000                       | 5.00 MB/s   | 2.50 MB/s               | 1.25 MB/s  |

| 001                       | 4.00 MB/s   | 2.00 MB/s               | 1.00 MB/s  |

| 010                       | 3.33 MB/s   | 1.67 MB/s               | 833 KB/s   |

| 011                       | 2.86 MB/s   | 1.43 MB/s               | 714 KB/s   |

| 100                       | 2.50 MB/s   | 1.25 MB/s               | 625 KB/s   |

| 101                       | 2.22 MB/s   | 1.11 MB/s               | 556 KB/s   |

| 110                       | 2.00 MB/s   | 1.00 MB/s               | 500 KB/s   |

| 111                       | 1.82 MB/s   | 909 KB/s                | 455 KB/s   |

#### EQUATION FOR DETERMINING THE SYNCHRONOUS TRANSFER RATE:

T = Period of Clock Synchronous Speed = (4 \* T) + (Synchronous Transfer Rate \* T)

#### EXAMPLE:

20 MHz Clock Rate (T = 50 ns), Transfer Rate Bits = 7 Synchronous Speed = (4 \* 50 ns) + (7 \* 50 ns) = 200 ns + 350 ns = 550 ns/byte = 1.82 Mbytes/second

NOTE: This register is valid only when BREQ, BACK, REQ and ACK are active.

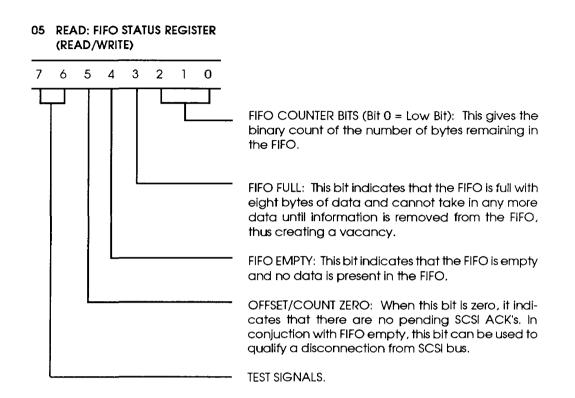

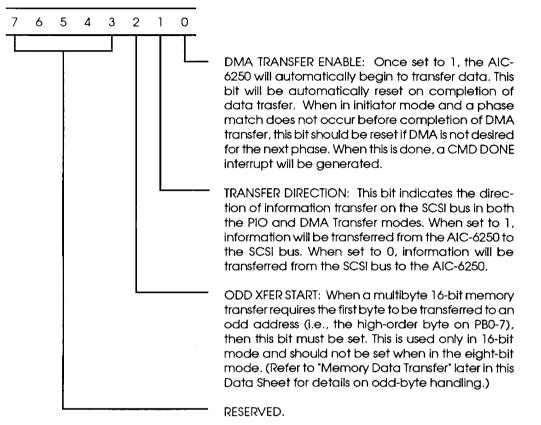

05 WRITE: DMA CONTROL REGISTER (READ/WRITE)

The microprocessor may set Bits 0 and 1 simultaneously since the AIC-6250 will automatically delay the DMA Transfer Enable until the transfer direction is first set internal to the chip.

The microprocessor may set Bit 2 along with Bits 0 and 1 in the same instruction anytime except when in the Initiator mode for data transfers from <u>SCSI. In such a case</u>, this bit must be set prior to target changing the SCSI bus signals (C/D, I/O, MSG) to the DATA IN phase.

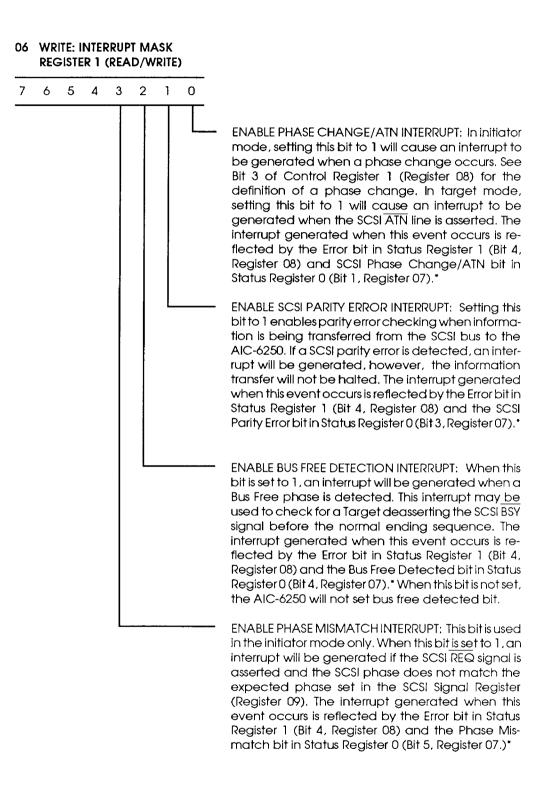

<sup>\*</sup>Denotes a secondary interrupt mask bit. The primary interrupt mask is the Enable Error Interrupt bit in Interrupt Mask Resiger 0 (Bit 4, Register 03).

06 WRITE: INTERRUPT MASK REGISTER 1 (READ/WRITE) Continued

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---|----------|---|---|---|---|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |          |   |   |   |   |   |   | ENABLE MEMORY PARITY ERROR INTERRUPT: When<br>this bit is set to 1, Memory Parity Error Checking is<br>enabled. When using the 16-bit bus mode, memory<br>Parity Checking will be enabled on both the high<br>byte (POR B bus) and the low byte (memory data<br>bus). When a Parity Error is detected, an interrupt<br>will be generated and information transfer halted.<br>The interrupt generated when this event occurs is<br>reflected by the Error bit in Status Register 1 (Bit 4,<br>Register 08) and the Memory Parity Error bit in Status<br>Register 0 (Bit 6, Register 07).*                                                                                                                                                                                                                                                                                                                                                                   |

|   |          | L |   |   |   |   |   | ENABLE SCSI RESET OCCURRENCE INTERRUPT: When<br>set to 1, an interrupt will be generated when a SCSI<br>RST condition occurs. A SCSI Reset must be of at<br>least 500 ns in duration. The SCSI RST signal will be<br>latched in the SCSI RST Occurred bit in Status Reg-<br>ister 0 (Bit 7, Register 07) and may be cleared only<br>by setting to 1 the Chip Software Reset bit in Control<br>Register 1 (Bit 0, Register 08) or a POR (Power On<br>Reset, pin 24). The SCSI RST signal will also be set to<br>1 on the SCSI Reset In bit in Status Register 1 (Bit 5,<br>Register 08), but is not latched in this bit. This bit may<br>be used to determine when the SCSI RST signal is de-<br>asserted and chip initialization may begin. The<br>interrupt generated when this event occurs is re-<br>flected by the Error bit in Status Register 1 (Bit 4,<br>Register 08) and the SCSI RST Occurred bit in Status<br>Register 0 (Bit 7, Register 07).* |

|   | <b>L</b> |   |   |   |   |   |   | ENABLE SCSI REQ ON INTERRUPT: This bit is used in<br>the initiator mode when the transfer method is<br>Microprocessor Controlled PIO. When set to 1, this<br>bit causes an interrupt to be generated when the<br>SCSI REQ signal is asserted. The interrupt generated<br>when this superior is the SCSI PEO On bit in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

when this event occurs is the SCSI REQ On bit in

Status Register 0 (Bit 2, Register 07).

<sup>\*</sup>Denotes a secondary interrupt mask bit. The primary interrupt mask is the Enable Error Interrupt bit in Interrupt Mask Resiger 0 (Bit 4, Register 03).

| 06 | REG |   | R 1 ( | RRUPT MASK<br>(READ/WRITE) |   |   |   | _ |          |

|----|-----|---|-------|----------------------------|---|---|---|---|----------|

| 7  | 6   | 5 | 4     | 3                          | 2 | 1 | 0 | _ |          |

|    |     |   |       |                            |   |   |   |   | RESERVED |

If Bits 0-6 of this register are not set to enable interrupts on the individual events, the microprocessor may poll Status Register 0 (Register 07) to detect the occurrence of the event.

#### 06 READ: REVISION CONTROL REGISTER (READ/WRITE)

When this register is read by the microprocessor, it gives the revision of the chip and should be "1 0"

RESERVED (All zero).

07 READ: STATUS REGISTER 0 (READ/WRITE)

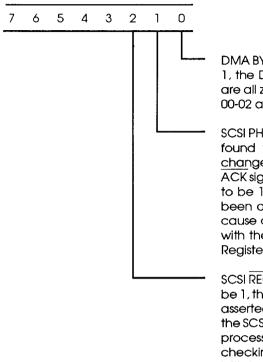

DMA BYTE COUNT ZERO: When this bit is found to be 1, the DMA Byte Count Registers (Registers 00-02) are all zero. This bit will be reset to 0 when Registers 00-02 are loaded with a new transfer count.

SCSI PHASE CHANGE/ATN: In initiator mode, when found to be 1, this bit indicates a SCSI phase <u>change</u> has occurred. This bit is reset when SCSI ACK signal is asserted. In target mode, when found to be 1, this bit indicates the SCSI ATN signal has been asserted. This bit is set to reflect the actual cause of the error when an interrupt is generated with the Error bit set in the Status Register 1 (Bit 4, Register 08).

SCSI REQ ON: In the initiator mode, when found to be 1, this bit indicates the SCSI REQ signal has been asserted. If the initiator wants to start transfer after the SCSI phase has been determined, or use Microprocessor Controlled PIO, this bit may be used for checking the SCSI REQ signal. In this way, if the initiator wishes to wait for REQ to be set to 1, then check the SCSI phase through the SCSI Signal Register (Register 09), this bit would indicate that the SCSI REQ signal has been asserted. The microprocessormay then perform the Phase Check and/ or the Microprocessor Controlled PIO Transfer. This bit is reset to 0 when the SCSI ACK signal is asserted (Bit 3, Register 08). This bit is not used in target mode.

| 7 6 5 | 5 4 | 3 | 2 | 1 | 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----|---|---|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     | T |   |   |   | SCSI PARITY ERROR: If this bit is found to be 1 durin<br>a transfer from the SCSI bus to the AIC-6250 (ir<br>bound), a Parity Error has been detected. This b<br>can be reset by disabling the SCSI Parity Error Inter<br>rupt in Interrupt Mask Register 1 (Bit 1, Register 06)<br>When a Parity Error is detected, and this interrupt<br>enabled, the INT signal (pin 57) is asserted, this bit<br>set, and the Error bit in Status Register 1 (Bit 4<br>Register 08) is set to 1. In the initiator mode, informa-<br>tion transfer will continue. If AUTO ATN (Reg 03, Bit 4<br>is on, SCSI ATN will be asserted and the Initiator mode<br>communicate with the target through the SC<br>message system. To reset parity error, the Initiator<br>must reset to 0 the Enable SCSI Parity Error Interrup<br>in Interrupt Mask Register 1 (Bit 1, Register 06). In the<br>target mode, the target is driving the SCSI but<br>control lines, so the target may terminate the tran-<br>fer and return error status to the host. Or, the target<br>may ask the host to retry the transfer via the SC<br>message system. This bit will be reset to 0 when the<br>Enable SCSI Parity Error Interrupt Mas<br>Register 1 (Bit 1, Register 06) is set to 0. |

|       |     |   |   |   |   | BUS FREE DETECTED: When this bit is found to be 1<br>SCSI BUS FREE phase has been detected. This bit w<br>be reset to 0 when the Enable Bus Free Detection<br>Interrupt in the Interrupt Mask Register 1 (Bit 2<br>Register 06) is masked out by setting to 0. When th<br>bit is found to be set to 1, the Error bit in Statu<br>Register 1 (Bit 4, Register 08) will be set as the primar<br>interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |     |   |   |   |   | PHASE MISMATCH: In the initiator mode, if this bit is<br>found to be 1, it indicates the SCSI REQ signal has<br>been asserted and the SCSI phase did not match<br>the expected phase in the SCSI Signal Register<br>(Register 09). This bit may also be used for the<br>detection of early termination during data transfer<br>This bit will be reset to 0 when the microprocesso<br>writes a new, expected phase to the SCSI Signal<br>Register (Register 09) which matches the actual<br>SCSI bus phase. When this bit is found to be 1, the<br>Error bit in Status Register 1 (Bit 4, Register 08) will be<br>set as the primary interrupt. In the Target mode, this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

bit is not used.

07 READ: STATUS REGISTER 0 (READ/WRITE) Continued

7 6 5 4 3 2 1 0

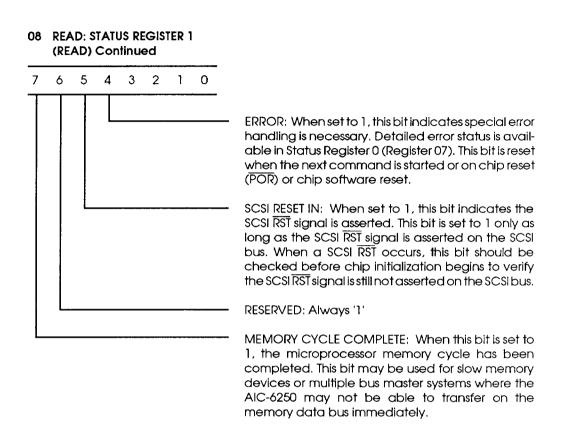

MEMORY PARITY ERROR: When this bit is found to be 1, a parity error on transfer from memory to the AIC-6250 has been detected. When a parity error is detected, information transfer is immediately halted, the INT signal (pin 57) is asserted, this bit is set, and the Error bit in Status Register 1 (Bit 4, Register 08) is set. This bit is reset, and information transfer continued, by disabling the Memory Parity Error Interrupt in the Interrupt Mask Register 1 (Bit 4, Register 06). After disabling the Memory Parity Error Interrupt, the interrupt may be re-enabled again at any time.

SCSI RST OCCURRED: When found to be 1, a SCSI Reset condition has occurred. A SCSI Reset condition is defined as the SCSI RST line being asserted for a minimum of 500 ns. When the SCSI bus Reset is detected, the Reset condition is latched in this bit, the INT signal (pin 57) is asserted, this bit is set to 1, the Error bit in Status Register 1 (Bit 4, Register 08) is set, and all SCSI signals are deasserted. To determine if the Reset signal has been deasserted, the microprocessor must read the SCSI Reset In bit in Status Register 1 (Bit 5, Register 08). This bit is reset by a Chip Software Reset in Control Register 1 (Bit 0, Register 08) or a Power On Reset, pin 24.

Bits 1 and 3-5 of this register are secondary interrupts, enabled through interrupt Mask Register 1 (Register 06). If error interrupt is not enabled, the microprocessor may still obtain the error information by reading this register.

| 07 | WRITE: CONTROL REGISTER 0<br>(READ/WRITE) |                                                                                                                                                                                                                                                                                                     |

|----|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  |                                           | SCSI ID: These bits are the AIC-6250's decoded SCSI<br>ID. The following is a list of the binary and equivalent<br>decimal ID values:                                                                                                                                                               |

|    |                                           | 000 = 0 $100 = 4$ $001 = 1$ $101 = 5$ $010 = 2$ $110 = 6$ $011 = 3$ $111 = 7$                                                                                                                                                                                                                       |

|    |                                           | SCSI INTERFACE MODE: When set to 0, the AIC-6250<br>is in the SCSI single-ended interface mode. When<br>set to 1, the AIC-6250 is in the SCSI differential<br>interface mode.                                                                                                                       |

|    |                                           | ENABLE PORTA INPUTOR OUTPUT: When this bit is set to 1, Port A is an eight-bit output port. When this bit is set to 0, Port A is an 8-bit input port.                                                                                                                                               |

|    |                                           | TARGET MODE: When this bit is set to 1 before<br>Arbitration begins, the AIC-6250 will enter the SCSI<br>Reselection phase if arbitration is won. If this bit is not<br>set, the AIC-6250 will proceed automatically from<br>the ARBITRATION phase to the SELECTION phase if<br>arbitration is won. |

|    |                                           | PROCESSOR MEMORY READ/WRITE: This bit deter-<br>mines the direction of transfer when the micropro-<br>cessor accesses memory through the AIC-6250.<br>When set to 1, a write cycle will occur. When set to<br>0, a read cycle will occur.                                                           |

|    |                                           | PROCESSOR MEMORY CYCLE REQUEST: When<br>there is no DMA activity, this bit can be set to<br>request a memory cycle. This bit is automatically<br>reset after the memory cycle is completed. When<br>DMA is in process, the microprocessor cannot                                                    |

access memory through the AIC-6250.

08 READ: STATUS REGISTER 1 (READ)

is set to zero.

Enable Command Done Interrupt bit (Reg 03, Bit 3)

Bits 0,1 and 3 of this register must be read before writing a zero to Bits 0 and 1 of Interrupt Mask Register 1 (Register 03) since masking the interrupts will reset Bits 0 and 1 in this register and cause the interrupt status to be lost.

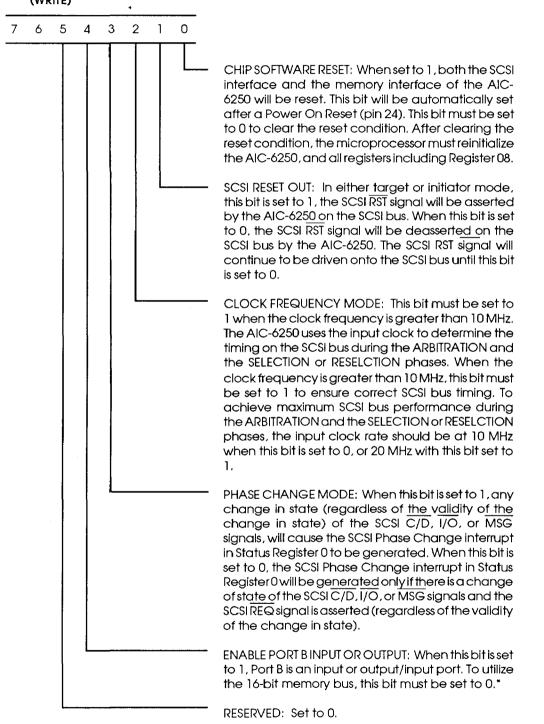

08 WRITE: CONTROL REGISTER 1 (WRITE)

<sup>\*</sup>For more information on Port A and Port B, see Table 2.

| 6 | 5 | 4   | 3     | 2       | 1         | 0           |

|---|---|-----|-------|---------|-----------|-------------|

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   |   |     |       |         |           |             |

|   | 6 | 6 5 | 6 5 4 | 6 5 4 3 | 6 5 4 3 2 | 6 5 4 3 2 1 |

OR WRITE CONTROL REGISTER 1

ENABLE 16-BIT MEMORY BUS: When set to 1, Port B is used as the high byte for the 16-bit memory bus. This bit has priority over Bit 4 of this register. Therefore, setting this bit to 1 will enable the 16-bit memory bus and prevent the Port B output port from being enabled. Also, Port A, Bits 2 and 7, become HBV and LBV, respectively, and are enabled as outputs, regardless of the state of Port A Output Enable. These help in odd-byte handling on DMA Transfers to memory. For more details, refer to the section entitled "Memory Data Transfer" later in this data sheet.

AUTOMATIC SCSI PIO REQUEST: When this bit is set to 1, an automatic SCSI handshake is performed. This bit is reset after the handshake is completed. Automatic PIO requires the microprocessor to read/ write data from the SCSI Data Register. Using this method of transfer, the Command Done Interrupt in Status Register 1 (Bit 3, Register 08) will be generated after each handshake is completed on the SCSI bus. If the SCSI phase does not match the phase set up in Register 09, then the microprocessor should reset this bit and start again.

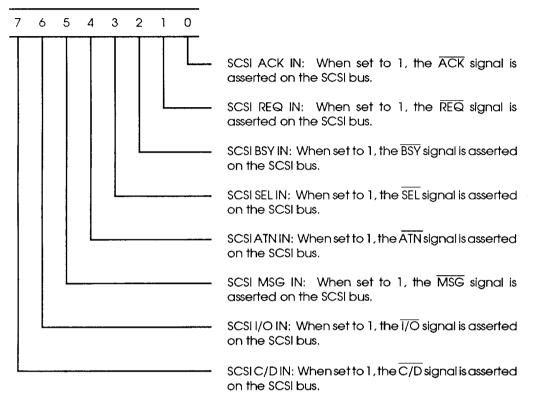

09 SCSI SIGNAL REGISTER (READ ONLY)