#### Distinguishing Features

- 250 MHz Operation

- Differential ECL Clock

Generation

- Ability to Divide by 3, 4, 5, or 8 of the Clock

- Ability to Divide by 2 and 4 of the Load

- Ability to Reset Pipeline Delay of the RAMDAC

- 1.2 V Voltage Reference Output

- Single +5 V Power Supply

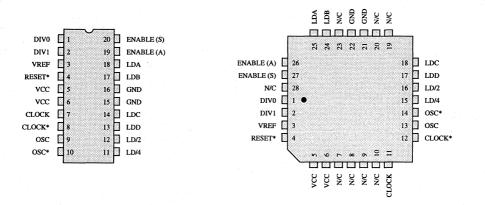

- 20-pin DIP or 28-pin PLCC Package

- Typical Power Dissipation: 325 mW

L438001 Rev. M

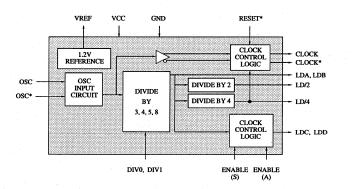

#### **Functional Block Diagram**

Brooktree Corporation • 9950 Barnes Canyon Rd. • San Diego, CA 92121-2790

(619) 452-7580 • (800) VIDEO IC • TLX: 383 596 • FAX: (619) 452-1249

#### **Customer Benefits**

- Reduces PC Board Area

- Simplifies RAMDAC Design

- Reduces Cost over Discretes

- Increases System Reliability

#### **Related Products**

- Bt439

- Bt440

# **Bt438**

250 MHz Clock Generator Chip for CMOS RAMDACs<sup>™</sup>

#### **Product Description**

The Bt438 is a clock generator for the highspeed Brooktree CMOS RAMDACs. It interfaces a 10KH ECL oscillator operating from a single +5 V supply to the RAMDAC, generating the necessary clock and control signals.

The clock output can be divided by 3, 4, 5, or 8 to generate the load signal. The load signal can also be divided by 2 and 4 to, for example, clock video timing logic.

A second load signal may be synchronously or asynchronously controlled to enable starting and stopping the clocking of the video DRAMs.

7

The Bt438 optionally configures the pipeline delay of the RAMDAC to a fixed pipeline delay.

An on-chip 1.2 V voltage reference is also provided, and may be used to provide the reference voltage for up to four RAMDACs.

## **Bt438**

#### **Circuit Description**

The Bt438 is designed to interface to a 10KH ECL crystal oscillator and generate the clock signals required by the RAMDACs. The OSC and OSC\* inputs are designed to interface to a 10KH ECL oscillator operating from a single +5 V power supply.

The CLOCK and CLOCK\* outputs are designed to interface directly to the CLOCK and CLOCK\* inputs of the RAMDACs. The output levels are compatible with 10KH ECL logic operating from a single +5 V power supply.

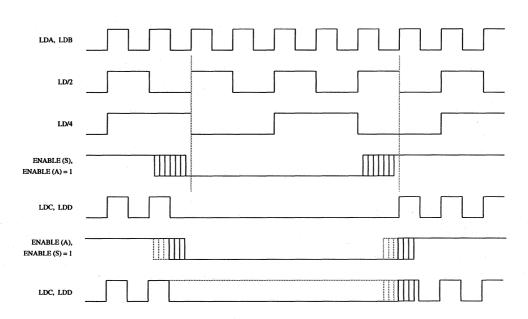

DIV0 and DIV1 are used to specify whether the pixel clock is to be divided by 3, 4, 5, or 8 to generate the LDA and LDB signals. LDA is also divided by 2 and 4 to generate the LD/2 and LD/4 signals, respectively.

ENABLE (S) is internally synchronized to LDA and may be used to synchronously start and stop the LDC and LDD outputs. While ENABLE (S) is a logical zero, LDC and LDD will be logical zeros.

ENABLE (A) is used to asynchronously start and stop the LDC and LDD outputs. While ENA-BLE (A) is a logical zero, the LDC and LDD outputs will remain in the state they were in when the ENABLE (A) input went to a logical zero.

ENABLE (A) and ENABLE (S) should not be a logical zero simultaneously. If this occurs, synchronous control of LDC and LDD by ENABLE (S) is not guaranteed.

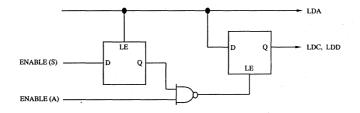

While both ENABLE (S) and ENABLE (A) are logical ones, LDC and LDD will be free running, and in phase with LDA and LDB. This architecture allows the shift registers of the video DRAMs to be optionally nonclocked during the retrace intervals. Figure 1 illustrates the ENABLE implementation within the Bt438, while Figure 2 shows the load output timing.

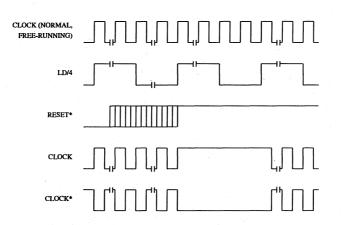

The RESET\* input is designed to enable the Bt438 to set the pipeline delay of the RAMDACs to a specified number of clock cycles. (The exact number depends on the RAMDAC.) Following the first rising edge of LD/4 after the rising edge of RESET\*, the CLOCK and CLOCK\* outputs are stopped in the high and low states, respectively. At the next rising edge of LD/4, the CLOCK and CLOCK\* outputs are restarted. Figure 3 shows the operation of the RESET\* input.

The Bt438 also generates a 1.2 V (typical) voltage reference that may be used to drive the VREF input of up to four RAMDACs.

Figure 1. ENABLE Control Implementation.

### **Circuit Description** (continued)

Figure 2. Load Output Timing.

Figure 3. RESET\* Timing.

## Bt438

7

# Bt438

# Pin Descriptions

| Pin Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                     |                  |                      |                     |                      |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|---------------------|----------------------|--|

| VREF             | Voltage reference output. This output provides a 1.2 V (typical) reference and may be used to drive the VREF input of up to four RAMDACs.                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                     |                  |                      |                     |                      |  |

| OSC, OSC*        | Differential ECL oscillator inputs. These inputs are designed to interface to a 10KH ECL crystal oscillator operating from a single +5 V supply.                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                     |                  |                      |                     |                      |  |

| CLOCK,<br>CLOCK* | Differential clock outputs. These outputs connect directly to the CLOCK and CLOCK* inputs of the RAMDAC. The clock rate is equal to the OSC rate, and these outputs can drive up to four RAMDACs directly. The output levels are equivalent to 10KH ECL logic operating from a single +5 V supply.                                                                                                                                                                              |                                                                                                                                                                     |                  |                      |                     |                      |  |

| DIV0, DIV1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Divide control inputs (TTL compatible). These inputs specify the division factor (3, 4, 5, or 8) for the generation of the LDA and LDB signals, as specified below: |                  |                      |                     |                      |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIV1                                                                                                                                                                | DIVO             | Division<br>Factor   | Clock Cycles<br>Low | Clock Cycles<br>High |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0<br>0<br>1<br>1                                                                                                                                                    | 0<br>1<br>0<br>1 | +3<br>+4<br>+5<br>+8 | 1<br>2<br>2<br>4    | 2<br>2<br>3<br>4     |  |

| LDA, LDB         | Load outputs (TTL compatible). LDA and LDB are generated by dividing CLOCK by 3, 4, 5, or 8, as determined by the DIV0 and DIV1 inputs.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                     |                  |                      |                     |                      |  |

| LD/2             | Load output (TTL compatible). LD/2 is generated by dividing LDA by 2.                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |                  |                      |                     |                      |  |

| LD/4             | Load output (TTL compatible). LD/4 is generated by dividing LDA by 4.                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |                  |                      |                     |                      |  |

| LDC, LDD         | Load outputs (TTL compatible). When both ENABLE inputs are a logical one, these outputs have the same timing as the LDA and LDB outputs.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                     |                  |                      |                     |                      |  |

| ENABLE (S)       | Synchronous load enable control input (TTL compatible). ENABLE (S) is internally syn-<br>chronized to LDA, and is used to synchronously start and stop the LDC and LDD outputs.<br>While ENABLE (S) is a logical zero, LDC and LDD will be logical zeros. While both<br>ENABLE (A) and ENABLE (S) are logical ones, LDC and LDD are free-running and in<br>phase with the LDA and LDB outputs.                                                                                  |                                                                                                                                                                     |                  |                      |                     |                      |  |

| ENABLE (A)       | Asynchronous load enable control input (TTL compatible). ENABLE (A) is used to asynchronously start and stop the LDC and LDD outputs. While ENABLE (A) is a logical zero, the LDC and LDD outputs will remain in the state they were in when the ENABLE (A) input went to a logical zero. While both ENABLE (A) and ENABLE (S) are logical ones, LDC and LDD are free running and in phase with the LDA and LDB outputs. Glitches should be avoided on this asynchronous input. |                                                                                                                                                                     |                  |                      |                     |                      |  |

## Pin Descriptions (continued)

| Pin Name | Description                                                                                                                                                                                                                                                                         |                                           |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| RESET*   | Reset control input (TTL compatible). Following the first rising edge rising edge of RESET*, CLOCK and CLOCK* are stopped in the high a spectively. At the next rising edge of LD/4, the CLOCK and CLOCK* be free running. Glitches should be avoided on this edge-triggered input. | and low states, re-<br>outputs are set to |  |  |  |  |

| VCC      | Device power. All VCC pins must be connected.                                                                                                                                                                                                                                       |                                           |  |  |  |  |

| GND      | Device ground. All GND pins must be connected.                                                                                                                                                                                                                                      |                                           |  |  |  |  |

#### A 28-pin Plastic J-Lead (PLCC) Package

*Note:* N/C pins may be left floating without affecting the performance of the Bt438.

#### **Application Information**

#### Interfacing to the RAMDAC

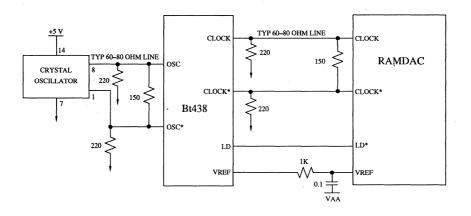

Figure 4 illustrates interfacing the Bt438 to a RAMDAC when using a differential ECL oscillator. The Bt438 should be located as close as possible to the RAMDAC. The 220  $\Omega$  resistors at the oscillator should be located as close as possible to the OSC and OSC\* outputs. The 150  $\Omega$  resistor at the Bt438 should be located as close as possible to the Bt438 should be located as close as possible to the Bt438 SoC and OSC\* inputs.

The 220  $\Omega$  resistors at the Bt438 should be located as close as possible to the Bt438 CLOCK and CLOCK\* outputs. The 150  $\Omega$  resistor at the RAMDAC should be as close as possible to the CLOCK and CLOCK\* inputs.

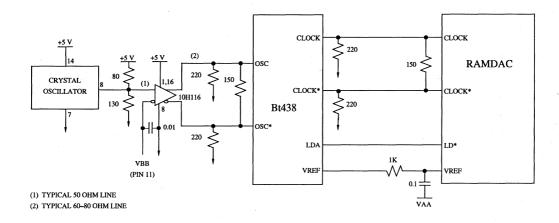

Figure 5 illustrates interfacing to a single-ended ECL oscillator.

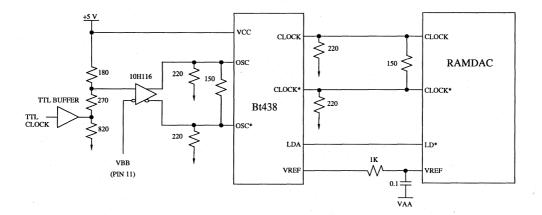

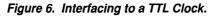

Figure 6 shows interfacing to a TTL clock for applications less than 80 MHz. The +5 V of the resistor divider should be tied directly to the device +5 V. At VCC max, noise margin is at the minimum (100 mV).

Because of the inability to ensure proper synchronization between Bt438s, multiple devices should not be used in applications where multiple RAMDACs drive the same monitor.

A 1 k $\Omega$  resistor must be used to isolate the VREF output between multiple RAMDACs. This keeps noise on the Bt438 voltage reference from being coupled into the RAMDAC's VREF pin. The VREF input of the RAMDAC must still have a decoupling capacitor to VAA or GND, as specified in the RAMDAC's datasheet.

Figure 4. Interfacing to a Differential Crystal Oscillator.

### Application Information (continued)

Figure 5. Interfacing to a Single-Ended Crystal Oscillator.

Bt438

### **Recommended Operating Conditions**

| Parameter                     | Symbol | Min  | Тур  | Max  | Units |

|-------------------------------|--------|------|------|------|-------|

| Power Supply                  | VCC    | 4.75 | 5.00 | 5.25 | v     |

| Ambient Operating Temperature | TA     | 0    |      | +70  | °C    |

| OSC/OSC* Duty Cycle           |        | 40   |      |      | %     |

|                               |        |      |      |      |       |

|                               |        |      |      |      |       |

Thermal equilibrium is established by applying power for at least 2 minutes while maintaining a transverse air flow of 400 linear feet per minute over the device mounted either in the test socket or on the printed circuit board.

#### **Absolute Maximum Ratings**

| Parameter                                                                    | Symbol         | Min      | Тур | Max          | Units    |

|------------------------------------------------------------------------------|----------------|----------|-----|--------------|----------|

| VCC (measured to GND)                                                        |                |          |     | 7.0          | V        |

| Voltage on any Pin                                                           |                | GND-0.5  |     | VCC + 0.5    | v        |

| CLOCK, CLOCK* Output Current                                                 |                |          |     | 30           | mA       |

| Ambient Operating Temperature<br>Storage Temperature<br>Junction Temperature | TA<br>TS<br>TJ | 55<br>65 |     | +125<br>+150 | °C<br>°C |

| Ceramic Package<br>Plastic Package                                           | 13             |          |     | +175<br>+150 | °C<br>°C |

| Soldering Temperature<br>(5 seconds, 1/4" from pin)                          | TSOL           |          |     | 260          | °C       |

| Vapor Phase Soldering<br>(1 minute)                                          | TVSOL          |          |     | 220          | °C       |

| Air Flow                                                                     |                | 0        |     |              | l.f.p.m. |

|                                                                              |                |          |     |              |          |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification isnot implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Characteristics**

| Parameter                                                                                                                                                                                                                 | Symbol                          | Min                          | Тур        | Max                                                      | Units                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|------------|----------------------------------------------------------|-------------------------------|

| TTL Inputs<br>Input High Voltage (general)<br>DIV0, DIV1<br>RESET* (at 0 °C)<br>Input Low Voltage<br>Input High Current (Vin = 2.4 V)<br>Input Low Current (Vin = 0.4 V)<br>Input Capacitance<br>(f = 1 MHz, Vin = 2.4 V) | VIH<br>VIL<br>IIH<br>IIL<br>CIN | 2.0<br>2.2<br>2.2<br>GND-0.5 | 4          | VCC + 0.5<br>VCC + 0.5<br>VCC + 0.5<br>0.8<br>10<br>-0.7 | V<br>V<br>V<br>µA<br>mA<br>pF |

| ECL Inputs<br>Input High Voltage<br>Input Low Voltage<br>Input High Current (Vin = 4.0 V)<br>Input Low Current (Vin = 0.4 V)<br>Input Capacitance<br>(f = 1 MHz, Vin = 4.0 V)                                             | VIH<br>VIL<br>IIH<br>IIL<br>CIN | VCC-1.1<br>GND-0.5           | 4          | VCC-0.8<br>VCC-1.5<br>15<br>15                           | V<br>V<br>μΑ<br>μΑ<br>pF      |

| Load Outputs<br>Output High Voltage<br>(IOH =-2 mA)<br>Output Low Voltage<br>(IOL = 20 mA)<br>Output Capacitance                                                                                                          | VOH<br>VOL                      | 2.4                          | 10         | 0.65                                                     | V<br>V<br>pF                  |

| Clock Outputs<br>Differential Output Voltage<br>Output Capacitance                                                                                                                                                        | ΔVOUT<br>COUT                   | 0.6                          | 7          |                                                          | V<br>pF                       |

| Voltage Reference<br>Output Voltage<br>(Bt438 Rev. C) (Note 1)<br>Output Current                                                                                                                                          | VREF<br>IREF                    | 1.12                         | 1.2<br>100 | 1.27                                                     | V<br>μA                       |

| VCC Supply Current (Note 2)                                                                                                                                                                                               | ICC                             |                              | 65         | 85                                                       | mA                            |

Test conditions (unless otherwise specified): "Recommended Operating Conditions." CLOCK and CLOCK\* have 50  $\Omega$  to VCC-2 V. Typical values are based on nominal temperature, i.e., room temperature, and nominal voltage, i.e., 5 V.

*Note 1:* RSET of the RAMDAC should be adjusted because the output voltage of the Bt438 Rev. C is lower than the recommended VREF for the RAMDAC. IOG (mA) = <u>11294 VREF</u>, IOG (typ) = 26.7 mA.

RSET

Note 2: Measured without 50  $\Omega$  to VCC-2 V on CLOCK and CLOCK\*.

The specified limits shown can be met only after thermal equilibrium has been established. Thermal equilibrium is established by applying power for at least 2 minutes while maintaining a transverse air flow of 400 linear feet per minute over the device mounted either in the test socket or on the printed circuit board.

### Bt438 AC Characteristics

| Parameter                         | Symbol | Min                                   | Тур | Max | Units |

|-----------------------------------|--------|---------------------------------------|-----|-----|-------|

| OSC, OSC* Clock Rate              | Fmax   |                                       |     | 250 | MHz   |

| LDA Output Delay (Note 1)         | 1      | · · · · · · · · · · · · · · · · · · · | 4   | 10  | ns    |

| LDA, LDB Pulse Width Low (Note 2) | 1      | 5                                     |     |     | ns    |

| LDA to LDB Output Skew (Note 3)   |        | -2.0                                  | 0   | 2.0 | ns    |

| LDA to LDC Output Skew (Note 3)   |        | -1.0                                  | 1.5 | 4.0 | ns    |

| LDA to LD/2 Output Skew (Note 3)  |        | 0                                     | 1.5 | 5.0 | ns    |

| LDA to LD/4 Output Skew (Note 3)  |        | 0                                     | 1.5 | 6.0 | ns    |

| LDC to LDD Output Skew (Note 3)   |        | -2.0                                  | 0   | 2.0 | ns    |

| RESET* Active Low Time            | 2      | 15                                    |     | · · | ns    |

| RESET* Setup Time                 | 3      | 12                                    |     |     | ns    |

| ENABLE (S) Setup Time             | 4      | 12                                    |     |     | ns    |

| ENABLE (S) Hold Time              | 5      | -2                                    |     |     | ns    |

| ENABLE (A) Setup Time             | 6      | 12                                    |     | 1   | ns    |

| ENABLE (A) Hold Time              | 7      | -2                                    |     |     | ns    |

Test conditions (unless otherwise specified): "Recommended Operating Conditions". CLOCK and CLOCK\* have 50  $\Omega$  to VCC-2 V. TTL outputs have -2 mA/20 mA load applied with 1.5 V switching point. TTL input values are 0-3 V with input rise/fall times  $\leq$  4 ns, measured between 10-percent and 90-percent points. ECL input values are VCC-1.8 to VCC-0.8 V with input rise/fall times  $\leq$  1 ns, measured between 20-percent and 80-percent points. Timing reference points at 50-percent for inputs and outputs, except TTL outputs measured at 1.5 V. Typical values are based on nominal temperature, i.e., room temperature, and nominal voltage, i.e., 5 V.

*Note 1*: Output load =  $50 \text{ pF}_{\cdot}$

Note 2: LD outputs not used in +3 over 200 MHz.

Note 3: LD outputs equally loaded. Unequal loading may result in additional output skew.

# Brooktree® Timing Waveforms

Input/Output Timing

## **Ordering Information**

| Model Number | Package                  | Ambient<br>Temperature<br>Range |  |

|--------------|--------------------------|---------------------------------|--|

| Bt438KC      | 20-pin 0.3"<br>CERDIP    | 0° to +70° C                    |  |

| Bt438KPJ     | 28-pin Plastic<br>J-Lead | 0° to +70° C                    |  |