#### 82C455 VGA FLAT PANEL/CRT CONTROLLER DATA SHEET

- VGA-Compatible flat panel controller optimized for laptop computer applications.

- Supports CRT, LCD, Plasma and Electro-Luminescent displays of varying resolutions.

- Single chip implementation tightly couples to the CHIPS/250 and CHIPS/280 and interfaces with 8 and 16 bit PC bus and MCA (an interface compatible with the MicroChannel™).

The 82C455 Graphics Controller provides a complete solution for implementing a Video Graphics Array-compatible controller. The 82C455 is supplied in a 144-pin PFP package. It can be used in 8 and 16-bit PC bus and in 16-bit MCA bus environments.

### **Display Types Supported**

CGA, EGA, MDA, Multifrequency, IBM PS/2™ and other monitors can be used. The choice of flat panel displays includes EL, plasma, as well as single panel/single drive, dual panel/single drive and dual panel/double drive LCDs. Both gray scale and monochrome panels are supported; a proprietary frame rate control algorithm provides gray scale capability on monochrome panels.

#### CHIPS/250 and CHIPS/280 Interface

The 82C455 interfaces directly to the CHIPS/250 and CHIPS/280, providing a simple, cost-effec-

- Up to 40 MHz dot clock speed for graphics and text modes.

- Can utilize an external palette DAC with up to 16 million colors.

- Provides intelligent backward compatibility to the EGA, CGA, Hercules™, and MDA on Flat Panel displays.

tive solution for PS/2 compatible systems. When used with one of these CHIPSets<sup>®</sup>, the 82C455 can execute FAST memory cycles at a speed greater than that normally available on the MCA bus.

#### **Backward Compatibility**

The 82C455 is compatible with IBM's EGA, CGA and MDA, in addition to offering a Hercules monochrome-graphics-compatible mode. Onchip compensation registers permit software designed for low resolution displays to utilize the entire screen area on a flat panel with higher resolution.

# Hardware Support for Context Switching

Multitasking and windowing environments can be implemented easily since all internal registers of the 82C455 can be read and written.

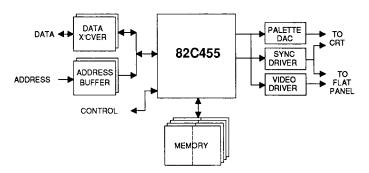

Figure 1: 82C455 System Implementation

#### 82C455 Functional Description

The 82C455 offers a complete solution for implementing a VGA/MCGA/EGA/CGA/MDA/Hercules-compatible display system. By integrating all necessary logic the device ensures that total chip count for a VGA-compatible solution can be as low as 14 chips (includes 82C455, display memory, buffers and drivers).

Any one of a variety of CRT monitors or flat panel displays can be driven. Internal compensation registers ensure that industry-standard software designed for different displays can be executed on the single flat panel used in an implementation. Mode initialization is supported at the BIOS and register levels, ensuring compatibility with all application software. The 256 Kbytes of display memory size is comprised of 8 64K\*4 DRAMs. Display memory refresh is controlled by the 82C455; it is transparent to the CPU.

For support of multitasking environments and context switching, the entire state of the 82C455 (internal registers and latches) is readable and writeable. This feature is 100% compatible to IBM's VGA.

The 82C455 directly interfaces to 8-bit PC and PC/XT, 16-bit PC/AT and 8 or 16-bit MCA buses. All operations necessary to ensure proper operation in these various environments are handled in a fashion transparent to the CPU. These include internal decoding of all memory and I/O addresses, bus width translations and generation of the necessary control signals.

The 82C455 contains 16 color palette registers. It also interfaces directly to an external Inmos G171 (or compatible) color palette and D/A converter. Like the VGA, it is capable of display resolutions of 640\*480 with 16 on-screen colors (internal palette) and 320\*200 with 256 on-screen colors from an external palette of 256 thousand (or 16 million) colors. The 82C455 can also be programmed for higher resolutions up to 800\*600 in 16 colors.

The 82C455 integrates four different modules as follows:

### **Graphics Controller**

The Graphics Controller interfaces the 8 or 16-bit CPU data bus to the 32-bit data bus used by the four planes (Maps) of display memory. It also latches and supplies to the Attribute Controller display memory data for use in refreshing the screen image. For text modes this data is supplied in parallel form (character generator data and an attribute code); for graphics modes it is converted to serial form (one bit from each of four bytes form a single pixel). The Graphics Controller also performs any one of several types of logical operations on data while reading it from or writing it to display memory or the CPU data bus.

#### Sequencer

The Sequencer generates all CPU and display memory timing signals. It controls CPU access of display memory by inserting cycles dedicated to CPU access and contains mask registers which can prevent writes of individual display memory planes.

#### **Attribute Controller**

The Attribute Controller generates the 4-bit-wide video data stream used to refresh the display. This is created in text modes from a font pattern and an attribute code which pass through a parallel to serial conversion. In graphics modes, the display memory contains the 4-bit pixel data. In text and graphic modes the 4-bit pixel data acts as an index into a set of internal palette registers which generate a 6-bit stream. Two additional bits of color data are added if 256-color mode is enabled. Text blink, underline and cursor are also the responsibility of the Attribute Controller.

#### **CRT Controller**

The CRT Controller generates all the sync and timing signals for the display and also generates the multiplexed row and column addresses used for both display refresh and CPU access of display memory.

# **Pin Description Table**

| Flatpack |      |      | *      |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | Name | Type | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

| 63       | AD0  | I/O  | Both   | SYSTEM ADDRESS and DATA Bits 0-15.                                                                                                                                                                                                                                                                                                                                                                                |

| 62       | AD1  | 1/0  | Both   | These bits are used to address display                                                                                                                                                                                                                                                                                                                                                                            |

| 61       | AD2  | I/O  | Both   | memory and the I/O mapped 82C455 inter-                                                                                                                                                                                                                                                                                                                                                                           |

| 60       | AD3  | 1/0  | Both   | nal registers. They also transfer data be-                                                                                                                                                                                                                                                                                                                                                                        |

| 59       | AD4  | 1/0  | Both   | tween the CPU bus and display memory                                                                                                                                                                                                                                                                                                                                                                              |

| 58       | AD5  | I/O  | Both   | and 82C455 registers. Addresses must be                                                                                                                                                                                                                                                                                                                                                                           |

| 57       | AD6  | 1/0  | Both   | valid when output signal DATAEN is low                                                                                                                                                                                                                                                                                                                                                                            |

| 56       | AD7  | I/O  | Both   | and data must be held until \VGACMD                                                                                                                                                                                                                                                                                                                                                                               |

| 53       | AD8  | 1/0  | Both   | (COMMAND) is low. Addresses are latched                                                                                                                                                                                                                                                                                                                                                                           |

| 52       | AD9  | I/O  | Both   | internally.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 51       | AD10 | 1/0  | Both   | •                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 50       | AD11 | I/O  | Both   |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 49       | AD12 | I/O  | Both   |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 48       | AD13 | 1/0  | Both   |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 47       | AD14 | 1/0  | Both   |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 46       | AD15 | 1/0  | Both   |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 44       | A16  |      | Both   | SYSTEM ADDRESS Bits 16-18 and                                                                                                                                                                                                                                                                                                                                                                                     |

| 43       | A17  | 1    | Both   | AUXILIARY DATA Bits 0-2. These bits trans-                                                                                                                                                                                                                                                                                                                                                                        |

| 42       | A18  | 1    | Both   | fer a high-order address when DATAEN is low. The auxiliary data bits on pins A16, A17, and A18 respectively are read into Bits 0-2, respectively, of the DIP Switch register when that register is accessed by the CPU. The address bits are latched internally and are ignored for I/O cycles.                                                                                                                   |

| 72       | \BHE | I    | Low    | BYTE HIGH ENABLE and AUXILIARY DATA Bit. \BHE low indicates that the high order byte at the current word address is being accessed. If active, \BHE must be valid when DATAEN is low. The pin is also an auxiliary data input which is read into Bit 3 of the DIP Switch register when the DIP Switch register is accessed by the CPU. This data bit is latched internally on the falling edge of \VGACMD (\IOR). |

| Flatpack |        | Turna | Activo         | Decarintian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | ADDHI  | Type  | Active<br>High | Description  ADDRESS HI and AUXILIARY DATA Bit. This high order memory address enable input is generated external to the 82C455 by decoding system addresses A19-A23. As an address, it must be valid when DATAEN is low, is latched internally and specifies that the current memory address is valid for the 82C455. This pin is an auxiliary data bit read into Bit 4 of the DIP Switch register when the DIP Switch register is accessed by the CPU. This input pin is ignored during I/O cycles. |

| 67       | DATAEN | 0     | High           | DATA ENABLE. The DATAEN output controls external multiplexing of the system address/data bus. DATAEN low selects address and DATAEN high selects data. In an MCA interface, DATAEN is low when \VGACMD is high and DATAEN is high when \VGACMD is low. In a PC or PC/AT bus interface, DATAEN is low when all \MEMR, \MEMW, \IOR, and \IOW are high. DATAEN is high when any one of \MEMR, \MEMW, \IOR or \IOW is low.                                                                                |

| 65       | \RDLO  | 0     | Low            | READ LO. This output controls the direction of the external data transceivers on the low order byte (Bits 0-7) of the address/data bus. It is low when data is read from the 82C455 and high when data is written to 82C455. DATAEN can be used to enable the external transceiver.                                                                                                                                                                                                                   |

| 64       | \RDHI  | 0     | Low            | READ HI. This output operates in a fashion identically to the \RDLO output except that it controls direction for the high order byte (Bits 8-15) of the address/data bus. RDHI is low when data is read from 82C455 and high when data is written to 82C455.                                                                                                                                                                                                                                          |

4

| Flatpack<br>Pin No. | Name                | Typo | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------|---------------------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 71                  | M/IO<br>(AEN)       | Type | Both   | MEMORY/IO or ADDRESS ENABLE AUXILIARY DATA input. In MCA interfact the MIO input pin selects either a memor an I/O transfer. M/IO high selects a memor cycle and low selects an I/O cycle. Wilder defined as M/IO, it must be valid when DATAEN input is low. In PC-Bus interfact this input is renamed AEN. When low, it is cates a valid I/O address when DATAEI low. The M/IO (AEN) signal is latched in nally. In both MCA and PC-Bus environmenthis pin serves as an auxiliary data bit in It is read into Bit 5 of the DIP Switch regist whenever the DIP Switch register is cessed by the CPU. |  |  |

| 69                  | \S0<br>(\MEMW)      | I    | Low    | S0 or MEMORY WRITE. \S0 is the memory and I/O write input from the MCA bus. In PC-Bus interface applications, this input is named \MEMW. It must be low for CPU writes to display memory.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 70                  | \S1<br>(\MEMR)      | I    | Low    | S1 or MEMORY READ. \S1 is the memory and I/O read input from the MCA bus. In PC-Bus interface applications, this input is named \MEMR. It must be low to permit the CPU to read display memory.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 79                  | \VGASETUP<br>(\IOW) | I    | Low    | VGA SETUP or I/O WRITE. In an MCA environment this active low \VGASETUP input allows configuration registers at I/O Addresses 100-104h to be accessed. All other memory and I/O functions are disabled. In PC-BUS interface applications, this input is named \IOW. It must be low to permit the CPU to write to an 82C455 I/O register.                                                                                                                                                                                                                                                              |  |  |

| 68                  | \VGACMD<br>(\IOR)   | ı    | Low    | VGA COMMAND or I/O READ. In an MCA environment this active low \VGACMD indicates a command bus cycle. \VGACMD must not be asserted during system memory refresh cycles. In a PC-Bus environment this input is named \IOR. It must be low to permit the CPU to read an I/O register.                                                                                                                                                                                                                                                                                                                   |  |  |

| Flatpack<br>Pin No. | Name                  | Typo      | Active   | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|-----------------------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80                  | VGAENAB<br>(\REFRESH) | Type<br>I | High/Low | Description  VGA ENABLE or REFRESH and AUXILIARY DATA. In an MCA environment this active high VGAENAB input signal enables memory and I/O accesses. In the PC-Bus interface, REFRESH high indicates a valid memory cycle. This pin also serves as an auxiliary data bit input which is read into Bit 6 of the DIP Switch register whenever the DIP Switch register is accessed by the CPU.            |

| 78                  | (VGAREQ<br>(VIOCS16)  | 0         | Low      | VGA REQUEST or I/O SELECT 16. In an MCA environment this output indicates that a FAST memory cycle can be executed (this feature can be disabled through a register). In a PC-Bus environment this active low \IOCS16 signal indicates a valid 16 bit I/O cycle.                                                                                                                                      |

| 74                  | VGARDY                | 0         | Low      | VGA READY. When low this output indicates that the current CPU read/write cycle must be extended with wait states.                                                                                                                                                                                                                                                                                    |

| 77                  | \VGADS16<br>(\MEN16)  | 0         | Low      | VGA ADDRESS SELECT 16 or MEMORY ENABLE 16. In an MCA environment this active low \VGADS16 output indicates that a 16-bit memory or I/O transfer cycle is occurring. In a PC-Bus environment this active low \MEN16 signal indicates a 16-bit memory cycle transfer is enabled. This signal should be used in external logic to decode the high order address and generate \MEMCS16 for the PC-AT bus. |

| 75                  | \VGAACK<br>(\WR46E8)  | 0         | Low      | VGA ACKNOWLEDGE or WRITE 46E8h. In an MCA environment this active low VGAACK output indicates a valid CPU access (memory and I/O) to the 82C455. In a PC-Bus environment this active low VWR46E8 signal indicates a valid I/O write to address 46E8h.                                                                                                                                                 |

| 113                 | VGAINT                | 0         | Either   | VGA INTERRUPT. This pin is asserted whenever the vertical sync signal goes active. This pin can be configured to be active high (EGA) or active low (VGA) through the Emulation Mode register (XR14).                                                                                                                                                                                                 |

6

82C455

| Flatpack<br>Pin No. | Name                 | Туре           | Active               | Description                                                                                                                                                                                                |

|---------------------|----------------------|----------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 114                 | RESET                | l I            | High                 | RESET. An active high input which resets the 82C455.                                                                                                                                                       |

| 38                  | TEST                 | 1              | High                 | TEST. This input is used for factory testing only. It should be tied low.                                                                                                                                  |

| 40                  | PWRDN2<br>PWRDN1     | I<br>I         | Both<br>Both         | POWER DOWN 2,1. The POWER DOWN input pins select the Normal, Relax, and Retire modes of operation as follows:  PWRDN2 PWRDN1 OPERATION  0 0 Normal Operation  0 1 Relax Mode  1 0 Retire Mode  1 1 Illegal |

| 105<br>104<br>103   | CLK0<br>CLK1<br>CLK2 | <br> <br> <br> | Both<br>Both<br>Both | CLOCK 2-0. Video Clock inputs. One of these dot clock inputs is selected by the Miscellaneous Output Register.                                                                                             |

| 101                 | MCLK                 | 1              | Both                 | MASTER CLOCK. This clock input is used to sequence internal 16-bit I/O cycles.                                                                                                                             |

| 108                 | SENSE                | 1              | Both                 | SENSE. The state of this input pin can be read in Input Status Register 0, Bit 4.                                                                                                                          |

| 100                 | \PALRD               | 0              | Low                  | PALETTE READ. This output is active low during an I/O read to an address in the range 3C6-3C9h and is connected to the Read input of an external Inmos G171 Palette/DAC.                                   |

| 99                  | \PALWR               | 0              | Low                  | PALETTE WRITE. This output is active low during an I/O write to an address in the range 3C6-3C9h and is connected to the Write input of an external Inmos G171 Palette/DAC.                                |

| 142                 | MODO<br>MOD1         | I/O<br>I/O     | Both<br>Both         | MEMORY 0 DATA. Display memory data bus for Plane 0 (Map 0).                                                                                                                                                |

|                     |                      | 1/0            | Both                 | Sas for Flame o (Map o).                                                                                                                                                                                   |

| 7                   | MOD2                 | 1/0            | Both                 |                                                                                                                                                                                                            |

| 12                  | MOD3                 | 1/0            | Both                 |                                                                                                                                                                                                            |

| 16<br>24            | M0D4<br>M0D5         | 1/0            | Both                 |                                                                                                                                                                                                            |

| 28                  | MODS                 | 1/0            | Both                 |                                                                                                                                                                                                            |

| 33                  | MOD7                 | 1/0            | Both                 |                                                                                                                                                                                                            |

| Flatpack |      | Tuna | Activo | Decarintion                          |

|----------|------|------|--------|--------------------------------------|

| Pin No.  | Name | Туре | Active | Description                          |

| 144      | M1D0 | 1/0  | Both   | MEMORY 1 DATA. Display memory data   |

| 5        | M1D1 | 1/0  | Both   | bus for Plane 1 (Map 1).             |

| 10       | M1D2 | 1/0  | Both   |                                      |

| 14       | M1D3 | 1/0  | Both   |                                      |

| 22       | M1D4 | 1/0  | Both   |                                      |

| 26       | M1D5 | 1/0  | Both   |                                      |

| 31       | M1D6 | I/O  | Both   |                                      |

| 35       | M1D7 | I/O  | Both   |                                      |

| 115      | M2D0 | I/O  | Both   | MEMORY 2 DATA. Display memory data   |

| 118      | M2D1 | 1/0  | Both   | bus for Plane 2 (Map 2).             |

| 120      | M2D2 | 1/0  | Both   | ` ' '                                |

| 122      | M2D3 | 1/0  | Both   |                                      |

| 124      | M2D4 | 1/0  | Both   |                                      |

| 128      | M2D5 | I/O  | Both   |                                      |

| 130      | M2D6 | 1/0  | Both   |                                      |

| 132      | M2D7 | 1/0  | Both   |                                      |

| 116      | M3D0 | 1/0  | Both   | MEMORY 3 DATA. Display memory data   |

| 119      | M3D1 | I/O  | Both   | bus for Plane 3 (Map 3).             |

| 121      | M3D2 | 1/0  | Both   | · · /                                |

| 123      | M3D3 | 1/0  | Both   |                                      |

| 125      | M3D4 | 1/0  | Both   |                                      |

| 129      | M3D5 | 1/0  | Both   |                                      |

| 131      | M3D6 | 1/0  | Both   |                                      |

| 133      | M3D7 | 1/0  | Both   |                                      |

| 143      | AA0  | 0    | Both   | ADDRESS PLANES 0,1. Display memory   |

| 4        | AA1  | 0    | Both   | address bus for DRAM planes 0 and 1. |

| 8        | AA2  | 0    | Both   |                                      |

| 13       | AA3  | 0    | Both   |                                      |

| 21       | AA4  | 0    | Both   |                                      |

| 25       | AA5  | 0    | Both   |                                      |

| 29       | AA6  | 0    | Both   |                                      |

| 34       | AA7  | 0    | Both   |                                      |

| Flatpack<br>Pin No. | Name  | Туре | Active | Description                                                                                                                                                                                                |

|---------------------|-------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |       |      |        |                                                                                                                                                                                                            |

| 141                 | BA0   | 0    | Both   | ADDRESS PLANES 2,3. Display memory address bus for DRAM Planes 2 and 3.                                                                                                                                    |

| 2                   | BA1   | 0    | Both   | address bus for DHAM Planes 2 and 3.                                                                                                                                                                       |

| 6                   | BA2   | 0    | Both   |                                                                                                                                                                                                            |

| 11                  | BA3   | 0    | Both   |                                                                                                                                                                                                            |

| 15                  | BA4   | 0    | Both   |                                                                                                                                                                                                            |

| 23                  | BA5   | 0    | Both   |                                                                                                                                                                                                            |

| 27                  | BA6   | 0    | Both   |                                                                                                                                                                                                            |

| 32                  | BA7   | 0    | Both   |                                                                                                                                                                                                            |

| 20                  | \RAS  | 0    | Low    | ROW ADDRESS STROBE. Row address strobe for all DRAM memory banks.                                                                                                                                          |

| 134                 | \CAS0 | 0    | Low    | COLUMN ADDRESS STROBE 0. Active low column address strobe for Memory Plane 0.                                                                                                                              |

| 135                 | \CAS1 | 0    | Low    | COLUMN ADDRESS STROBE 1. Active low column address strobe for Memory Plane 1.                                                                                                                              |

| 136                 | \CAS2 | 0    | Low    | COLUMN ADDRESS STROBE 2. Active low column address strobe for Memory Plane 2.                                                                                                                              |

| 137                 | \CAS3 | 0    | Low    | COLUMN ADDRESS STROBE 3. Active low column address strobe for Memory Plane 3.                                                                                                                              |

| 139                 | \WE   | 0    | Low    | WRITE ENABLE. Active low write enable signal for all display memory banks/planes.                                                                                                                          |

| 97                  | HSYNC | 0    | Both   | HORIZONTAL SYNC OUTPUT. HSYNC is active high if the horizontal polarity bit (Bit 6 of the Miscellaneous Output register; I/O address 3C2) is low. It is active low if the horizontal polarity bit is high. |

| 98                  | VSYNC | 0    | Both   | VERTICAL SYNC OUTPUT. VSYNC is active high if the vertical polarity bit (Bit 7 of the Miscellaneous Output register; I/O address 3C2) is low. It is active low if the vertical polarity bit is high.       |

| 96                  | BLANK | 0    | Both   | BLANK is a programmable output for blank-<br>ing the CRT or Flat Panel. Its polarity is<br>programmable. It can be redefined as the Dis-<br>play Enable signal.                                            |

| Flatpack |          |      |        |                                                                                                |                                              |                                                                                                                                                         |  |

|----------|----------|------|--------|------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.  | Name     | Type | Active | Descrip                                                                                        |                                              |                                                                                                                                                         |  |

| 85       | VIDEO0   | 0    | Both   |                                                                                                | _                                            | video outputs to drive a                                                                                                                                |  |

| 86       | VIDEO1   | 0    | Both   | color or m                                                                                     | onochro                                      | me display devices.                                                                                                                                     |  |

| 87       | VIDEO2   | 0    | Both   | Color values for digital CRT interface a                                                       |                                              |                                                                                                                                                         |  |

|          |          |      |        | assigned as follows:                                                                           |                                              |                                                                                                                                                         |  |

| 88       | VIDEO3   | 0    | Both   | Video0                                                                                         | В                                            | Blue                                                                                                                                                    |  |

| 89       | VIDEO4   | 0    | Both   | Video1                                                                                         | G                                            | Green                                                                                                                                                   |  |

| 93       | VIDEO5   | 0    | Both   | Video2                                                                                         | R                                            | Red                                                                                                                                                     |  |

| 94       | VIDEO6   | 0    | Both   | Video3                                                                                         | BS/V                                         | Secondary Blue/                                                                                                                                         |  |

| 95       | VIDEO7   | 0    | Both   |                                                                                                |                                              | Monochrome                                                                                                                                              |  |

|          |          |      |        | Video4                                                                                         | GS/I                                         | Secondary Green/In-<br>tensity                                                                                                                          |  |

|          |          |      |        | Video5                                                                                         | RS                                           | Secondary Red                                                                                                                                           |  |

|          |          |      |        | Video6                                                                                         |                                              | User Defined                                                                                                                                            |  |

|          |          |      |        | Video7                                                                                         |                                              | User Defined                                                                                                                                            |  |

| 92       | SHIFTCLK | 0    | High   | SHIFT CLOCK. Output pixel clock to whi video output data is synchronized.                      |                                              |                                                                                                                                                         |  |

| 83       | WGTCLK   | 0    | High   | WEIGHT CONTROL CLOCK. Gray scal reference clock for Panels with Pulse Widt Modulation support. |                                              |                                                                                                                                                         |  |

| 17       | ACDCLK   | 0    | High   |                                                                                                | rammable                                     | % duty cycle square-wave<br>e period. Used to back bias                                                                                                 |  |

| 140      | \ERMEN   | 0    | Low    | indicates<br>accessed<br>refresh th<br>device ac                                               | whether<br>by the (<br>e display<br>cess and | INDICATOR. This output display memory is being CPU or by the 82C455 to v. A high indicates display a low is CPU access. This fined as a general purpose |  |

| 112      | \TRAP    | 0    | Low    | TRAP cor                                                                                       | ndition rec<br>can be re                     | e low output indicates a<br>quiring special CPU assis-<br>defined as a general pur-                                                                     |  |

| 82       | PTMC     | I    | Both   | terface. P                                                                                     | TMC low selects                              | selects the type of CPU inselects an MCA interface a PC-Bus interface. This be valid.                                                                   |  |

| Flatpack |      |      |        |             |  |

|----------|------|------|--------|-------------|--|

| Pin No.  | Name | Type | Active | Description |  |

| 1        | Vcc  |      |        | POWER       |  |

| 18       |      |      |        |             |  |

| 54       |      |      |        |             |  |

| 73       |      |      |        |             |  |

| 90       |      |      |        |             |  |

| 126      |      |      |        |             |  |

| 9        | Vss  |      |        | GROUND      |  |

| 19       |      |      |        |             |  |

| 30       |      |      |        |             |  |

| 45       |      |      |        |             |  |

| 55       |      |      |        |             |  |

| 66       |      |      |        |             |  |

| 81       |      |      |        |             |  |

| 91       |      |      |        |             |  |

| 102      |      |      |        |             |  |

| 117      |      |      |        |             |  |

| 127      |      |      |        |             |  |

| 138      |      |      |        |             |  |

| 36       | NC   |      |        | NO CONNECTS |  |

| 37       |      |      |        |             |  |

| 39       |      |      |        |             |  |

| 76       |      |      |        |             |  |

| 84       |      |      |        |             |  |

| 106      |      |      |        |             |  |

| 107      |      |      |        |             |  |

| 109      |      |      |        |             |  |

| 110      |      |      |        |             |  |

## **Absolute Maximum Ratings**

| Parameter             | Symbol           | Min  | Max                  | Units |

|-----------------------|------------------|------|----------------------|-------|

| Supply Voltage        | $V_{DD}$         | _    | 7.0                  | ٧     |

| Input Voltage         | Vi               | -0.5 | V <sub>DD</sub> +0.5 | ٧     |

| Output Voltage        | Vo               | -0.5 | V <sub>DD</sub> +0.5 | ٧     |

| Operating Temperature | Тор              | -25  | 85                   | 0°C   |

| Storage Temperature   | T <sub>stg</sub> | -40  | 125                  | 0°C   |

## 82C455 Operating Conditions

| Parameter           | Symbol          | Min  | Max  | Units |

|---------------------|-----------------|------|------|-------|

| Supply Voltage      | V <sub>DD</sub> | 4.75 | 5.25 | ٧     |

| Ambient Temperature | TA              | -40  | 70   | 0°C   |

### 82C455 DC Characteristics

| Parameter                                         | Symbol          | Min  | Max  | Units |

|---------------------------------------------------|-----------------|------|------|-------|

| Input Low Voltage                                 | V <sub>IL</sub> |      | 0.8  | ٧     |

| Input High Voltage                                | V <sub>IH</sub> | 2.0  |      | ٧     |

| Output Low Voltage<br>IOL = TBD                   | Vol             |      | 0.45 | ٧     |

| Output High Voltage<br>IOH = TBD                  | Vон             | 3.5  |      | ٧     |

| Input Leakage Current                             | InL             | -100 | +100 | uA    |

| Power Supply Current<br>@25 MHz CLK, 0°C          | lcc             |      | 100  | mA    |

| Ouput High Impedance Leakage<br>0.45 < VPIN < VDD | loz             | -100 | +100 | uA    |

**Note:** Electrical specifications contained herein are preliminary and subject to change without notice.

# 82C455 AC Timing Characteristics

$(TA = 0^{\circ}C - 70^{\circ}C, VDD = 5V\pm5\%)$

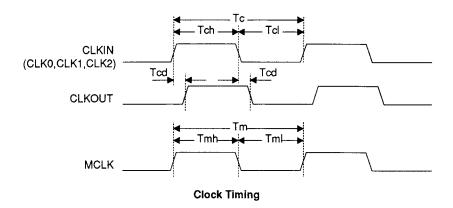

# **Clock Timing**

| Parameter             | Symbol          | Min(ns)                | Max(ns) |  |

|-----------------------|-----------------|------------------------|---------|--|

| CLK Period            | Тс              | 25                     |         |  |

| CLK High time         | T <sub>ch</sub> | (Tc/2)-5%              |         |  |

| CLK Low time          | T <sub>cl</sub> | (Tc/2)-5%              |         |  |

| MCLK Period           | T <sub>m</sub>  | 25                     | 40      |  |

| MCLK High time        | T <sub>mh</sub> | (T <sub>m</sub> /2)-5% |         |  |

| MCLK Low time         | T <sub>ml</sub> | (T <sub>m</sub> /2)-5% |         |  |

| CLK to SHIFTCLK delay | T∞d             |                        | 25      |  |

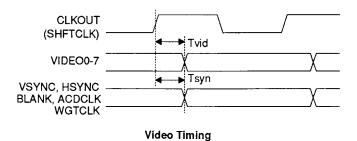

## **Video Timing**

| Parameter                                  | Symbol           | Min(ns) | Max (ns) |

|--------------------------------------------|------------------|---------|----------|

| SYNC and VIDEO CONTROL delay from SHIFTCLK | T <sub>syn</sub> |         | 20       |

| Video delay from SHIFTCLK                  | T <sub>vid</sub> | 5       | 20       |

# Other Timing

| Parameter         | Symbol | Min(ns)           | Max (ns) |

|-------------------|--------|-------------------|----------|

| RESET Pulse Width |        | 64 T <sub>c</sub> |          |

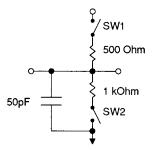

**AC Characteristics Load Circuit**

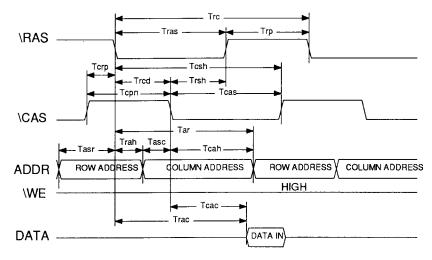

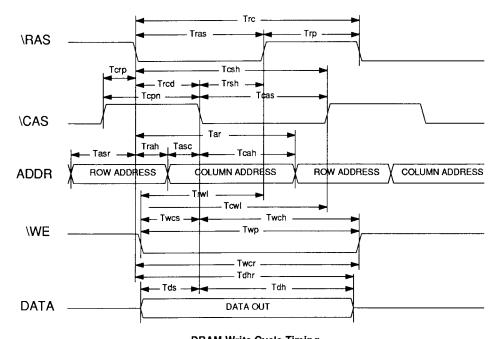

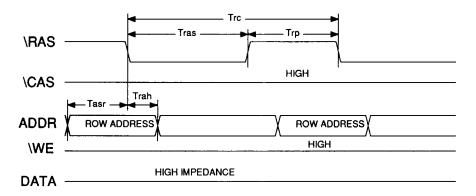

# **DRAM Timing**

| Parameter                     | Symbol           | 8 dot mode<br>Min(ns) Max(ns) |                 | 9 dot mode<br>Min(ns) Max(ns) |                 |

|-------------------------------|------------------|-------------------------------|-----------------|-------------------------------|-----------------|

| Read/Write Cycle time         | T <sub>rc</sub>  | 7T <sub>c</sub>               | -               | 8T <sub>c</sub>               | -               |

| \RAS Pulse Width              | T <sub>ras</sub> | 4T <sub>c</sub>               | -               | 4T <sub>c</sub>               | -               |

| Column Address Hold from Ras  | Tar              | 5T <sub>c</sub>               | -               | 5T <sub>c</sub>               | -               |

| \RAS precharge                | T <sub>rp</sub>  | 3T <sub>c</sub>               | <del>-</del>    | 4T <sub>c</sub>               | -               |

| \CAS to \RAS precharge        | T <sub>crp</sub> | 1T <sub>c</sub>               | -               | 2T <sub>c</sub>               | -               |

| \CAS hold from \RAS           | T <sub>csh</sub> | 6T <sub>c</sub>               | -               | 6T <sub>c</sub>               | -               |

| \RAS to \CAS delay            | T <sub>rcd</sub> | 2T <sub>c</sub>               | -               | 2T <sub>c</sub>               | -               |

| \RAS hold from \CAS           | T <sub>rsh</sub> | 2T <sub>c</sub>               | -               | 2T <sub>c</sub>               | -               |

| \CAS Precharge                | Topn             | 3T <sub>c</sub>               | -               | 4Tc                           | -               |

| \CAS Pulse Width              | T <sub>cas</sub> | 4T <sub>c</sub>               | -               | 4T <sub>c</sub>               | -               |

| Row Address Setup to \RAS     | Tasr             | 2T <sub>c</sub>               | -               | 3T <sub>c</sub>               | _               |

| Column Address setup to \CAS  | Tasc             | 1T <sub>c</sub>               | _               | 1T <sub>c</sub>               | -               |

| Row Address hold from \RAS    | T <sub>rah</sub> | 1T <sub>c</sub>               | -               | 1T <sub>c</sub>               | -               |

| Column Address hold from \CAS | T <sub>cah</sub> | 3T <sub>c</sub>               | -               | 3Тс                           | -               |

| Data Access time from \CAS    | T <sub>cac</sub> | -                             | 3T <sub>c</sub> | -                             | 3Т₀             |

| Data Access time from \RAS    | T <sub>rac</sub> | -                             | 5T <sub>c</sub> | -                             | 5T <sub>c</sub> |

| \WE Pulse Width               | Twp              | 7T <sub>c</sub>               | -               | 8T <sub>c</sub>               | -               |

| Write Data Setup to \CAS      | T <sub>ds</sub>  | 2T <sub>c</sub>               | -               | 2T <sub>c</sub>               | -               |

| Write Data Hold from \CAS     | T <sub>dh</sub>  | 5T <sub>c</sub>               | -               | 6T <sub>c</sub>               | -               |

| Write Data Hold from \RAS     | T <sub>dhr</sub> | 7Tc                           | -               | 8T <sub>c</sub>               | -               |

| \WE hold from \CAS            | T <sub>wch</sub> | 5T <sub>c</sub>               | -               | 6T <sub>c</sub>               | -               |

| \WE setup to \CAS             | T <sub>wcs</sub> | 2T <sub>c</sub>               | -               | 2T <sub>c</sub>               | -               |

| \WE lead to \RAS              | Trwi             | 4T <sub>c</sub>               | -               | 4T <sub>c</sub>               | -               |

| \WE lead to \CAS              | T <sub>cwl</sub> | 6T <sub>c</sub>               | _               | 6T <sub>c</sub>               | -               |

| \WE hold from \RAS            | Twer             | 7T <sub>c</sub>               | -               | 8T <sub>c</sub>               | -               |

## **DRAM Read Cycle Timing**

**DRAM Write Cycle Timing**

### Compatibility with DRAMs

| Parameters                                            | Symbol   | Max                                     | Units |

|-------------------------------------------------------|----------|-----------------------------------------|-------|

| CLKIN Frequency for 16 Color Display and 120 ns DRAMS | <u>-</u> | 30                                      | MHz   |

| CLKIN Frequency for 16 Color Display and 100 ns DRAMS | -        | 35-40                                   | MHz   |

| DRAM Refresh interval                                 | -        | 85000/(V <sub>R</sub> *V <sub>L</sub> ) | ms    |

| Vertical refresh rate                                 | VR       |                                         | Hz    |

| Total number of lines per frame (including retrace)   | VL       |                                         | -     |

**DRAM Refresh Cycle Timing**

17

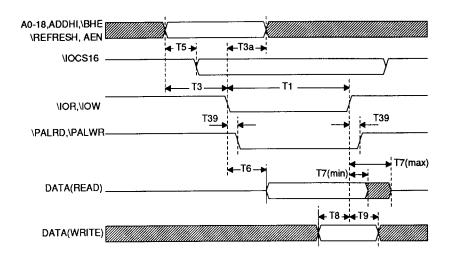

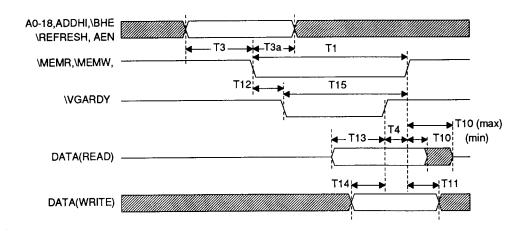

# PC & PC/AT BUS Interface

# I/O and Memory Bus Timing

| Symbol | Min(ns)                                                 | Max(ns)                                                                                    |

|--------|---------------------------------------------------------|--------------------------------------------------------------------------------------------|

| T1     | 175                                                     | - 190                                                                                      |

| ТЗ     | 80                                                      |                                                                                            |

| ТЗа    | 20                                                      | · · · · · · · · · · · · · · · · ·                                                          |

| T5     |                                                         | 25                                                                                         |

| T4     | 0                                                       |                                                                                            |

| Т6     |                                                         | 50                                                                                         |

| T7     | 10                                                      | 40                                                                                         |

| T8     | 40                                                      |                                                                                            |

| T9     | 0                                                       |                                                                                            |

| T10    | 10                                                      | 40                                                                                         |

| T11    | 0                                                       |                                                                                            |

| T12    |                                                         | 25                                                                                         |

| T13    | 25                                                      |                                                                                            |

| T14    | 40                                                      |                                                                                            |

| T15    | 7T <sub>c</sub>                                         | 128Tc                                                                                      |

| T39    |                                                         | 25                                                                                         |

| T2     |                                                         | 25                                                                                         |

|        | T1 T3 T3a T5 T4 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T39 | T1 175 T3 80 T3a 20 T5 T4 0 T6 T7 10 T8 40 T9 0 T10 10 T11 0 T12 T13 25 T14 40 T15 7Tc T39 |

### PC and PC/AT Bus I/O Cycle Timing

PC and PC/AT Bus Memory Cycle Timing

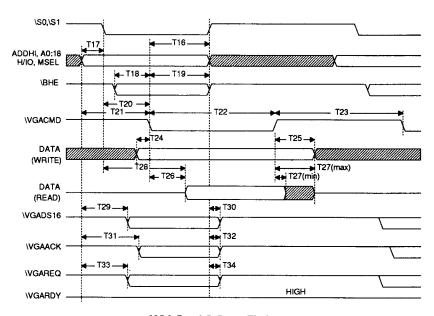

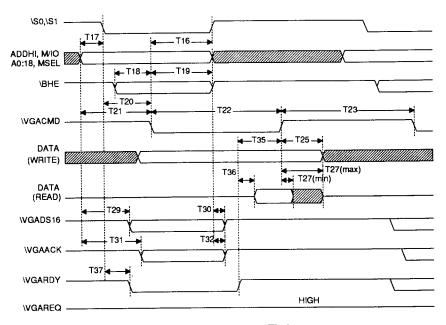

# **MCA Interface**

# I/O and Memory Cycle Timing

| Parameter                                 | Symbol | Min(ns) | Max(ns) |

|-------------------------------------------|--------|---------|---------|

| Status hold from \VGACMD                  | T16    | 20      |         |

| Status active from address valid          | T17    | 0       |         |

| \BHE setup to \VGACMD                     | T18    | 30      |         |

| Address, \BHE hold from \VGACMD           | T19    | 20      |         |

| \VGACMD active from Status                | T20    | 45      |         |

| \VGACMD from address valid                | T21    | 80      |         |

| \GACMD Pulse Width                        | T22    | 80      |         |

| \GACMD inactive to next \VGACMD           | T23    | 80      |         |

| Write data setup to \VGACMD               | T24    | 0       |         |

| Write data hold from \VGACMD              | T25    | 10      |         |

| Read data valid from \VGACMD              | T26    |         | 50      |

| Read data hold from \VGACMD               | T27    | 10      | 40      |

| Status to Read data valid                 | T28    |         | 125     |

| VGADS16 active from address valid         | T29    |         | 25      |

| \VGADS16 inactive from Status             | T30    | 5       | 25      |

| \VGAACK active from address valid         | T31    |         | 25      |

| \VGAACK inactive from Status              | T32    | 5       | 25      |

| \VGAREQ active from address valid         | T33    |         | 25      |

| \VGAREQ inactive from Status              | T34    | 5       | 25      |

| \VGARDY active from \VGACMD high          | T35    | 65      |         |

| Read data from \VGARDY active (high)      | T36    |         | 50      |

| \VGARDY inactive (low) from Status        | T37    |         | 25      |

| Write data setup to \VGARDY active (high) | T38    |         | 40      |

| \PALRD, \PALWR delay from Command         | T39    |         | 25      |

MCA Bus I/O Cycle Timing

**MCA Bus Memory Cycle Timing**

# CHIP'S

Chips and Technologies, Incorporated 3050 Zanker Road, San Jose, CA 95134 408-4340600 Telex 272929 CHIP UR

IBM, AT, XT, PS/2, OS/2, Enhanced Graphics Adapter, Color Graphics Adapter, Monochrome Adapter, and IBM Color Display are trademarks of International Business Machines Corporation.

Intel, and iAPX 386 are trademarks of Intel Corporation.

MOTOROLA is a trademark of Motorola.

Hercules Graphics is a trademark of Hercules Computer Technology.

Lotus is a trademark of Lotus Corporation.

Microsoft is a trademark of Microsoft Corporation.

CHIPSet, CHIPSpak, CHIPSport, SharpScan EGA, and ChipsLink are trademarks of Chips and Technologies, Inc.

Copyright 1988 Chips and Technologies, Inc.

Chips and Technologies, Inc. makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document.

Chips and Technologies, Inc. retains the right to make changes to these specifications at any time without notice.

T-52-33-45

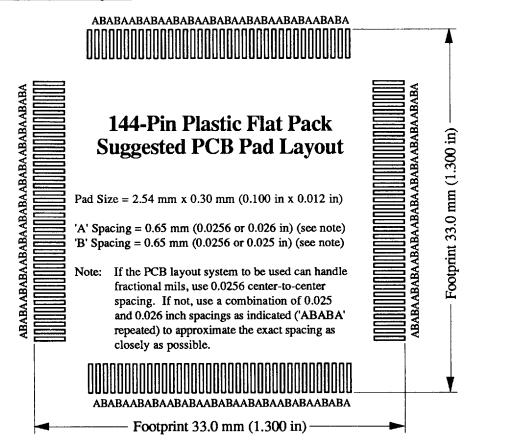

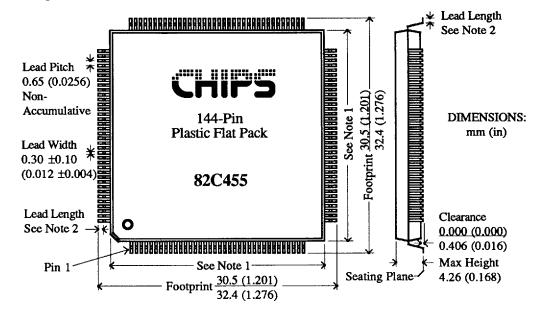

## 82C455 Mechanical Specifications:

Note 1: Package Body Size =  $26 \pm 0.2$  (1.024  $\pm 0.008$ ) Note 2: Lead Length =  $1.2 \pm 0.2$  (0.047  $\pm 0.008$ )

# 82C455 Suggested PCB Pad Layout: