# Preliminary Data Book

#### **APPLICATIONS**

- Presentation

- Video Editina

- **Video Authoring**

- Video Teleconferencing

- Interactive Education Systems

- Games

# **FEATURES**

- ☐ Extensive software support available contact Cirrus Logic Sales office for complete details

- Supports up to three simultaneous video data streams

- Video scaling

- Supports both YCbCr and RGB formats

- Interfaces to CODECs, decoders, encoders

- Integrated ISA, MCA, and host bus interfaces

(cont. next page)

# **Digital Video Processor**

### **OVERVIEW**

The CL-PX2070 Digital Video Processor (DVP) provides a powerful, cost-effective desktop solution for computer graphics and imaging. The DVP can be used in presentations, video teleconferencing, animation, and video capture for scaling with video signal processors dedicated to compressing and decompressing video data streams.

(cont. next page)

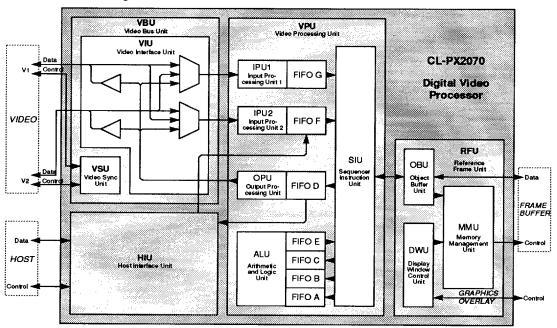

#### Functional Block Diagram

#### FEATURES (cont.)

- Complete frame buffer control

- 1/2 8 Mbytes of frame buffer memory

- Video stream format conversion

- Color space conversion

- Supports up to eight simultaneous object **buffers**

- Programmable, triple-channel LUT RAM

- Prescaling, zoom, and windowing

- Graphic and bitmapped stream support

- Programmable sync slave or master

- When used with the CL-PX2080 MediaDAC™

- Simultaneous video and graphics display

- Four simultaneous, overlapping (occluded) display windows

- Zooms from 1x to 256x

- 1024 x 768 display at 85 MHz

#### **OVERVIEW** (cont.)

The DVP combines the real-time video scaling features of the CL-PX0072 VWG with the frame buffer memory management, arithmetic and logical processing, a programmable host system bus interface, flexible mainstream video datapath, and windowing control for multiple, simultaneous video data streams.

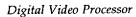

The DVP has four major functional units:

- HIU: Host Interface Unit

- VBU: Video Bus Unit

- VPU: Video Processing Unit

- RFU: Reference Frame Unit

#### HIU: Host Interface Unit

The HIU interfaces the DVP to the host system. It transfers graphic or video data between the host system and the frame buffer through direct access to FIFOs in the VPU, and accesses the DVP control registers.

#### VBU: Video Bus Unit

The VBU manages the flow of video and graphic streams between the DVP and up to three independent devices (including the host system).

The VBU provides two independent, real-time video I/O ports (V1 and V2), and contains two subunits - the VIU and VSU.

V1 and V2 have the following characteristics:

- Each can be configured as input only, output only, or pixel- or field-duplexed I/O;

- Each provides programmable sync polarity;

- Either port can use the VSU sync generator;

- Each supports the following video formats:

- Input: YCbCr 16-bit 4:2:2, 12-bit 4:1:1; RGB 16-bit, 8-bit;

- Output: YCbCr 16-bit; RGB 16-bit, 8-bit;

- V2 controls the video stream data flow between the DVP and typical CODEC devices.

|                      | ISA Bus                                                                         | MCA Bus                                                                                             | Local Hardware                         |

|----------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------|

| Interface            | DVP interfaces with the host s                                                  | ystem interface bus.                                                                                | DVP interfaces with the processor bus. |

| Multiplex<br>Support | DVP signals support the requir impleading, and provide bidired system data bus. |                                                                                                     | N/A                                    |

| Address<br>Decode    | DVP internally decodes the bu cycles.                                           | The host system provides the decoded chip select signal for use with register select input signals. |                                        |

Digital Video Processor

The VIU (Video Interface Unit) controls the flow of internal video streams through the video ports to all external devices. It controls:

- the source and direction of video stream and sync control inputs;

- the field-toggling mode and field ID signals:

- the watchdog timer feature.

Two VIU master control registers provide matching fields that specify input and output sync modes.

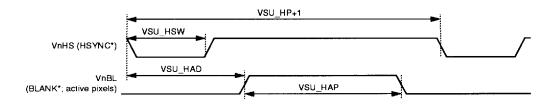

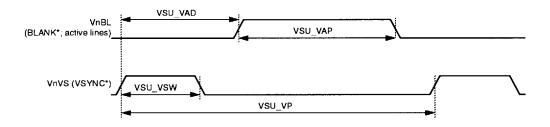

The VSU (Video Sync Unit) implements identical, independent reference signals for each video port:

- Vertical sync signals specify the beginning of a field or frame.

- Horizontal sync signals specify the beginning

- Horizontal/composite blanking signals specify the horizontal/composite blanking interval.

#### **VPU: Video Processing Unit**

The VPU processes field-oriented video. It can simultaneously process two external, bidirectional real-time video streams and a single external, bidirectional host video or graphic data stream. It also provides a data path between the DVP and the host system for bidirectional graphic streams through the HIU. FIFO D can send to, and FIFO F can receive from the HIU directly.

The VPU has five subunits - the IPU1, IPU2. OPU, ALU, and SIU.

The IPU1 (Input Processor Unit 1) prepares an input video stream for ALU processing and/or storage in the frame buffer, then outputs the prepared stream to the frame buffer data bus. Its video processing features include:

- YCbCr and RGB input stream format conversion.

- color space conversion,

- programmable data tagging,

- three-channel lookup table operations,

- horizontal prescaling,

- window clipping,

- horizontal and vertical scaling, and

- output stream format conversion.

The IPU2 (Input Processor Unit 2) controls prescaling and windowing.

The OPU (Output Processing Unit) controls zoom, window clipping, and output format functions.

The ALU (Arithmetic Logic Unit) performs arithmetic, logical, and tagging operations for YCbCr streams, and logical and tagging operations only for RGB and 8-bit pseudocolor streams. It controls stream format, operand source selection, tagging operation selection, and arithmetic or logical operation for both field times, and can process up to three simultaneous video streams input through its FIFOs.

The SIU (Sequencer Instruction Unit) is a specialpurpose microcontroller that coordinates the flow of multiple, simultaneous data streams between the IPU1, IPU2, OPU, ALU, and OBU.

The SIU is field-based when processing interlaced video data; that is, it distinguishes between the vertical sync pulses for each field and executes one of two different instruction sequences, causing multiple stream flows to appear concurrent.

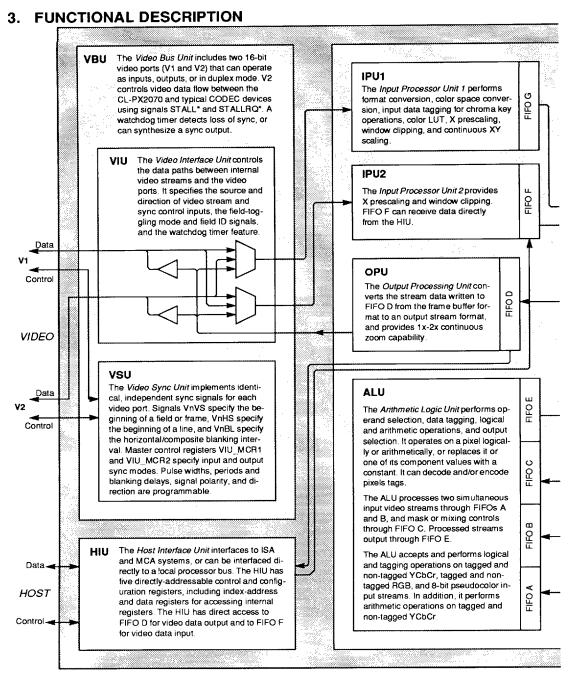

#### RFU: Reference Frame Unit

The RFU provides simultaneous access to eight object buffers and four display windows. It has three subunits - the OBU, DWU, and MMU.

The OBU (Object Buffer Unit) specifies the size, location, operating mode, X and Y raster directions. FIFO association, chrominance and luminance channel masking, and output decimation for each object buffer. It allows each object buffer to be locked to either video source, or to be programmed to operate independently. Object buffers can also be placed anywhere within the linearly-addressable frame buffer.

The DWU (Display Window Unit) allows each display window to be any size or location. These display windows can overlap when the DVP is used with the CL-PX2080 MediaDAC™.

The MMU (Memory Management Unit) provides the frame buffer control interface for up to 8 megabytes of DRAM or VRAM.

July 1993

# **TABLE OF CONTENTS**

| LIST | OF TA  | BLES .   |                    |                                  | 7    |

|------|--------|----------|--------------------|----------------------------------|------|

| CON  | VENTI  | ONS, A   | BBREVIAT           | TONS, AND TRADEMARKS             | 8    |

| 1.   | PIN IN | FORMA    | TION               |                                  | .10  |

|      | 1.1    | Pin Diag | gram               |                                  | .10  |

|      | 1.2    | DVP Fu   | nctional Si        | gnal Groups                      | .11  |

|      | 1.3    | Pin Ass  | ignment Ta         | able                             | .12  |

| 2.   | DETA   | ILED SK  | GNAL DES           | SCRIPTIONS                       | .14  |

|      | 2.1    | Host Int | erface — I         | SA                               | . 14 |

|      | 2.2    | Host Int | erface — I         | MCA                              | .15  |

|      | 2.3    | Host Int | erface — l         | ocal Hardware                    | 16   |

|      | 2.4    | Graphic  | s Overlay          | Interface                        | .17  |

|      | 2.5    | Video Ir | nterface           |                                  | .18  |

|      | 2.6    |          |                    | face                             |      |

|      | 2.7    |          |                    | j                                |      |

| 3.   | FUNC   | TIONAL   | DESCRIP            | TION                             | .20  |

| 4.   | DETA   | ILED RE  | GISTER             | DESCRIPTIONS                     | .22  |

|      | 4.1    | HIU: Ho  | st Interfac        | e Unit                           | 22   |

|      |        | 4.1.1    | HIU CSU            | : Configuration Setup            | 23   |

|      |        | 4.1.2    | HIU_DBG            | : Debug Control                  | 24   |

|      |        | 4.1.3    | HIU_DRD            | : Debug Read                     | 24   |

|      |        | 4.1.4    |                    | Interrupt Request                |      |

|      |        | 4.1.5    | HIU_OCS            | : Operation Control/Status       | 26   |

|      |        | 4.1.6    | HIU_RIN:           | Register Index                   | 27   |

|      |        | 4.1.7    | HIU_RDT:           | : Register Data Port             | 28   |

|      |        | 4.1.8    | HIU_MDT            | : Memory Data Port               | 28   |

|      |        | 4.1.9    |                    | Interrupt Setup                  |      |

|      | 4.2    |          |                    | nit                              |      |

|      |        | 4.2.1    |                    | Interface Unit                   | 30   |

|      |        |          | 4.2.1.1            | VIU_MCRp: VIU Master Control     | 30   |

|      |        |          | 4.2.1.2            | VIU_DPCf: Datapath Control       | 32   |

|      |        |          | 4.2.1.3            | VIU_WDT: Watchdog Timer          | 33   |

|      |        |          | 4.2.1.4            | VIU_TEST: Test Register          |      |

|      |        | 4.2.2    |                    | o Sync Unit                      |      |

|      |        |          | 4.2.2.1            | VSU_HSW: Horizontal Sync Width   |      |

|      |        |          | 4.2.2.2            | VSU_HAP: Horizontal Active Delay | oo   |

|      |        |          | 4.2.2.3<br>4.2.2.4 | VSU_HP: Horizontal Period        |      |

|      |        |          | 4.2.2.4            | VSU_VSW: Vertical Sync Width     |      |

|      |        |          | 4.2.2.5            | VSU_VAD: Vertical Active Delay   |      |

|      |        |          | 4.2.2.7            | VSU_VAP: Vertical Active Pixels  |      |

|      |        |          | 4.2.2.8            | VSU_VP: Vertical Period          | 38   |

|      | 4.3    | VPI I: V |                    | ssor Unit                        |      |

|      | 5      | 4.3.1    |                    | al Control                       |      |

|      |        |          | 4.3.1.1            | VPU_MCR: VPU Master Control      |      |

|      |        |          |                    |                                  |      |

# CL-PX2070 Digital Video Processor

| 4.3.2 | IPU1: Inp          | ut Processor Unit 1                     | . 45 |

|-------|--------------------|-----------------------------------------|------|

|       | 4.3.2.1            | IPU1_PIX: Pixel Count                   | . 45 |

|       | 4.3.2.2            | IPU1_LIC: Line Count                    | . 45 |

|       | 4.3.2.3            | IPU1_FLC: Field Count                   | . 46 |

|       | 4.3.2.4            | IPU1_LIR: Line Count Interrupt Request  |      |

|       | 4.3.2.5            | IPU1_FIR: Field Count Interrupt Request | . 46 |

|       | 4.3.2.6            | IPU1_LRB: LUT RAM Base Address          |      |

|       | 4.3.2.7            | IPU1_LRD: LUT RAM Data                  |      |

|       | 4.3.2.8            | IPU1_MCRf: IPU1 Master Control          |      |

|       | 4.3.2.9            | IPU1_XBnf: X Begin                      |      |

|       | 4.3.2.10           | IPU1_XEIf: X End                        |      |

|       | 4.3.2.11           | IPU1_XSnf: X Shrink                     |      |

|       | 4.3.2.12           | IPU1_YBnf: Y Begin                      |      |

|       | 4.3.2.13           | IPU1_YEIf: Y End                        |      |

|       | 4.3.2.14           | IPU1_YSnf: Y Shrink                     |      |

|       | 4.3.2.15           | IPU1_KFCf: Key Function Code            |      |

|       | 4.3.2.16           | IPU1_MMxf: Chroma Key Max/Min           |      |

| 4.3.3 |                    | ut Processing Unit 2                    |      |

|       | 4.3.3.1            | IPU2_PIX: Pixel Count                   |      |

|       | 4.3.3.2            | IPU2_LIC: Line Count                    |      |

|       | 4.3.3.3            | IPU2_FLC: Field Count                   |      |

|       | 4.3.3.4            | IPU2_LIR: Line Count Interrupt Request  |      |

|       | 4.3.3.5            | IPU2_FIR: Field Count Interrupt Request |      |

|       | 4.3.3.6            | IPU2_MCRf: IPU2 Master Control          |      |

|       | 4.3.3.7<br>4.3.3.8 | IPU2_XBIf: X Begin                      |      |

|       | 4.3.3.8            | IPU2_XEI1: X End                        |      |

|       | 4.3.3.10           | IPU2_YBIf: Y Begin                      |      |

| 4.3.4 |                    | IPU2_YEIf: Y End                        |      |

| 4.3.4 | 4.3.4.1            | Jencer Instruction Unit                 |      |

|       |                    | SIU_MCR: SIU Master Control             |      |

|       | 4.3.4.2<br>4.3.4.3 | SIU_FCS: FIFO Control/Status            |      |

|       | 4.3.4.3            | SIU_FOU: FIFO Overflow/Underflow        |      |

|       | 4.3.4.5            | SIU_FAR: FIFO Auto Reset                |      |

| 4.3.5 |                    | nmetic and Logic Unit                   |      |

| 4.5.5 | 4.3.5.1            | ALU MCRf: ALU Master Control            |      |

|       | 4.3.5.2            | ALU TOP: Tag Operation                  |      |

|       | 4.3.5.3            | ALU AV: Alpha Value                     |      |

|       | 4.3.5.4            | ALU LOPx: Logic Operation               |      |

|       | 4.3.5.5            | ALU_CAx: Constant A                     |      |

|       | 4.3.5.6            | ALU_CBx: Constant B                     |      |

|       | 4.3.5.7            | ALU CCx: Constant C                     |      |

| 4.3.6 |                    | put Processing Unit                     |      |

|       | 4.3.6.1            | OPU_MCRf: OPU Master Control            |      |

|       | 4.3.6.2            | OPU_XBI1: X Begin                       |      |

|       | 4.3.6.3            | OPU_XEIf: X End                         |      |

|       | 4.3.6.4            | OPU_YBIf: Y Begin                       |      |

|       | 4.3.6.5            | OPU YEIf: Y End                         |      |

| 4.3.7 |                    | erence Frame Unit                       |      |

|       |                    |                                         |      |

July 1993

| Digital | Video | Processor |

|---------|-------|-----------|

|     |       | 4.3.8  | MMU: Me      | emory Management Unit                         | 73  |

|-----|-------|--------|--------------|-----------------------------------------------|-----|

|     |       |        | 4.3.8.1      | MMU_MCR: MMU Master Control                   | 73  |

|     |       | 4.3.9  | OBU: Ob      | ject Buffer Unit                              | 74  |

|     |       |        | 4.3.9.1      | OBUo_MCR: Object Buffer Master Control        | 74  |

|     |       |        | 4.3.9.2      | OBUo_RFX: Object Buffer Reference Frame Size  | 75  |

|     |       | 4.3.10 | OBUo_LS      | Sb: Object Buffer Linear Start Address        | 76  |

|     |       |        | 4.3.10.1     | OBUo BSa: Object Buffer Size                  | 77  |

|     |       |        | 4.3.10.2     | OBUo_DEC: Object Buffer Decimate Control      | 78  |

|     |       | 4.3.11 | DWU: Dis     | splay Window Unit                             | 78  |

|     |       |        | 4.3.11.1     | DWU_MCR: Display Window Master Control        | 78  |

|     |       |        | 4.3.11.2     | DWU_HCR: Display Window Horizontal Control    | 80  |

|     |       |        | 4.3.11.3     | DWUd_DZF: Display Window Display Zoom Factor  | 81  |

|     |       |        | 4.3.11.4     | DWUd_RFX: Display Window Reference Frame Size | 81  |

|     |       |        | 4.3.11.5     | DWUd_LSb: Display Window Linear Start Address | 82  |

|     |       |        | 4.3.11.6     | DWUd_WSa: Display Window Size                 | 82  |

|     |       |        | 4.3.11.7     |                                               |     |

| 5.  | ELEC  | TRICAL | . SPECIFI    | CATIONS                                       | 84  |

|     | 5.1   | Absolu | te Maximu    | ım Ratings                                    | 84  |

|     | 5.2   | DVP S  | pecification | ns (Digital)                                  | 84  |

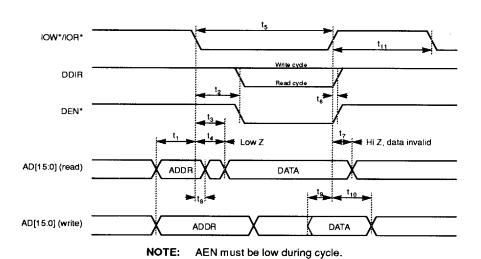

|     | 5.3   | AC Ch  | aracteristic | cs/Timing Information                         | 85  |

|     |       | 5.3.1  | Index of     | Timing Information                            |     |

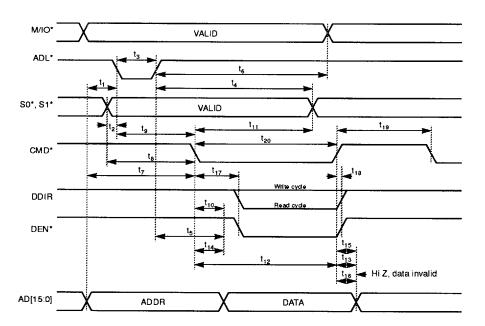

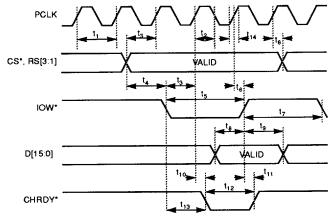

|     |       | 5.3.2  | ISA Bus      | Timing                                        | 86  |

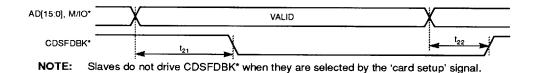

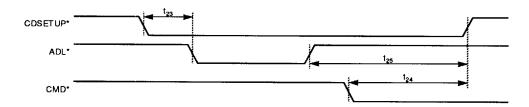

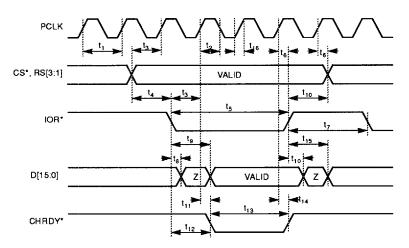

|     |       | 5.3.3  | MCA Bus      | s Timing                                      | 88  |

|     |       | 5.3.4  | Local Ha     | rdware Interface Timing                       | 90  |

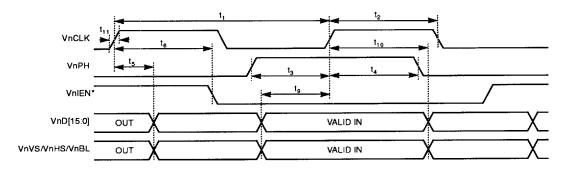

|     |       | 5.3.5  | Video Po     | ort Timing                                    | 92  |

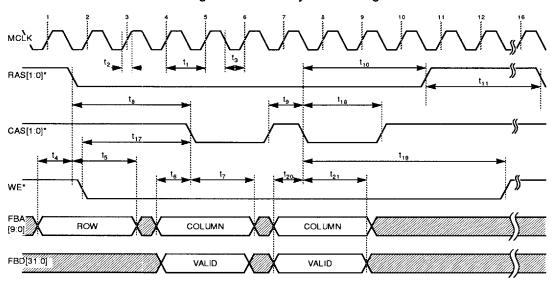

|     |       | 5.3.6  | Memory       | Timing                                        | 94  |

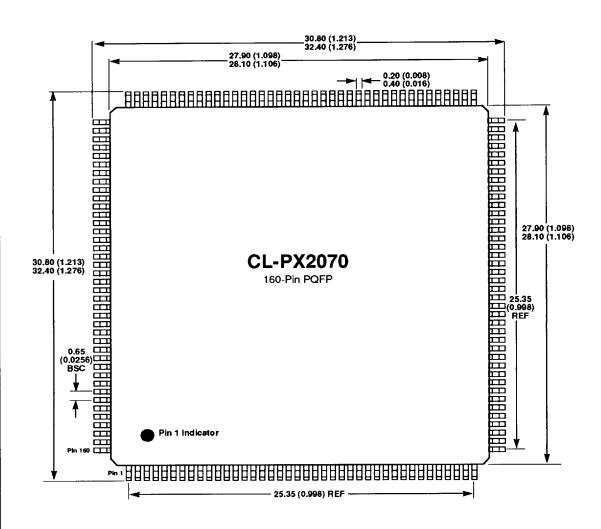

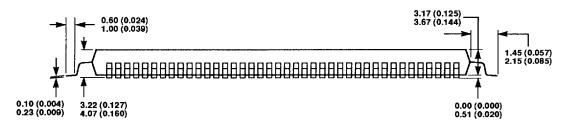

| 6.  | PAC   | KAGE D |              | NS — 160-Lead PQFP                            |     |

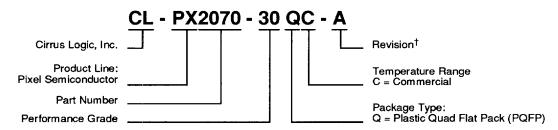

| 7.  |       |        |              | TION                                          |     |

|     |       |        | NECHNIA      | GISTERS — QUICK REFERENCE                     | 400 |

|     | PENDI |        |              |                                               |     |

|     |       |        |              | ***************************************       |     |

| IND | EX OF | CONTR  | OL REGIS     | STERS                                         | 109 |

|     |       |        | TED EIEI I   |                                               |     |

# CL-PX2070 Digital Video Processor

# **LIST OF FIGURES**

| Figure 1-1.  | DVP Pin Diagram                         |    |

|--------------|-----------------------------------------|----|

| Figure 4-1.  | VSU Horizontal Sync Timing              |    |

| Figure 4-2.  | VSU Vertical Sync Timing                |    |

| Figure 5-1.  | ISA Bus — I/O Timing                    |    |

| Figure 5-2.  | MCA Bus — I/O Timing                    |    |

| Figure 5-3.  | MCA Bus — CDSFDBK* Timing               |    |

| Figure 5-4.  | MCA Bus — CDSETUP* Timing               |    |

| Figure 5-5.  | Local Hardware Interface — Write Timing |    |

| Figure 5-6.  | Local Hardware Interface — Read Timing  |    |

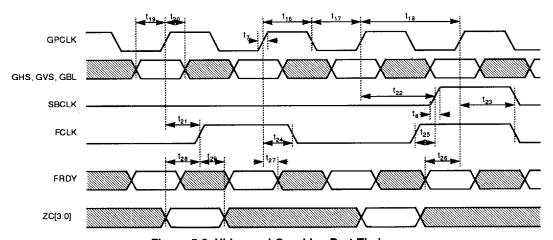

| Figure 5-7.  | Video I/O Timing                        |    |

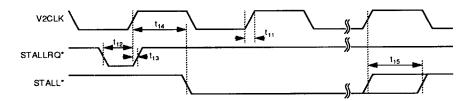

| Figure 5-8.  | STALL* and STALLRQ* Timing              |    |

| Figure 5-9.  | Video and Graphics Port Timing          |    |

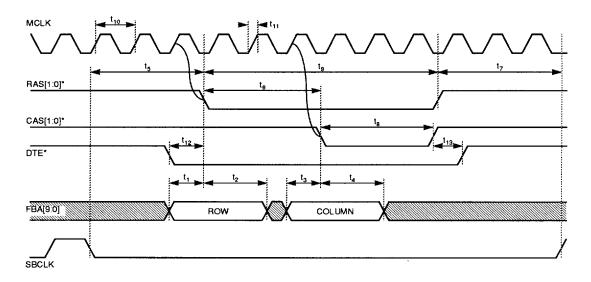

| Figure 5-10. | Read Transfer Cycle Timing              | 94 |

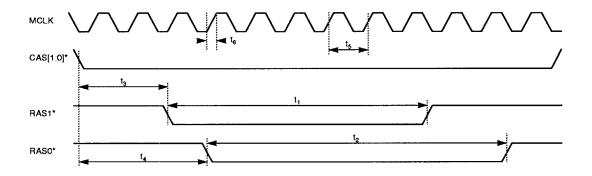

| Figure 5-11. | CAS* Before RAS* Refresh Timing         |    |

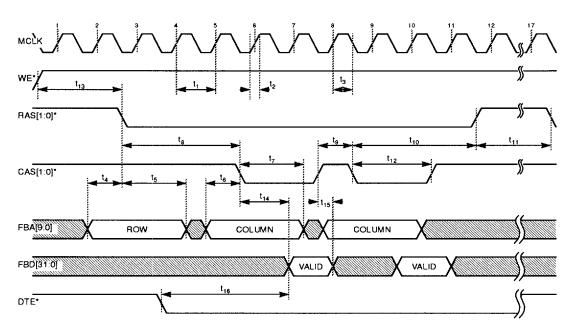

| Figure 5-12. | Memory Read Timing                      |    |

| Figure 5-13. | Memory Write Timing                     |    |

| Figure 6-1.  | DVP Package Information                 |    |

| Figure 6-2.  | DVP Package Information (Expanded View) | 99 |

|              |                                         |    |

|              | LIST OF TABLES                          |    |

| Table 4-1. | HIU Register Address Map                         | 22 |

|------------|--------------------------------------------------|----|

| Table 4-2. | HIU Registers Accessed by the Register Data Port |    |

| Table 5-1. | ISA Bus Timing                                   |    |

| Table 5-2. | MCA Bus Timing                                   |    |

| Table 5-3, | Local Hardware Interface — Write Timing          |    |

| Table 5-4. | Local Hardware Interface — Read Timing           |    |

| Table 5-5. | Video Port Timing                                |    |

| Table 5-6. | Read Transfer Cycle Timing                       |    |

| Table 5-7. | CAS* Before RAS* Refresh Timing                  |    |

| Table 5-8. | Memory Read and Write Timing                     |    |

Digital Video Processor

# CONVENTIONS, ABBREVIATIONS, AND TRADEMARKS

# CONVENTIONS

| VIU_DPCf | Register names containing lower case variables represent groups of registers with similar functions. For example, VIU_DPCf represents both Datapath Control registers — VIU_DPC1 (Datapath Control, Field 1) and VIU_DPC2 (Datapath Control, Field 2). In this data book, the following register variables are used: |                  |   |                             |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|-----------------------------|--|--|--|

|          | а                                                                                                                                                                                                                                                                                                                    | (axis)           | = | X, Y                        |  |  |  |

|          | b                                                                                                                                                                                                                                                                                                                    | (byte)           | = | L (Low) or H (High)         |  |  |  |

|          | С                                                                                                                                                                                                                                                                                                                    | (color space)    | = | Y, U, V or R, G, B          |  |  |  |

|          | d                                                                                                                                                                                                                                                                                                                    | (display window) | = | 0:3                         |  |  |  |

|          | f                                                                                                                                                                                                                                                                                                                    | (field)          | = | 1:2                         |  |  |  |

|          | n                                                                                                                                                                                                                                                                                                                    | (number)         | = | F (Fraction) or I (Integer) |  |  |  |

|          | 0                                                                                                                                                                                                                                                                                                                    | (object buffer)  | = | 0:7                         |  |  |  |

|          | р                                                                                                                                                                                                                                                                                                                    | (port)           | = | 1:2                         |  |  |  |

|          | s                                                                                                                                                                                                                                                                                                                    | (SIM)            | = | 0:31                        |  |  |  |

|          | х                                                                                                                                                                                                                                                                                                                    | (channel)        | = | Y, U, V                     |  |  |  |

# ABBREVIATIONS, ACRONYMS, and MNEMONICS

| ALU   | Arithmetic and Logic Unit          |

|-------|------------------------------------|

| CODEC | COde/DEcode or Compress/decompress |

| CPU   | Central Processing Unit            |

| CRT   | Cathode Ray Tube                   |

| CTAG  | Control TAG multiplexer signal     |

| DRAM  | Dynamic Random Access Memory       |

| DWU   | Display Window Unit                |

| FBD   | Frame Buffer Data                  |

| FIFO  | First In, First Out                |

| ISA   | Industry Standard Architecture     |

| I/O   | Input/Output                       |

| LSA   | Linear Start Address               |

| JPEG  | Joint Photographic Expert Group    |

8 PRELIMINARY DATA BOOK

# CL-PX2070 Digital Video Processor

| LSB   | Least Significant Byte                                                                                               |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LSb   | Least Significant bit                                                                                                |  |  |  |  |

| LUT   | Look-Up Table                                                                                                        |  |  |  |  |

| MCA   | Micro Channel Architecture                                                                                           |  |  |  |  |

| мми   | Memory Management Unit                                                                                               |  |  |  |  |

| MSB   | Most Significant Byte                                                                                                |  |  |  |  |

| MSb   | Most Significant bit                                                                                                 |  |  |  |  |

| OPU   | Output Processor Unit                                                                                                |  |  |  |  |

| OTAG  | Output TAG multiplexer signal                                                                                        |  |  |  |  |

| IPU1  | Input Processor Unit 1                                                                                               |  |  |  |  |

| IPU2  | Input Processor Unit 2                                                                                               |  |  |  |  |

| POS   | Programmable Option Select                                                                                           |  |  |  |  |

| PQFP  | Plastic Quad Flat Pack                                                                                               |  |  |  |  |

| PSE   | PreScaler Enable                                                                                                     |  |  |  |  |

| RGB   | Red, Green, Blue                                                                                                     |  |  |  |  |

| RAM   | Random Access Memory                                                                                                 |  |  |  |  |

| RFU   | Reference Frame Unit                                                                                                 |  |  |  |  |

| SIM   | Sequencer Instruction Memory                                                                                         |  |  |  |  |

| SIU   | Sequencer Instruction Unit                                                                                           |  |  |  |  |

| VPU   | Video Processor Unit                                                                                                 |  |  |  |  |

| VRAM  | Video dynamic Random Access Memory                                                                                   |  |  |  |  |

| YCbCr | Components of the CCIR601 color representation standard. Y = luminance; CbCr = chrominance Y-blue, chrominance Y-red |  |  |  |  |

# **TRADEMARKS**

MediaDAC™ is a trademark of Pixel Semiconductor, Inc.

July 1993

Digital Video Processor

#### 1. PIN INFORMATION

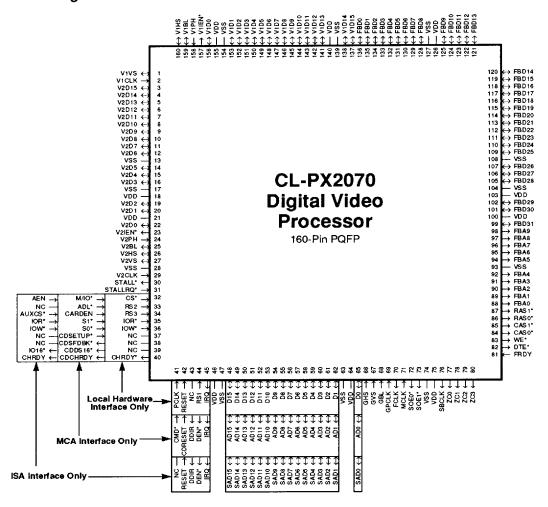

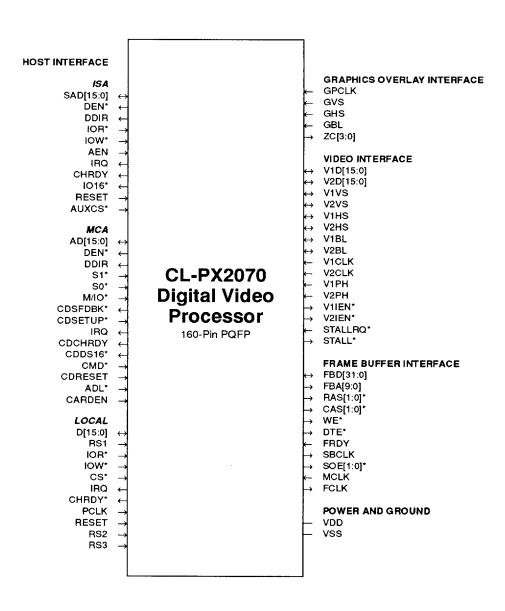

The CL-PX2070 DVP is available in a 160-lead Plastic Quad Flat Pack (PQFP) surface-mount package. It can be configured for ISA, MCA, and local hardware configurations, as shown in Figure 1-1.

NOTE: (\*) denotes active-low signals.

#### 1.1 Pin Diagram

Figure 1-1. DVP Pin Diagram

CL-PX2070

Digital Video Processor

# 1.2 DVP Functional Signal Groups

# 1.3 Pin Assignment Table

July 1993

Digital Video Processor

The following conventions are used in the pin assignment table:

(\*) = active-low signal

| = input

O = output

PWR = power

TTL = the pad has standard TTL input threshold and output levels

OD = open drain, TTL inputs

4 = 4-mA sink and 2-mA source drive capability

24 = 24-mA sink and 8-mA source drive capability

| NAME                      |                     |                 | PIN                    | TYPE             | CELL                  | FUNCTION                                                                               |

|---------------------------|---------------------|-----------------|------------------------|------------------|-----------------------|----------------------------------------------------------------------------------------|

| HOST INTERI               | FACE<br>MCA         | LOCAL           |                        |                  |                       |                                                                                        |

| Address/Data<br>SAD[15:0] | AD[15:0]            | <br>D[15:0]     | 48:62, 65<br>48:62, 65 | I/O<br>I/O       | TTL, 4<br>TTL, 4      | Address/Data Bus<br>Data Bus                                                           |

| Control DEN*              | DEN*                | —<br>RS1        | 44<br>44               | OD<br>I          | TTL, 8<br>TTL         | Data Buffer Enable<br>Register Select                                                  |

| DDIR<br>—<br>IOR*         | DDIR<br>            | —<br>NC<br>IOR* | 43<br>43<br>35         | OD<br>N/A<br>I   | TTL, 8<br>N/A<br>TTL  | Data Buffer Direction  No Connect (must be left floating)  I/O Read                    |

| <br>10W*                  | S1*<br>—            | iow*            | 35<br>36               | i<br>I           | TTL<br>TTL<br>TTL     | Status 1<br>I/O Write<br>Status 0                                                      |

| AEN                       | S0*<br><br>M/IO*    |                 | 36<br>32<br>32         | <br> <br>        | TTL<br>TTL            | Address Enable<br>Memory or I/O Cycle                                                  |

| NC<br>—                   | —<br>—<br>CDSFDBK*  | CS*<br>NC<br>—  | 32<br>38<br>38         | I<br>N/A<br>O    | TTL<br>N/A<br>TTL, 4  | Chip Select No Connect (must be left floating) Card Select Feedback                    |

| NC<br>—<br>IRQ            | CDSETUP*            | NC<br>—<br>IRQ  | 37<br>37<br>45         | N/A<br>I<br>O    | N/A<br>TTL<br>TTL, 4  | No Connect (must be left floating) Card Setup Interrupt Request                        |

| CHRDY<br>IO16*            | CDCHRDY             | CHRDY*          | 40<br>39               | OD<br>OD         | TTL, 24<br>TTL, 24    | Channel Ready<br>16-bit I/O Cycle                                                      |

| <br><br>NC                | CDDS16*<br>         | NC<br>—         | 39<br>39<br>41         | OD<br>N/A<br>N/A | TTL, 24<br>N/A<br>N/A | Card Data Size  No Connect (must be left floating)  No Connect (must be left floating) |

| <del></del>               | CMD*                | PCLK            | 41<br>41               |                  | TTL<br>TTL            | Command<br>Processor Clock                                                             |

| RESET<br>NC<br>—          | CDRESET<br><br>ADL* | RESET<br><br>   | 42<br>33<br>33         | N/A<br>I         | TTL<br>N/A<br>TTL     | Reset No Connect (must be left floating) Address Latch                                 |

| AUXCS*                    | —<br>—<br>CARDEN    | RS2<br>         | 33<br>34<br>34         | <br>             | TTL<br>TTL<br>TTL     | Register Select Auxiliary Chip Select Card Enable                                      |

|                           | _                   | RS3             | 34                     | i                | TTL                   | Register Select                                                                        |

Digital Video Processor

| NAME                       | PIN                                                 | TYPE | CELL    | FUNCTION                                       |

|----------------------------|-----------------------------------------------------|------|---------|------------------------------------------------|

| GRAPHICS (                 | OVERLAY INTERFACE                                   |      |         |                                                |

| GPCLK                      | 69                                                  | 1    | TTL     | Graphics Pixel Clock                           |

| GVS                        | 67                                                  | 1    | TTL     | Graphics Vertical Sync                         |

| GHS                        | 66                                                  | ı    | TTL     | Graphics Horizontal Sync                       |

| GBL                        | 68                                                  | ł    | TTL     | Graphics Blanking                              |

| ZC[3:0]                    | 80:77                                               | 0    | TTL, 4  | Zoom Control Bus                               |

| VIDEO INTEI                | RFACE                                               |      |         |                                                |

| Data                       |                                                     |      |         | •                                              |

| V1D[15:0]                  | 137:138, 141:153, 156                               | I/O  | TTL, 4  | V1 (Video Port 1) Data Bus                     |

| V2D[15:0]                  | 3:12, 14:16, 19:20, 22                              | I/O  | TTL, 4  | V2 (Video Port 2) Data Bus                     |

| Control                    |                                                     |      |         | ,                                              |

| V1VS                       | 1                                                   | I/O  | TTL, 4  | V1 Vertical Sync                               |

| V2VS                       | 27                                                  | I/O  | TTL, 4  | V2 Vertical Sync                               |

| V1HS                       | 160                                                 | 1/0  | TTL, 4  | V1 Horizontal Sync                             |

| V2HS                       | 26                                                  | 1/0  | TTL, 4  | V2 Horizontal Sync                             |

| V1BL                       | 159                                                 | 1/0  | TTL, 4  | V1 Horizontal/Composite Blanking               |

| V2BL                       | 25                                                  | VO   | TTL, 4  | V2 Horizontal/Composite Blanking               |

| V1CLK                      | 2                                                   | 1    | TTL     | V1 Data Clock                                  |

| V2CLK                      | 29                                                  | i    | TTL     | V2 Data Clock                                  |

| V1PH                       | 158                                                 | i    | TTL     | V1 Phase                                       |

| V2PH                       | 24                                                  | i    | TTL     |                                                |

| V2FFI<br>V1IEN*            |                                                     | •    |         | V2 Phase                                       |

|                            | 157                                                 | 0    | TTL, 4  | V1 Input Enable                                |

| V2IEN*                     | 23                                                  | 0    | TTL, 4  | V2 Input Enable                                |

| STALLRQ*                   | 31                                                  | 1    | TTL     | Stall Request                                  |

| STALL*                     | 30                                                  | 0    | TTL, 4  | Stall                                          |

|                            | FER INTERFACE                                       |      |         |                                                |

| Address/Data               |                                                     |      |         |                                                |

| FBD[31:0]                  | 99, 101:102, 105:107, 109:125, 128:136              | I/O  | TTL, 4  | Frame Buffer Data Bus                          |

| FBA[9:0]<br><i>Control</i> | 98:94, 92:88                                        | 0    | TTL, 8  | Frame Buffer Address Bus                       |

| RAS[1:0]*                  | 87:86                                               | 0    | TTL, 8  | Row Address Strobes                            |

| CAS[1:0]*                  | 85:84                                               | Ō    | TTL, 8  | Column Address Strobes                         |

| WE*                        | 83                                                  | Ö    | TTL, 12 | Write Enable                                   |

| DTE*                       | 82                                                  | ŏ    | TTL, 12 | Data Transfer Enable                           |

| FRDY                       | 81                                                  | Ĭ    | TTL     | FIFO Ready                                     |

| SBCLK                      | 76                                                  | 0    | TTL, 8  | Serial Bus Clock                               |

| SOE[1:0]*                  | 73:72                                               | 0    | TTL, 8  | Serial Port Output Enable                      |

| MCLK                       | 73.72                                               | ì    | TTL, 8  |                                                |

| FCLK                       | 71<br>70                                            | 0    |         | Memory Clock                                   |

| -CLK                       | 70                                                  | U    | TTL, 8  | FIFO Write Clock                               |

| POWER AND                  |                                                     |      |         |                                                |

| VDD                        | 18, 21, 46, 64, 75, 100, 103, 126, 140, 155         | PWR  | N/A     | +5 VDC for Digital Logic and Interface Buffers |

| vss                        | 13, 17, 28, 47, 63, 74, 93, 104, 108, 127, 139, 154 | PWR  | N/A     | Ground for Digital Logic and Interface Buffers |

July 1993

# **DETAILED SIGNAL DESCRIPTIONS**

# 2.1 Host Interface — ISA

| Signal    | Pin          | Type | Cell    | Function                                                                                                                                                                     |  |  |  |  |  |

|-----------|--------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SAD[15:0] | 48:62,<br>65 | 1/0  | TTL, 4  | Address/Data Bus. Bidirectional, multiplexed address/data bus that transfers video data and operation status and commands between the host system and the DVP.               |  |  |  |  |  |

| DEN*      | 44           | OD   | TTL, 8  | Data Buffer Enable.  Description: Enables the host data bus buffer.                                                                                                          |  |  |  |  |  |

| DDIR      | 43           | OD   | TTL, 8  | Data Buffer Direction. Specifies the direction of data flow on SAD[15:0].  On The host system is reading data from SAD[15:0];  The host system is writing data to SAD[15:0]. |  |  |  |  |  |

| IOR*      | 35           | ı    | TTL     | I/O Read. 0 Specifies an I/O read cycle.                                                                                                                                     |  |  |  |  |  |

| IOW*      | 36           | ı    | TTL     | I/O Write. 0 Specifies an I/O write cycle.                                                                                                                                   |  |  |  |  |  |

| AEN       | 32           | ı    | TTL     | Address Enable. 0 I/O cycle in progress. 1 DMA cycle in progress.                                                                                                            |  |  |  |  |  |

| NC        | 38           | N/A  | N/A     | No Connect. (must be left floating).                                                                                                                                         |  |  |  |  |  |

| NC        | 37           | N/A  | N/A     | No Connect. (must be left floating).                                                                                                                                         |  |  |  |  |  |

| IRQ       | 45           | 0    | TTL, 4  | Interrupt Request.  1 The DVP is requesting service from the host system.                                                                                                    |  |  |  |  |  |

| CHRDY     | 40           | OD   | TTL, 24 | Channel Ready.  The DVP is not ready to complete the current host access cycle.  The current host access cycle is complete.                                                  |  |  |  |  |  |

| IO16*     | 39           | OD   | TTL, 24 | 16-bit I/O Cycle.  O The DVP is able to respond as a 16-bit I/O data device for both read and write cycles.                                                                  |  |  |  |  |  |

| NC        | 41           | N/A  | N/A     | No Connect. (must be left floating).                                                                                                                                         |  |  |  |  |  |

| RESET     | 42           | ı    | TTL     | Reset.  Stops all DVP activity and resets the hardware.                                                                                                                      |  |  |  |  |  |

| NC        | 33           | N/A  | N/A     | No Connect. (must be left floating).                                                                                                                                         |  |  |  |  |  |

| AUXCS*    | 34           |      | TTL     | Auxiliary Chip Select. When programmed for aux ISA mode, primary and secondary addresses are ignored; AUXCS* and SAD[3:1] select specific registers.                         |  |  |  |  |  |

Digital Video Processor

# 2.2 Host Interface — MCA

| Signal   | Pin          | Туре | Cell    | Function                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|----------|--------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AD[15:0] | 48:62,<br>65 | 1/0  | TTL, 4  | Address/Data Bus. Bidirectional, multiplexed address/data bus that transfers video data and operation status and commands between the host system and the DVP.                                                                                                 |  |  |  |  |  |  |

| DEN*     | 44           | OD   | TTL, 8  | Data Buffer Enable.  O Enables the host data bus buffer.                                                                                                                                                                                                       |  |  |  |  |  |  |

| DDIR     | 43           | OD   | TTL, 8  | Data Buffer Direction. Specifies the direction of data flow on SAD[15:0].  The host system is reading data from SAD[15:0];  The host system is writing data to SAD[15:0].                                                                                      |  |  |  |  |  |  |

| S1*      | 35           | I    | TTL     | Status 1. Specifies current bus cycle (used with M/IO* and S0*).                                                                                                                                                                                               |  |  |  |  |  |  |

| S0*      | 36           | 1    | TTL     | Status 0. Specifies current bus cycle (used with M/IO* and S1*).                                                                                                                                                                                               |  |  |  |  |  |  |

| CDSFDBK* | 32           | 0    | TTL     | Memory or I/O Cycle. Specifies current bus cycle current bus cycle (used with S0* and S1*):  M/IO* S0* S1*  0                                                                                                                                                  |  |  |  |  |  |  |

| ·····    |              |      |         | and status inputs. The DVP does not drive CDSFDBK* low during the configuration period (CDSETUP* = 0).                                                                                                                                                         |  |  |  |  |  |  |

| CDSETUP* | 37           | I    | TTL     | Card Setup.  O Specifies that the host system is accessing the configuration registers of the MCA adapter.  To obtain adapter ID and configuration data (containing POS [Programmable Option Select] 100, 101, and 102), perform an I/O read cycle to the DVP. |  |  |  |  |  |  |

| IRQ      | 45           | 0    | TTL, 4  | Interrupt Request.  O The DVP is requesting service from the host system.                                                                                                                                                                                      |  |  |  |  |  |  |

| CDCHRDY  | 40           | OD   | TTL, 24 | Channel Ready.  The DVP is ready to complete the current host access cycle.                                                                                                                                                                                    |  |  |  |  |  |  |

| CDDS16*  | 39           | OD   | TTL, 24 | Card Data Size.  O The DVP is able to respond as a 16-bit I/O data device for both read and write cycles.                                                                                                                                                      |  |  |  |  |  |  |

July 1993

Digital Video Processor

# 2.2 Host Interface — MCA (cont.)

| Signal  | Pin | Type | Cell | Function                                                                                                                                                                           |

|---------|-----|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD*    | 41  | 1    | TTL  | Command.  O Valid data is on AD[15:0] (write cycle); or DVP should place valid data on AD[15:0] (read cycle).                                                                      |

| CDRESET | 42  | ı    | TTL  | Reset.  1 Stops all DVP activity and resets the hardware.                                                                                                                          |

| ADL*    | 33  | I    | TTL  | Address Latch.  O Demultiplexes the address from bus AD[15:0], and status from signals M/O*, S1*, and S0*. The address and status must be valid during the low-to-high transition. |

| CARDEN  | 34  | ŀ    | TTL  | Card Enable.  1 Specifies that the data on bus AD[15:8] is valid.                                                                                                                  |

# 2.3 Host Interface — Local Hardware

| Signal  | Pin          | Type | Cell    | Function                                                                                        |  |  |  |  |  |

|---------|--------------|------|---------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D[15:0] | 48:62,<br>65 | I/O  | TTL, 4  | Data Bus. Bidirectional data bus that transfers video data between the host system and the DVP. |  |  |  |  |  |

| RS[3:1] | 34:33,<br>44 | ı    | TTL     | Register Select. Specify the register address during a host access.                             |  |  |  |  |  |

| NC      | 43           | N/A  | N/A     | No Connect. (must be left floating).                                                            |  |  |  |  |  |

| IOR*    | 35           | I    | TTL     | VO Read. 0 Specifies an VO read cycle.                                                          |  |  |  |  |  |

| IOW*    | 36           | I    | TTL     | I/O Write. 0 Specifies an I/O write cycle.                                                      |  |  |  |  |  |

| CS*     | 32           | ı    | TTL     | Chip Select. 0 The host system is accessing the DVP.                                            |  |  |  |  |  |

| NC      | 38           | N/A  | N/A     | No Connect. (must be left floating).                                                            |  |  |  |  |  |

| NC      | 37           | N/A  | N/A     | No Connect. (must be left floating).                                                            |  |  |  |  |  |

| IRQ     | 45           | 0    | TTL, 4  | Interrupt Request.  O The DVP is requesting service from the host system.                       |  |  |  |  |  |

| CHRDY*  | 40           | OD   | TTL, 24 | Channel Ready.  O The DVP is ready to complete the current host access cycle.                   |  |  |  |  |  |

| NC      | 39           | N/A  | N/A     | No Connect. (must be left floating).                                                            |  |  |  |  |  |

Digital Video Processor

# 2.3 Host Interface — Local Hardware (cont.)

| Signal | Pin | Туре | Cell | Function                                                                                                         |

|--------|-----|------|------|------------------------------------------------------------------------------------------------------------------|

| PCLK   | 41  | 1    | TTL  | <b>Processor Clock.</b> Input clock that synchronizes the flow of data on bus D[15:0] during DMA data transfers. |

| RESET  | 42  | 1    | TTL  | Reset.  1 Stops all DVP activity and resets the hardware.                                                        |

# 2.4 Graphics Overlay Interface

| Signal  | Pin   | Type | Cell   | Function                                                                                                                                                                                                                                                                            |

|---------|-------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPCLK   | 69    | 1    | TTL    | <b>Graphics Pixel Clock.</b> Clocks display output pixel data from the graphics controller.                                                                                                                                                                                         |

| GVS     | 67    | I    | TTL    | Graphics Vertical Sync. Identifies the start of the vertical sync interval. A vertical sync pulse is generated once every field time for interlaced data, and once every frame time for non-interlaced data. Register DWU_MCR, bit GVSP specifies GVS as active high or active low. |

| GHS     | 66    | ı    | TTL    | Graphics Horizontal Sync. Identifies the start of the horizontal sync interval. A horizontal sync pulse is generated once for each input line. Register DWU_MCR, bit GHSP specifies GHS as active high or active low.                                                               |

| GBL     | 68    | I    | TTL    | Graphics Blanking. Identifies the blanking interval. Register DWU_MCR, bit GBP specifies GBL as active high or active low.                                                                                                                                                          |

| ZC[3:0] | 80:77 | 0    | TTL, 4 | Zoom Control Bus (used only with CL-PX2080 MediaDAC™).  Specifies to the MediaDAC™ the zoom factor to be used on the current data.                                                                                                                                                  |

Digital Video Processor

# 2.5 Video Interface

| Signal    | Pin                                                                         | Туре | Cell      | Function                                         | on                                                                                                                                                                                                                              |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------|------|-----------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| V1D[15:0] | 156,<br>153:141,<br>138:137                                                 | I/O  | TTL, 4    | V1 (Video Port 1)<br>Data Bus.                   | VnD[15:0]. Bidirectional data bus that transfers video data between the DVP and an external device through video port Vn.                                                                                                       |  |  |  |  |  |

| V2D[15:0] | 3:12, I/O TTL, 4 <b>V2 (Video Port 2)</b> 14:16, <b>Data Bus.</b> 19:20, 22 |      | port viii |                                                  |                                                                                                                                                                                                                                 |  |  |  |  |  |

| V1VS      | 1                                                                           | I/O  | TTL, 4    | V1 Vertical Sync.                                | VnVS. Identifies the start of the vertical                                                                                                                                                                                      |  |  |  |  |  |

| V2VS      | 27                                                                          | I/O  | TTL, 4    | V2 Vertical Sync.                                | sync interval. A vertical sync pulse is generated once every field time for interlaced data, and once every frame time for non-interlaced data. Register VIU_MCRp (bits OVSP/IVSP) specifies VnVS as active high or active low. |  |  |  |  |  |

| V1HS      | 160                                                                         | I/O  | TTL, 4    | V1 Horizontal Sync.                              | VnHS. Identifies the start of the horizon-                                                                                                                                                                                      |  |  |  |  |  |

| V2HS      | 26                                                                          | I/O  | TTL, 4    | V2 Horizontal Sync.                              | tal sync interval; register VIU_MCRp (bits OHSP/IHSP) specifies VnHS as active high or active low.                                                                                                                              |  |  |  |  |  |

| V1BL      | 159                                                                         | I/O  | TTL, 4    | V1 Horizontal/Composite Blanking.                | VnBL. Identifies the blanking interval;<br>register VIU_MCRp (bits OBP/IBP)<br>specifies VnBL as active high or active                                                                                                          |  |  |  |  |  |

| V2BL      | 25                                                                          | 1/0  | TTL, 4    | V2 Horizontal/Composite Blanking.                | low.                                                                                                                                                                                                                            |  |  |  |  |  |

| V1CLK     | 2                                                                           | l    | TTL       | V1 Data Clock.                                   | VnCLK. Clocks bidirectional video data on bus VnD[15:0].                                                                                                                                                                        |  |  |  |  |  |

| V2CLK     | 29                                                                          | I    | TTL       | V2 Data Clock.                                   |                                                                                                                                                                                                                                 |  |  |  |  |  |

| V1PH      | 158                                                                         | 1    | TTL, 4    | V1 Phase.                                        | VnPH. Controls data qualification and                                                                                                                                                                                           |  |  |  |  |  |

| V2PH      | 24                                                                          | ı    | TTL       | V2 Phase.                                        | duplexing of video data on VnD[15:0].                                                                                                                                                                                           |  |  |  |  |  |

| V1IEN*    | 157                                                                         | 0    | TTL, 4    | V1 Input Enable.                                 | VnIEN*. Specifies that the DVP is not                                                                                                                                                                                           |  |  |  |  |  |

| V2IEN*    | 23                                                                          | 0    | TTL, 4    | V2 Input Enable.                                 | driving bus VnD[15:0]. VnIEN* can be used as a tristate control by an external buffer connected to bus VnD[15:0].                                                                                                               |  |  |  |  |  |

| STALLRQ*  | 31                                                                          | I    | TTL       | Stall Request. 0 Requests that to V2D[15:0] be s | the current transfer of video data on bus uspended.                                                                                                                                                                             |  |  |  |  |  |

| STALL*    | 30                                                                          | 0    | TTL, 4    | Stali.<br>0 The DVP has s                        | uspended transferring data on V2D[15:0].                                                                                                                                                                                        |  |  |  |  |  |

### 2.6 Frame Buffer Interface

| Signal    | Pin                                                | Туре | Cell    | Function                                                                                                                                                                                                                                                     |

|-----------|----------------------------------------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBD[31:0] | 136:128,<br>125:109,<br>107:105,<br>102:101,<br>99 | I/O  | TTL, 4  | Frame Buffer Data Bus. Bidirectional data bus that transfers data between the DVP and the frame buffer.                                                                                                                                                      |

| FBA[9:0]  | 98:94,<br>92:88                                    | 0    | TTL, 8  | Frame Buffer Address Bus. Multiplexed output bus that specifies an address to the frame buffer. The row address is valid during the HIGH-to-LOW transition of signals RAS[1:0]*; the column address is valid during the high-to-low transition of CAS[1:0]*. |

| RAS[1:0]* | 87:86                                              | 0    | TTL, 8  | Row Address Strobes. Instruct the frame buffer to latch the row address from bus FBA[9:0] during the HIGH-to-LOW transition.                                                                                                                                 |

| CAS[1:0]* | 85:84                                              | 0    | TTL, 8  | Column Address Strobes. Instruct the frame buffer to latch the column address from bus FBA[9:0] during the HIGH-to-LOW transition.                                                                                                                           |

| WE*       | 83                                                 | 0    | TTL, 12 | Write Enable. Specifies a write cycle to the frame buffer.                                                                                                                                                                                                   |

| DTE*      | 82                                                 | 0    | TTL, 12 | Data Transfer Enable. Specifies a transfer cycle to the frame buffer (VRAMs only).                                                                                                                                                                           |

| FRDY      | 81                                                 | 1    | TTL     | FIFO Ready. (used only with CL-PX2080 MediaDAC™) Specifies that the input FIFO of the MediaDAC™ is ready to receive serial data from the frame buffer.                                                                                                       |

| SBCLK     | 76                                                 | 0    | TTL, 8  | <b>Serial Bus Clock.</b> Clocks serial data from the frame buffer (VRAMs only).                                                                                                                                                                              |

| SOE[1:0]* | 73:72                                              | 0    | TTL, 8  | Serial Port Output Enable.  0 Enable the frame-buffer serial data port output.                                                                                                                                                                               |

| MCLK      | 71                                                 | I    | TTL     | Memory Clock. Synchronizes all frame buffer control signals.                                                                                                                                                                                                 |

| FCLK      | 70                                                 | 0    | TTL, 8  | FIFO Write Clock. (used only with CL-PX2080 MediaDAC™) Clocks serial data into the MediaDAC™.                                                                                                                                                                |

# 2.7 Power and Ground

| Signal | Pin                                                       | Туре | Function                                                                                                            |

|--------|-----------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------|

| VDD    | 18, 21, 46, 64, 75,<br>100, 103, 126,<br>140, 155         | PWR  | +5 VDC for Digital Logic and Interface Buffers. Each VDD pin must be connected directly to the VDD plane.           |

| VSS    | 13, 17, 28, 47, 63,<br>74, 93, 104, 108,<br>127, 139, 154 | PWR  | <b>Ground for Digital Logic and Interface Buffers.</b> Each VSS pin must be connected directly to the ground plane. |

July 1993

July 1993

20

Digital Video Processor

# **DETAILED REGISTER DESCRIPTIONS**

This section lists and defines the CL-PX2070 DVP registers.

NOTE:

In order to maintain compatibility with future Pixel Semiconductor products, all reserved registers bits must be written as '0'. Data values in reserved register locations are not guaranteed on readback.

Register names containing lower-case variables represent groups of registers with similar functions. Refer to the Conventions table on page 8 for a list of DVP register variables.

#### 4.1 HIU: Host Interface Unit

## Table 4-1. HIU Register Address Map

| Register | Pri.<br>Map | Sec.<br>Map                 | Definition             | Used by I                     | Ref. Section                                       |                                              |  |

|----------|-------------|-----------------------------|------------------------|-------------------------------|----------------------------------------------------|----------------------------------------------|--|

| HIU_0    | 27C0        | 0290 Register I/O Address 0 |                        | HIU_CSU<br>HIU_DBG<br>HIU_DRD | Configuration Setup<br>Debug Control<br>Debug Read | 4.1.1, p. 23<br>4.1.2, p. 24<br>4.1.3, p. 24 |  |

| HIU_1    | 27C2        | 0292                        | Register I/O Address 1 | HIU_OCS<br>HIU_IRQ            | Operation Control/Status<br>Interrupt Request      | 4.1.5, p. 26<br>4.1.4, p. 25                 |  |

| HIU_2    | 27C4        | 0294                        | Register I/O Address 2 | HIU_RIN                       | Register Index                                     | 4.1.6, p. 27                                 |  |

| HIU_3    | 27C6        | 0296                        | Register I/O Address 3 | HIU_RDT                       | Register Data Port                                 | 4.1.7, p. 28                                 |  |

| HIU_4    | 27C8        | 0298                        | Register I/O Address 4 | HIU_MDT                       | Memory Data Port                                   | 4.1.8, p. 28                                 |  |

#### Table 4-2. HIU Registers Accessed by the Register Data Port

| Register | Index | Definition      | Ref. Section |

|----------|-------|-----------------|--------------|

| HIU_ISU  | 0001  | Interrupt Setup | 4.1.9, p. 29 |

Digital Video Processor

#### HIU\_CSU: Configuration Setup

I/O Address

27C0 (Primary Map)

0290 (Secondary Map)

HIU\_CSU is a read-only register that stores hardware configuration data for the DVP. An external configuration register must provide configuration data to bits 5:0 during the reset interval. HIU\_CSU is shadowed by registers HIU\_DBG and HIU\_DRD.

| 15 | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5 | 4   | 3 | 2    | 1   | 0   |

|----|------|----|----|----|----|---|---|----|----|---|-----|---|------|-----|-----|

|    | RSVD |    |    |    | VE | R |   | RS | VD |   | HSB |   | RSVD | FBT | PAS |

| Bit # | Access | Reset | Description |                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-------|--------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 15:12 | R      | 0000  | RSVD        | Reserved (read as '0').                                                                                                                                                                                                                |  |  |  |  |  |  |

| 11:8  | R      | 0000  | VER         | DVP Device Version 0000 CL-PX2070 revision AB 0001 CL-PX2070, revision AC                                                                                                                                                              |  |  |  |  |  |  |

| 7:6   | R      | 00    | RSVD        | Reserved (read as '00')                                                                                                                                                                                                                |  |  |  |  |  |  |

| 5:3   | R      | 111   | HSB         | Host System Bus. Specifies the type of host system connected to the DVP.  OOO ISA bus OO1 MCA bus O10 Reserved O11 Local hardware interface 100 Aux ISA 101 Aux MCA 111 Local hardware interface XXX All other configurations reserved |  |  |  |  |  |  |

| 2     | R      | 1     | RSVD        | Reserved (read as 1)                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 1     | R      | 1     | FBT         | Frame Buffer Jumper State. (Used only for software configuration. Does not affect internal DVP operation.)  O DRAM  1 VRAM                                                                                                             |  |  |  |  |  |  |

| 0     | R      | 0     | PAS         | Port Address Select. Specifies the I/O address map that the host system should use when accessing the DVP.  O Primary port map  Secondary port map                                                                                     |  |  |  |  |  |  |

July 1993

65E D

9003364 0000086 525 PIXL

CL-PX2070

Digital Video Processor

# 4.1.2 HIU\_DBG: Debug Control

I/O Address

27C0 (Primary Map)

0290 (Secondary Map)

HIU\_DBG is a write-only register that controls the diagnostic mode of the DVP. Register HIU\_OCS, field MDE enables access to this register when set to '1.' HIU\_DBG is shadowed by register HIU\_DRD.

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|---|----|----|----|----|----|----|-----|---|---|---|---|------|---|---|---|---|

| Г |    |    | RS | VD |    |    | DRE |   |   |   |   | RSVD |   |   |   |   |

| Bit#  | Access | Reset | Descrip | otion                                                                                                    |

|-------|--------|-------|---------|----------------------------------------------------------------------------------------------------------|

| 15:10 | w      | 0h    | RSVD    | Reserved (read as '0').                                                                                  |

| 9     | W      | 0     | DRE     | Debug Read Enable. Enables access to shadow register HIU_DRD.  O Disable debug read  1 Enable debug read |

| 8:0   | w      | 00h   | RSVD    | Reserved (read as '0').                                                                                  |

# 4.1.3 HIU\_DRD: Debug Read

I/O Address

27C0 (Primary Map)

0290 (Secondary Map)

See also:

HIU DBG: Debug Control, p. 24

HIU\_OCS: Operation Control/Status, p. 26

SIU\_MCR: SIU Master Control, p. 58

SIUs SIM: Sequencer Instruction Memory, p. 61

HIU DRD is a read-only register that provides diagnostic information, including the global Error Detection Trap, the current object buffer counters, and the SIU current index. HIU\_DRD is a shadow register to HIU\_CSU. Read access to this register is enabled when HIU\_OCS, field MDE and HIU\_DBG, field DRE are set to '1.'

| 15  | 14 | 13    | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2     | 1 | 0 |

|-----|----|-------|----|----|----|---|---|----|---|---|---|---|-------|---|---|

| EDT |    | ***** | XC |    |    |   |   | YÇ |   |   |   | - | SIMIN |   |   |

| Bit # | Access | Reset | Description |                                                                                                                                                  |  |  |  |  |  |  |  |