# EMULEX MICRO DEVICES FAST ARCHITECTURE SCSI CHIP

FAS216/226/236 \*

#### **FEATURES**

- ☐ For Host Applications and 16-bit Peripheral Applications

- ☐ Supports ANSI X3T9.2 SCSI Standard, with SCSI-2 Fast Timing Requirements

- ☐ Asynchronous Data Transfer up to 7 MB/sec

- ☐ Synchronous Data Transfers up to 5 MB/sec and 10 MB/sec FAST

- Programmable Synchronous Transfer Period

- Programmable Synchronous Transfer Offsets up to 15 Bytes

- ☐ 24-Bit Transfer Counter

- ☐ Functions as Initiator or Target

- ☐ Up to 20 MB/sec DMA Burst Transfer Rate (10 Megatransfers Per Second)

- → Pipelined Command Structure

- ☐ 16 Byte Data FIFO Between the DMA and SCSI Channels

- ☐ Implements SCSI Sequences without Microprocessor Intervention

- Parity Pass-Through on FIFO Data

- ☐ Part Unique ID Code

- ☐ On-Chip 48 mA Single-Ended SCSI Transceivers

- ☐ Interrupts Microprocessor Only When Service is Required

- □ Packaging

- 216 84 PLCC

- 226 84 PLCC

- 236 100 PQFP

- \* FAS216 will refer to FAS226 and FAS236 except as noted

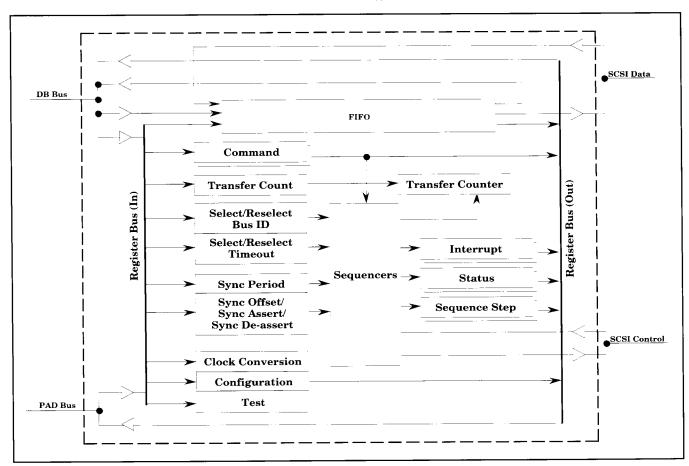

Figure 1. FAS216 Block Diagram Mode 2/3

#### PRODUCT DESCRIPTION

The FAS216, FAS226, and FAS236 are new additions to the Emulex SCSI Processor (ESP) chip family with features designed to facilitate SCSI-2 support. The major new feature of the FAS chip is its ability to transfer synchronous data at 10 Mbytes per second. The current 5 Mbytes per second transfer rate is also supported on-chip by setting a register. Asynchronous transfers up to 7 Mbytes per second are supported as well.

Of the three versions of the chip, the FAS216 supports single-ended operations; the FAS226 supports differential only; and the FAS236 supports both single-ended and differential operations. Since the FAS216 operates in both the Initiator and Target roles, it can be used in both host and peripheral applications. The chip performs such functions as bus arbitration, selection of a target, or reselection of an initiator. The FAS216 also handles message, command, status, and data transfers between the SCSI Bus and its internal FIFO or a buffer memory.

The chip maximizes protocol efficiency by utilizing a first-in, first-out command pipeline and combination commands to minimize host intervention. The FAS216 also maximizes transfer rates by sustaining asynchronous data rates up to 7 MB/sec and, in the FAST SCSI mode, synchronous data rates up to 10 MB/sec.

The FAS216 controller systems support three main busses: the 8-bit SCSI Bus, the 8-bit or 16-bit Data Bus (DB), and the 8-bit Processor Address (PAD) bus. This versatile split-bus architecture separates the two high traffic information flows of the system, providing maximum efficiency and throughput. Figure 1 shows the internal architecture of the FAS216.

The FAS216 replaces existing SCSI interface circuitry which typically consists of discrete devices, external drivers, and a low performance SCSI interface chip. It contains a fast DMA interface, a 16-byte FIFO, and fast asynchronous and synchronous data interfaces to the SCSI Bus, including drivers.

The FAS216 has been optimized for interaction with the controller processor. Common SCSI bus sequences that would typically require significant amounts of time have been reduced to single commands. The commands are:

| Sequence                         | Description                                                                                                                                                    |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Selection                        | Arbitration, target selection,<br>transmission of optional 1- or 3-<br>byte message followed by mul-<br>tiple-byte command                                     |

| Reselection                      | Arbitration, initiator reselection,<br>and transmission of a 1-byte<br>message                                                                                 |

| Bus-initiated<br>Selection       | Transmission of selection bus ID,<br>a 1-byte Identify or null message,<br>a 2-byte Queue Tag Message (if<br>SCSI-2 mode), followed by<br>Command Phase bytes. |

| Bus-initiated<br>Reselection     | Reselection detection and receipt of a 1-byte message.                                                                                                         |

| Target Command<br>Complete       | Transmission of a status byte and a 1-byte message.                                                                                                            |

| Target<br>Disconnect<br>Sequence | Transmission of two 1-byte<br>messages followed by disconnec-<br>tion from the SCSI bus                                                                        |

| Initiator<br>Command<br>Complete | Receipt of a status byte and a<br>1-byte message                                                                                                               |

#### SYSTEM ORGANIZATION

The FAS216 chip provides the host with a complete SCSI interface. An 8-bit microprocessor bus (PAD) provides access to all internal registers and an 18-bit DMA bus (DB) provides a path for DMA transfers through the FIFO.

The versatile architecture supports various microprocessor and DMA bus configurations such as the following:

- ☐ Microprocessor interface via the PAD bus or the DB

- → PAD bus selectable as data-only bus or as a multiplexed address and data bus

- ☐ DB bus selectable for 8-bit transfers, 16-bit transfers with byte control

Page 2

FAS216 bus configuration is selected by pulling the MODE1 and MODE0 signals up or down, as shown in Table 1.

| Mode | Mo | de | Regi   | ster    |                                                     |

|------|----|----|--------|---------|-----------------------------------------------------|

| No.  | 1  | 0  | Addr   | Data    | Register                                            |

| 0    | 0  | 0  | A3-0   | DB Bus  | Single-bus,<br>8-bit DMA                            |

| 1    | 0  | 1  | A3-0   | DB Bus  | Single-bus,<br>16-bit DMA                           |

| 2    | 1  | 0  | PAD3-0 | PAD Bus | Split-bus,<br>16-bit DMA,<br>byte control<br>option |

| 3    | 1  | 1  | PAD3-0 | PAD Bus | Split-bus,<br>16-bit DMA                            |

**Table 1. Bus Configuration**

#### PROCESSOR INTERFACE

The processor can interface to the FAS216 using either the PAD bus or the DB bus. Both interfaces allow the processor to read and write to all chip registers, including the FIFO. The PAD bus allows the processor interface to the chip registers independent of DMA activity on the DB bus. All register accesses are 8-bits wide.

#### **DMA INTERFACE**

The FAS216 DMA logic transfers data to and from a buffer over the DB bus, which may be configured as either 8-bit or 16-bit.\* If byte control mode is enabled, an external DMA controller can control how the bytes are placed on the bus.

#### **SIGNALS**

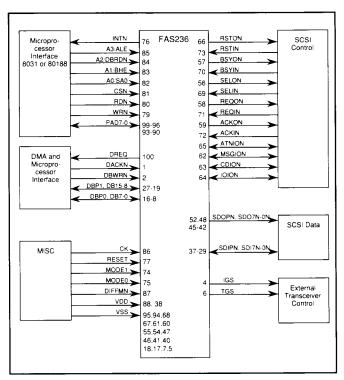

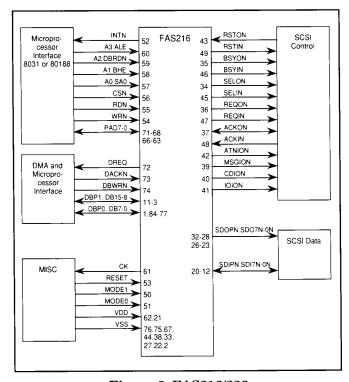

The FAS216 acts as the interface between the microprocessor and the SCSI Bus, in either the target or initiator mode. Refer to Figure 2 (FAS216/226 Functional Signal Grouping) and Figure 3 (FAS236 Functional Signal Grouping) which show which pins interface with the microprocessor and which interface with the SCSI Bus.

Figure 2. FAS236

Functional Signal Grouping

Figure 3. FAS216/226 Functional Signal Grouping

<sup>\*</sup> Each byte on the bus has its own parity.

#### **PACKAGING**

The FAS216 and FAS226 chips are available in an 84-pin PLCC for surface or socket mounting. The FAS236 is available in a 100-pin plastic quad flat pack (PQFP).

#### PIN DESCRIPTION

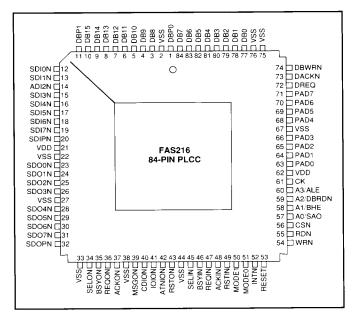

Figure 4 shows the signal names with each pin of the FAS216/226 84-pin PLCC. The diagram is viewed from the top of the chip, with the pins facing away from the reader. The pins for the FAS216 and 226 are identical, with the exception of pins 75 and 76. Pins

75 and 76 in FAS216 are VSS; in the FAS226, pin 75 is IGS and pin 76 is TGS.

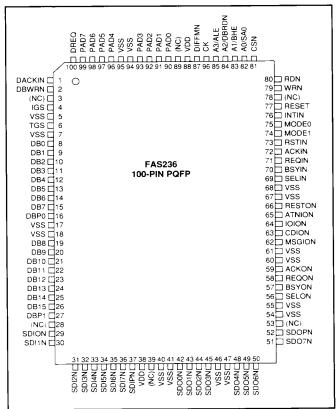

Figure 5 shows the signal name associated with each pin of the FAS236 100-pin PQFP. The diagram is viewed from the top of the chip, with the pins facing away from the reader.

#### REGISTERS

The FAS216 registers are used by the microprocessor to control the operation of the SCSI bus. Through these registers, the microprocessor can configure, command, monitor, and pass through the chip to the SCSI bus. These registers are listed in Table 2.

#### **FAS216 FEATURES/BENEFITS**

| Features:                                          | Benefits:                                                                                                                       |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| ☐ Low SCSI Bus overhead                            | ☐ Allows sharing of the SCSI Bus with more peripherals, more efficient bus utilization, fast delivery of information to host    |

| ☐ Fast synchronous SCSI data transfers (10 MB/sec) | ☐ Can transfer data twice as fast as normal SCSI                                                                                |

| □ SCSI-2 command support                           | ☐ Allows the option of utilizing new SCSI commands                                                                              |

| □ SCSI-2 feature selectability                     | ☐ Backward-compatible with existing chips, so SCSI-<br>2 features can be selected when necessary                                |

| ☐ Parity pass-through                              | ☐ Maintains data integrity all the way through the chip directly into the buffer                                                |

| ☐ Separate microprocessor and DMA busses           | During data transfer, the microprocessor has<br>instant access to status and has the ability to<br>execute commands             |

| □ 16-bit DMA Channel                               | ☐ High-speed information flow can be handled with<br>the split-bus architecture to provide maximum<br>efficiency and throughput |

|                                                    |                                                                                                                                 |

Page 4 EMULEX MICRO DEVICES

Figure 4. FAS216 84-Pin PLCC Designations

Figure 5. FAS236 100-Pin PQFP Designations

| FAS216<br>Address<br>(BFxx or<br>FExx) | Register Name           | Туре         | FAS216<br>Address<br>(BFxx or<br>FExx) | Register Name         | Туре |

|----------------------------------------|-------------------------|--------------|----------------------------------------|-----------------------|------|

| 00                                     | Transfer Counter Low    | R            | 07                                     | FIFO Flags            | R    |

|                                        | Transfer Count Low      | W            |                                        | Synchronous Offset    | W    |

| 01                                     | Transfer Counter Mid    | $\mathbf{R}$ | 08                                     | Configuration #1      | R/W  |

|                                        | Transfer Count Mid      | W            | 09                                     | Clock Conversion      | W    |

| 02                                     | FIFO                    | R/W          |                                        | Factor                |      |

| 03                                     | Command                 | R/W          | 0A                                     | Test                  | W    |

| 04                                     | Status                  | R            | 0B                                     | Configuration #2      | R/W  |

|                                        | Select/Reselect Bus ID  | W            | OC.                                    | Configuration #3      | R/W  |

| 05                                     | Interrupt               | R            | 0E                                     | Transfer Counter High | R    |

|                                        | Select/Reselect Timeout | W            | 1                                      | Transfer Count High   | W    |

| 06                                     | Sequence Step           | R            | 0F                                     | FIFO Bottom           | W    |

|                                        | Synch Transfer Period   | W            |                                        |                       |      |

Table 2. FAS216 Registers

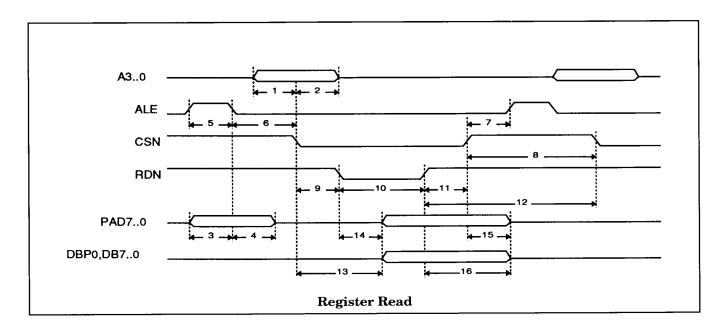

#### **AC TIMING**

The following figures and table values that accompany them are illustrative of the FAS216 chip timing characteristics. For more information, see the FAS216/226/236 Technical Manual, VLSI51007-00 .

#### Register Interface Timing (In ns)

| #                                    | Symbol                                                                           | Description                                                                                                                                       | Min                                         | Max | Note                                 |

|--------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|--------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | T RASC<br>T RAHC<br>T RALSA<br>T RALHA<br>T RALD<br>T RALSC<br>T RALHC<br>T RCCY | Address Setup to CSN Address Hold from CSN Address Setup to ALE Address Hold from ALE ALE Pulse Width ALE to CSN ALE from CSN CSN High to CSN Low | 0<br>30<br>10<br>10<br>20<br>10<br>50<br>30 |     | 1<br>1<br>2<br>2<br>2<br>2<br>2<br>2 |

#### **Read Cycle**

| #                                     | Symbol                                                              | Description                                                                                                                                                   | Min                          | Max                  | Note  |

|---------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------|-------|

| 9<br>10<br>11<br>12<br>13<br>14<br>15 | TRCSR<br>TRRD<br>TRCHR1<br>TRCHR2<br>TRDC<br>TRDR<br>TRDHC<br>TRDHC | CSN Low to RDN Low RDN Pulse Width RDN High to CSN High RDN High to CSN Low CNS Low to Data RDN Low to Data CSN High to Data Release RDN High to Data Release | 0<br>30<br>0<br>40<br>2<br>2 | 65<br>30<br>30<br>30 | 3 3 4 |

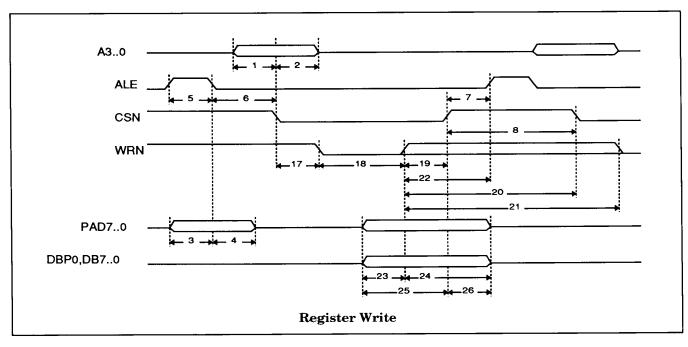

#### **Write Cycle**

| #                                       | Symbol             | Description             | Min | Max | Note       |

|-----------------------------------------|--------------------|-------------------------|-----|-----|------------|

| 17                                      | TCSW               | CSN Low to WRN Low      | 0   |     | <b>5</b> C |

| 18                                      | TRWR               | WRN Pulse Width         | 30  |     | 5,6        |

| 19                                      | TRCHW              | WRN High to CSN High    | 0   |     | 5,6        |

| 20                                      | TRWH               | WRN High to CSN Low     | 30  |     | 6          |

| 21                                      | TRWCY              | WRN High to WRN Low     | 40  |     | 6          |

| $\frac{1}{22}$                          | TRAHW              | WRN High to ALE         | 50  |     | 2,6        |

| 23                                      | TRDW               | Data Setup to WRN High  | 15  |     | 6,7        |

| $\begin{array}{c} 24 \\ 25 \end{array}$ | $\frac{T}{T}$ RDHW | Data Hold from WRN High | 0   |     | 6,8        |

|                                         | $\frac{T}{T}$ RDWC | Data Setup to CSN High  | 10  |     | 7          |

| 26                                      | T RDHWC            | Data Hold from CSN High | 30  |     | 8          |

#### Notes:

- 1. Bus Configuration modes #0, #1, and #3 only.

- 2. Bus configuration mode #2 only (multiplexed address and data mode).

- 3. Both <sup>T</sup>RDC and <sup>T</sup>RDR specifications must be met.

- 4. RDN edges may precede or follow CSN edges.

- 5. WRN edges may precede or follow CSN edges.

- 6. In Bus Configuration modes #0 and #1, WRN must be tied to DBWRN.

- 7. Either TRDW or TRDWC specification must met.

- 8. Either TRDHW or TRDHWC specification must met.

Page 6

Figure 6. Register Access

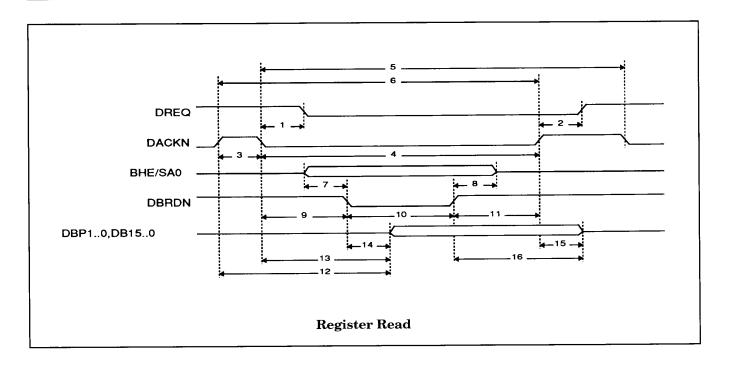

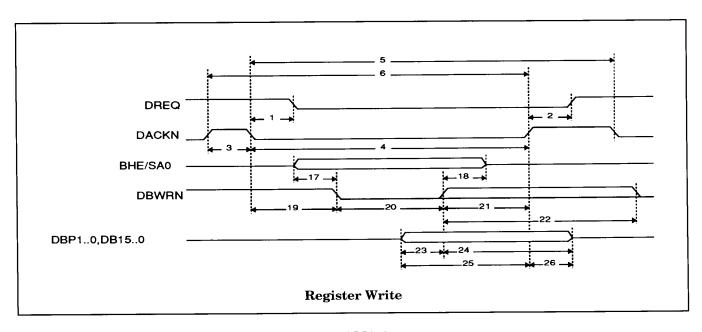

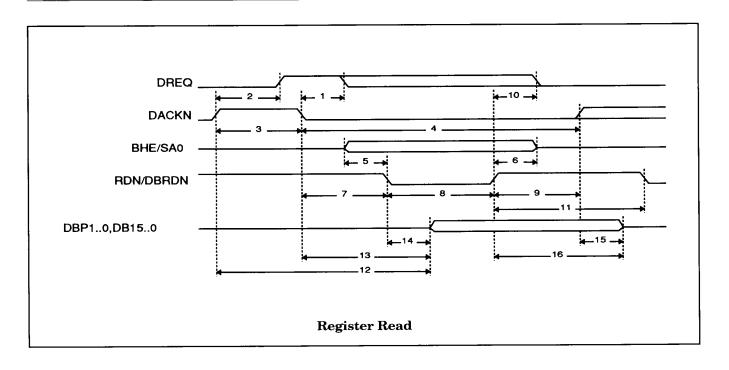

### DMA Interface Timing (In ns)

| #                          | Symbol                                  | Description                                                                                                                             | Min                           | Max      | Note         |

|----------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------|--------------|

| 1<br>2<br>3<br>4<br>5<br>6 | T DARL T DRH T DACY T ACK T ACP0 T ACP1 | DACKN Low to DREQ Low DACKN High to DREQ High DACKN High to DACKN Low DACKN Pulse Width DACKN Low to DACKN Low DACKN High to DACKN High | 12<br>45<br>95<br>T CS<br>+25 | 30<br>30 | 1<br>2<br>12 |

#### **Read Cycle**

| #  | Symbol             | Description                  | Min             | Max | Note       |

|----|--------------------|------------------------------|-----------------|-----|------------|

| 7  | TDBSSR             | BHE/SA0 Setup to DBRDN Low   | 20              |     | 9.4        |

| 8  | T DBSHR            | BHE/SA0 Hold from DBRDN High | $\frac{20}{20}$ |     | 3,4<br>3,4 |

| 9  | l <sup>T</sup> DAR | DACKN Low to DBRDN Low       | 0               |     | 3,6        |

| 10 | TDRD               | DBRDN Pulse Width            | 35              |     | 3          |

| 11 | TDRA               | DBRDN High to DACKN High     | 0               |     | 3,7        |

| 12 | T DDAH             | DACKN High to Data           | 45              |     | 5          |

| 13 | TDDAL              | DACKN Low to Data            | 30              |     | 5          |

| 14 | TDDRL              | DBRDN Low to Data            | 35              |     | 3,5        |

| 15 | TDADR              | DACKN High to Data Release   | 2               | 25  | <b>1</b>   |

| 16 | T DRDR             | DBRDN High to Data Release   | 2               | 35  | 3          |

|    |                    |                              | Į.              |     |            |

#### **Write Cycle**

| #                                                        | Symbol                                                                    | Description                                                                                                                                                                                                                                             | Min                                             | Max | Note                                         |

|----------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|----------------------------------------------|

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | T DBSSW T DBSHW T DAW T DWR T DWA T DWCY T DDW T DHW T DDWA T DHWA T DHWA | BHE/SA0 Setup to DBWRN Low BHE/SA0 Hold from DBWRN High DACKN Low to DBWRN Low DBWRN Pulse Width DBWRN High to DACKN High DBWRN High to DBWRN Low Data Setup to DBWRN High Data Hold from DBWRN High Data Setup to DACKN High Data Hold from DACKN High | 20<br>20<br>0<br>30<br>0<br>25<br>15<br>0<br>10 |     | 3,4<br>3,4<br>8<br>9<br>10<br>11<br>10<br>11 |

#### Notes:

- 1. Negation pending.

- 2. Assertion pending.

- Bus configuration mode #2 only. 3.

- Byte control mode only. 4.

- TDDAH and TDDAL specifications must be met. 5.

- 6. DBRDN low may precede DACKN low.

- 7. DBRDN low may follow DACKN high.

- 8. DBWRN low may precede DACKN low.

- 9.

- 10.

- DBWRN low may follow DACKN high.

Either <sup>T</sup>DDW or <sup>T</sup>DDWA specification must be met.

Either <sup>T</sup>DHW or <sup>T</sup>DHWA specification must be met. 11.

- 12. Synchronous transfers only.

Page 8

Figure 7. DMA Access

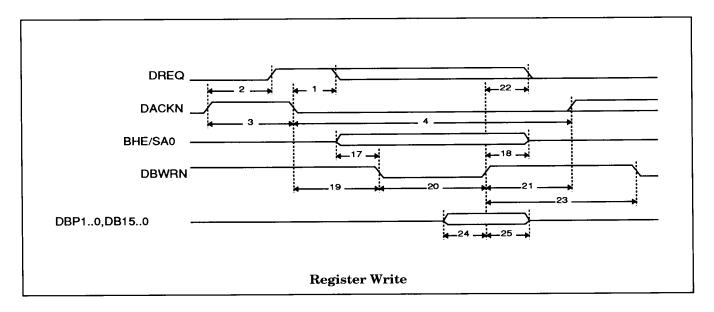

# Alternate DMA Interface Timing (In ns)

| #                | Symbol                             | Description                                                                                      | Min      | Max      | Note |

|------------------|------------------------------------|--------------------------------------------------------------------------------------------------|----------|----------|------|

| 1<br>2<br>3<br>4 | T DARL<br>T DRH<br>T DACY<br>T ACK | DACKN Low to DREQ Low<br>DAKCN High to DREQ High<br>DACKN High to DACKN Low<br>DACKN Pulse Width | 60<br>70 | 30<br>30 | 1,10 |

#### **Read Cycle**

| _ [                                            |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                      | Max      | Note                                                                    |

|------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------|-------------------------------------------------------------------------|

| 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | T DBSSR T DBSHR T DAR T DRD T DRA T DRRL T DRACY T DDAH T DDAL T DDRL T DADR T DADR T DADR | BHE/SA0 Setup to RDN/DBRDN Low<br>BHE/SA0 Hold from RDN/DBRDN High<br>DACKN Low to RDN/DBRDN Low<br>RDN/DBRDN Pulse Width<br>RDN/DBRDN High to DACKN High<br>RDN/DBRDN High to DREQ Low<br>RDN/DBRDN High to RDN/DBRDN Low<br>DACKN High to Data<br>DACKN Low to Data<br>RDN/DBRDN Low to Data<br>RDN/DBRDN Low to Data<br>DACKN High to Data Release<br>RDN/DBRDN High to Data Release | 20<br>20<br>0<br>70<br>0<br>90<br>60<br>45<br>35<br>55 | 25<br>45 | 3,4<br>3,4<br>6,12<br>12<br>7,12<br>1,11,12<br>11, 12<br>5<br>5<br>5,12 |

#### **Write Cycle**

| #                                                  | Symbol                                                      | Description                                                                                                                                                                                                                 | Min                                        | Max | Note                             |

|----------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|----------------------------------|

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25 | T DBSSW T DBSHW T DAW T DWR T DWA T DWRL T DWCY T DDW T DHW | BHE/SA0 Setup to DBWRN Low BHE/SA0 Hold from DBWRN High DACKN Low to DBWRN Low DBWRN Pulse Width DBWRN High to DACKN High DBWRN High to DREQ Low DBWRN High to DBWRN Low Data Setup to DBWRN High Data Hold from DBWRN High | 20<br>20<br>0<br>70<br>0<br>90<br>60<br>15 |     | 3,4<br>3,4<br>8<br>9<br>11<br>11 |

#### Notes:

- 1. Negation pending.

- 2. Assertion pending.

- 3. Bus configuration mode #2 only.

- 4. Byte control mode only.

- 5. TDDAH and TDDAL specifications must be met.

- 6. RDN/DBRDN low may precede DACKN low.

- 7. RDN/DBRDN high may follow DACKN high.

- 8. DBWRN low may precede DACKN low.

- 9. DBWRN high may follow DACKN high.

- 10. Single DMA transfers only.

- 11. Multiple DMA transfers only.

- 12. The DMA Read line is defined as RDN in Bus Configuration Modes #0 and #1, and as DBRDN in Bus Configuration Mode #2. In Bus Configuration Mode #3 there is no DMA read line, and DACKN must toggle for each DMA read cycle.

Page 10

Figure 8. Alternate DMA Access

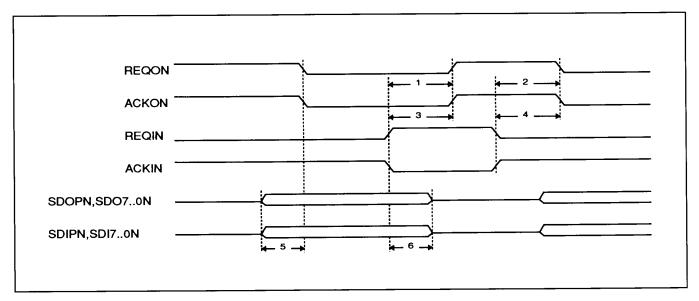

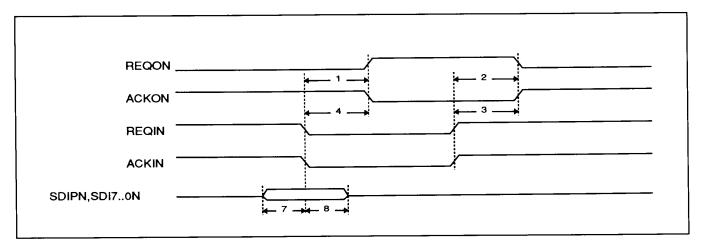

#### **SCSI Asynchronous Timing**

#### SINGLE-ENDED MODE<sup>1</sup>

| #                | Symbol                                   | Description                                                                                             | Min | Max                  | Note       |

|------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|----------------------|------------|

| 1<br>2<br>3<br>4 | T AAR01<br>T AAR02<br>T ARA01<br>T ARA02 | ACKINLow to REQON High<br>ACKIN High to REQON Low<br>REQIN High to ACKON High<br>REQIN Low To ACKON Low |     | 50<br>45<br>50<br>50 | 3,6<br>4,6 |

#### **Output Cycle**

| #                | Symbol                                   | Description                                                                                                 | Min                | Max | Note   |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------|-----|--------|

| 5<br>5<br>6<br>6 | T ARDSO<br>T AADSO<br>T ARHDO<br>T AAHDO | Data Setup to REQON Low<br>Data Setup to ACKON Low<br>Data Hold from REQIN High<br>Data Hold from ACKIN Low | 60<br>60<br>5<br>5 |     | 5<br>5 |

#### DIFFERENTIAL MODE<sup>2</sup>

| #                | Symbol                                   | Description                                                                                              | Min | Max                  | Note       |

|------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|----------------------|------------|

| 1<br>2<br>3<br>4 | T AAR01<br>T AAR02<br>T ARA01<br>T ARA02 | ACKIN Low to REQON High<br>ACKIN High to REQON Low<br>REQIN High to ACKON High<br>REQIN Low to ACKON Low |     | 30<br>30<br>25<br>30 | 3,6<br>4,6 |

#### **Output Cycle**

| #                | Symbol                                   | Description                                                                                                 | Min                | Max | Note   |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------|-----|--------|

| 5<br>5<br>6<br>6 | T ARDSO<br>T AADSO<br>T ARHDO<br>T AAHDO | Data Setup to REQON Low<br>Data Setup to ACKON Low<br>Data Hold from REQIN High<br>Data Hold from ACKIN Low | 70<br>70<br>5<br>5 |     | 5<br>5 |

#### Input Cycle

| #                | Symbol                                   | Description                                                                                                | Min | Max      | Note |

|------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|----------|------|

| 7<br>7<br>8<br>8 | T ARDSI<br>T AADSI<br>T ARHDI<br>T AAHDI | Data Setup to REQIN Low<br>Data Setup to ACKIN Low<br>Data Hold from REQIN Low<br>Data Hold from ACKIN Low | 0 0 | 18<br>18 |      |

#### Notes:

- 1. 200pF loading, data out on lines SDOPN, SDO7N-0N.

- 2. Data out on lines SDIPN, SDI7N-0N.

- 3. TARDSO specification must also be met (output cycle only).

- 4. TAADSO specification must also be met (output cycle only).

- 5. FIFO is not empty.

- 6. FIFO is not full (input cycle only).

Page 12

Figure 9. SCSI Asynchronous Timing

Figure 10. SCSI Asynchronous Input

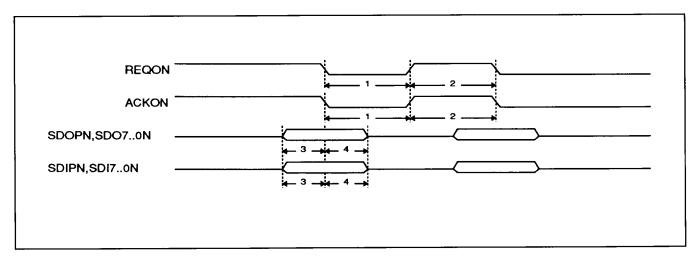

#### SCSI Synchronous Timing (In ns)

#### OUTPUT CYCLE Normal SCSI, Single-Ended Mode<sup>1</sup>

| # | Symbol  | Description                        | Min | Max |

|---|---------|------------------------------------|-----|-----|

| 1 | T SASTO | REQON/ACKON Assertion Period       | 90  |     |

| 2 | T SNEGO | REQON/ACKON Negation Period        | 90  |     |

| 3 | T SDSO  | Data Setup to REQON Low/ACKON Low  | 55  |     |

| 4 | T SHIDO | Data Hold from REQON Low/ACKON Low | 100 |     |

# Normal SCSI, Differential Mode $^2$

| # | Symbol  | Description                        | Min | Max |

|---|---------|------------------------------------|-----|-----|

| 1 | T SASTO | REQON/ACKON Assertion Period       | 96  |     |

| 2 | T SNEGO | REQON/ACKON Negation Period        | 96  |     |

| 3 | T SDSO  | Data Setup to REQON Low/ACKON Low  | 65  |     |

| 4 | T SHDO  | Data Hold from REQON Low/ACKON Low | 110 |     |

## FAST SCSI, Single-Ended Mode<sup>3</sup>

| # | Symbol  | Description                        | Min | Max |

|---|---------|------------------------------------|-----|-----|

| 1 | T SASTO | REQON/ACKON Assertion Period       | 30  |     |

| 2 | T SNEGO | REQON/ACKON Negation Period        | 30  |     |

| 3 | T SDSO  | Data Setup to REQON Low/ACKON Low  | 25  |     |

| 4 | T SHDO  | Data Hold from REQON Low/ACKON Low | 35  |     |

#### FAST SCSI, Differential Mode 4

| # | Symbol  | Description                        | Min | Max |

|---|---------|------------------------------------|-----|-----|

| 1 | T ASTO  | REQON/ACKON Assertion Period       | 40  |     |

| 2 | T SNEGO | REQON/ACKON Negation Period        | 40  |     |

| 3 | T SDSO  | Data Setup to REQON Low/ACKON Low  | 35  |     |

| 4 | T SHDO  | Data Hold from REQON Low/ACKON Low | 45  |     |

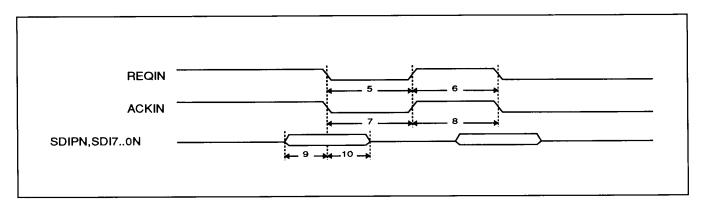

#### INPUT CYCLE

| #                           | Symbol                                                           | Description                                                                                                                                                                          | Min                                   | Max |

|-----------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|

| 5<br>6<br>7<br>8<br>9<br>10 | T SRASTI<br>T SRNEGI<br>T SAASTI<br>T SANEGI<br>T SDSI<br>T SHDI | REQIN Assertion Period REQIN Negation Period ACKIN Assertion Period ACKIN Negation Period ACKIN Negation Period Data Setup to REQIN Low/ACKIN Low Data Hold from REQIN Low/ACKIN Low | 27<br>20<br>20<br>20<br>20<br>5<br>15 |     |

#### Notes:

- 1. 5MBytes/sec max., data out on lines SDOPN, SDO7N-0N

- 2. 5MBytes/sec max., data out on lines SDIPN, SDI7N-0N

- 3. 10MBytes/sec max., data out on lines SDOPN, SDO7N-0N

- 4. 10MBytes/sec max., data out on lines SDIPN, SDI7N-0

Page 14

Figure 11. SCSI Synchronous Output

Figure 12. SCSI Synchronous Input

**NOTES:**

#### Emulex is a registered trademark of Emulex Corporation

Emulex Corporation, 3545 Harbor Blvd., Costa Mesa, CA 92626, (800) EMULEX-3 or (714) 662-5600 in California North America Offices: Anaheim, CA (714) 385-1685; San Jose, CA (408) 452-4777;

Rosewell, GA (404) 587-3610; Burlington, MA (617) 229-8880; Saddle Brook, NJ (201) 368-9400; Houston, TX (713) 981-6824; Reston, VA (703) 264-0670; Schaumburg, IL (708) 605-0888

$International\ Offices:\ Workingham\ (44)\ 71-4772929;\ Munich\ (49)\ 89-3608020;\\ Sydney\ (02)\ 417-8585;\ Paris\ (33)\ 134-65-9191;\ Milan\ (39)\ 39-639261;\ Toronto\ (416)\ 673-1211;\ Hong\ Kong\ (852)\ 529-2705$

Emulex Micro Devices Sales Representatives: Montgomery Marketing (919) 467-6319 - Alabama, Georgia, Florida Pan Handle, No. Carolina, South Carolina, Tennessee; ProMerge, Sales (408) 453-5544 - No. California, No. Nevada; Sales Engineering Concepts (305) 426-4601 - Florida, Puerto Rico; West Associates (214) 680-2800 - Mississippi, Oklahoma, Texas; Advanced Tech Sales, Inc. (508) 664-0888 - Massachusetts, Connecticut, Vermont, New Hampshire, Maine, Rhode Island; Oasis Sales Corporation (708) 680-2800 - No. Illinois, Wisconsin, Iowa, North Dakota, South Dakota, Minnesota

PAGE /6 ©1990 Emulex Corporation

Specifications Subject To Change Without Notice

FAS200/100A (6/91)

MAY O 4 1992

029704 🗹 \_ \_