## Powered by ICminer.com Electronic-Library Service CopyRight 2003

# HM511665 Series

65,536-Word x 16-Bit Dynamic Random Access Memory

#### DESCRIPTION

The Hitachi HM511665 are CMOS dynamic RAM organized as 65,536-word x 16-bit. HM511665 have realized higher density, higher performance and various functions by employing 0.8  $\mu m$  CMOS process technology and some new CMOS circuit design technologies. The HM511665 offer Fast Page Mode as a high speed access mode.

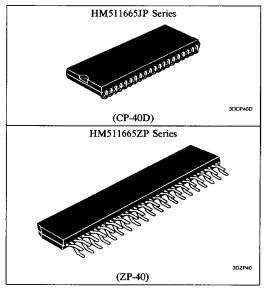

Multiplexed address input permits the HM511665 to be packaged in standard 400 mil 40-pin plastic SOJ, standard 475 mil 40-pin plastic ZIP.

#### FEATURES

- Single 5V (±10%)

- High Speed

| Active Mode  | <b>TBD</b> |

|--------------|------------|

| Standby Mode |            |

|              |            |

- Fast Page Mode Capability

- Write per Bit Capability

- 256 Refresh Cycles ......(4 ms)

- 3 Variations of Refresh RAS Only Refresh CAS Before RAS Refresh Hidden Refresh

Hidden Refresh

### ORDERING INFORMATION

| Part No.                      | Access Time     | Package                                   |

|-------------------------------|-----------------|-------------------------------------------|

| HM511665JP-8<br>HM511665JP-10 | 80 ns<br>100 ns | 400 mil 40-pin<br>Plastic SOJ<br>(CP-40D) |

| HM511665ZP-8<br>HM511665ZP-10 | 80 ns<br>100 ns | 475 mil 40-pin<br>Plastic ZIP<br>(ZP-40)  |

#### PIN DESCRIPTION

| Pin Name                                   | Function                               |

|--------------------------------------------|----------------------------------------|

| A <sub>0</sub> -A <sub>7</sub>             | Address Input<br>Refresh Address Input |

| W1/I/O <sub>1</sub> -W16/I/O <sub>16</sub> | Write Select/Data-in/Data-out          |

| RAS                                        | Row Address Strobe                     |

| CAS                                        | Column Address Strobe                  |

| WB/WE                                      | Write per Bit/Read/Write Enable        |

| WB/WE                                      | Write per Bit/Read/Write Enable        |

| ŌĒ                                         | Output Enable                          |

| V <sub>CC</sub>                            | Power ( + 5V)                          |

| V <sub>SS</sub>                            | Ground                                 |

| NC                                         | No Connection                          |

#### PIN OUT

| HM511665.                                                                                                                                                                                                                                                                     | JP Series                                                                                                                                                                                                                             | HM511665ZP Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> [1<br>w1/101 [2<br>w2/102 [3<br>w3/103 [4<br>w4/104 [5<br>w5/106 [6<br>w5/106 [7<br>w7/107 [3<br>w8/108 [9<br>NC [10<br>V <sub>cc</sub> [11<br><u>NC [12</u><br>w8/m2 [13<br>RAS [14<br>A0 [15<br>A1 [16<br>A2 [17<br>A3 [18<br>A4 [19<br>V <sub>cc</sub> [20 | 40 2 V <sub>35</sub><br>39 2 W16/1016<br>38 2 V15/1015<br>37 2 W14/1014<br>36 2 V13/1013<br>35 2 V12/1012<br>34 2 W11/1011<br>33 2 V16/1010<br>31 2 NC<br>30 2 V35<br>27 2 NC<br>26 2 NC<br>25 2 NC<br>24 2 A5<br>22 2 A5<br>21 2 V55 | W9/109         Z         1         NC           W1/1011         4         3         W10/1010           W13/1013         6         7         W14/2014           V15/1015         8         9         W16/1016           Vys         10         11         W1//101           W2/102         12         1.1         W1//101           W3/103         14         1.1         W1//101           W3/103         14         1.1         Vrc           W5/105         15         1.1         Vrc           W5/105         15         1.1         Vrc           W5/105         15         1.1         Vrc           W5/105         15         1.7         Vrc           W162         2.2         2.3         W5/108           WC 20         2.1         Yrc         2.3           W162         2.2         2.3         W5/108           MC 20         2.1         Yrc         3.3           W12         2.2         2.3         W5/108           M2 25         2.7         A.2         2.3           W12         3.3         3.3         NC           W2 32 |

| (Top V                                                                                                                                                                                                                                                                        | iew)                                                                                                                                                                                                                                  | (Bottom View) 0075-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# HITACHI

186

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

# Preliminary

#### ■ TRUTH TABLE

|                  | I                | nputs            |                       | 1/0                                                               | Operation                           |

|------------------|------------------|------------------|-----------------------|-------------------------------------------------------------------|-------------------------------------|

| RAS              | RAS CAS WB/WE    |                  |                       | W1/I/O1-W16/I/O16                                                 | Operation                           |

| H<br>L<br>L<br>L | H<br>H<br>L<br>L | H<br>H<br>H<br>L | H<br>H<br>L<br>H<br>H | High-Z<br>High-Z<br>D <sub>out</sub><br>D <sub>in</sub><br>High-Z | Standby<br>Refresh<br>Read<br>Write |

#### ABSOLUTE MAXIMUM RATINGS

| Parameter                                      | Symbol           | Value          | Unit |

|------------------------------------------------|------------------|----------------|------|

| Voltage on Any Pin Relative to V <sub>SS</sub> | V <sub>T</sub>   | - 1.0 to + 7.0 | v    |

| Supply Voltage Relative to V <sub>SS</sub>     | v <sub>cc</sub>  | -1.0 to +7.0   | v    |

| Short Circuit Output Current                   | Iout             | 50             | mA   |

| Power Dissipation                              | P <sub>T</sub>   | 0.8            | W    |

| Operating Temperature                          | T <sub>opr</sub> | 0 to + 70      | °C   |

| Storage Temperature                            | T <sub>stg</sub> | - 55 to + 125  | °C   |

### ELECTRICAL CHARACTERISTICS

## • Recommended DC Operating Conditions ( $T_A = 0$ to $+70^{\circ}$ C)

| Par              | ameter          | Symbol          | Min   | Тур | Max | Unit | Note |

|------------------|-----------------|-----------------|-------|-----|-----|------|------|

|                  |                 | V <sub>SS</sub> | 0     | 0   | 0   | v    |      |

| Supply Voltage   |                 | V <sub>CC</sub> | 4.5   | 5.0 | 5.5 | v    | 1    |

| Input High Volt  | age             | VIH             | 2.4   | _   | 6.5 | v    | 1    |

| Input Low        | (Wi/I/Oi Pin)   | V <sub>IL</sub> | - 0.5 |     | 0.8 | v    | 1, 2 |

| Voltage (Others) | v <sub>IL</sub> | - 1.0           | -     | 0.8 | v   | 1, 2 |      |

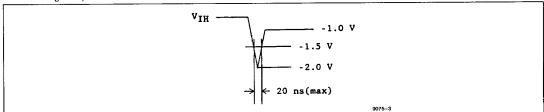

#### Notes: 1. All voltage referenced to VSS.

2. The device will withstand undershoots to the -2V level with a maximum pulse width of 20 ns at the -1.5V level. (See figure 1.)

Figure 1. Undershoot of input voltage

# HITACHI Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### HM511665 Series

| Parameter                         | 6 h 1            | HM511665-8 |                 | HM51 | HM511665-10     |                                                   |                                                                                                                                         |      |      |

|-----------------------------------|------------------|------------|-----------------|------|-----------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Farameter                         | Symbol           | Min        | Max             | Min  | Max             | Unit                                              | Test Conditions                                                                                                                         | Note |      |

| Operating Current                 | I <sub>CC1</sub> |            | TI              | BD   |                 | mA                                                | $\overline{RAS}, \overline{CAS} \text{ Cycling} \\ t_{RC} = Min$                                                                        | 1, 2 |      |

| Standby Current                   | I <sub>CC2</sub> |            | :               | 2    |                 | mA                                                | $\frac{\text{TTL Interface}}{\text{RAS}, \overline{\text{CAS}}} = V_{\text{IH}},$ $D_{\text{out}} = \text{High-Z}$                      |      |      |

|                                   | 4002             |            |                 | 1    |                 | mA                                                | $\frac{\text{CMOS Interface } \overline{\text{RAS}}}{\overline{\text{CAS}}} \ge V_{\text{CC}} - 0.2V,$ $D_{\text{out}} = \text{High-Z}$ |      |      |

| <b>RAS</b> Only Refresh Current   | I <sub>CC3</sub> |            | TI              | BD   |                 | mA                                                | t <sub>RC</sub> = Min                                                                                                                   | 2    |      |

| Standby Current                   | I <sub>CC5</sub> |            | TI              | BD   |                 | mA                                                | $\overline{RAS} = V_{IH},$<br>$\overline{CAS} = V_{IL},$<br>$D_{out} = Enable$                                                          | 1    |      |

| CAS Before RAS Refresh<br>Current | I <sub>CC6</sub> |            | TI              | BD   |                 | mA                                                | $t_{RC} = Min$                                                                                                                          |      |      |

| Fast Page Mode Current            | I <sub>CC7</sub> |            | TBD             |      | TBD             |                                                   | mA t <sub>PC</sub> = Min                                                                                                                |      | 1, 3 |

| Input Leakage Current             | ILI              | - 10       | 10              | - 10 | 10              | μΑ                                                | $0V \le V_{in} \le 6.5V$                                                                                                                |      |      |

| Output Leakage Current            | ILO              | - 10       | -10 10 -10 10   |      | μA              | $0V \le V_{out} \le 5.5V,$<br>$D_{out} = Disable$ |                                                                                                                                         |      |      |

| Output High Voltage               | V <sub>OH</sub>  | 2.4        | V <sub>CC</sub> | 2.4  | V <sub>CC</sub> | v                                                 | High $I_{out} = -2.5 \text{ mA}$                                                                                                        |      |      |

| Output Low Voltage                | VOL              | 0          | 0.4             | 0    | 0.4             | v                                                 | $Low I_{out} = 2.1 mA$                                                                                                                  |      |      |

Notes: 1. I<sub>CC</sub> depends on output load condition when the device is selected, I<sub>CC</sub> max is specified at the output open condition. 2. Address can be changed once or less while  $\overline{RAS} = V_{IL}$ .

3. Address can be changed once or less while  $\overline{CAS} = V_{IH}$ .

• Capacitance ( $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$ )

| Parameter                              | Symbol           | Тур | Max | Unit | Note |

|----------------------------------------|------------------|-----|-----|------|------|

| Input Capacitance (Address)            | C <sub>I1</sub>  | _   | 5   | pF   | 1    |

| Input Capacitance (Clocks)             | CI2              | —   | 7   | pF   | 1    |

| Output Capacitance (Data-in, Data-out) | C <sub>I/O</sub> | -   | 7   | pF   | 1, 2 |

Notes: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2.  $\overline{CAS} = V_{IH}$  to disable  $D_{out}$ .

# **OHITACHI**

## • AC Characteristics (T<sub>A</sub> = 0 to +70°C, V<sub>CC</sub> = 5V $\pm$ 10%, V<sub>SS</sub> = 0V)<sup>1, 14, 15</sup> Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

|                                    |                  | HM5 | 11665-8 | HM51 | 1665-10 | Unit | Note |

|------------------------------------|------------------|-----|---------|------|---------|------|------|

| Parameter                          | Symbol           | Min | Max     | Min  | Max     | Onit | NOR  |

| Random Read or Write Cycle Time    | t <sub>RC</sub>  | 135 |         | 170  | —       | ns   |      |

| RAS Precharge Time                 | t <sub>RP</sub>  | 45  |         | 60   | _       | ns   |      |

| RAS Pulse Width                    | tRAS             | 80  | 10000   | 100  | 10000   | ns   |      |

| CAS Pulse Width                    | tCAS             | 30  | 10000   | 40   | 10000   | ns   |      |

| Row Address Setup Time             | tASR             | 0   | —       | 0    | 1       | ns   |      |

| Row Address Hold Time              | t <sub>RAH</sub> | 10  | _       | 10   | —       | ns   |      |

| Column Address Setup Time          | tASC             | 0   | _       | 0    | —       | ns   |      |

| Column Address Hold Time           | <sup>t</sup> CAH | 15  | _       | 15   | _       | ns   |      |

| RAS to CAS Delay Time              | t <sub>RCD</sub> | 20  | 50      | 20   | 60      | ns   | 8    |

| RAS to Column Address Delay Time   | tRAD             | 15  | 35      | 15   | 45      | ns   | 9    |

| RAS Hold Time                      | tRSH             | 30  | _       | 40   | —       | ns   |      |

| CAS Hold Time                      | <sup>t</sup> CSH | 80  | _       | 100  | -       | ns   |      |

| CAS to RAS Precharge Time          | <sup>t</sup> CRP | 10  | _       | 10   | _       | ns   |      |

| OE to D <sub>in</sub> Delay Time   | todd             | 15  | _       | 15   | -       | ns   |      |

| OE Delay Time from D <sub>in</sub> | <sup>t</sup> DZO | 0   |         | 0    |         | ns   |      |

| CAS Setup Time from Din            | tDZC             | 0   | _       | 0    | —       | ns   |      |

| Transition Time (Rise and Fall)    | tT               | 3   | 50      | 3    | 50      | ns   | 7    |

| Refresh Period                     | tREF             | _   | 4       | _    | 4       | ms   |      |

### **Read Cycle**

| _                               |                   | HM5 | 11665-8 | HM51 | 1665-10 | Unit | Note     |

|---------------------------------|-------------------|-----|---------|------|---------|------|----------|

| Parameter                       | Symbol            | Min | Max     | Min  | Max     | Om   | INOLE    |

| Access Time from RAS            | tRAC              | _   | 80      | _    | 100     | ns   | 2, 3     |

| Access Time from CAS            | <sup>t</sup> CAC  | _   | 30      | —    | 40      | ns   | 3, 4, 13 |

| Access Time from Address        | t <sub>AA</sub>   |     | 45      | _    | 55      | ns   | 3, 5, 13 |

| Access Time from OE             | tOAC              | _   | 30      | -    | 40      | ns   |          |

| Read Command Setup Time         | tRCS              | 0   | —       | 0    | —       | ns   |          |

| Read Command Hold Time to CAS   | tRCH              | 0   | _       | 0    | —       | ns   |          |

| Read Command Hold Time to RAS   | <sup>t</sup> RRH  | 0   | -       | 0    | _       | ns   |          |

| Column Address to RAS Lead Time | <sup>t</sup> RAL  | 45  | —       | 55   | —       | ns   |          |

| Output Buffer Turn-off Time     | toffi             | 0   | 20      | 0    | 20      | ns   | 6        |

| Output Buffer Turn-off to OE    | t <sub>OFF2</sub> | 0   | 15      | 0    | 15      | ns   | 6        |

| CAS to Din Delay Time           | <sup>t</sup> CDD  | 20  |         | 20   |         | ns   |          |

| RAS Hold Time Referenced to OE  | tROH              | 10  | _       | 10   | -       | ns   |          |

#### Write Cycle

| Parameter                      | HM511665-8       |     | HM51 | 1665-10 | Unit | Note |      |

|--------------------------------|------------------|-----|------|---------|------|------|------|

|                                | Symbol           | Min | Max  | Min     | Max  |      | Note |

| Write Command Setup Time       | twcs             | 0   | -    | 0       | _    | ns   | 10   |

| Write Command Hold Time        | twcH             | 15  | _    | 15      | -    | ns   |      |

| Write Command Pulse Width      | twp              | 15  | —    | 15      | —    | ns   |      |

| Write Command to RAS Lead Time | t <sub>RWL</sub> | 20  | _    | 20      | _    | ns   |      |

| Write Command to CAS Lead Time | <sup>t</sup> CWL | 20  | -    | 20      |      | ns   |      |

| Data-in Setup Time             | t <sub>DS</sub>  | 0   | _    | 0       | _    | ns   | 11   |

| Data-in Hold Time              | t <sub>DH</sub>  | 15  | _    | 15      | _    | ns   | 11   |

# **OHITACHI**

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### HM511665 Series -

### Read-Modify-Write Cycle

| Parameter                       | Symbol           | HM511665-8 |     | HM511665-10 |     |      |        |

|---------------------------------|------------------|------------|-----|-------------|-----|------|--------|

|                                 |                  | Min        | Max | Min         | Max | Unit | Note   |

| Read-Modify-Write Cycle Time    | t <sub>RWC</sub> | 185        | _   | 220         | _   | ns   |        |

| RAS to WE Delay Time            | t <sub>RWD</sub> | 105        | _   | 125         | _   | ns   | 10     |

| CAS to WE Delay Time            | tCWD             | 55         | _   | 65          | _   | ns   | 10     |

| Column Address to WE Delay Time | tAWD             | 70         |     | 80          |     | ns   | 10, 13 |

| OE Hold Time from WE            | tOEH             | 15         |     | 15          |     | ns   |        |

## **Refresh Cycle**

| Parameter                                        | Symbol           | HM511665-8 |     | HM511665-10 |     | <b>TT 1</b> . |      |

|--------------------------------------------------|------------------|------------|-----|-------------|-----|---------------|------|

|                                                  |                  | Min        | Max | Min         | Max | Unit          | Note |

| CAS Setup Time<br>(CAS Before RAS Refresh Cycle) | <sup>t</sup> CSR | 10         | _   | 10          | _   | ns            |      |

| CAS Hold Time<br>(CAS Before RAS Refresh Cycle)  | t <sub>CHR</sub> | 10         | -   | 10          | _   | ns            |      |

| RAS Precharge to CAS Hold Time                   | tRPC             | 10         | -   | 10          | _   | ns            |      |

| CAS Precharge Time in Normal Mode                | <sup>t</sup> CPN | 10         | _   | 10          | _   | ns            |      |

## Fast Page Mode Cycle

| Parameter                                                                    | Symbol            | HM5 | 11665-8 | HM511665-10 |        | <b>TT</b> 1. |       |

|------------------------------------------------------------------------------|-------------------|-----|---------|-------------|--------|--------------|-------|

|                                                                              |                   | Min | Max     | Min         | Max    | Unit         | Note  |

| Fast Page Mode Cycle Time                                                    | tPC               | 55  | _       | 65          |        | ns           |       |

| Fast Page Mode CAS Precharge Time                                            | t <sub>CP</sub>   | 10  |         | 10          |        | ns           |       |

| Fast Page Mode RAS Pulse Width                                               | tRASC             | 80  | 100000  | 100         | 100000 | ns           | 12    |

| Access Time from CAS Precharge                                               | tACP              | _   | 45      | _           | 55     | ns           | 3, 13 |

| RAS Hold Time from CAS Precharge                                             | t <sub>RHCP</sub> | 45  |         | 55          |        | ns           |       |

| Fast Page Mode Read-Modify-<br>Write Cycle CAS Precharge<br>to WE Delay Time | <sup>t</sup> CPW  | 70  |         | 80          | _      | ns           |       |

| Fast Page Mode Read-Modify-<br>Write Cycle Time                              | t <sub>PCM</sub>  | 100 | _       | 110         | _      | ns           |       |

## **Counter Test Cycle**

| Parameter                                   | Symbol           | HM51 | 1665-8 | HM51 | 1665-10 | Unit | N    |

|---------------------------------------------|------------------|------|--------|------|---------|------|------|

|                                             |                  | Min  | Max    | Min  | Max     |      | Note |

| CAS Precharge Time in<br>Counter Test Cycle | <sup>t</sup> CPT | 40   | _      | 40   | -       | ns   |      |

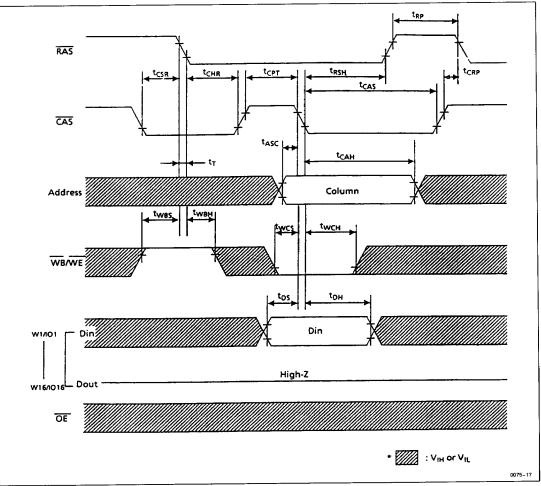

## Write per Bit Cycle<sup>16, 17</sup>

190

| Parameter                          | Symbol           | HM511665-8 |     | HM511665-10 |     |      |      |

|------------------------------------|------------------|------------|-----|-------------|-----|------|------|

|                                    |                  | Min        | Max | Min         | Max | Unit | Note |

| Write per Bit Setup Time           | t <sub>WBS</sub> | 0          |     | 0           | _   | ns   |      |

| Write per Bit Hold Time            | t <sub>WBH</sub> | 10         |     | IO          | -   | ns   |      |

| Write per Bit Selection Setup Time | twDs             | 0          | _   | 0           | _   | ns   |      |

| Write per Bit Selection Hold Time  | twDH             | 10         | _   | 10          | —   | ns   |      |

# (C) HITACHI

#### Notes: 1. AC measurements assume $t_T = 5$ ns.

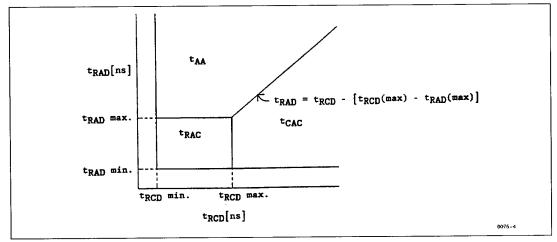

- 2. Assumes that  $t_{RCD} \le t_{RCD}$  (max) and  $t_{RAD} \le t_{RAD}$  (max). If  $t_{RCD}$  or  $t_{RAD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  exceeds the value shown.

- 3. Measured with a load circuit equivalent to 1 TTL load and 50 pF.

- 4. Assumes that  $t_{RCD} \ge t_{RCD}$  (max) and  $(t_{RCD} t_{RAD}) \ge [t_{RCD}$  (max)  $t_{RAD}$  (max)].

- 5. Assumes that  $t_{RAD} \ge t_{RAD}$  (max) and  $(t_{RCD} t_{RAD}) \le [t_{RCD} (max) t_{RAD} (max)]$ .  $t_{RAC}$ ,  $t_{CAC}$ , and  $t_{AA}$  are determined as follows.

- 6. toFF (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 7. V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- 8. Operation with the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met,  $t_{RCD}$  (max) is specified as a reference point only, if  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max) limit, then access time is controlled exclusively by  $t_{CAC}$ .

- 9. Operation with the  $t_{RAD}$  (max) limit insures that  $t_{RAC}$  (max) can be met,  $t_{RAD}$  (max) is specified as a reference point only, if  $t_{RAD}$  is greater than the specified  $t_{RAD}$  (max) limit, then access time is controlled exclusively by  $t_{AA}$ .

- 10. twCS, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only: if t<sub>WCS</sub>  $\geq$  t<sub>WCS</sub> (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if t<sub>RWD</sub>  $\geq$  t<sub>RWD</sub> (min), t<sub>CWD</sub>  $\geq$  t<sub>CWD</sub> (min), t<sub>AWD</sub>  $\geq$  t<sub>AWD</sub> (min) and t<sub>CPW</sub>  $\geq$  t<sub>CPW</sub> (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- 11. These parameters are referenced to CAS leading edge in an early write cycle and to WE leading edge in a delayed write or a read-modify-write cycle.

- 12.  $t_{RASC}$  defines  $\overline{RAS}$  pulse width in fast page mode cycles.

- 13. Access time is determined by the longer of tAA or tCAC or tACP.

- 14. An initial pause of 100  $\mu$ s is required after power up followed by a minimum of eight initialization cycles (RAS only refresh cycle or CAS before RAS refresh cycle). If the internal refresh counter is used, a minimum of eight CAS before RAS refresh cycles is required.

- 15. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.

- 16. When using the write-per-bit capability,  $\overline{WB}/\overline{WE}$  must be low as  $\overline{RAS}$  falls.

- 17. The data bits to which the write operation is applied can be specified by keeping Wi/I/Oi high with setup and hold time referenced to the  $\overline{RAS}$  negative transition.

# **OHITACHI**

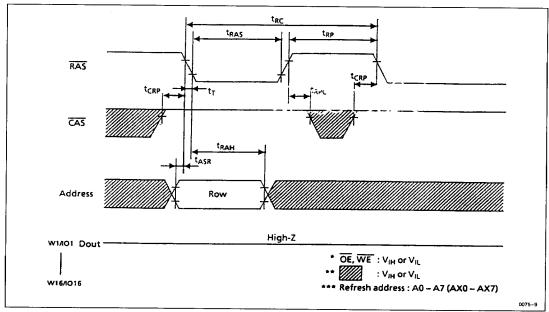

## **TIMING WAVEFORMS**

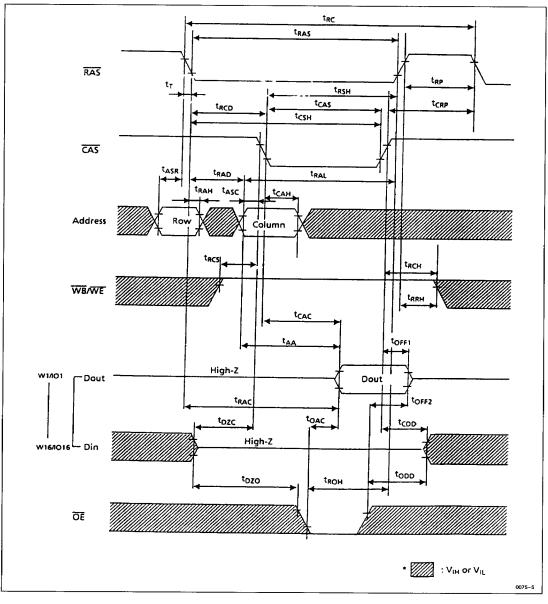

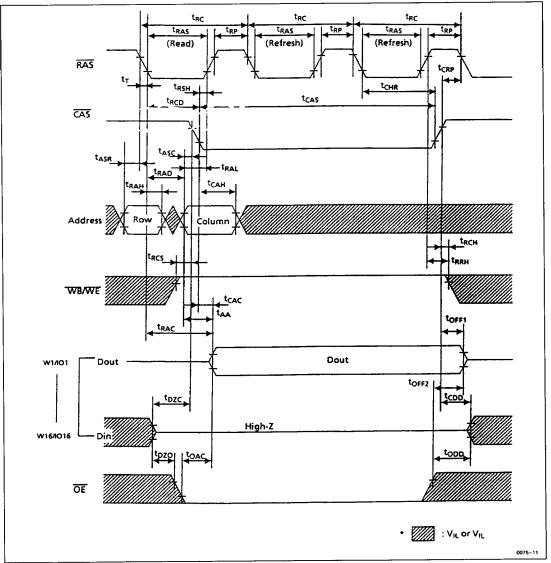

## • Read Cycle

192

# **OHITACHI**

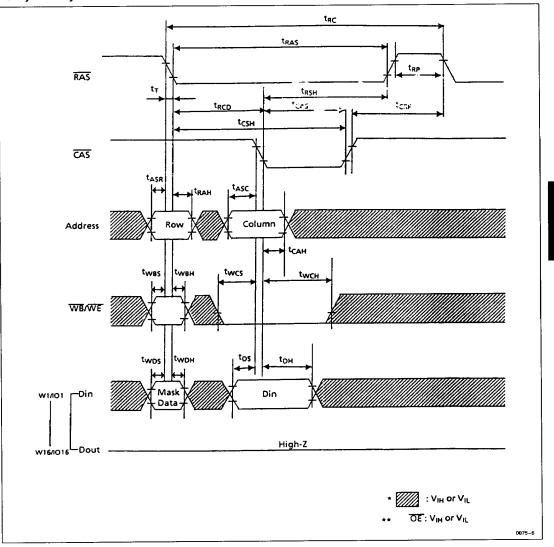

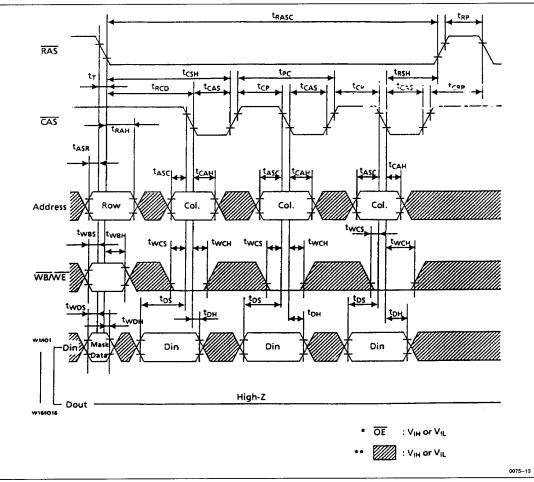

#### • Early Write Cycle

HITACHI Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

HM511665 Series

194

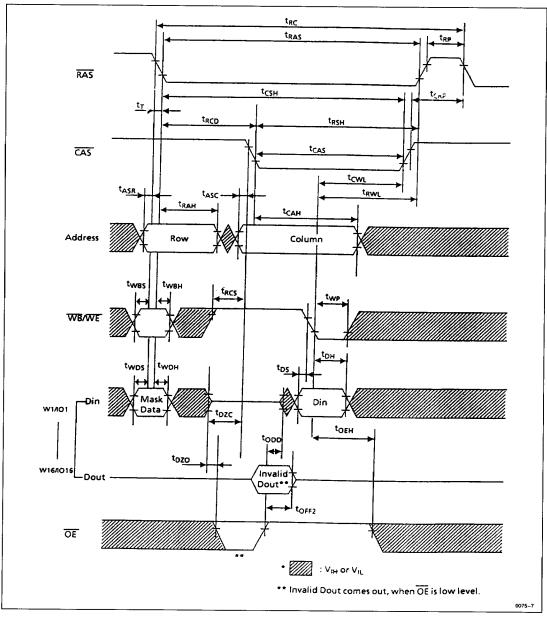

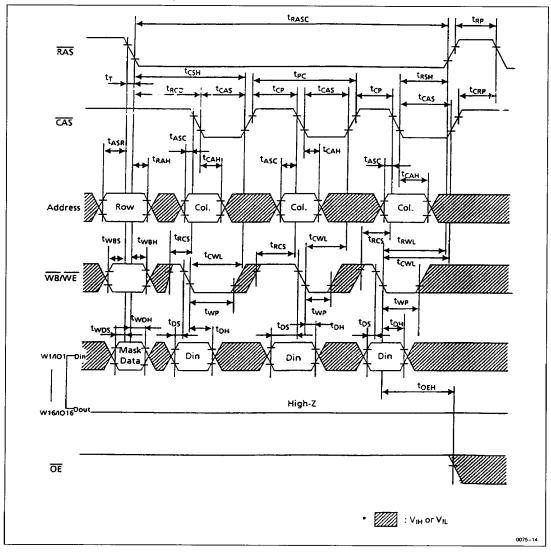

Delayed Write Cycle

# HITACHI

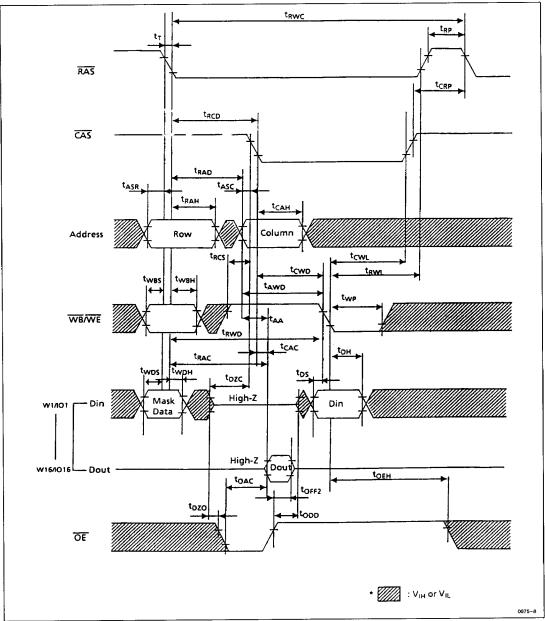

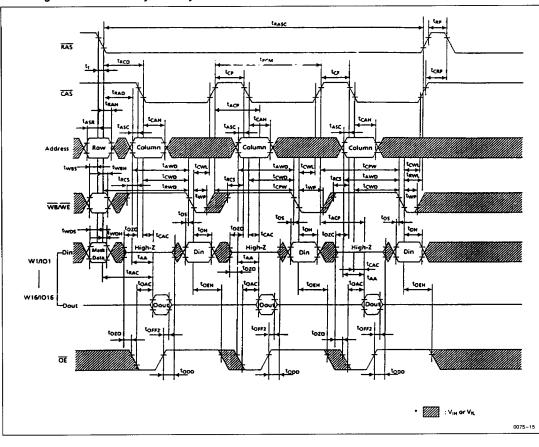

#### • Read-Modify-Write Cycle

# D HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### HM511665 Series -

## • RAS Only Refresh Cycle

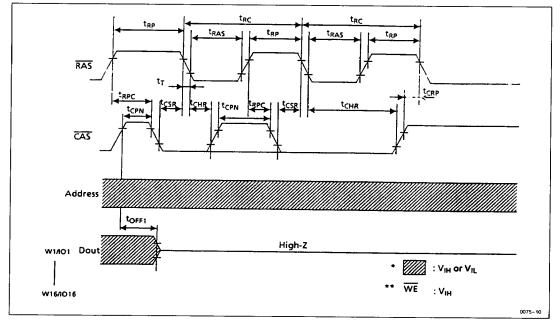

## CAS Before RAS Refresh Cycle

196

#### Hidden Refresh Cycle

HM511665 Series -

198

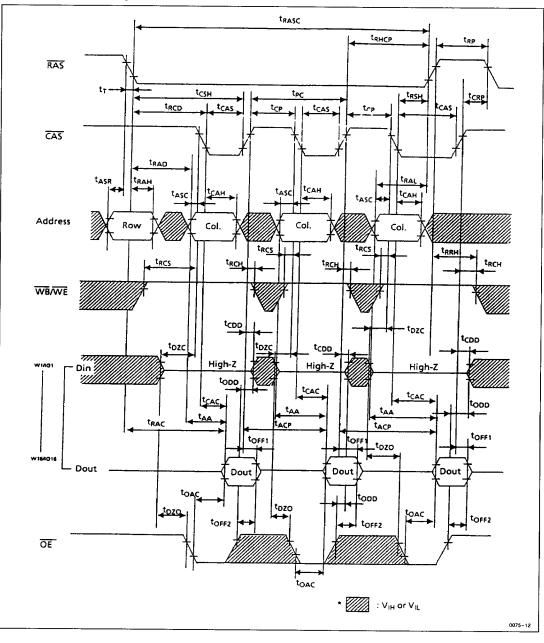

#### • Fast Page Mode Read Cycle

## HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

Powered by ICminer.com Electronic-Library Service CopyRight 2003

HM511665 Series

200

• Fast Page Mode Delayed Write Cycle

# CHITACHI

• Fast Page Mode Read-Modify-Write Cycle

# D HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

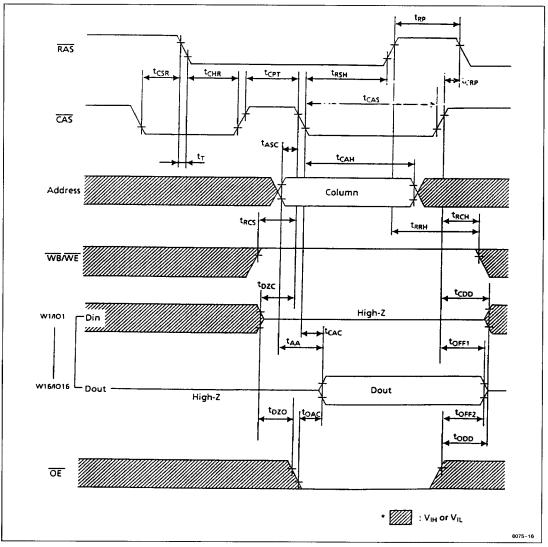

## • CAS Before RAS Refresh Counter Check Cycle (Read)

# (C) HITACHI

202

CAS Before RAS Refresh Check Cycle (Write)