262,144-word × 16-bit Dynamic Random Access Memory

### HITACHI/ LOGIC/ARRAYS/MEM

The Hitachi HM514260 are CMOS dynamic RAM organized as 262,144-word  $\times$  16-bit. HM514260 have realized higher density, higher performance and various functions by employing 0.8  $\mu$ m CMOS process technology and some new CMOS circuit design technologies. The HM514260 offer fast page mode as a high speed access mode.

Multiplexed address input permits the HM514260 to be packaged in standard 400-mil 40-pin plastic SOJ, standard 475-mil 40-pin plastic ZIP, and 400-mil 40-pin plastic TSOP.

#### **Features**

- Single 5 V (± 10%)

- · High speed

- Access time: 70 ns/80 ns/100 ns (max)

- Low power dissipation

- Active mode: 935 mW/825 mW/715 mW (max)

- Standby mode: 11 mW (max) 1.1 mW (max) (L-version)

- · Fast page mode capability

- 512 refresh cycles: 8 ms

128 ms (L-version)

- 2 CAS byte control

- · 3 variations of refresh

- RAS-only refresh

- CAS-before-RAS refresh

- Hidden refresh

- Battery back up operation (L-version)

### **Ordering Information**

| Type No.       | Access time | Package        |

|----------------|-------------|----------------|

| HM514260JP-7   | 70 ns       | 400-mil 40-pin |

| HM514260JP-8   | 80 ns       | plastic SOJ    |

| HM514260JP-10  | 100 ns      | (CP-40D)       |

| HM514260ZP-7   | 70 ns       | 475-mil 40-pin |

| HM514260ZP-8   | 80 ns       | plastic ZIP    |

| HM514260ZP-10  | 100 ns      | (ZP-40)        |

| HM514260TT-7   | 70 ns       | 400-mil 40-pin |

| HM514260TT-8   | 80 ns       | plastic TSOP   |

| HM514260TT-10  | 100 ns      | (TTP-40DB)     |

| HM514260LJP-7  | 70 ns       | 400-mil 40-pin |

| HM514260LJP-8  | 80 ns       | plastic SOJ    |

| HM514260LJP-10 | 100 ns      | (CP-40D)       |

| HM514260LZP-7  | 70 ns       | 475-mil 40-pin |

| HM514260LZP-8  | 80 ns       | plastic ZIP    |

| HM514260LZP-10 | 100 ns      | (ZP-40)        |

| HM514260LTT-7  | 70 ns       | 400-mil 40-pin |

| HM514260LTT-8  | 80 ns       | plastic TSOP   |

| HM514260LTT-10 | 100 ns      | (TTP-40DB)     |

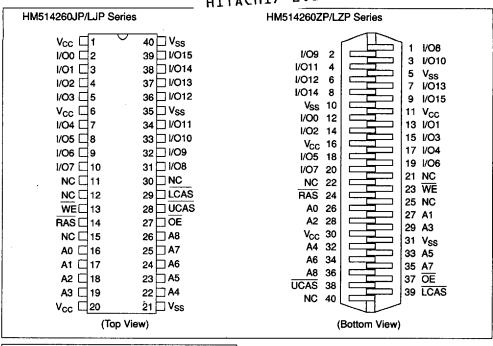

### Pin Arrangement

# HITACHI/ LOGIC/ARRAYS/MEM

#### HM514260TT/LTT Series Vcc □1 ○ 44 | V<sub>SS</sub> 43 | I/O15 1/00 🗆 2 1/01 □3 42 1/014 1/02 🗆 4 41 1/013 1/03 □5 40 1/012 39 V<sub>SS</sub> 38 1/O11 1/04 🗆 7 37 1/010 1/05 □8 1/06 □9 36 🗀 1/09 1/07 □ 10 35 🗀 1/08 32 NC 31 LCAS 30 UCAS NC | 13 NC | 14 WE ☐ 15 29 DE RAS ☐16 28 🗆 A8 NC ☐ 17 A0 🗆 18 27 🗆 A7 A1 🗆 19 26 🗆 A6 25 🗆 A5 A2 🗆 20 24 A4 23 Vss A3 □21 V<sub>CC</sub> □22 (Top View)

## Pin Description

| Pin name            | Function                                                                         |

|---------------------|----------------------------------------------------------------------------------|

| A0 A8               | Address input Row address A0 - A8 Column address A0 - A8 Refresh address A0 - A8 |

| I/O0 – I/O15        | Data-in/data-out                                                                 |

| RAS                 | Row address strobe                                                               |

| UCAS, LCAS          | Column address strobe                                                            |

| WE                  | Read/write enable                                                                |

| OE                  | Output enable                                                                    |

| V <sub>CC</sub>     | Power (+5 V)                                                                     |

| <br>V <sub>SS</sub> | Ground                                                                           |

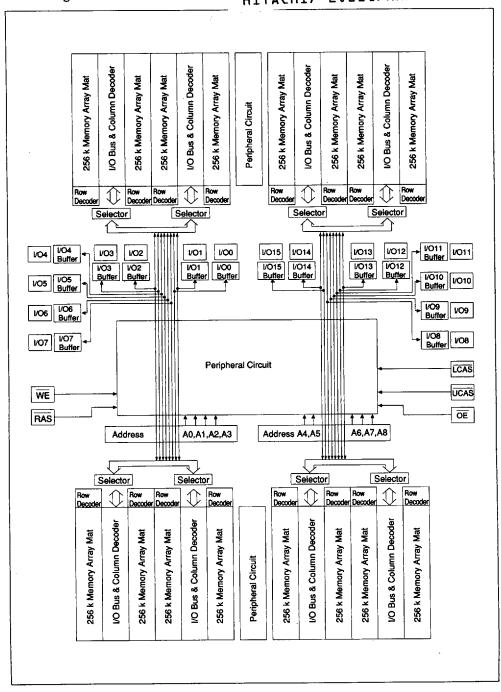

## **Block Diagram**

# HITACHI/ LOGIC/ARRAYS/MEM

| HM     | 51426       | 0, HM | 5142 | 60L Se | eries       |              |                  |

|--------|-------------|-------|------|--------|-------------|--------------|------------------|

| Trut   | h Table     |       |      | HITAC  | HI/ LOGICA  | ARRAYS/MEM   |                  |

| Inputs |             | I/O   |      |        |             |              |                  |

| RAS    | <b>LCAS</b> | UCAS  | WE   | ŌE     | 1/00 – 1/07 | I/O8 – I/O15 | -<br>Operation   |

| Н      | Н           | Н     | Н    | Н      | High-Z      | High-Z       | Standby          |

| L      | Н           | Н     | н    | Н      | High-Z      | High-Z       | Refresh          |

| L      | L           | Н     | Н    | L      | Dout        | High-Z       | Lower byte read  |

| L      | Н           | L     | Н    | L      | High-Z      | Dout         | Upper byte read  |

| L      | L           | L     | Н    | L      | Dout        | Dout         | Word read        |

| L      | L           | Н     | L    | Н      | Din         | Don't care   | Lower byte write |

| L      | Н           | L     | L    | Н      | Don't care  | Din          | Upper byte write |

| <br>L  | L           | L     | L    | Н      | Din         | Din          | Word write       |

# **Absolute Maximum Ratings**

L

Н

Н

L

| Parameter                                      | Symbol          | Value        | Unit |

|------------------------------------------------|-----------------|--------------|------|

| Voltage on any pin relative to V <sub>SS</sub> | V <sub>T</sub>  | -1.0 to +7.0 | ٧    |

| Supply voltage relative to V <sub>SS</sub>     | v <sub>cc</sub> | -1.0 to +7.0 | ٧    |

| Short circuit output current                   | lout            | 50           | mA   |

| Power dissipation                              | P <sub>T</sub>  | 1.0          | w    |

| Operating temperature                          | Topr            | 0 to +70     | °C   |

| Storage temperature                            | Tstg            | -55 to +125  | °C   |

High-Z

High-Z

# HITACHI/ LOGIC/ARRAYS/MEM

# HM514260, HM514260L Series

# **Recommended DC Operating Conditions** (Ta = 0 to $+70^{\circ}$ C) \*2

| Parameter            |           | Symbol          | Min  | Тур         | Max | Unit | Note |

|----------------------|-----------|-----------------|------|-------------|-----|------|------|

| Supply voltage       |           | V <sub>SS</sub> | 0    | 0           | 0   | ٧    |      |

|                      |           | v <sub>cc</sub> | 4.5  | 5.0         | 5.5 | ٧    | 1    |

| Input high vol       | Itage     | V <sub>IH</sub> | 2.4  | _           | 6.5 | ٧    | 1    |

| Input low<br>voltage | (I/O pin) | VIL             | -1.0 |             | 0.8 | ٧.   | 1    |

|                      | (Others)  | V <sub>IL</sub> | -2.0 | <del></del> | 0.8 | ٧    | 1    |

Notes: 1. All voltage referenced to V<sub>SS</sub>

2. The supply voltage with all V<sub>CC</sub> pins must be on the same level.

The supply voltage with all V<sub>SS</sub> pins must be on the same level.

**DC** Characteristics (Ta = 0 to 70°C,  $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ )

| Symbol                                                                                                             | Min  | Max  | Min        | Max | Min                                                                                                                                                                                                                                          | Max                                                                                                                                                                                                                                           | Unit                                                                                                                                                                                                                                                                                      | Test conditions                                                                                                                                                                                                                                                                                                                                                                                                               | Notes            |

|--------------------------------------------------------------------------------------------------------------------|------|------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ting $I_{CC1}$ — 170 — 150 — 130 mA $\overline{RAS}$ cycling $I_{CAS}$ or $\overline{UCAS}$ cycling $I_{RC}$ = min |      | 1, 2 |            |     |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |

| I <sub>CC2</sub>                                                                                                   | _    | 2    |            | 2   | _                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                             | mA                                                                                                                                                                                                                                                                                        | TTL interface<br>RAS, LCAS, UCAS = V <sub>IH</sub><br>Dout = High-Z                                                                                                                                                                                                                                                                                                                                                           |                  |

|                                                                                                                    | _    | 1    | <b>-</b> . | 1   | _                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                             | mA                                                                                                                                                                                                                                                                                        | CMOS interface<br>RAS, LCAS,<br>UCAS ≥ V <sub>CC</sub> - 0.2 V<br>Dout = High-Z                                                                                                                                                                                                                                                                                                                                               |                  |

|                                                                                                                    | _    | 200  | _          | 200 | _                                                                                                                                                                                                                                            | 200                                                                                                                                                                                                                                           | μА                                                                                                                                                                                                                                                                                        | CMOS interface<br>RAS, LCAS,<br>UCAS ≥ V <sub>CC</sub> = 0.2 V<br>Dout = High-Z                                                                                                                                                                                                                                                                                                                                               |                  |

| I <sub>CC3</sub>                                                                                                   | _    | 150  | _          | 130 | _                                                                                                                                                                                                                                            | 110                                                                                                                                                                                                                                           | mA                                                                                                                                                                                                                                                                                        | t <sub>RC</sub> = min                                                                                                                                                                                                                                                                                                                                                                                                         | 2                |

| I <sub>CC5</sub>                                                                                                   | _    | 5    |            | 5   |                                                                                                                                                                                                                                              | 5                                                                                                                                                                                                                                             | mA                                                                                                                                                                                                                                                                                        | RAS = V <sub>IH</sub><br>LCAS or UCAS = V <sub>IL</sub><br>Dout = enable                                                                                                                                                                                                                                                                                                                                                      | 1                |

| lcc6                                                                                                               |      | 150  | _          | 130 |                                                                                                                                                                                                                                              | 110                                                                                                                                                                                                                                           | mA                                                                                                                                                                                                                                                                                        | t <sub>RC</sub> = min                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| I <sub>CC7</sub>                                                                                                   | _    | 130  | _          | 120 | _                                                                                                                                                                                                                                            | 110                                                                                                                                                                                                                                           | mA                                                                                                                                                                                                                                                                                        | t <sub>PC</sub> = min                                                                                                                                                                                                                                                                                                                                                                                                         | 1, 3             |

|                                                                                                                    | lcc2 | cc2  | CC1        | CC1 | Icc1     —     170     —     150       Icc2     —     2     —     2       —     1     —     1       —     200     —     200       Icc3     —     150     —     130       Icc5     —     5     —     5       Icc6     —     150     —     130 | Icc1     —     170     —     150     —       Icc2     —     2     —     2     —       —     1     —     1     —       —     200     —     200     —       Icc3     —     150     —     130     —       Icc6     —     150     —     130     — | Icc1     —     170     —     150     —     130       Icc2     —     2     —     2     —     2       —     1     —     1     —     1       —     200     —     200     —     200       Icc3     —     150     —     130     —     110       Icc6     —     150     —     130     —     110 | Icc1       —       170       —       150       —       130       mA         Icc2       —       2       —       2       —       2       mA         —       1       —       1       —       1       mA         —       200       —       200       —       200       µA         Icc3       —       150       —       130       —       110       mA         Icc6       —       150       —       130       —       110       mA | I <sub>CC1</sub> |

## HITACHI/ LOGIC/ARRAYS/MEN

## HM514260, HM514260L Series

**DC** Characteristics (Ta = 0 to 70°C,  $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ) (cont)

#### HM514260-7 HM514260-8 HM514260-10

| Parameter                                                                  | Symbol            | Min | Max             | Min | Max             | Min | Max             | Unit | Test conditions                                                                                                                 | Notes |

|----------------------------------------------------------------------------|-------------------|-----|-----------------|-----|-----------------|-----|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------|-------|

| Battery back up<br>current<br>(Standby with<br>CBR refresh)<br>(L-version) | l <sub>CC10</sub> | _   | 300             |     | 300             | _   | 300             | μА   | Standby: CMOS interface Dout = High-Z CBR refresh: $t_{RC}$ = 125 $\mu$ s $t_{RAS} \le 1$ $\mu$ s, CAS = $V_{IL}$ WE = $V_{IH}$ | 4     |

| Input leakage current                                                      | lLI               | -10 | 10              | -10 | 10              | -10 | 10              | μА   | 0 V ≤ Vin ≤ 7 V                                                                                                                 |       |

| Output leakage current                                                     | lLO               | -10 | 10              | -10 | 10              | -10 | 10              | μА   | 0 V ≤ Vout ≤ 7 V<br>Dout = disable                                                                                              | ,     |

| Output high voltage                                                        | V <sub>OH</sub>   | 2.4 | v <sub>cc</sub> | 2.4 | v <sub>cc</sub> | 2.4 | V <sub>CC</sub> | ٧    | High lout = -5 mA                                                                                                               |       |

| Output low voltage                                                         | V <sub>OL</sub>   | 0   | 0.4             | 0   | 0.4             | 0   | 0.4             | ٧    | Low lout = 4.2 mA                                                                                                               |       |

- Notes: 1. I<sub>CC</sub> depends on output load condition when the device is selected, I<sub>CC</sub> max is specified at the output open condition.

- 2. Address can be changed once or less while  $\overline{RAS} = V_{|L}$ .

- 3. Address can be changed once or less while LCAS and UCAS =  $V_{IH}$ . 4.  $V_{IH} \ge V_{CC} 0.2 \text{ V}$ ,  $V_{IL} \le 0.2 \text{ V}$

## Capacitance (Ta = 25°C, $V_{CC} = 5 \text{ V} \pm 10\%$ )

| Parameter                              | Symbol           | Тур | Max | Unit | Notes |

|----------------------------------------|------------------|-----|-----|------|-------|

| Input capacitance (Address)            | C <sub>I1</sub>  | *** | 5   | pF   | 1     |

| Input capacitance (Clocks)             | C <sub>12</sub>  | _   | 7   | pF   | 1     |

| Output capacitance (Data-in, Data-out) | C <sub>I/O</sub> | _   | 10  | pF   | 1, 2  |

Notes: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2. LCAS and UCAS = V<sub>IH</sub> to disable Dout

AC Characteristics (Ta = 0 to 70°C,  $V_{CC}$  = 5 V  $\pm$  10%,  $V_{SS}$  = 0 V) \*1,\*14,\*15,\*17,\*18

#### **Test Conditions**

## HITACHI/ LOGIC/ARRAYS/MEM

· Input rise and fall times: 5 ns

• Input timing reference levels: 0.8 V, 2.4 V

Output load: 2 TTL gate + C<sub>L</sub> (100 pF) (Including scope and jig)

### Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

| Parameter                        | Symbol           | Min | Max   | Min | Max         | Min | Max   | Unit | Notes |

|----------------------------------|------------------|-----|-------|-----|-------------|-----|-------|------|-------|

| Random read or write cycle time  | t <sub>RC</sub>  | 130 | _     | 150 | _           | 180 | _     | ns   |       |

| RAS precharge time               | t <sub>RP</sub>  | 50  | _     | 60  | _           | 70  | _     | ns   |       |

| RAS pulse width                  | t <sub>RAS</sub> | 70  | 10000 | 80  | 10000       | 100 | 10000 | ns   |       |

| CAS pulse width                  | tCAS             | 20  | 10000 | 20  | 10000       | 25  | 10000 | ns   |       |

| Row address setup time           | t <sub>ASR</sub> | 0   | _     | 0   | _           | 0   | _     | ns   |       |

| Row address hold time            | <sup>t</sup> RAH | 10  | _     | 10  |             | 15  |       | ns   |       |

| Column address setup time        | t <sub>ASC</sub> | 0   | _     | 0   | _           | 0   | _     | ns   | 19    |

| Column address hold time         | <sup>t</sup> CAH | 15  | _     | 15  | _           | 20  | _     | ns   | 19    |

| RAS to CAS delay time            | <sup>t</sup> RCD | 20  | 50    | 20  | 60          | 25  | 75    | ns   | .8    |

| RAS to column address delay time | t <sub>RAD</sub> | 15  | 35    | 15  | 40          | 20  | 55    | ns   | 9     |

| RAS hold time                    | <sup>t</sup> RSH | 20  | _     | 20  | <del></del> | 25  | _     | ns   |       |

| CAS hold time                    | t <sub>CSH</sub> | 70  |       | 80  |             | 100 |       | ns   |       |

| CAS to RAS precharge time        | tCRP             | 15  | _     | 15  | _           | 15  | _     | ns   | 20    |

| OE to Din delay time             | topp             | 20  | _     | 20  | _           | 25  | _     | . ns |       |

| OE delay time from Din           | t <sub>DZO</sub> | 0   | _     | 0   | _           | 0   | _     | ns   |       |

| CAS setup time from Din          | tozc             | 0   | _     | 0   | _           | 0   | _     | ns   |       |

| Transition time (rise and fall)  | t <sub>T</sub>   | 3   | 50    | 3   | 50          | 3   | 50    | ns   | 7     |

| Refresh period                   | t <sub>REF</sub> |     | 8     | _   | 8           | _   | 8     | ms   |       |

| Refresh period (L-version)       | t <sub>REF</sub> |     | 128   | _   | 128         |     | 128   | ms   |       |

# 61E D = 4496203 0023145 109 = HIT2

# HM514260, HM514260L Series

## HITACHI/ LOGIC/ARRAYS/MEM

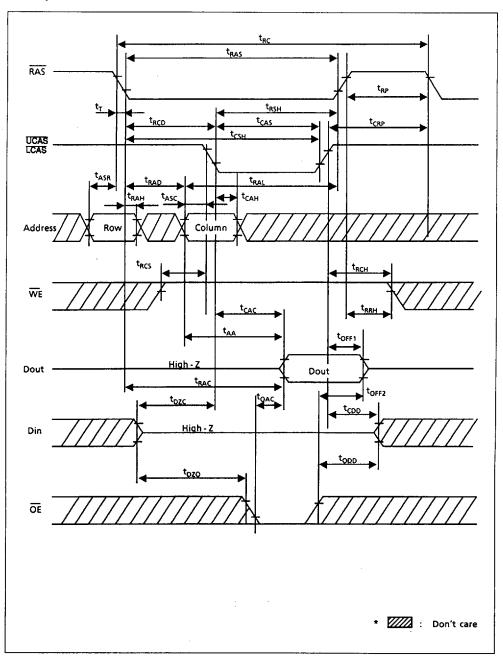

Read Cycle

### HM514260-7 HM514260-8 HM514260-10

| Parameter                       | Symbol            | Min | Max         | Min | Max | Min | Max         | <br>Unit | Notes    |  |

|---------------------------------|-------------------|-----|-------------|-----|-----|-----|-------------|----------|----------|--|

| Access time from RAS            | t <sub>RAC</sub>  | _   | 70          | _   | 80  | _   | 100         | ns       | 2, 3     |  |

| Access time from CAS            | †CAC              | _   | 20          | _   | 20  |     | 25          | ns       | 3, 4, 13 |  |

| Access time from address        | t <sub>AA</sub>   | _   | 35          | _   | 40  |     | 45          | ns       | 3, 5, 13 |  |

| Access time from OE             | tOAC              | _   | 20          |     | 20  | _   | 25          | ns       |          |  |

| Read command setup time         | tRCS              | 0   | _           | 0   | _   | 0   | _           | ns       | 19       |  |

| Read command hold time to CAS   | <sup>t</sup> RCH  | 0   | _           | 0   |     | 0   | <del></del> | ns       | 16, 19   |  |

| Read command hold time to RAS   | <sup>t</sup> RRH  | 0   | _           | 0   | _   | 0   | _           | ns       | 16       |  |

| Column address to RAS lead time | t <sub>RAL</sub>  | 35  | <del></del> | 40  | _   | 55  | _           | ns       |          |  |

| Output buffer turn-off time     | <sup>t</sup> OFF1 | 0   | 15          | 0   | 15  | 0   | 20          | ns       | 6        |  |

| Output buffer turn-off to OE    | t <sub>OFF2</sub> | 0   | 15          | 0   | 15  | 0   | 20          | ns       | 6        |  |

| CAS to Din delay time           | t <sub>CDD</sub>  | 15  | _           | 15  |     | 20  |             | ns       |          |  |

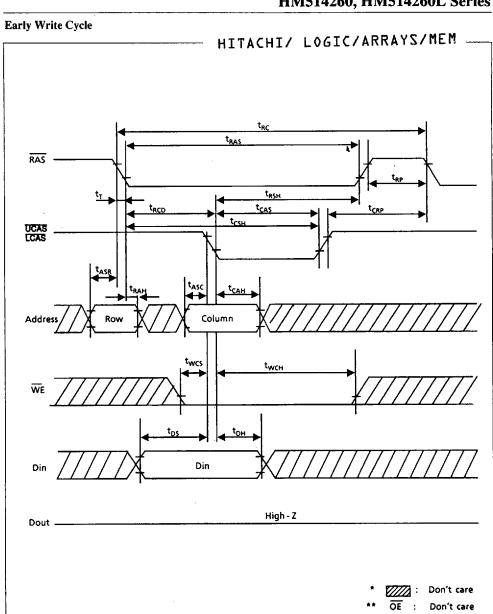

## Write Cycle

| Symbol           | Min                         | Max                                                | Min                                                              | Max                                                                                 | Min                                                                                                     | Max                                                                                                                                                                                                                                                                                                  | <br>Unit                                                                                                                                                              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------|-----------------------------|----------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| twcs             | 0                           | _                                                  | 0                                                                | _                                                                                   | 0                                                                                                       | -                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                    | 10, 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| twch             | 15                          | _                                                  | 15                                                               | _                                                                                   | 20                                                                                                      | _                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| t <sub>WP</sub>  | 10                          | _                                                  | 10                                                               | _                                                                                   | 20                                                                                                      |                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| <sup>t</sup> RWL | 20                          | _                                                  | 20                                                               | _                                                                                   | 25                                                                                                      | _                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| tcwL             | 20                          | _                                                  | 20                                                               | _                                                                                   | 25                                                                                                      |                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| t <sub>DS</sub>  | 0                           | _                                                  | 0                                                                | _                                                                                   | 0                                                                                                       | _                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                    | 11, 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| t <sub>DH</sub>  | 15                          | _                                                  | 15                                                               | _                                                                                   | 20                                                                                                      |                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                    | 11, 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| t <sub>COD</sub> | _                           | 0                                                  | _                                                                | 0                                                                                   | _                                                                                                       | 0                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                    | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                  | twcs twcH twP trwL tcwL tos | twcs 0 twcH 15 twP 10 tRWL 20 tcWL 20 tDS 0 tDH 15 | twcs 0 — twch 15 — twp 10 — trwc 20 — tcwc 20 — tos 0 — toh 15 — | twcs 0 — 0 twch 15 — 15 twp 10 — 10 trwl 20 — 20 tcwl 20 — 20 tbs 0 — 0 tdh 15 — 15 | twcs 0 — 0 —  twch 15 — 15 —  twp 10 — 10 —  trul 20 — 20 —  tcwl 20 — 20 —  tos 0 — 0 —  toh 15 — 15 — | twcs     0     —     0     —     0       twch     15     —     15     —     20       twp     10     —     10     —     20       tRWL     20     —     20     —     25       tcwl     20     —     20     —     25       tDS     0     —     0     —     0       tDH     15     —     15     —     20 | twcs 0 - 0 - 0 -   twch 15 - 15 - 20 -   twp 10 - 10 - 20 -   trunch 20 - 20 - 25 -   tcwl 20 - 20 - 25 -   tds 0 - 0 - 0 -   tdh 15 - 15 - 20 -   tdh 15 - 15 - 20 - | twcs         0         —         0         —         0         —         ns           twch         15         —         15         —         20         —         ns           twp         10         —         10         —         20         —         ns           tRWL         20         —         20         —         25         —         ns           tCWL         20         —         20         —         25         —         ns           tDS         0         —         0         —         0         —         ns           tDH         15         —         15         —         20         —         ns |  |

## Read-Modify-Write Cycle

# HITACHI/ LOGIC/ARRAYS/MEM

| Parameter                       | Symbol           | Min | Max | Min | Max                                          | Min | Max | <br>Unit | Notes  |

|---------------------------------|------------------|-----|-----|-----|----------------------------------------------|-----|-----|----------|--------|

| Read-modify-write cycle time    | tRWC             | 180 | _   | 200 | _                                            | 245 | _   | ns       |        |

| RAS to WE delay time            | t <sub>RWD</sub> | 95  | _   | 105 | -                                            | 135 | _   | ns       | 10     |

| CAS to WE delay time            | <sup>t</sup> CWD | 45  | _   | 45  | _                                            | 60  | _   | ns       | 10     |

| Column address to WE delay time | tawd             | 60  | _   | 65  | <u>,                                    </u> | 80  | _   | ns       | 10, 13 |

| OE hold time from WE            | <sup>t</sup> OEH | 20  | _   | 20  |                                              | 25  | _   | ns       |        |

#### Refresh Cycle

| Parameter                                        | Symbol           | Min | Max | Min | Max | Min | Max | –<br>Unit | Note |

|--------------------------------------------------|------------------|-----|-----|-----|-----|-----|-----|-----------|------|

| CAS setup time<br>(CAS-before-RAS refresh cycle) | t <sub>CSR</sub> | 10  |     | 10  | _   | 10  | _   | ns        | 19   |

| CAS hold time<br>(CAS-before-RAS refresh cycle)  | <sup>t</sup> CHR | 10  | _   | 10  | -   | 10  |     | ns        | 20   |

| RAS precharge to CAS hold time                   | tRPC             | 10  | _   | 10  | _   | 10  | _   | ns        | 19   |

| CAS precharge time in normal mode                | <sup>†</sup> CPN | 10  | _   | 10  | _   | 10  |     | ns        | 22   |

#### Fast Page Mode Cycle

### HITACHI/ LOGIC/ARRAYS/MEM

#### HM514260-7 HM514260-8 HM514260-10

|                                                                       | Symbol            |     |        |     |        |     |        |      |              |

|-----------------------------------------------------------------------|-------------------|-----|--------|-----|--------|-----|--------|------|--------------|

| Parameter                                                             |                   | Min | Max    | Min | Max    | Min | Max    | Unit | Notes        |

| Fast page mode cycle time                                             | tpc               | 50  | _      | 55  | _      | 60  |        | ns   |              |

| Fast page mode CAS precharge time                                     | t <sub>CP</sub>   | 15  | _      | 15  | _      | 15  |        | ns   | 22           |

| Fast page mode RAS pulse width                                        | <sup>t</sup> RASC |     | 100000 | _   | 100000 | )   | 100000 | ns   | 12           |

| Access time from CAS precharge                                        | <sup>t</sup> ACP  | _   | 40     | _   | 45     | _   | 50     | ns   | 3, 13,<br>20 |

| RAS hold time from CAS precharge                                      | †RHCP             | 40  | _      | 45  |        | 50  |        | ns   |              |

| Fast page mode read-modify-write cycle CAS precharge to WE delay time | <sup>t</sup> CPW  | 65  | _      | 70  |        | 85  | _      | ns   |              |

| Fast page mode read-modify-write cycle time                           | <sup>t</sup> PCM  | 95  | _      | 100 | _      | 110 |        | ns   |              |

#### Counter Test Cycle

| Parameter                                | Symbol           | Min | Max | Min | Max | Min | Max | Unit | Note |

|------------------------------------------|------------------|-----|-----|-----|-----|-----|-----|------|------|

| CAS precharge time in counter test cycle | <sup>t</sup> CPT | 50  |     | 50  | _   | 50  |     | 'ns  | 22   |

- Notes: 1. AC measurements assume  $t_T = 5$  ns.

- Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max) and t<sub>RAD</sub> ≤ t<sub>RAD</sub> (max). If t<sub>RCD</sub> or t<sub>RAD</sub> is greater than the maximum recommended value shown in this table, tRAC exceeds the value shown.

- 3. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

- Assumes that t<sub>RCD</sub> ≥ t<sub>RCD</sub> (max) and t<sub>RAD</sub> ≤ t<sub>RAD</sub> (max).

- Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max) and t<sub>RAD</sub> ≥ t<sub>RAD</sub> (max).

- 6. topp (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 7. VIH (min) and VIL (max) are reference levels for measuring timing of input signals. Also, transition times are measured between VIH and VIL.

- 8. Operation with the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met,  $t_{RCD}$  (max) is specified as a reference point only, if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 9. Operation with the t<sub>RAD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met, t<sub>RAD</sub> (max) is specified as a reference point only, if tran is greater than the specified tran (max) limit, then access time is controlled exclusively by tAA.

- 10. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only: if t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min), t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min), t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min) and t<sub>CPW</sub> ≥ t<sub>CPW</sub> (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- 11. These parameters are referenced to CAS leading edge in an early write cycle and to WE leading edge in a delayed write or a read-modify-write cycle.

- 12. tRASC defines RAS pulse width in fast page mode cycles.

- 13. Access time is determined by the longer of tAA or tCAC or tACP.

- 14. An initial pause of 100 μs is required after power up followed by a minimum of eight initialization cycles (RAS-only refresh cycle or CAS-before-RAS refresh cycle). If the internal refresh counter is used, a minimum of eight CAS-before-RAS refresh cycles is required.

- In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.

- 16. Either t<sub>RCH</sub> or T<sub>RRH</sub> must be satisfied for a read cycle.

- 17. When both LCAS and UCAS go low at the same time, all 16-bits data are written into the device. LCAS and UCAS cannot be straggered within the same write/read cycles.

- 18. All the V<sub>CC</sub> and V<sub>SS</sub> pins shall be supplied with the same voltages.

- 19. t<sub>ASC</sub>, t<sub>CAH</sub>, t<sub>RCS</sub>, t<sub>RCH</sub>, t<sub>WCS</sub>, t<sub>WCH</sub>, t<sub>DS</sub>, t<sub>DH</sub>, t<sub>CSR</sub>, and t<sub>RPC</sub> are determined by the earlier falling edge of UCAS or LCAS.

- 20. t<sub>CRP</sub>, t<sub>CHR</sub>, t<sub>ACP</sub>, and t<sub>CPW</sub> are determined by the later rising edge of UCAS or LCAS.

- 21. t<sub>CWI</sub> should be satisfied by both UCAS and LCAS.

- 22. t<sub>CPN</sub>, t<sub>CP</sub>, and t<sub>CPT</sub> are determined by the time that both UCAS and LCAS are high.

- 23. Do not enable Dout buffer when using delayed write timing.

HITACHI/ LOGIC/ARRAYS/MEM

# HITACHI/ LOGIC/ARRAYS/MEM

# HM514260, HM514260L Series

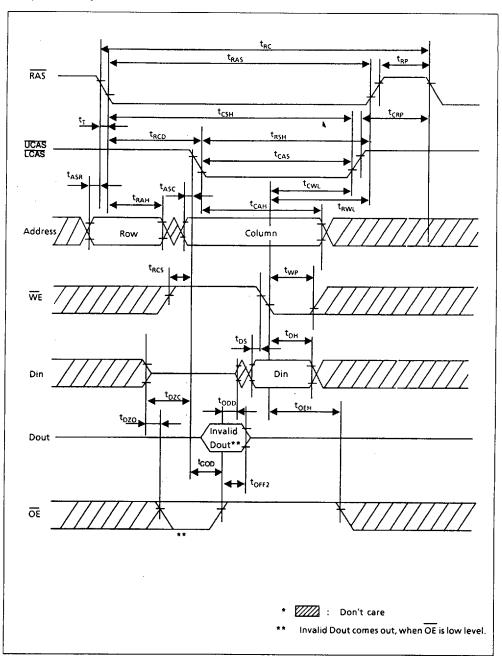

## **Timing Waveforms**

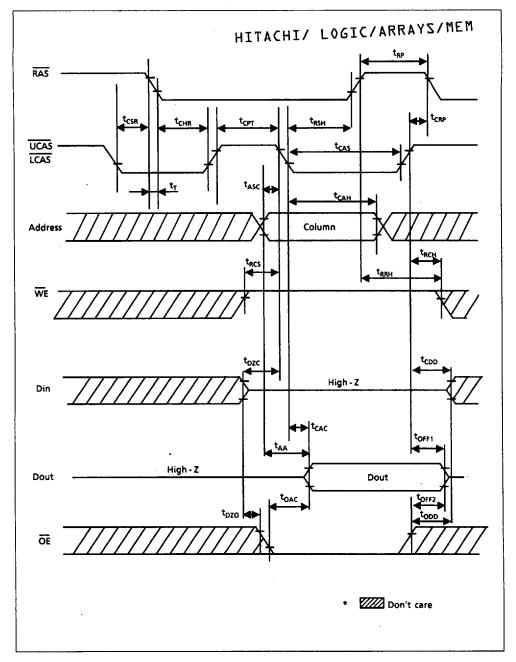

## Read Cycle

# HITACHI/ LOGIC/ARRAYS/MEM

# HM514260, HM514260L Series

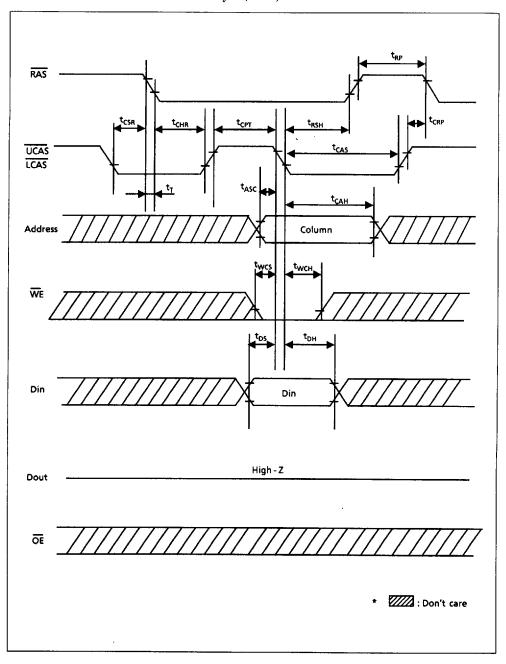

Delayed Write Cycle

Read-Modify-Write Cycle HITACHI/ LOGIC/ARRAYS/MEM RAS UCAS **LCAS** Address Row t<sub>RWI</sub> tozc Dout t<sub>OEH</sub> t<sub>DZO</sub> ŌE \* Don't care

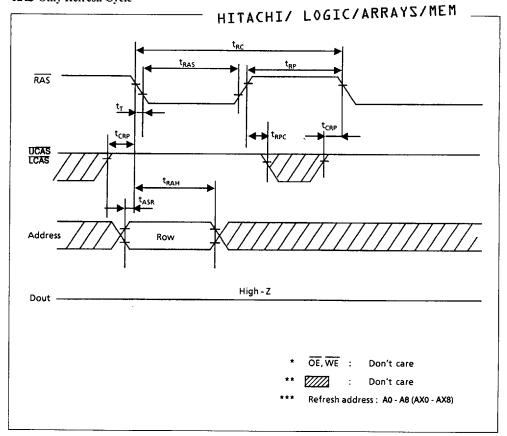

### RAS-Only Refresh Cycle

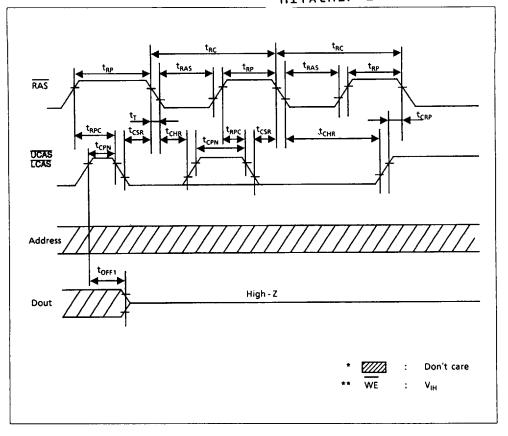

## CAS-Before-RAS Refresh Cycle

# HITACHI/ LOGIC/ARRAYS/MEM

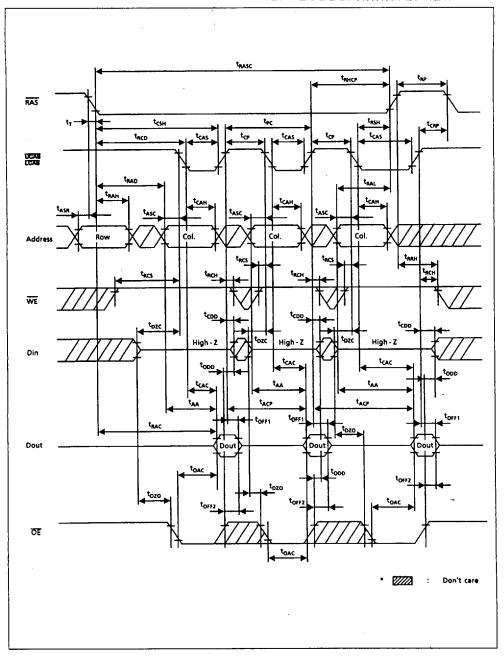

# Hidden Refresh Cycle HITACHI/ LOGIC/ARRAYS/MEM (Refresh) (Refresh) (Read) RAS $t_{CHR}$ $t_{CAS}$ UCAS LCAS t<sub>ASR</sub> tRAL Column Address t<sub>RCH</sub> WE Dout Dout t<sub>DZC</sub> t<sub>OFF2</sub> High - Z Din $t_{ODD}$ ŌĒ

Don't care

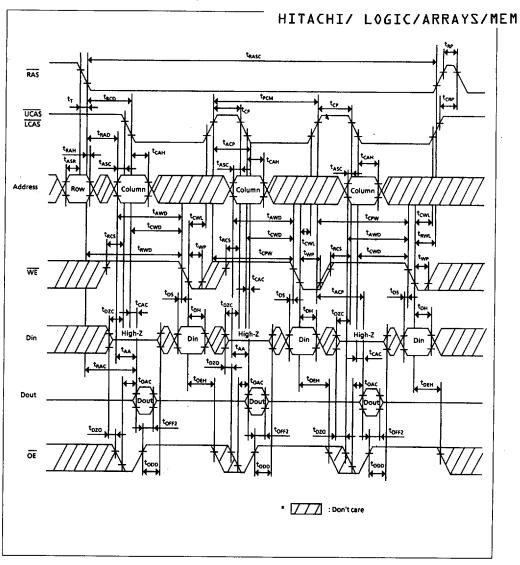

Fast Page Mode Read Cycle

## HITACHI/ LOGIC/ARRAYS/MEM

# HITACHI/ LOGIC/ARRAYS/MEM

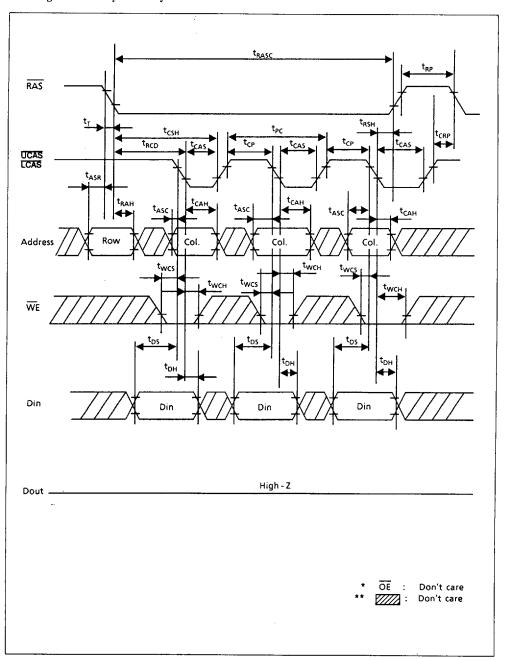

Fast Page Mode Early Write Cycle

Fast Page Mode Delayed Write Cycle HITACHI/ LOGIC/ARRAYS/MEM RAS t<sub>RSH</sub> UCAS LCAS Address WE Din High - Z Dout todo ŌE \* ZZZ Don't care

## Fast Page Mode Read-Modify-Write Cycle

## CAS-Before-RAS Refresh Counter Check Cycle (Read)

HITACHI/ LOGIC/ARRAYS/MEM

# HM514260, HM514260L Series

CAS-Before-RAS Refresh Counter Check Cycle (Write)

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.