8192-word × 8-bit CMOS Electrically Erasable and Programmable CMOS ROM

# **HITACHI**

ADE-203-375F (Z) Rev. 6.0 Apr. 12, 1995

#### **Description**

The Hitachi HN58C66 is a electrically erasable and programmable ROM organized as 8192-word  $\times$  8-bit. It realizes high speed, low power consumption, and a high level of reliability, employing advanced MNOS memory technology and CMOS process and circuitry technology. It also has a 32-byte page programming function to make its erase and write operations faster.

#### **Features**

- Single 5 V supply

- On chip latches: address, data,  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{WE}$

- Automatic byte write: 10 ms max

- Automatic page write (32 bytes): 10 ms max

- High speed: Access time 250 ns max

- Low power dissipation:

- 20 mW/MHz typ (active)

- 2.0 mW typ (standby)

- Data polling, RDY/Busy

- Data protection circuit on power on/off

- · Conforms to JEDEC byte-wide standard

- Reliable CMOS with MNOS cell technology

- 10<sup>5</sup> erase/write cycles (in page mode)

- 10 years data retension

- Write protection by RES pin

## **Ordering Information**

| Type No      | Access Time | Package                                      |

|--------------|-------------|----------------------------------------------|

| HN58C66P-25  | 250 ns      | 600-mil 28-pin plastic DIP (DP-28)           |

| HN58C66FP-25 | 250 ns      | 28-pin plastic SOP <sup>*1</sup> (FP-28D/DA) |

| HN58C66T-25  | 250 ns      | 32-pin plastic TSOP (TFP-32DA)               |

Note: 1. T is added to the end of the type no. for a SOP of 3.00 mm (max) thickness.

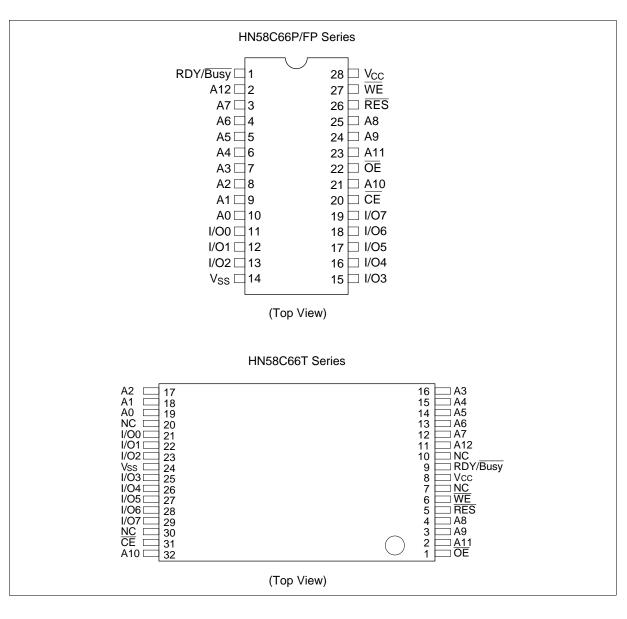

#### **Pin Arrangement**

### **Pin Description**

| Pin Name        | Function            |

|-----------------|---------------------|

| A0 – A12        | Address             |

| I/O0 – I/O7     | Data input/output   |

| ŌĒ              | Output enable       |

| CE              | Chip enable         |

| WE              | Write enable        |

| V <sub>cc</sub> | Power supply (+5 V) |

| V <sub>SS</sub> | Ground              |

| RES             | Reset               |

| NC              | No connection       |

| RDY/Busy        | Ready/Busy          |

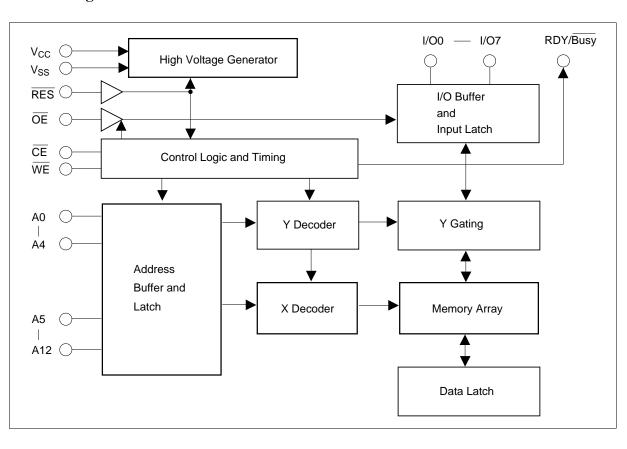

### **Block Diagram**

#### **Mode Selection**

| Pin Mode      | CE              | OE              | WE              | RDY/Busy                  | RES               | I/O             |

|---------------|-----------------|-----------------|-----------------|---------------------------|-------------------|-----------------|

| Read          | $V_{IL}$        | $V_{IL}$        | $V_{IH}$        | High-Z                    | V <sub>H</sub> *1 | Dout            |

| Standby       | $V_{\text{IH}}$ | X*2             | Χ               | High-Z                    | Χ                 | High-Z          |

| Write         | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | High-Z to V <sub>OL</sub> | V <sub>H</sub>    | Din             |

| Deselect      | $V_{\text{IL}}$ | $V_{\text{IH}}$ | $V_{\text{IH}}$ | High-Z                    | $V_{H}$           | High-Z          |

| Write inhibit | Χ               | Χ               | $V_{\text{IH}}$ | High-Z                    | Χ                 | _               |

|               | X               | V <sub>IL</sub> | Х               |                           |                   |                 |

| Data polling  | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>OL</sub>           | V <sub>H</sub>    | Data out (I/O7) |

| Program reset | Х               | Х               | Х               | High-Z                    | V <sub>IL</sub>   | High-Z          |

Notes: 1. Refer to the recommended DC operating condition.

2. X = Don't care.

### **Absolute Maximum Ratings**

| Parameter                                 | Symbol          | Value                      | Unit |

|-------------------------------------------|-----------------|----------------------------|------|

| Supply voltage <sup>*1</sup>              | V <sub>cc</sub> | -0.6 to +7.0               | V    |

| Input voltage <sup>*1</sup>               | Vin             | -0.5 <sup>*2</sup> to +7.0 | V    |

| Operating temperature range <sup>*3</sup> | Topr            | 0 to +70                   | °C   |

| Storage temperature range                 | Tstg            | -55 to +125                | °C   |

Notes: 1. With respect to V<sub>ss</sub>

2. Vin min = -3.0 V for pulse width  $\leq 50$  ns

3. Including electrical characteristics and data retention

### **Recommended DC Operating Conditions**

| Parameter             | Symbol          | Min                   | Тур | Max                   | Unit |

|-----------------------|-----------------|-----------------------|-----|-----------------------|------|

| Supply voltage        | V <sub>cc</sub> | 4.5                   | 5.0 | 5.5                   | V    |

| Input voltage         | $V_{IL}$        | -0.3                  | _   | 0.8                   | V    |

|                       | V <sub>IH</sub> | 2.2                   | _   | V <sub>cc</sub> + 1.0 | V    |

|                       | V <sub>H</sub>  | $V_{\text{CC}} - 0.5$ | _   | V <sub>cc</sub> + 1.0 | V    |

| Operating temperature | Topr            | 0                     | _   | 70                    | °C   |

### **DC Characteristics** (Ta = 0 to +70°C, $V_{CC} = 5 \text{ V} \pm 10\%$ )

| Parameter                         | Symbol           | Min                | Тур | Max                   | Unit | <b>Test Conditions</b>                                                       |

|-----------------------------------|------------------|--------------------|-----|-----------------------|------|------------------------------------------------------------------------------|

| Input leakage current             | I <sub>LI</sub>  | _                  | _   | 2 <sup>*1</sup>       | μΑ   | $V_{CC} = 5.5 \text{ V},$<br>Vin = 5.5 V                                     |

| Output leakage current            | I <sub>LO</sub>  | _                  | _   | 2                     | μΑ   | V <sub>cc</sub> = 5.5 V,<br>Vout = 5.5/0.4 V                                 |

| V <sub>cc</sub> current (standby) | I <sub>CC1</sub> | _                  | _   | 1                     | mA   | $\overline{\text{CE}} = V_{\text{IH}}, \overline{\text{CE}} = V_{\text{CC}}$ |

| V <sub>cc</sub> current (active)  | I <sub>CC2</sub> | _                  | _   | 8                     | mA   | lout = 0 mA,<br>Duty = 100%,<br>Cycle = 1 $\mu$ s at<br>$V_{cc}$ = 5.5 V     |

|                                   |                  | _                  | _   | 25                    | mA   | lout = 0 mA,<br>Duty = 100%<br>Cycle = 250 ns<br>at $V_{cc}$ = 5.5 V         |

| Input low voltage                 | V <sub>IL</sub>  | -0.3 <sup>*2</sup> | _   | 0.8                   | V    |                                                                              |

| Input high voltage                | $V_{IH}$         | 2.2                | _   | V <sub>cc</sub> + 1.0 | V    |                                                                              |

|                                   | $V_{H}$          | $V_{\rm cc}-0.5$   | _   | V <sub>cc</sub> + 1.0 | V    |                                                                              |

| Output low voltage                | $V_{OL}$         | _                  | _   | 0.4                   | V    | I <sub>OL</sub> = 2.1 mA                                                     |

| Output high voltage               | $V_{OH}$         | 2.4                | _   | _                     | V    | $I_{OH} = -400  \mu A$                                                       |

Notes: 1.  $I_{LI}$  on  $\overline{RES}$  = 100  $\mu$ A max.

2.  $V_{IL}$  min = -1.0 V for pulse width  $\leq$  50 ns

### **Capacitance** (Ta = 25°C, f = 1 MHz)

| Parameter          | Symbol             | Min | Тур | Max | Unit | Test Conditions |

|--------------------|--------------------|-----|-----|-----|------|-----------------|

| Input capacitance  | Cin*1              | _   | _   | 6   | pF   | Vin = 0 V       |

| Output capacitance | Cout <sup>*1</sup> | _   | _   | 12  | pF   | Vout = 0 V      |

Note: 1. This parameter is periodically sampled and not 100% tested.

### **AC Characteristics** (Ta = 0 to +70°C, $V_{CC}$ = 5 V ± 10%)

#### **Test Conditions**

• Input pulse levels: 0.4 V to 2.4 V,  $0 \text{ to V}_{CC}$  ( $\overline{RES}$  pin)

• Input rise and fall time: ≤ 20 ns

Output load: 1TTL gate +100 pF

• Reference levels for measuring timing: 0.8 V, 2.0 V

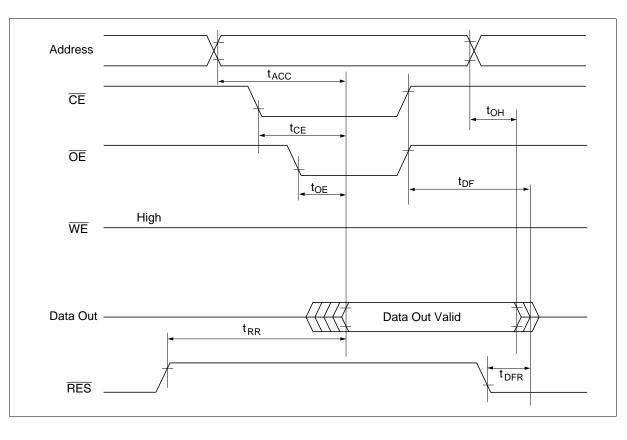

#### Read Cycle

| Parameter                      | Symbol           | Min | Max | Unit | Test Conditions                                                    |

|--------------------------------|------------------|-----|-----|------|--------------------------------------------------------------------|

| Address to output delay        | t <sub>ACC</sub> | _   | 250 | ns   | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$   |

| CE to output delay             | t <sub>CE</sub>  | _   | 250 | ns   | $\overline{OE} = V_{IL}, \overline{WE} = V_{IH}$                   |

| OE to output delay             | t <sub>OE</sub>  | 10  | 100 | ns   | $\overline{CE} = V_{IL}, \overline{WE} = V_{IH}$                   |

| OE (CE) high to output float*1 | t <sub>DF</sub>  | 0   | 90  | ns   | $\overline{\text{CE}} = V_{IL}, \overline{\text{WE}} = V_{IH}$     |

| RES low to output float*1      | t <sub>DFR</sub> | 0   | 350 | ns   | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$   |

| Data output hold               | t <sub>oh</sub>  | 0   | _   | ns   | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$   |

| RES to output delay            | t <sub>RR</sub>  | 0   | 450 | ns   | $\overline{CE} = \overline{OE} = V_{IL}, \ \overline{WE} = V_{IH}$ |

Note: 1. t<sub>DF</sub>, t<sub>DFR</sub> is defined at which the outputs achieve the open circuit conditions and are no longer driven.

#### **Read Timing Waveform**

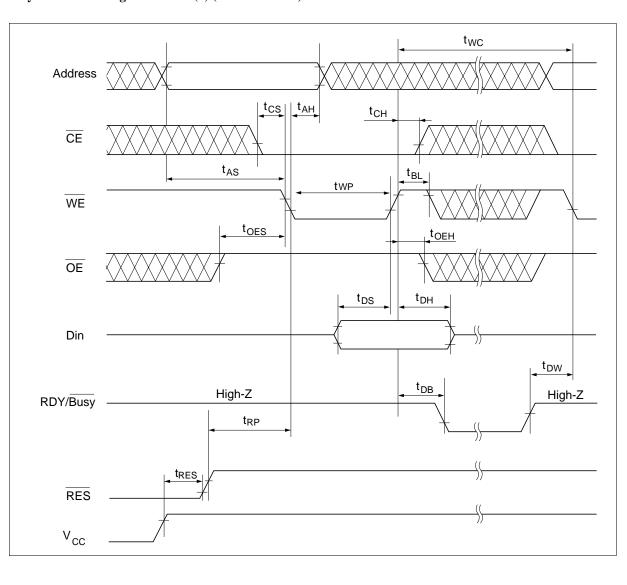

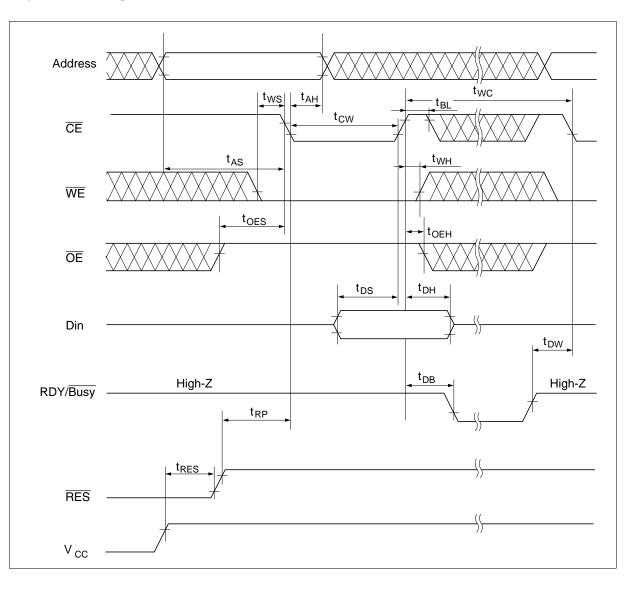

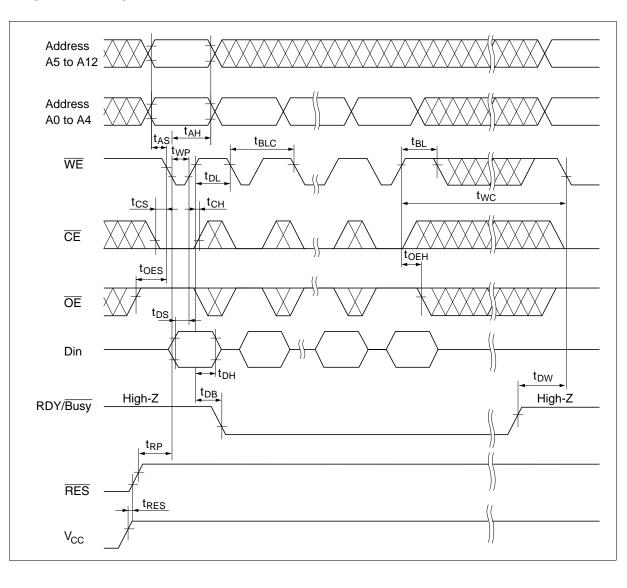

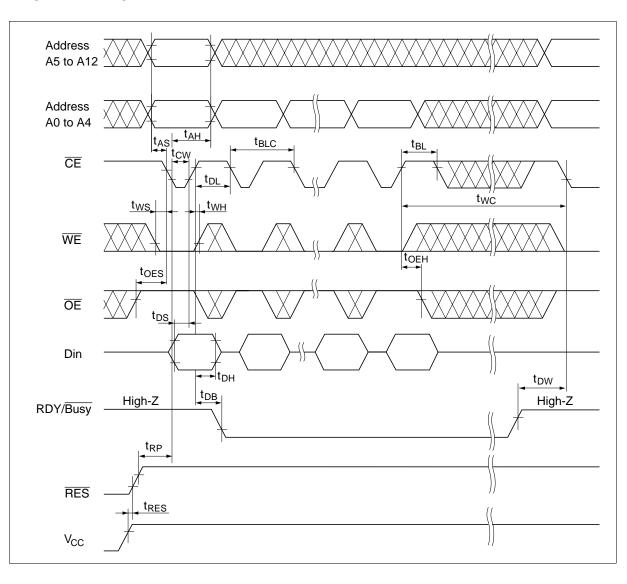

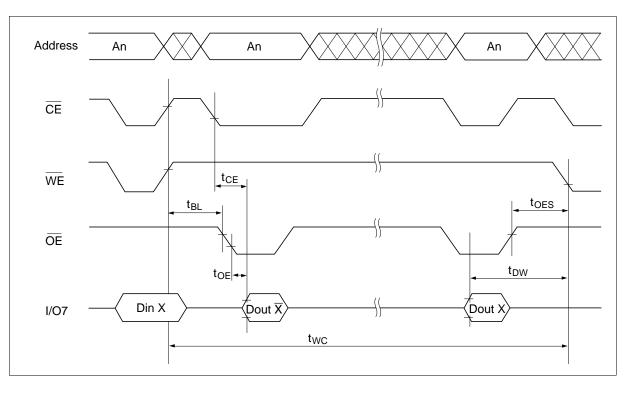

#### Write Cycle

| Parameter                              | Symbol                           | Min <sup>*1</sup> | Тур | Max  | Unit | <b>Test Conditions</b> |

|----------------------------------------|----------------------------------|-------------------|-----|------|------|------------------------|

| Address setup time                     | t <sub>AS</sub>                  | 0                 | _   | _    | ns   |                        |

| Address hold time                      | t <sub>AH</sub>                  | 150               | _   | _    | ns   |                        |

| CE to write setup time (WE controlled) | t <sub>CH</sub>                  | 0                 | _   | _    | ns   |                        |

| CE hold time (WE controlled)           | t <sub>CH</sub>                  | 0                 | _   | _    | ns   |                        |

| WE to write setup time (CE controlled) | t <sub>ws</sub>                  | 0                 | _   | _    | ns   |                        |

| WE hold time (CE controlled)           | t <sub>wh</sub>                  | 0                 | _   | _    | ns   |                        |

| OE to write setup time                 | $t_{\text{OES}}$                 | 0                 | _   | _    | ns   |                        |

| OE hold time                           | $t_{OEH}$                        | 0                 | _   | _    | ns   |                        |

| Data setup time                        | t <sub>DS</sub>                  | 100               | _   | _    | ns   |                        |

| Data hold time                         | $t_{\text{DH}}$                  | 20                | _   | _    | ns   |                        |

| WE pulse width (WE controlled)         | t <sub>WP</sub>                  | 200               | _   | _    | ns   |                        |

| CE pulse width (CE controlled)         | $t_{\scriptscriptstyle{\sf CW}}$ | 200               | _   | _    | ns   |                        |

| Data latch time                        | $t_{\scriptscriptstyle DL}$      | 100               | _   | _    | ns   |                        |

| Byte load cycle                        | $t_{\scriptscriptstyle BLC}$     | 0.30              | _   | 30   | μs   |                        |

| Byte load window                       | t <sub>BL</sub>                  | 100               | _   | _    | μs   |                        |

| Write cycle time                       | $t_{wc}$                         | _                 | _   | 10*2 | ms   |                        |

| Time to device busy                    | t <sub>DB</sub>                  | 120               | _   | _    | ns   |                        |

| Write start time                       | t <sub>DW</sub>                  | 150*3             | _   | _    | ns   |                        |

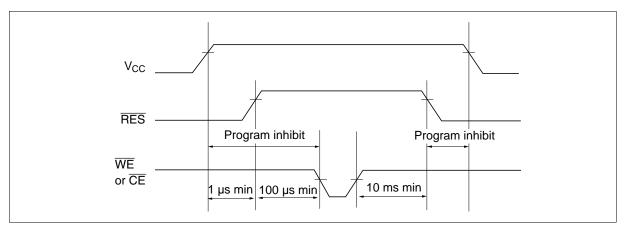

| Reset protect time                     | t <sub>RP</sub>                  | 100               | _   | _    | μs   |                        |

| Reset high time                        | t <sub>RES</sub>                 | 1                 | _   | _    | μs   |                        |

Notes: 1. Use this device in longer cycle than this value.

<sup>2.</sup>  $t_{wc}$  must be longer than this value unless polling technique or RDY/Busy are used. This device automatically completes the internal write operation within this value.

<sup>3.</sup> Next read or write operation can be initiated after  $t_{\scriptscriptstyle DW}$  if polling technique or RDY/ $\overline{\text{Busy}}$  are used.

### **Byte Write Timing Waveform (1)** (WE Controlled)

### **Byte Write Timing Waveform (2)** ( $\overline{\text{CE}}$ Controlled)

### Page Write Timing Waveform (1) (WE Controlled)

### Page Write Timing Waveform (2) (CE Controlled)

#### Data Polling Timing Waveform

### **Functional Description**

#### **Automatic Page Write**

Page-mode write feature allows 1 to 32 bytes of data to be written into the EEPROM in a single write cycle. Following the initial byte cycle, an additional 1 to 31 bytes can be written in the same manner. Each additional byte load cycle must be started within 30  $\mu$ s from the preceding falling edge of  $\overline{WE}$  or  $\overline{CE}$ . When  $\overline{CE}$  or  $\overline{WE}$  is high for 100  $\mu$ s after data input, the EEPROM enters write mode automatically and the input data are written into the EEPROM.

#### Data Polling

Data polling allows the status of the EEPROM to be determined. If EEPROM is set to read mode during a write cycle, an inversion of the last byte of data to be loaded outputs from I/O7 to indicate that the EEPROM is performing a write operation.

#### RDY/Busy Signal

RDY/ $\overline{Busy}$  signal also allows the status of the EEPROM to be determined. The RDY/ $\overline{Busy}$  signal has high impedance except in write cycle and is lowered to  $V_{OL}$  after the first write signal. At the end of a write cycle, the RDY/ $\overline{Busy}$  signal changes state to high impedance.

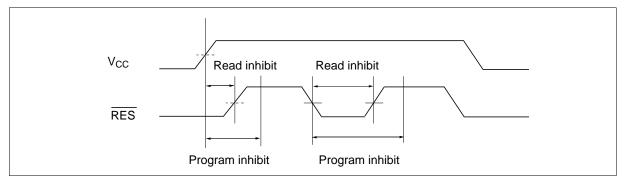

#### **RES** Signal

When  $\overline{RES}$  is low, the EEPROM cannot be read or programmed. Therefore, data can be protected by keeping  $\overline{RES}$  low when  $V_{CC}$  is switched.  $\overline{RES}$  should be high during read and programming because it doesn't provide a latch function.

#### WE, CE Pin Operation

During a write cycle, addresses are latched by the falling edge of  $\overline{WE}$  or  $\overline{CE}$ , and data is latched by the rising edge of  $\overline{WE}$  or  $\overline{CE}$ .

#### Write/Erase Endurance and Data Retention

The endurance is  $10^5$  cycles in case of the page programming and  $3 \times 10^3$  cycles in case of byte programming (1% cumulative failure rate). The data retention time is more than 10 years when a device is page-programmed less than  $10^4$  cycles.

#### **Data Protection**

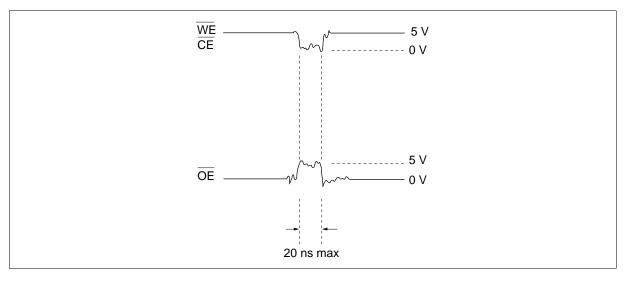

1. Data Protection against Noise on Control Pins ( $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{WE}$ ) during Operation

During readout or standby, noise on the control pins may act as a trigger and turn the EEPROM to program mode by mistake.

To prevent this phenomenon, this device has a noise cancelation function that cuts noise if its width is 20 ns or less in program mode.

Be careful not to allow noise of a width of more than 20 ns on the control pins.

#### 2. Data Protection at V<sub>CC</sub> On/Off

When  $V_{CC}$  is turned on or off, the noise on the control pins generated by external circuits (CPU, etc.) may act as a trigger and turn the EEPROM to program mode by mistake. To prevent this unintentional programming, the EEPROM must be kept in an unprogrammable state by using a CPU reset signal to  $\overline{RES}$  pin.  $\overline{RES}$  pin should be kept at  $V_{SS}$  level when  $V_{CC}$  is turned on and off. The EEPROM breaks off programming operation when  $\overline{RES}$  becomes low, programming operation doesn't finish correctly in case that  $\overline{RES}$  falls low during programming operation.  $\overline{RES}$  should be kept high for 10 ms after the last data input.

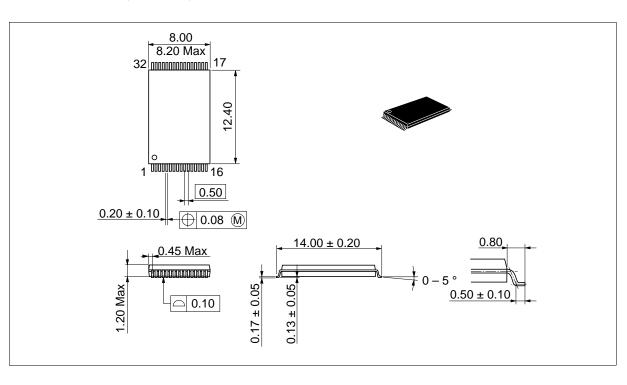

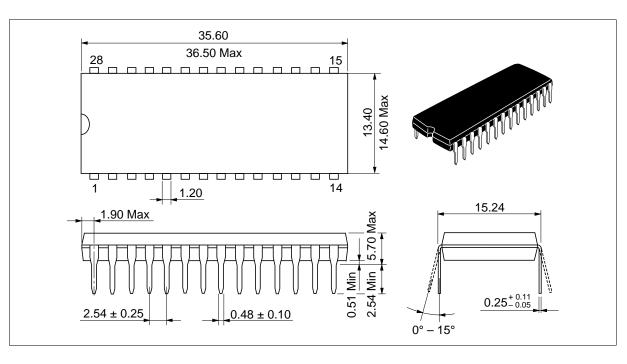

#### **Package Dimensions**

HN58C66P Series (DP-28)

Unit: mm

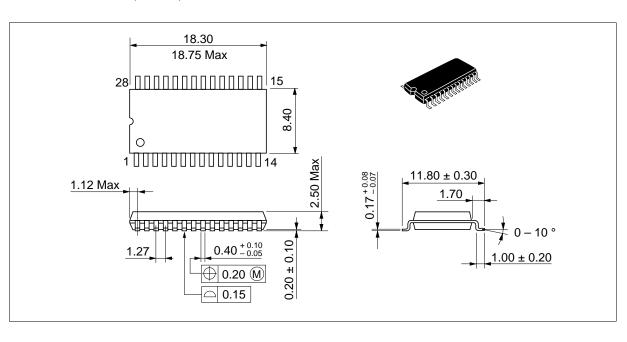

#### HN58C66FP Series (FP-28D)

Unit: mm

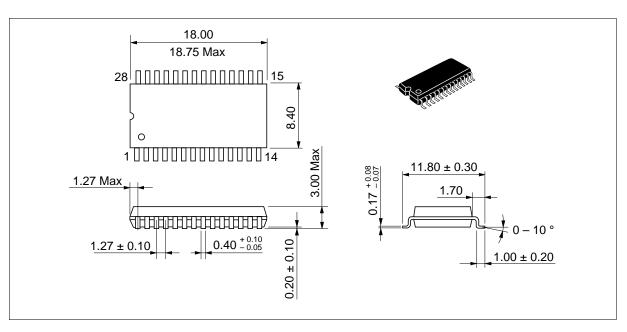

#### HN58C66FP Series (FP-28DA)

Unit: mm

#### HN58C66T Series (TFP-32DA)

Unit: mm