# IT8661F & IT8661RF

Plug and Play Super AT I/O

**Preliminary Specification V0.6**

Copyright ©1998 ITE, Inc.

This is Preliminary document release. All specifications are subject to change without notice. The material contained in this document supersedes all previous documentation issued for the related products included herein. Please contact ITE, Inc. for the latest document(s).

All sales are subject to ITE's Standard Terms and Conditions, a copy of which is included in the back of this document.

ITE, IT8661F and IT8661RF are trademarks of ITE, Inc.

Intel, Pentium, and MMX are claimed as trademarks by Intel Corp.

Cyrix, M1, and SLiC/MP are claimed as trademarks by Cyrix Corp.

AMD, AMD-K5, and AMD-K6 are claimed as trademarks by Advanced Micro Devices, Inc.

Microsoft and Windows are claimed as trademarks by Microsoft Corporation.

PCI is claimed as a trademark by the PCI Special Interest Group.

IrDA is claimed as a trademark by the Infrared Data Association.

All other trademarks are claimed by their respective owners.

All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

| ITE (USA) Inc.<br>Marketing Department<br>2710 Walsh Avenue<br>Santa Clara, CA 95051<br>U.S.A.          | Phone: (408) 980-8168<br>Fax: (408) 980-9232            |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| ITE (USA) Inc.<br>Eastern U.S.A. Sales Office<br>896 Summit St., #105<br>Round Rock, TX 78664<br>U.S.A. | Phone: (512) 388-7880<br>Fax: (512) 388-3108            |

| ITE, Inc.<br>Marketing Department<br>15F, No. 376, Jen-Ai Road, Sec. 4,<br>Taipei, Taiwan 106, R.O.C    | Phone: (02) 2707-9589<br>Fax: (02) 2703-3889, 2708-3186 |

If you have any marketing or sales questions, please contact:

David Lin, at ITE U.S.A: E-mail: david.lin@iteusa.com, Tel: (408) 980-8168 X238,

Fax: (408) 980-9232

Don Gardenhire, at ITE Eastern USA Office: E-mail: don.gardenhire@iteusa.com

Tel: (512) 388-7880, Fax: (512) 388-3108

Lawrence Liu, at ITE Taiwan: E-mail: lawrence.liu@ite.com.tw, Tel: 886-2-27079589 X6071,

Fax: 886-2-27038389

To find out more about ITE, visit our World Wide Web at: http://www.iteusa.com http://www.ite.com.tw

### CONTENTS

|    |      |        |                                                                           | Page |

|----|------|--------|---------------------------------------------------------------------------|------|

| 1. | Fea  | atures | S                                                                         | 1    |

| 2. | Ger  | neral  | Description                                                               | 3    |

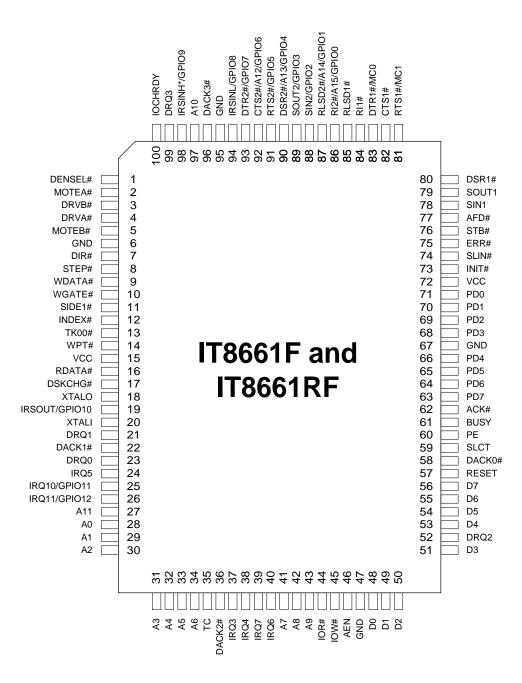

| 3. | Pin  | Con    | figuration                                                                | 3    |

| 4. | Blo  | ock D  | iagram                                                                    | 4    |

| 5. | IT8  | 661F   | and IT8661RF Pin Descriptions                                             | 5    |

| 6. | Cor  | nfigu  | ring Sequence Description                                                 | 9    |

| 6  | 5.1  | Gen    | eral Description                                                          | 9    |

| 6  | 6.2  | MB     | PnP Mode                                                                  | 10   |

| 6  | 5.3  | ISA    | PnP Mode                                                                  | 10   |

| 6  | 6.4  | Plug   | g and Play Operation Sequence                                             | 12   |

| 6  | 6.5  | Des    | cription of the Configuration Registers                                   | 13   |

|    | 6.5. | .1     | Logical Device Base Address                                               | 17   |

| 6  | 6.6  | Glob   | oal Configuration Registers (LDN: All)                                    | 18   |

|    | 6.6. | .1     | Set RD_DATA Port (Index=00h, ISA PnP)                                     | 18   |

|    | 6.6. | .2     | Serial Isolation (Index=01h, ISA PnP)                                     | 18   |

|    | 6.6. | .3     | Configure Control (Index=02h, ISA PnP/MB PnP)                             | 18   |

|    | 6.6. | .4     | Wake[CSN] (Index=03h, ISA PnP)                                            | 18   |

|    | 6.6. | .5     | Resource Data (Index=04h, ISA PnP)                                        | 18   |

|    | 6.6. | .6     | Status (Index=05h, ISA PnP)                                               | 18   |

|    | 6.6. | .7     | Card Select Number (CSN, Index=06h, Default=00h, ISA PnP)                 | 18   |

|    | 6.6. | .8     | Logical Device Number (LDN, Index=07h, ISA PnP/MB PnP)                    | 18   |

|    | 6.6. | .9     | Chip ID Byte 1 (Index=20h, Default=86h, MB PnP)                           | 18   |

|    | 6.6. | .10    | Chip ID Byte 2 (Index=21h, Default=61h, MB PnP)                           | 18   |

|    | 6.6. | .11    | Chip Version & Multi-Chips Clarification (Index=22h, Default=00h, MB PnP) | 18   |

|    | 6.6. | .12    | PnP Logical Device Enable Register (Index=23h, Default=00h, MB PnP)       | 19   |

|    | 6.6. | .13    | Software Suspend and Input Clock Select (Index=24h, Default=00h, MB PnP)  | 19   |

|    | 6.6. | .14    | GPIO Function Enable Registers[12:8] (Index=25h, Default=00h, MB PnP)     | 19   |

|    | 6.6. | .15    | GPIO Function Pin Enable Register[7:0] (Index=26h, Default=00h, MB PnP)   | 19   |

| 6  | 6.7  | FDC    | Configuration Registers (LDN=00h)                                         | 20   |

|    | 6.7. | .1     | FDC Activate (Index=30h, Default=00h, ISA PnP/MB PnP)                     | 20   |

|    | 6.7. | .2     | FDC I/O Range Check (Index=31h, Default=00h, ISA PnP)                     | 20   |

|    | 6.7. | .3     | FDC Base Address MSB Register (Index=60h, Default=03h, ISA PnP/MB PnP)    | 20   |

|    | 6.7. | .4     | FDC Base Address LSB Register (Index=61h, Default=F0h, ISA PnP/MB PnP)    | 20   |

|    | 6.7. | .5     | FDC Interrupt Level Select (Index=70h, Default=06h, ISA PnP/MB PnP)       | 20   |

|    | 6.7. | .6     | FDC Interrupt Type (Index=71h, Default=02h, ISA PnP)                      | 20   |

|    | 6.7. | .7     | FDC DMA Channel Select (Index=74h, Default=02h, ISA PnP/MB PnP)           | 20   |

|    | 6.7. | .8     | FDC Special Configuration Register (Index=F0h, Default=00h, MB PnP)       | 21   |

| 6.8  | Ser           | ial Port 1 Configuration Registers (LDN=01h)                                         | 21     |

|------|---------------|--------------------------------------------------------------------------------------|--------|

| 6    | .8.1          | Serial Port 1 Activate (Index=30h, Default=00h, ISA PnP/MB PnP)                      | 21     |

| 6    | .8.2          | Serial Port 1 I/O Range Check (Index=31h, Default=00h, ISA PnP)                      | 21     |

| 6    | .8.3          | Serial Port 1 Base Address MSB Register (Index=60h, Default=03h, ISA PnP/MB PnP)     | 21     |

| 6    | .8.4          | Serial Port 1 Base Address LSB Register (Index=61h, Default=F8h, ISA PnP/MB PnP)     | 21     |

| 6    | .8.5          | Serial Port 1 Interrupt Level Select (Index=70h, Default=04h, ISA PnP/MB PnP)        | 21     |

| 6    | .8.6          | Serial Port 1 Interrupt Type (Index=71h, Default=02h, ISA PnP)                       | 21     |

| 6    | .8.7          | Serial Port 1 Special Configuration Register (Index=F0h, Default=00h, MB PnP)        | 21     |

| 6.9  | Ser           | ial Port 2 Configuration Registers (LDN=02h)                                         | 22     |

| 6    | .9.1          | Serial Port 2 Activate (Index=30h, Default=00h, ISA PnP/MB PnP)                      | 22     |

| 6    | .9.2          | Serial Port 2 I/O Range Check (Index=31h, Default=00h, ISA PnP)                      | 22     |

| 6    | .9.3          | Serial Port 2 Base Address MSB Register (Index=60h, Default=02h, ISA PnP/MB PnP)     | 22     |

| 6    | .9.4          | Serial Port 2 Base Address LSB Register (Index=61h, Default=F8h, ISA PnP/MB PnP)     | 22     |

| 6    | .9.5          | Serial Port 2 Interrupt Level Select (Index=70h, Default=03h, ISA PnP/MB PnP)        | 22     |

| 6    | .9.6          | Serial Port 2 Interrupt Type (Index=71h, Default=02h, ISA PnP)                       | 22     |

| 6    | .9.7          | Serial Port 2 Special Configuration Register 1 (Index=F0h, Default=00h, MB PnP)      | 22     |

| 6.10 | ) Par         | allel Port Configuration Registers (LDN=03h)                                         | 23     |

| 6    | .10.1         | Parallel Port Activate (Index=30h, Default=00h, ISA PnP/MB PnP)                      | 23     |

| 6    | .10.2         | Parallel Port I/O Range Check (Index=31h, Default=00h, ISA PnP)                      | 23     |

| 6    | .10.3         | Parallel Port Base Address 1 MSB Register (Index=60h, Default=03h, ISA PnP/MB PnP)   | 23     |

| 6    | .10.4         | Parallel Port Base Address 1 LSB Register (Index=61h, Default=78h, ISA PnP/MB PnP)   | 23     |

| 6    | .10.5         | Parallel Port Base Address 2 MSB Register (Index=62h, Default=07h, ISA PnP/MB PnP)   | 23     |

| 6    | .10.6         | Parallel Port Base Address 2 LSB Register (Index=63h, Default=78h, ISA PnP/MB PnP)   | 23     |

| 6    | .10.7         | Parallel Port Interrupt Level Select (Index=70h, Default=07h, ISA PnP/MB PnP)        | 23     |

| 6    | .10.8         | Parallel Port Interrupt Type (Index=71h, Default=02h, ISA PnP)                       | 23     |

| 6    | .10.9         | Parallel Port DMA Channel Select (Index=74h, Default=03h, ISA PnP/MB PnP)            | 24     |

| 6    | .10.10        | Parallel Port Special Configuration Register (Index=F0h, Default=03h, MB PnP)        | 24     |

| 6.11 | 1 IR (        | Configuration Registers (LDN=04h)                                                    | 24     |

| 6    | .11.1         | IR Activate (Index=30h, Default=00h, ISA PnP/MB PnP)                                 | 24     |

| 6    | .11.2         | IR I/O Range Check (Index=31h, Default=00h, ISA PnP)                                 | 24     |

| 6    | .11.3         | IR Base Address 1 MSB Register (Index=60h, Default=02h, ISA PnP/MB PnP)              | 24     |

| 6    | .11.4         | IR Base Address 1 LSB Register (Index=61h, Default=E8h, ISA PnP/MB PnP)              | 24     |

|      | .11.5<br>nly) | IR Base Address 2 MSB Register (Index=62h, Default=03h, ISA PnP/MB PnP) (IT8661RF 24 |        |

| 6    | .11.6         | IR Base Address 2 LSB Register (Index=63h, Default=00h, ISA PnP/MB PnP) (IT8661RF o  | nly)25 |

| 6    | .11.7         | IR Interrupt Level Select 1 (Index=70h, Default=0Ah, ISA PnP/MB PnP)                 | 25     |

| 6    | .11.8         | IR Interrupt Type 1 (Index=71h, Default=02h, ISA PnP)                                | 25     |

| 6    | .11.9         | IR Interrupt Level Select 2 (Index=72h, Default=0Bh, ISA PnP/MB PnP) (IT8661RF only) | 25     |

| 6.11.10                 | IR Interrupt Type 2 (Index=73h, Default=02h, ISA PnP) (IT8661RF only)                              | 25 |

|-------------------------|----------------------------------------------------------------------------------------------------|----|

| 6.11.11                 | IR DMA Channel Select 1 (Index=74h, Default=01h, ISA PnP/MB PnP) (IT8661RF only).                  | 25 |

| 6.11.12                 | IR DMA Channel Select 2 (Index=75h, Default=00h, ISA PnP/MB PnP) (IT8661RF only).                  | 25 |

| 6.11.13                 | IR Special Configuration Register (Index=F0h, Default=00h, MB PnP)                                 | 26 |

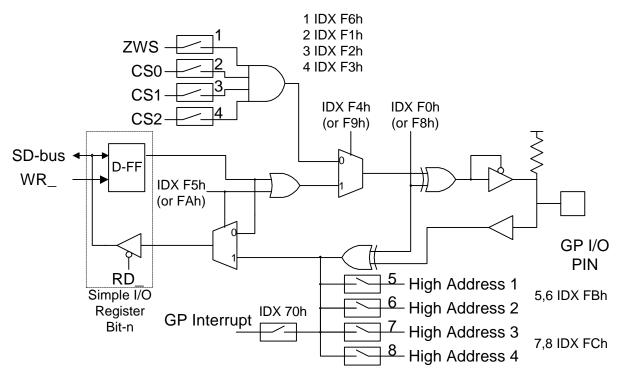

| 6.12 GP                 | IO & Alternate Function Configuration Registers (LDN=05h)                                          | 26 |

| 6.12.1                  | CS0 Base Address MSB Register (Index=60h, Default=00h, MB PnP)                                     | 26 |

| 6.12.2                  | CS0 Base Address LSB Register (Index=61h, Default=00h, MB PnP)                                     | 26 |

| 6.12.3                  | CS1 Base Address MSB Register (Index=62h, Default=00h, MB PnP)                                     | 26 |

| 6.12.4                  | CS1 Base Address LSB Register (Index=63h, Default=00h, MB PnP)                                     | 26 |

| 6.12.5                  | CS2 Base Address MSB Register (Index=64h, Default=00h, MB PnP)                                     | 26 |

| 6.12.6                  | CS2 Base Address LSB Register (Index=65h, Default=00h, MB PnP)                                     | 26 |

| 6.12.7                  | Simple I/O Base Address MSB Register (Index=66h, Default=00h, MB PnP)                              | 27 |

| 6.12.8                  | Simple I/O Base Address LSB Register (Index=67h, Default=00h, MB PnP)                              | 27 |

| 6.12.9                  | GPIO Interrupt Level Select (Index=70h, Default=00h, MB PnP)                                       | 27 |

| 6.12.10                 | GPIO[7:0] Pin Polarity Register (Index=F0h, Default=00h, MB PnP)                                   | 27 |

| 6.12.11                 | CS0/CS1/CS2 Control Register (Index=F1h/F2h/F3h, Default=00h, MB PnP)                              | 27 |

| 6.12.12                 | GPIO[7:0] Function Selection Register (Index=F4h, Default=00h, MB PnP)                             | 27 |

| 6.12.13                 | Simple I/O[7:0] Direction Selection Register (Index=F5h, Default=00h, MB PnP)                      | 27 |

| 6.12.14<br>Default=     | Zero Wait State Control & On-Chip High Address Qualification Enable Register (Index=F=00h, MB PnP) |    |

| 6.12.15                 | Device Zero Wait State Enable Register (Index=F7h, Default=00h, MB PnP)                            | 28 |

| 6.12.16                 | GPIO[12:8] Pin Polarity Register (Index=F8h, Default=00h, MB PnP)                                  | 28 |

| 6.12.17                 | GPIO[12:8] Function Selection Register (Index=F9h, Default=00h, MB PnP)                            | 28 |

| 6.12.18                 | Simple I/O[12:8] Direction Selection Register (Index=FAh, Default=00h, MB PnP)                     | 28 |

| 6.12.19<br>PnP)         | High Address Qualification Inputs 1 & 2 Selection Register (Index=FBh, Default = 00h, M            |    |

| 6.12.20<br>PnP)         | High Address Qualification Inputs 3 & 4 Selection Register (Index=FCh, Default = 00h, N            |    |

| 7. Functio              | nal Description                                                                                    | 30 |

| 7.1 Gei                 | neral Purpose I/O                                                                                  | 30 |

| 7.2 FD                  | C Register Description                                                                             | 32 |

| 7.2.1                   | Digital Output Register (DOR) - (Base Address + 02h)                                               | 32 |

| 7.2.2                   | Main Status Register (MSR) - (Base Address + 04h)                                                  | 32 |

| 7.2.3                   | Data Register (FIFO) - (Base Address + 05h)                                                        | 33 |

| 7.2.4                   | Digital Input Register (DIR) - (Base + 07h)                                                        | 33 |

| 7.2.5                   | Diskette Control Register (DCR) - (Base Address + 07h WRITE)                                       | 33 |

| 7.2.6                   | Status Register                                                                                    | 34 |

| 7.2.7                   | Reset                                                                                              | 36 |

| 7.2.8 Controller Phases |                                                                                                    | 36 |

| 7.2                                                                                                                                            | 2.9                                                                                                           | Data Transfer Commands Description                                                                                                                                                                                                                                                                                                   | . 36                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 7.3                                                                                                                                            | Seri                                                                                                          | al Channel Register Description                                                                                                                                                                                                                                                                                                      | . 49                                                                                         |

| 7.3                                                                                                                                            | 3.1                                                                                                           | Data Register                                                                                                                                                                                                                                                                                                                        | . 49                                                                                         |

| 7.3                                                                                                                                            | 3.2                                                                                                           | Control Registers: IER, IIR, FCR, DLL, DLM, LCR, MCR                                                                                                                                                                                                                                                                                 | . 49                                                                                         |

| 7.3                                                                                                                                            | 3.3                                                                                                           | Status Register LSR and MSR                                                                                                                                                                                                                                                                                                          | . 51                                                                                         |

| 7.3                                                                                                                                            | 3.4                                                                                                           | Reset                                                                                                                                                                                                                                                                                                                                | . 53                                                                                         |

| 7.3                                                                                                                                            | 3.5                                                                                                           | Programming                                                                                                                                                                                                                                                                                                                          | . 55                                                                                         |

| 7.3                                                                                                                                            | 3.6                                                                                                           | Software Reset                                                                                                                                                                                                                                                                                                                       | . 55                                                                                         |

| 7.3                                                                                                                                            | 3.7                                                                                                           | Clock Input Operation                                                                                                                                                                                                                                                                                                                | . 55                                                                                         |

| 7.3                                                                                                                                            | 8.8                                                                                                           | FIFO Interrupt Mode Operation                                                                                                                                                                                                                                                                                                        | . 55                                                                                         |

| 7.4                                                                                                                                            | Para                                                                                                          | allel Port                                                                                                                                                                                                                                                                                                                           | . 55                                                                                         |

| 7.4                                                                                                                                            | 4.1                                                                                                           | SPP and EPP Modes                                                                                                                                                                                                                                                                                                                    | . 55                                                                                         |

| 7.4                                                                                                                                            | 1.2                                                                                                           | EPP Mode Operation                                                                                                                                                                                                                                                                                                                   | . 56                                                                                         |

| 7.4                                                                                                                                            | 1.3                                                                                                           | ECP Mode Operation                                                                                                                                                                                                                                                                                                                   | . 57                                                                                         |

| 7.5                                                                                                                                            | FIR                                                                                                           | Controller                                                                                                                                                                                                                                                                                                                           | . 66                                                                                         |

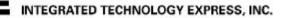

| 7.5                                                                                                                                            | 5.1                                                                                                           | FIR Transmit Operation                                                                                                                                                                                                                                                                                                               | .66                                                                                          |

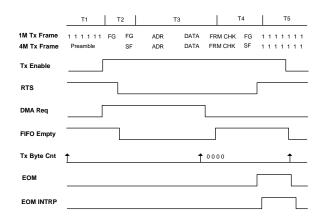

| 7.5                                                                                                                                            | 5.2                                                                                                           | FIR Receive Operation                                                                                                                                                                                                                                                                                                                | . 67                                                                                         |

| 7.5                                                                                                                                            | 5.3                                                                                                           | FIR Controller Registers Description                                                                                                                                                                                                                                                                                                 | . 69                                                                                         |

|                                                                                                                                                |                                                                                                               |                                                                                                                                                                                                                                                                                                                                      | 70                                                                                           |

| 8. DC                                                                                                                                          | C Elec                                                                                                        | trical Characteristics                                                                                                                                                                                                                                                                                                               | . 78                                                                                         |

|                                                                                                                                                |                                                                                                               | trical Characteristics<br>racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                                | Cha                                                                                                           |                                                                                                                                                                                                                                                                                                                                      | . 80                                                                                         |

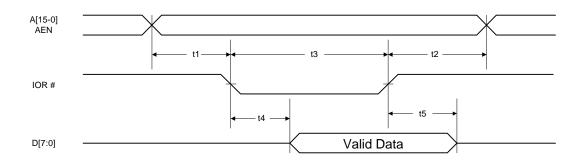

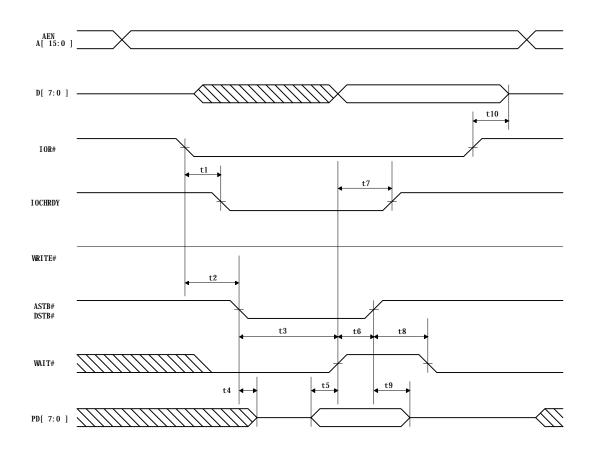

| 9. AC                                                                                                                                          | <b>Cha</b> i<br>REA                                                                                           | racteristics ( VCC = 5.0V $\pm$ 5%, Ta = 0°C to + 70°C)                                                                                                                                                                                                                                                                              | <b>80</b><br>80                                                                              |

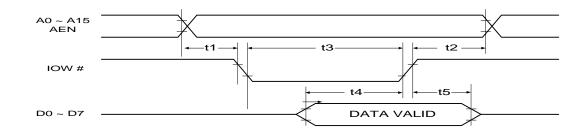

| <b>9. AC</b><br>9.1                                                                                                                            | <b>Cha</b><br>REA<br>WR                                                                                       | racteristics(VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)                                                                                                                                                                                                                                                                                    | <b>80</b><br>80<br>80                                                                        |

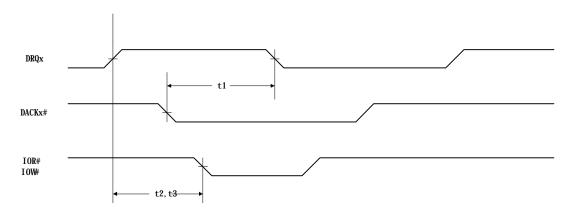

| <b>9. AC</b><br>9.1<br>9.2                                                                                                                     | <b>Cha</b><br>REA<br>WR<br>FDC                                                                                | racteristics(VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing                                                                                                                                                                                                                                             | <b>80</b><br>80<br>80<br>81                                                                  |

| 9. AC<br>9.1<br>9.2<br>9.3                                                                                                                     | Chai<br>REA<br>WR<br>FDC<br>3.1                                                                               | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing                                                                                                                                                                                                                               | <b>80</b><br>80<br>80<br>81<br>81                                                            |

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3                                                                                                              | <b>Cha</b><br>REA<br>WR<br>FDC<br>3.1<br>3.2                                                                  | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing<br>DMA Operation Timing                                                                                                                                                                                                       | 80<br>80<br>81<br>81<br>81                                                                   |

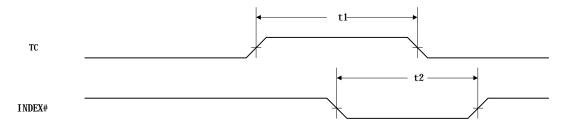

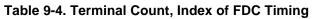

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3                                                                                                       | Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3                                                                 | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing<br>DMA Operation Timing<br>Terminal Count, Index                                                                                                                                                                              | 80<br>80<br>81<br>81<br>81<br>81                                                             |

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3                                                                                                | C Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4                                                        | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing.                                                                                                                                          | 80<br>80<br>81<br>81<br>81<br>81<br>82<br>82                                                 |

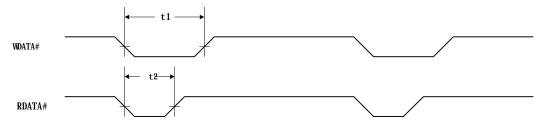

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.3                                                                                         | C Chai<br>RE4<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri                                                | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing<br>SEEK Operation Timing.                                                                                                                 | 80<br>80<br>81<br>81<br>81<br>82<br>82<br>83                                                 |

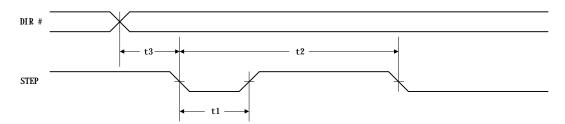

| <ul> <li>9. AC</li> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.3</li> <li>9.3</li> <li>9.3</li> <li>9.3</li> <li>9.3</li> <li>9.4</li> </ul> | Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1                                           | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing<br>SEEK Operation Timing<br>al Port Timing                                                                                                | 80<br>80<br>81<br>81<br>81<br>82<br>82<br>83<br>83                                           |

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.4<br>9.4                                                                                  | C Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1                                         | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>C Timing<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing<br>SEEK Operation Timing<br>al Port Timing<br>Transmitter                                                                                 | 80<br>80<br>81<br>81<br>82<br>82<br>82<br>83<br>83<br>84                                     |

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.3<br>9.4<br>9.4<br>9.4                                                                    | C Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1<br>4.2<br>4.3                           | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing.<br>ITE Cycle Timing.<br>C Timing.<br>DMA Operation Timing.<br>Terminal Count, Index .<br>FDD WRITE/READ Operation Timing.<br>SEEK Operation Timing.<br>al Port Timing.<br>Transmitter.<br>Modem                                                              | 80<br>80<br>81<br>81<br>82<br>82<br>82<br>83<br>83<br>83<br>84<br>85                         |

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.4<br>9.4<br>9.4<br>9.4                                                                    | Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1<br>4.2<br>4.3                             | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing.<br>ITE Cycle Timing.<br>C Timing.<br>DMA Operation Timing.<br>Terminal Count, Index.<br>FDD WRITE/READ Operation Timing.<br>SEEK Operation Timing.<br>al Port Timing.<br>Transmitter<br>Modem<br>Receiver                                                    | 80<br>80<br>81<br>81<br>81<br>82<br>83<br>83<br>83<br>83<br>84<br>85<br>85                   |

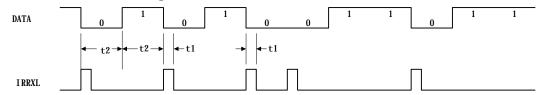

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.4<br>9.4<br>9.4<br>9.4<br>9.4                                                             | Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1<br>4.2<br>4.3<br>4.4                      | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing.<br>ITE Cycle Timing.<br>C Timing.<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing.<br>SEEK Operation Timing.<br>al Port Timing.<br>Transmitter<br>Modem<br>Receiver                                                      | 80<br>80<br>81<br>81<br>81<br>82<br>82<br>83<br>83<br>83<br>84<br>85<br>85<br>86             |

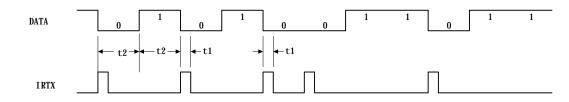

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.4<br>9.4<br>9.4<br>9.4<br>9.4<br>9.4                                                      | Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6        | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>DMA Operation Timing<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing<br>SEEK Operation Timing<br>al Port Timing<br>Transmitter<br>Modem<br>Receiver<br>IrDA Receive Timing<br>IrDA Transmit Timing | 80<br>80<br>81<br>81<br>82<br>82<br>82<br>83<br>83<br>83<br>84<br>85<br>86<br>86             |

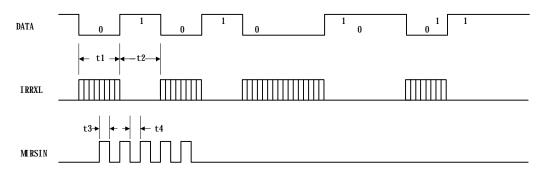

| 9. AC<br>9.1<br>9.2<br>9.3<br>9.3<br>9.3<br>9.3<br>9.3<br>9.4<br>9.4<br>9.4<br>9.4<br>9.4<br>9.4<br>9.4                                        | Chai<br>REA<br>WR<br>FDC<br>3.1<br>3.2<br>3.3<br>3.4<br>Seri<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | racteristics ( VCC = 5.0V ± 5%, Ta = 0°C to + 70°C)<br>AD Cycle Timing<br>ITE Cycle Timing<br>DMA Operation Timing<br>Terminal Count, Index<br>FDD WRITE/READ Operation Timing<br>SEEK Operation Timing<br>al Port Timing<br>Transmitter<br>Modem<br>Receiver<br>IrDA Receive Timing<br>ASKIR Receive Timing                         | 80<br>80<br>81<br>81<br>81<br>82<br>83<br>83<br>83<br>83<br>85<br>85<br>85<br>86<br>86<br>87 |

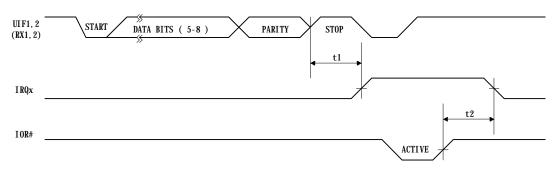

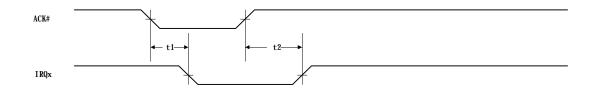

| 9.5    | 5.2 Interrupt Request Timing              | 88 |

|--------|-------------------------------------------|----|

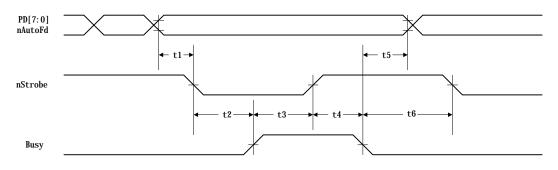

| 9.6    | EPP Address or DATA WRITE Cycle           | 89 |

| 9.7    | EPP Address or DATA READ Cycle            | 90 |

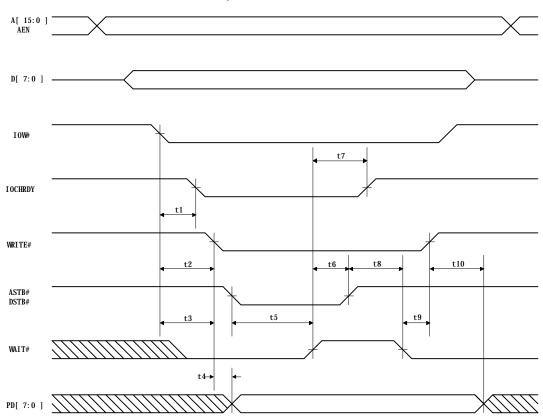

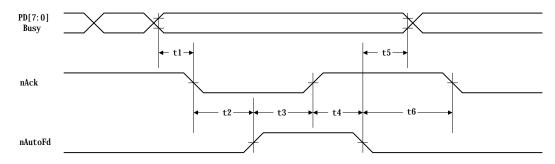

| 9.8    | ECP Parallel Port Forward Timing Diagram  | 91 |

| 9.9    | ECP Parallel Port Backward Timing Diagram | 92 |

| 10. Pa | ckage Information                         | 93 |

| 11. Or | dering Information                        | 94 |

### TABLES

|                                                                         | Page |

|-------------------------------------------------------------------------|------|

| Table 5-1. Signal Names (by pin numbers in alphabetical order)          | 5    |

| Table 5-2. Signal Names (by pin numbers in alphabetical order) [cont'd] | 6    |

| Table 5-3. Signal Names (by pin numbers in alphabetical order) [cont'd] | 7    |

| Table 5-4. Signal Names (by pin numbers in alphabetical order) [cont'd] | 8    |

| Table 6-1. Global Configuration Registers                               | 13   |

| Table 6-2. FDC Configuration Registers                                  | 14   |

| Table 6-3. Serial Port 1 Configuration Registers                        | 14   |

| Table 6-4. Serial Port 2 Configuration Registers                        | 14   |

| Table 6-5. Parallel Port Configuration Registers                        | 15   |

| Table 6-6. IR Configuration Registers                                   | 15   |

| Table 6-7. GPIO & Alternate Function Configuration Registers            | 16   |

| Table 6-8. Base Address of Logical Devices                              | 17   |

| Table 7-1. Digital Output Register (DOR)                                | 32   |

| Table 7-2. Main Status Register (MSR)                                   | 32   |

| Table 7-3. Digital Input Register (DIR)                                 | 33   |

| Table 7-4. Diskette Control Register (DCR)                              | 33   |

| Table 7-5. Status Register 0                                            | 34   |

| Table 7-6. Status Register 1                                            | 34   |

| Table 7-7. Status Register 2                                            | 35   |

| Table 7-8. Status Register 3                                            | 35   |

| Table 7-9. Command Symbol Description                                   | 37   |

| Table 7-10. Effects of MT and N Bits                                    | 39   |

| Table 7-11. Description of the READ DATA Command                        | 39   |

| Table 7-12. Description of the READ DELETED DATA Command                | 40   |

| Table 7-13. Description of the READ A TRACK Command                     | 41   |

| Table 7-14. Description of the WRITE DATA Command                       | 42   |

| Table 7-15. Description of the WRITE DELETED DATA Command                  | 43 |

|----------------------------------------------------------------------------|----|

| Table 7-16. Description of the FORMAT A TRACK Command                      | 44 |

| Table 7-17. Description of the READ ID Command                             | 45 |

| Table 7-18. Description of the RE-CALIBRATE Command                        | 45 |

| Table 7-19. Description of the SEEK Command                                | 46 |

| Table 7-20. Interrupt Identification of the SENSE INTERRUPT STATUS Command | 47 |

| Table 7-21. Description of the SENSE INTERRUPT STATUS Command              | 47 |

| Table 7-22. Description of the SENSE DRIVE STATUS Command                  | 47 |

| Table 7-23. Description of the SPECIFY Command                             | 48 |

| Table 7-24. Description of the INVALID Command                             | 48 |

| Table 7-25. Serial Channel Registers                                       | 49 |

| Table 7-26. Interrupt Identification Register                              | 50 |

| Table 7-27. Baud Rates Using (24MHz ÷ 13) Clock                            | 51 |

| Table 7-28. Modem Control Register Bits                                    | 51 |

| Table 7-29. Line Status Register Bits                                      | 52 |

| Table 7-30. Modem Status Register Bits                                     | 53 |

| Table 7-31. Reset Control of Registers and Pinout Signals                  | 53 |

| Table 7-32. Parallel Port Connector in Different Modes                     | 55 |

| Table 7-33. Address Map and Bit Map for SPP and EPP Modes                  | 55 |

| Table 7-34. Bit Map of the ECP Registers                                   | 58 |

| Table 7-35. ECP Register Definitions                                       | 58 |

| Table 7-36. ECP Mode Descriptions                                          | 59 |

| Table 7-37. ECP Pin Descriptions                                           | 59 |

| Table 7-38. Extended Control Register (ECR) Mode and Description           | 61 |

| Table 7-39. FIR Controller Registers Summary                               | 69 |

| Table 9-1. READ Cycle Timing                                               | 80 |

| Table 9-2. WRITE Cycle Timing                                              | 80 |

| Table 9-3. DMA Operation Timing of FDC Timing                              | 81 |

| Table 9-4. Terminal Count, Index of FDC Timing                             | 81 |

| Table 9-5. FDD WRITE/READ Operation Timing of FDC Timing                   | 82 |

| Table 9-6. SEEK Operation Timing of FDC Timing                             | 82 |

| Table 9-7. Transmitter of Serial Port Timing                               | 83 |

| Table 9-8. Modem of Serial Port Timing                                     | 84 |

| Table 9-9. Receiver of Serial Port Timing                                  | 85 |

| Table 9-10. IrDA Receive Timing of Serial Port Timing                      | 85 |

| Table 9-11. IrDA Transmit Timing of Serial Port Timing                     | 86 |

| Table 9-12. ASKIR Receive Timing of Serial Port Timing                     | 87 |

| Table 9-13. ASKIR Transmit Timing of Serial Port Timing                    | 87 |

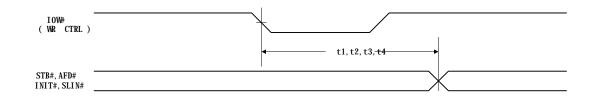

| Table 9-14. Control Signal Delay Time of Parallel Port Timing | 88 |

|---------------------------------------------------------------|----|

| Table 9-15. Interrupt Request Timing of Parallel Port Timing  | 88 |

| Table 9-16. EPP Address or DATA WRITE Cycle                   | 89 |

| Table 9-17. EPP Address or DATA READ Cycle                    | 91 |

| Table 9-18. ECP Parallel Port Forward Timing                  | 92 |

| Table 9-19. ECP Parallel Port Backward Timing                 | 92 |

## **FIGURES**

| Figure 6-1. Configuration Sequence Flow Chart        | 9  |

|------------------------------------------------------|----|

| Figure 6-2. PnP State Transition                     | 11 |

| Figure 7-1. General Logic of GPIO Function           | 31 |

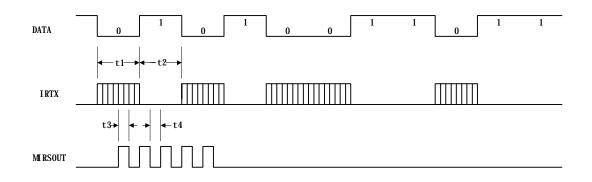

| Figure 7-2. Time Waveform for FIR Transmit Operation | 66 |

| Figure 7-3. Time Waveform for FIR Receive Operation  | 67 |

Preliminary V0.6

Specifications are subject to Change without Notice

### 1. Features

- PC97/98 Compliant Hardware (PC99 Ready)

- Unique PnP device ID for each logical device compliant with Plug and Play specification V1.0a

- Built-in resource data ROM

- Five (5) logical devices

- 16-bit address decoding

- Seven (7) selectable IRQs

- Four (4) selectable DMA channels

- Flexible resource configure and dynamic disable

- IRQ sharing supported 2.88MB floppy disk controller

- -Base address 0x0100h-0x0FF8h, seven IRQ and four DMA options

- -48mA direct output driver

- Enhanced digital data separator

- A and B drives can be logically swapped via registers

- -3-mode drives supported

- Supports automatic write protection via software

- Supports two (2) 360K/ 720K/ 1.2M/ 1.44M/2.88M floppy disk drives

- Multi-mode High Performance Parallel Port

- -Base address 0x0100h-0x0FFCh, seven IRQ and four DMA options

- Standard mode -- bi-directional SPP

- Enhanced mode EPP V1.7 and EPP V1.9 compliant

- High Speed mode -- ECP, IEEE1284 compliant

- Backdrive current protection

- Printer power-on damage protection

## IT8661F and IT8661RF

### Plug and Play Super AT I/O

ITPA-PN-97014, W.B., Apr. 18, 1998

### Serial Ports

- -Base address 0x100h-0x0FF8h, seven (7) IRQ options

- Supports two 16C550 standard compatible enhanced serial ports

- Supports send/receive 16-byte FIFOs

- -MIDI standard compatible

- Infrared Communication Controller

- -Base address 0x0100h-0x0FF8h, seven(7) IRQ and four (4) DMA options

- -Supports HPSIR or ASKIR infrared interface

- -Only IT8661RF supports MIR or FIR

- Dedicated 16C550 standard UART supporting infrared communication

- Single or dual DMA channel mode for FIR (RF version only)

- -Back-to-back packet transmission and reception for FIR (RF version only)

- Supports 2-input FIR transceiver or 1-input FIR transceiver interface (RF version only)

- Provides thirteen (13) General Purpose I/O pins

- Only one (1) 24MHz or 48MHz crystal needed

- 5-volt operation

- 100-pin QFP package

### 2. General Description

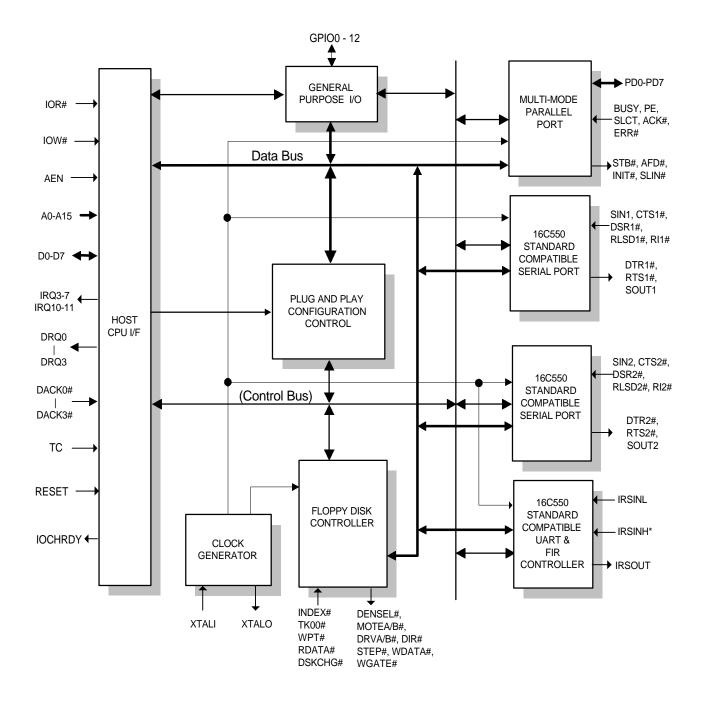

The IT8661F and IT8661RF Plug and Play Super AT I/O chip are user-friendly, low cost peripheral controllers. They provide an ideal solution for Microsoft PC97/98 (PC99 ready) system requirements. A programmable IRQ sharing function is supported to comply with Microsoft PC97/98 (PC99 ready) requirements. No N.V. memory is needed to store resource data for Plug and Play system applications.

The IT8661F and IT8661RF consist of five (5) logical devices. One (1) high performance 2.88MB floppy disk controller, with digital data separator, supports two (2) 360K/ 720K/ 1.2M/ 1.44M/ 2.88M floppy disk drives. One multimode high performance Parallel Port features the bi-directional Standard Parallel Port (SPP), the Enhanced Parallel Port (EPP. V1.7 and v1.9 are supported), and IEEE 1284 compliant Extended Capabilities Port (ECP). Two (2) 16C550 standard compatible enhanced UARTs perform asynchronous communication for serial ports. One (1) highly integrated infrared communication controller is capable of supporting HPSIR, MIR, FIR or ASKIR with a built-in dedicated 16C550 standard compatible UART (MIR and FIR are available only on the RF version).

These five (5) logical devices can be individually enabled or disabled via software configuration registers. The IT8661F and IT8661RF utilize power saving circuitry to reduce power consumption. Once a logical device is disabled, its related inputs are gate inhibited, outputs are tristated, and input clock is disabled. The Parallel Port includes a specifically designed circuit to reduce damage or backdrive current when a printer or another parallel port device is powered-on. In effect, the IT8661F and IT8661RF are highperformance, low-power consumption I/O device.

### 3. Pin Configuration

\* Note: IRSINH is available for IT8661RF only.

### 4. Block Diagram

\* Note: IRSINH is available for IT8661RF only.

### 5. IT8661F and IT8661RF Pin Descriptions

| Pin No.          | Symbol        | I/O           | Description                                                                                                                                                                                                                                     |

|------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | DENSEL#       | O48           | DENSEL# is high for high data rate (500 Kbps/1 Mbps)<br>DENSEL# is low for low data rate (250/300 Kbps)                                                                                                                                         |

| 2                | MOTEA#        | O48           | FDD Motor A Enable, active low                                                                                                                                                                                                                  |

| 3                | DRVB#         | O48           | FDD Drive B Enable, active low                                                                                                                                                                                                                  |

| 4                | DRVA#         | O48           | FDD Drive A Enable, active low                                                                                                                                                                                                                  |

| 5                | MOTEB#        | O48           | FDD Motor Enable, active low                                                                                                                                                                                                                    |

| 7                | DIR#          | O48           | FDC Head Direction. Step in when low, step out when high during a SEEK operation.                                                                                                                                                               |

| 8                | STEP#         | O48           | FDC Step Pulse Output to the drive during a SEEK operation, active low.                                                                                                                                                                         |

| 9                | WDATA#        | O48           | FDC Write Serial Data to the drive, active low                                                                                                                                                                                                  |

| 10               | WGATE#        | O48           | FDC Write Enable Identify, active low                                                                                                                                                                                                           |

| 11               | SIDE1#        | O48           | Floppy Disk Side 1 Select, active low                                                                                                                                                                                                           |

| 12               | INDEX#        | IS            | FDC Index, active low. Indicates the beginning of a disk track.                                                                                                                                                                                 |

| 13               | TK00#         | IS            | Floppy Disk Track 0, active low. Indicates that the head of the selected drive is on track zero (0).                                                                                                                                            |

| 14               | WPT#          | IS            | FDD Write Protect, active low. Indicates that the disk of the selected drive is write-protected.                                                                                                                                                |

| 16               | RDATA#        | IS            | Read Disk Data, active low, serial data input from the FDD                                                                                                                                                                                      |

| 17               | DSKCHG#       | IS            | Floppy Disk Change, active low. This is an input pin that senses whether the drive door has been opened or a diskette has been changed.                                                                                                         |

| 18               | XTALO         | OCLK          | 24 MHz or 48 MHz Crystal Oscillator Output. If an external clock is used, this pin is left disconnected.                                                                                                                                        |

| 19               | IRSOUT/GPIO10 | I/O24         | Infrared data output of SIR or FIR. The second function is General Purpose I/O.                                                                                                                                                                 |

| 20               | XTALI         | ICLK          | 24 MHz or 48 MHz Crystal Oscillator Input. An external clock in use must be connected to this pin.                                                                                                                                              |

| 23, 21<br>52, 99 | DRQ0 - 3      | OP12          | DMA Request 0, 1, 2, 3. The logical devices of the IT8661F and IT8661RF can be mapped to individual DRQx via configuration register(0x74). These signals are cleared by the going-low of DACK 0, 1, 2, and 3# signals.                          |

| 22, 58<br>36, 96 | DACK0 - 3#    | IS            | DMA Acknowledge 0, 1, 2, 3. The logical devices of the IT8661F and IT8661RF can be mapped to individual DACKx.                                                                                                                                  |

| 25               | IRQ10/GPIO11  | OD24<br>I/O24 | Interrupt Request 10. The logical devices of the IT8661F and IT8661RF can be mapped to the individual IRQx via configuration register (0x70). The second function is General Purpose I/O. This pin is internally pulled up to $50$ K $\Omega$ . |

### Table 5-2. Signal Names (by pin numbers in alphabetical order) [cont'd]

| Pin No.                    | Symbol       | I/O           | Description                                                                                                                                                                                                                                     |  |  |

|----------------------------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 26                         | IRQ11/GPIO12 | OD24<br>I/O24 | Interrupt Request 11. The logical devices of the IT8661F and IT8661RF can be mapped to the individual IRQx via configuration register (0x70). The second function is General Purpose I/O. This pin is internally pulled up to $50$ K $\Omega$ . |  |  |

| 97, 27,<br>41-43,<br>28-34 | A0 - A11     | IS            | 12-bit I/O Address bus                                                                                                                                                                                                                          |  |  |

| 35                         | тс           | IS            | Terminal Count, active high to indicate that data transfer is completed                                                                                                                                                                         |  |  |

| 40, 39<br>37, 38<br>24     | IRQ3 - 7     | OD24          | Interrupt Request 3, 4, 5, 6, 7. The logical devices of the IT8661F and IT8661RF can be mapped to the individual IRQx via configuration register(0x70).                                                                                         |  |  |

| 44                         | IOR#         | IS            | Read Strobe, active low                                                                                                                                                                                                                         |  |  |

| 45                         | IOW#         | IS            | Write Strobe, active low                                                                                                                                                                                                                        |  |  |

| 46                         | AEN          | IS            | Address Enable, active high to indicate that the system is in DMA transfermode                                                                                                                                                                  |  |  |

| 53-56<br>48-51             | D0 - D7      | I/O24         | 8-bit bi-directional data bus                                                                                                                                                                                                                   |  |  |

| 57                         | RESET        | IS            | SYSTEM RESET, active high. At the falling edge of RESET, the voltage level of MC0 (pin 83) and MC1 (pin 81) are latched.                                                                                                                        |  |  |

| 59                         | SLCT         | IS            | Printer Select. This signal goes high when the line printer has been selected.                                                                                                                                                                  |  |  |

| 60                         | PE           | IS            | Printer Paper End. This signal is set high by the printer when it runs out of paper.                                                                                                                                                            |  |  |

| 61                         | BUSY         | IS            | Printer Busy. This signal goes high when the line printer has a local operation in progress and cannot accept data.                                                                                                                             |  |  |

| 62                         | ACK#         | IS            | Printer Acknowledge. This signal goes low to indicate that the printer has already received a character and is ready to accept another.                                                                                                         |  |  |

| 68-71<br>63-66             | PD7 - PD0    | I/O24         | Parallel Port Data Bus. This bus provides a byte-wide input or output to the system. The eight (8) lines are held in high-impedance state when the port is deselected.                                                                          |  |  |

| 73                         | INIT#        | O24           | Printer Initialize. Active low, this signal is derived from bit 2 of the printer control register, and is used to initialize printer.                                                                                                           |  |  |

### Table 5-3. Signal Names (by pin numbers in alphabetical order) [cont'd]

| Pin No. | Symbol               | I/O   | Description                                                                                                                                                                                                                                                                                                                          |  |  |  |

|---------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 75      | ERR#                 | IS    | Printer Error. Active low to indicate that the printer has encountered an error. The error message can be read from bit 3 of the printer status register.                                                                                                                                                                            |  |  |  |

| 76      | STB#                 | O24   | Printer Strobe. Active low, this signal is derived from the complement of bit<br>0 of the printer control register. It is used to strobe printer data into the<br>printer.                                                                                                                                                           |  |  |  |

| 77      | AFD#                 | O24   | Printer Autofeed. Active low, this signal is derived from the complement of bit 1 of the printer control register. It is used to inform the printer to advance one line after previous lines are printed.                                                                                                                            |  |  |  |

| 78      | SIN1                 | IS    | Serial Port 1, Data Input.                                                                                                                                                                                                                                                                                                           |  |  |  |

| 79      | SOUT1                | 012   | Serial Port 1, Data Output.                                                                                                                                                                                                                                                                                                          |  |  |  |

| 80      | DSR1#                | IS    | Serial Port 1, Data Set Ready, active low.                                                                                                                                                                                                                                                                                           |  |  |  |

| 81      | RTS1#/MC1            | O12/I | Serial Port 1, Request to Send Output, active low. During the hardware reset, this pin and pin 83 become input and DTR1# is tristated, then latches the voltage level of MC1 to clarify systems that use the same IT8661F and IT8661RF I/O controller. (Refer to the general description of the configuring sequence on Page9.)      |  |  |  |

| 82      | CTS1#                | O12/I | Serial Port 1, Clear to Send Input, active low.                                                                                                                                                                                                                                                                                      |  |  |  |

| 83      | DTR1#/MC0            | O12/I | Serial Port 1, Data Terminal Ready Output, active low. During the hardware reset, this pin and pin 81 become input and DTR1# is tristated, then latches the voltage level of MC0 to clarify systems that use the same IT8661F and IT8661RF I/O controller. (Refer to the general description of the configuring sequence on Page 9.) |  |  |  |

| 84      | RI1#                 | IS    | Serial Port 1, Ring Indicator, active low.                                                                                                                                                                                                                                                                                           |  |  |  |

| 85      | RLSD1#               | IS    | Serial Port 1, Receive Line Signal Detect, active low.                                                                                                                                                                                                                                                                               |  |  |  |

| 86      | R12#/A15/GPIO0       | I/O12 | Serial Port 2, Ring Indicator, active low. The second function is I/O Address 15. The third function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ .                                                                                                                                                       |  |  |  |

| 87      | RLSD2#/A14/<br>GPIO1 | I/O12 | Serial Port 2, Receive Line Signal Detect, active low. The second function is I/O Address 14. The third function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ .                                                                                                                                           |  |  |  |

| 88      | SIN2/GPIO2           | I/O12 | Serial Port 2, Data Input. The second function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ .                                                                                                                                                                                                             |  |  |  |

| 89      | SOUT2/GPIO3          | I/O12 | Serial Port 2, Data Output. The second function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ .                                                                                                                                                                                                            |  |  |  |

| 90      | DSR2#/A13/<br>GPIO4  | I/O12 | Serial Port 2, Data Set Ready, active low. The second function is I/O Address 13. The third function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ .                                                                                                                                                       |  |  |  |

### IT8661F and IT8661RF

### Table 5-4. Signal Names (by pin numbers in alphabetical order) [cont'd]

| Pin No.         | Symbol          | I/O   | Description                                                                                                                                                                                                                                                                                                                   |  |

|-----------------|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 92              | CTS2#/A12/GPIO6 | I/O12 | Serial Port 2. Clear to Send Input, active low. The second function is I/O Address 12. The third function is General Purpose I/O.                                                                                                                                                                                             |  |

| 93              | DTR2#GPIO7      | I/O12 | Serial Port 2, Data Terminal Ready Output, active low. The second function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ .                                                                                                                                                                          |  |

| 94              | IRSINL/GPIO8    | I/O12 | The first function is one of the following: (1) Infrared data input pin or (2) Low frequency infrared data input pin of 2-input FIR transceiver (HP-like) or (3) Infrared data input pin of 1-input FIR transceiver (IBM-like). The second function is General Purpose I/O. This pin is internally pulled up to $50K\Omega$ . |  |

| 98              | IRSINH*/GPIO9   | OD12  | The IT8661F is a high-frequency infrared data input pin of 2-input FIR transceiver(HP-like) or mode select output pin of 1-input FIR transceiver (IBM-like). The second function for both IT8661F and IT8661RF is General Purpose I/O. This pin is internally pulled up $50K\Omega$ .                                         |  |

| 100             | IOCHRDY         | OD24  | EPP mode, pulled low to extend the READ/WRITE command                                                                                                                                                                                                                                                                         |  |

| 15, 72          | VCC             |       | +5V power pin                                                                                                                                                                                                                                                                                                                 |  |

| 6, 47<br>67, 95 | GND             |       | Ground                                                                                                                                                                                                                                                                                                                        |  |

\* Note: IRSINH is available for IT8661RF only.

### 6. Configuring Sequence Description

### 6.1 General Description

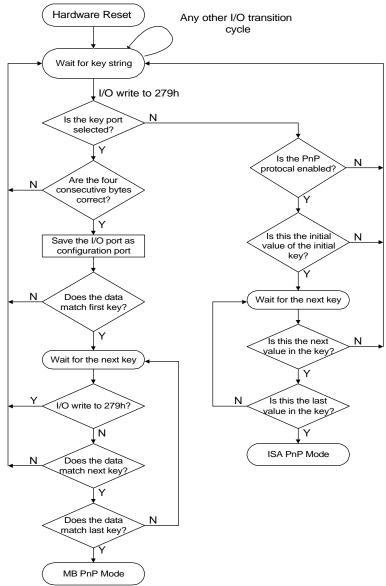

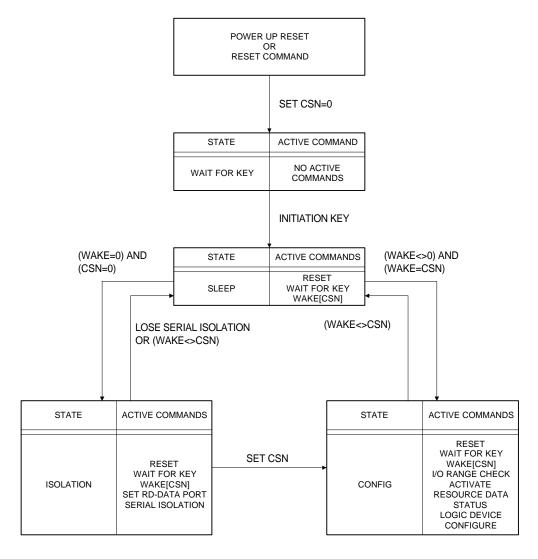

After hardware reset or power-on reset, the IT8661F and IT8661RF enter the normal mode with all logical devices disabled. There are two configuration modes for IT8661F and IT8661RF, MB PnP mode and ISA PnP mode.

The MC0 (pin 83) and MC1 (pin 81) are used to clarify different systems that use the same IT8661F and IT8661RF I/O controller. In ISA PnP mode, the latched values of MC0 and MC1 can be used as the serial number LSB of to clarify different systems that use the same IT8661F and IT8661RF I/O controller. In MB PnP mode, if bits 5 and 4 of global configuration register index 22h are written and the values of bits 5 and 4 equal the corresponding latch-reversed values of MC1 and MC0, then the MB PnP configuration mode can be entered. This can clarify different systems that use the same IT8661F and IT8661F

Figure 6-1. Configuration Sequence Flow Chart

### 6.2 MB PnP Mode

There are three (3) steps to complete the configuration setup: (1) Enter the MB PnP mode; (2) Modify the data of configuration registers; (3) Exit the MB PnP mode. Unless normal exiting is done, the configuration setup may cause undesired results.

(1) Enter the MB PnP Mode

To enter the MB PnP mode, 36 special I/O write operations are to be performed during the Wait for Key state. To ensure the initial state of the key-check logic, it is first necessary to perform two write operations to Address port (279h) of the ISA PnP.

The Entering Key includes two (2) steps. The first FOUR (4) bytes are used to determine the I/O address and data port of configuration register. If the other 32 bytes are not written properly and sequentially, it will cause a failure in the MB PnP mode while performing any IOR/IOW command to other I/O ports. To avoid this situation, we suggest that programmers disable interrupts while performing the 36 write operations. The corresponding sequential data for the first four (4) bytes are:

|  | I/O Address | port | Data | port |  |

|--|-------------|------|------|------|--|

|--|-------------|------|------|------|--|

|                        | -     | -    |

|------------------------|-------|------|

| 86h, 61h, 55h, 55h;    | 3F0h; | 3F1h |

| or 86h, 61h, 55h, AAh; | 3BDh; | 3BFh |