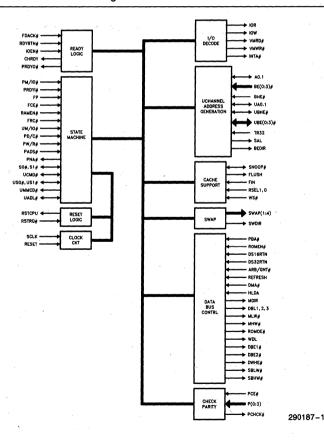

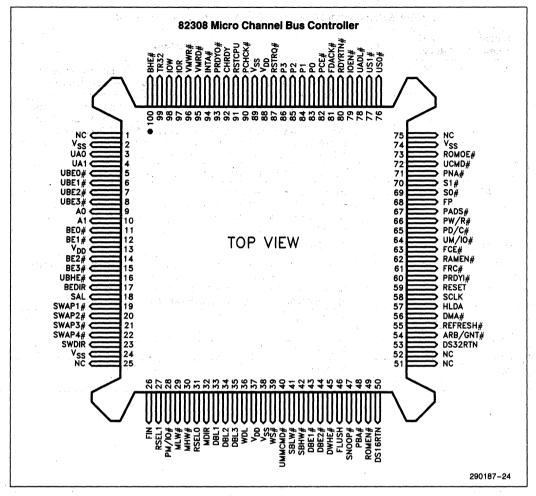

# 82308 Micro Channel BUS CONTROLLER

- Micro Channel Compatible Bus Control

- Supports 8-, 16- or 32-Bit Data Transfers on the Micro Channel

- Optional Hardward Enforced I/O **Recovery Mechanism**

- Cache Controller (82385) Interface to Maximize Performance for 80386 Based **Systems**

- Low Power CHMOS Technology

- 100-Pin Plastic Quad Flat Pack Packaging

(See Packaging Spec., Order # 231369)

The 82308 Micro Channel Bus Controller is the complementary device to the 82309 Address Bus Controller. It is designed to facilitate data transfers between the Microprocessor, DMA, Memory and Micro Channel bus. It generates the appropriate data conversion and alignment control signals to implement an external byte swap mechanism for transferring data of equal and different widths.

The 82308 Bus Controller generates all control signals necessary to run Micro Channel Memory and I/O Bus cycles for both 80386 and 80386SX processors.

To implement the highest performance 80386 based system with the 82385 cache controller, the Bus Controller features special cache hardware interface signals.

October 1988

## STATE MACHINE

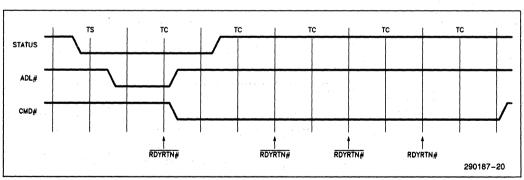

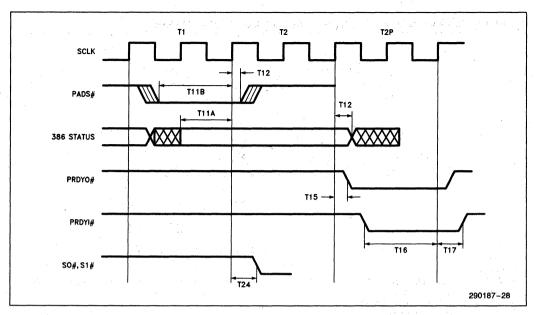

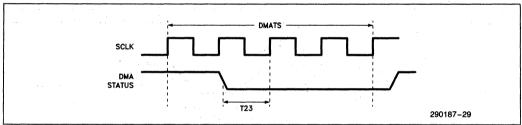

The primary purpose of the state machine is to generate the Micro Channel signals for processor and DMA cycles. These Micro Channel signals are: S0#, S1#, ADL#, MMCCMD# and CMD#. The state machine also generates the PNA# signal required by the 386 CPU and generates the DMA S0# and S1# based on the 386 processor status.

## **DATA TRANSFER**

The 82308 Bus Controller directs the transfer of data between the 32-bit 80386 bus and 32-bit, 16-bit or 8-bit devices on the Micro Channel. For 16-bit transfers initiated by the 80386SX or DMA, the Bus Controller provides the control signals to facilitate transfers to 16-bit or 8-bit devices on the Micro Channel data bus and vice versa.

In addition to providing the transceiver direction, latch, and enable signals, the Bus Controller manipulates Address signals for the DMA and Micro Channel. For example, a 32-bit access to an 8-bit device is broken into four cycles, and the BC automatically sequences A1 and A0 in each cycle.

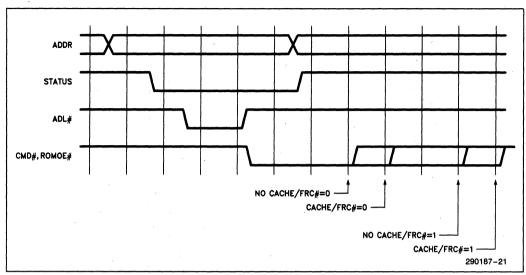

The 82308 Bus Controller also supports the ROM BIOS by providing the output enable for the BIOS based on the decoded BIOS address signal from the Address Bus Controller (ROMEN#).

#### RESET DETECT

The reset detect logic generates a synchronous CPU reset signal based on any of the following events:

- An active low-pulse on the RC# input to the Bus Controller

- Processor Shutdown Condition based on the Processors' status signals

- Power-up condition as determined by the RESET input.

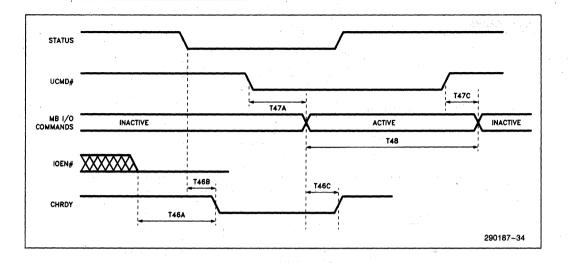

#### I/O SUPPORT

The 82308 Bus Controller generates Memory and I/O Read and Write signals for devices on the motherboard. It also generates the Interrupt Acknowledge signal.

The Bus Controller extends motherboard device accesses by de-asserting CHRDY until a read or write strobe is generated. This gives the peripheral device an opportunity to extend the cycle even further if required by driving its own CHRDY inactive after it detects the read or write strobe. The motherboard device decode is performed by the 82309 Address Bus Controller.

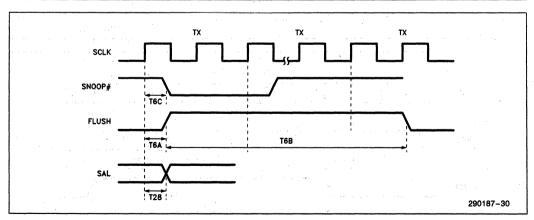

## **CACHE SUPPORT**

The 82308 Bus Controller supports 82385 Cache Controller interface signals to allow maximum system performance in cache based 386 systems.

## **CACHE FLUSH**

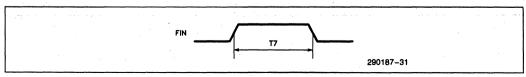

The Bus Controller generates a synchronous flush output signal (FLUSH) to the cache controller whenever the flush request (FIN) is generated.

# **SNOOP STROBE**

The Snoop Strobe output of the 82308 Bus Controller is a synchronized strobe indicating a valid address during non-processor write cycles. It is compatible with the 82385 cache controller's bus watching mechanism.

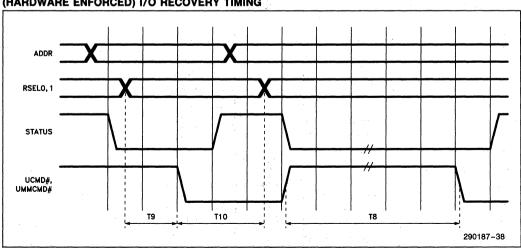

# HARDWARE ENFORCED I/O RECOVERY

Certain I/O devices require a minimum delay between consecutive accesses. Typically, software loops are executed in the I/O routine to force the delay, but software loops cannot guarantee minimum delay times in all cases. The 82308 Bus Controller provides the option of enforcing I/O recovery in hardware. This mechanism is controlled by two inputs (RSEL1 and RSEL0), which select one of four possible minimum I/O recovery times. At the end of a CPU initiated I/O cycle, an internal timer is triggered, and the 82308 will not allow the next I/O access to proceed until the timer has timed out. The specific functioning of RSEL1 and RSEL0 is detailed in the pin definitions and A.C. Timing specifications.

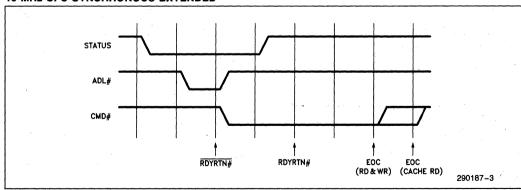

## 16 MHz CPU SYNCHRONOUS EXTENDED

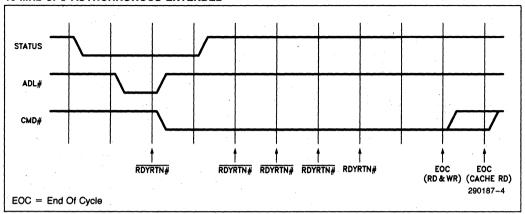

## 16 MHz CPU ASYNCHRONOUS EXTENDED

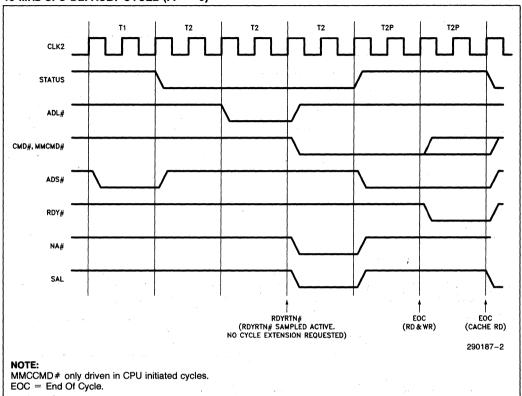

# 20 MHz CPU DEFAULT CYCLE (FP = 1)

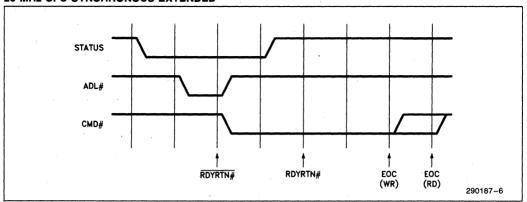

## 20 MHz CPU SYNCHRONOUS EXTENDED

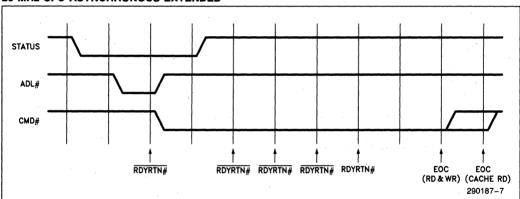

## 20 MHz CPU ASYNCHRONOUS EXTENDED

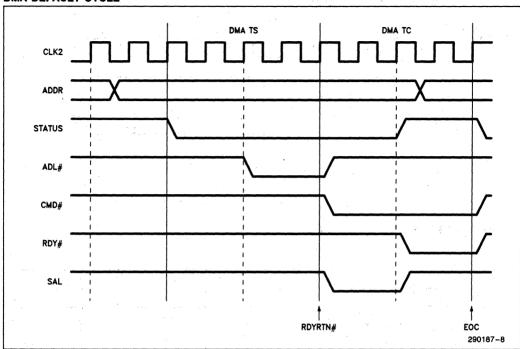

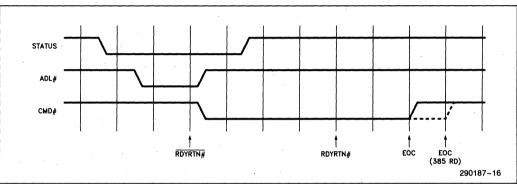

## **DMA DEFAULT CYCLE**

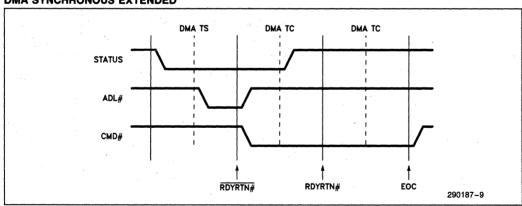

## **DMA SYNCHRONOUS EXTENDED**

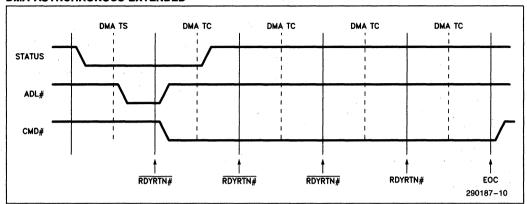

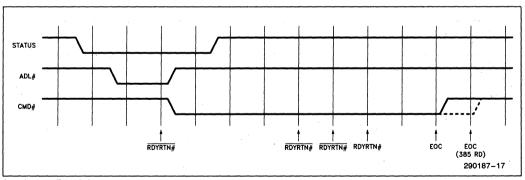

#### **DMA ASYNCHRONOUS EXTENDED**

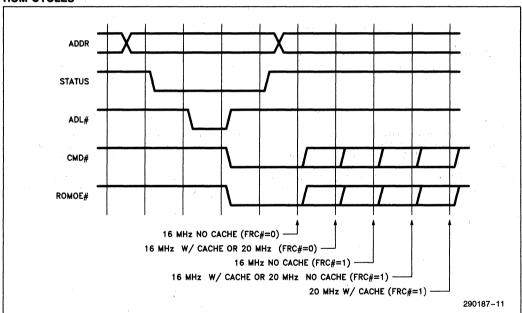

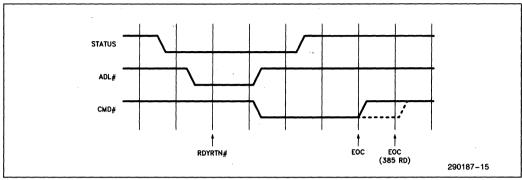

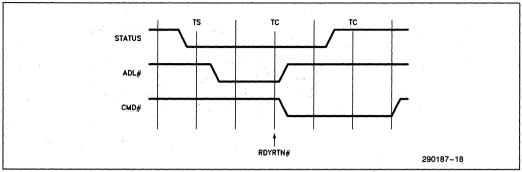

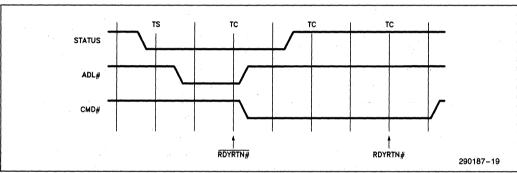

## **ROM CYCLES**

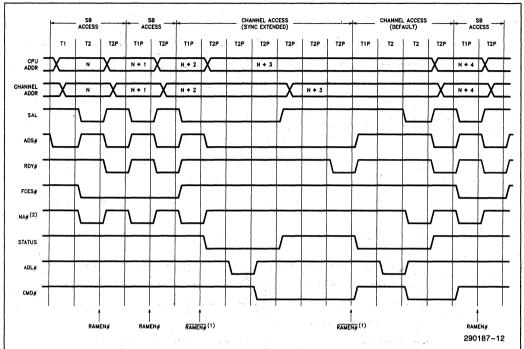

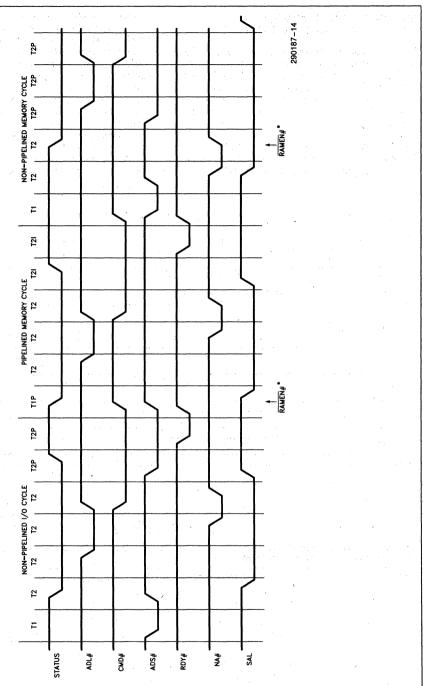

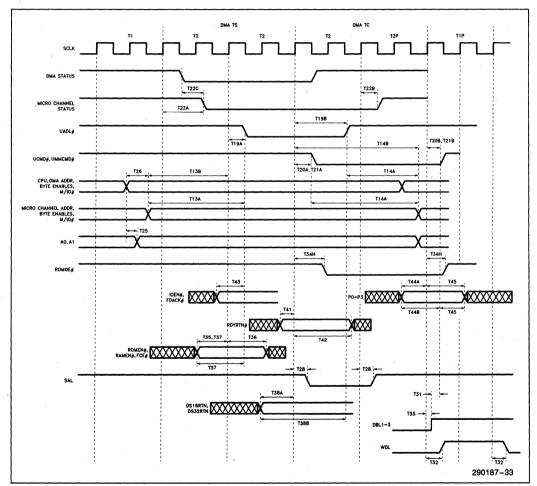

## CPU SYSTEM BOARD MEMORY/Micro Channel MEMORY ACCESSES

### NOTES:

1. RAMEN# distinguishes between system board and channel memory accesses. The BC must wait for RAMEN# to resolve before driving STATUS in a channel access. Thus, in non-pipelined channel accesses or pipelined channel accesses in which the ABC sees only one state of pipelined address, the BC delays starting the channel access until the end of the T1P or first T2 state.

2. In memory cycles the BC must drive NA# before RAMEN# resolves in order to sustain 0WS pipelined page hits.

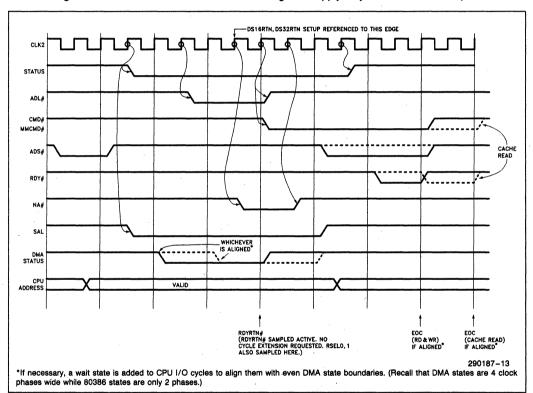

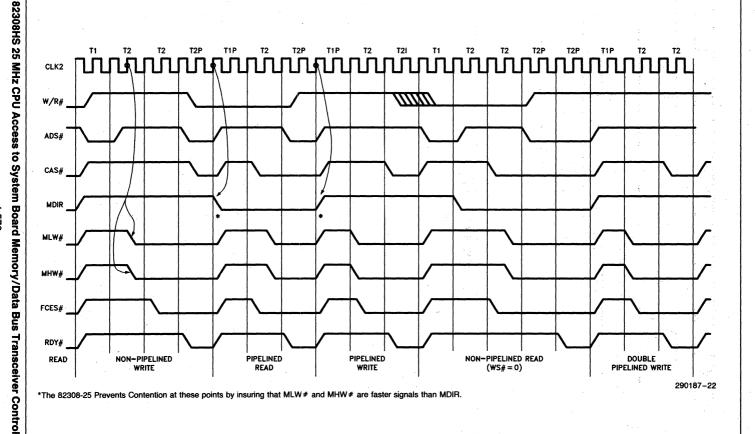

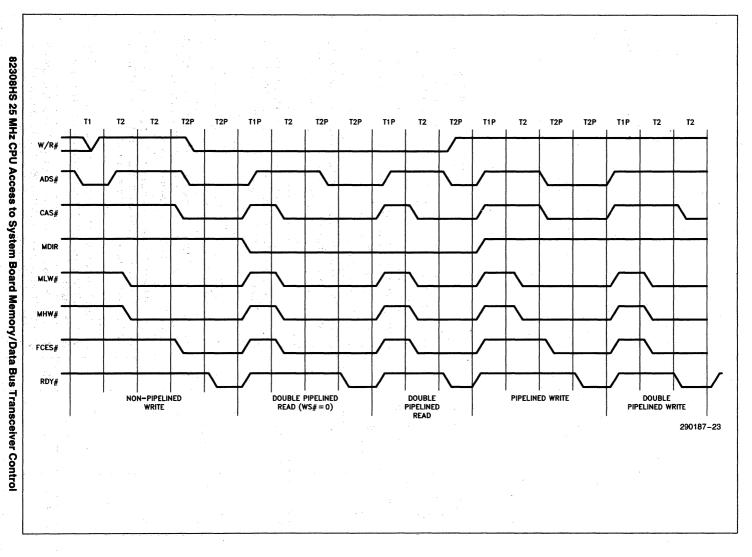

# 82308HS-25 MICROCHANNEL BUS CONTROLLER TIMING DIAGRAMS

The 82308HS-25 provides Microchannel Bus Control for 25 MHz 80386 systems. It is 100% function and pin compatible with the 82308-16/20 Bus Controller, so minimal system re-design is required to upgrade current 16 MHz or 20 MHz systems to 25 MHz. (Note that the 82308HS-25 FP input must be tied high.)

Although the 82308HS-25 is functionally identical to the 82308-16/20, its internal state machine and external timing behavior are modified to insure full compatibility with published Microchannel timings at the increased CPU frequency, and to accommodate 25 MHz system and component specifications. This addendum to the 82308-16/20 data sheet provides the basic timing diagrams for the 82308HS-25, highlighting the specific clock edges that either sample specific inputs, or else trigger specific outputs. All AC specification output delays are referenced to the "causal" clock edge, and input setup/hold times are referenced to the sampling clock edge. Any signal not specifically addressed in these diagrams behaves just as it does in the 82308-16/20. (Note in the AC specifications that notes numbered 21 or greater apply only to the 82308HS-25.)

82308HS 25 MHz CPU Default I/O Cycle

\*Ramen # distinguishes between (non-broadcast) system board and channel memory accesses. (The 82308-25 samples Ramen # and Romen # on the phase 2 clock edge.) The BC must wait for Ramen # to resolve "not true" before driving status in a channel access. Thus, in a non-piplined channel memory access, the BC delays starting the channel cycle until after the first T2 state.

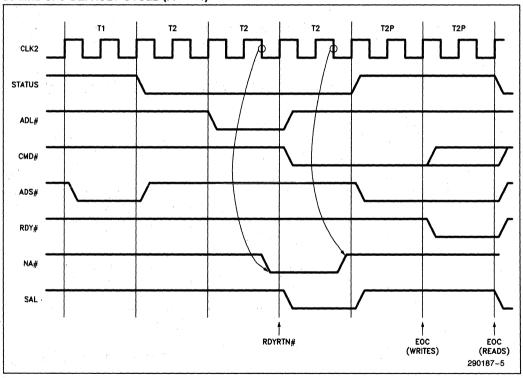

## 82308HS 25 MHz CPU EXTENDED CYCLES

Default

Synchronous Extended

Asynchronous Extended

## 82308HS 25 MHz DMA EXTENDED CYCLES

Default

Synchronous Extended

Asynchronous Extended

82308HS 25 MHz ROM Cycles

4-571

# 82308 Micro Channel Bus Controller Pin Definitions

| Signal<br>Name | Pin<br>Number | 1/0 | Description                                                                                                                                                                                                  |  |  |  |  |

|----------------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RSTRQ#         | 87            |     | Logical NOR of 8042 pin 20 and LCS ALTRESET to initialize reset (Software reset).                                                                                                                            |  |  |  |  |

| RSTCPU         | 91            | 0   | Microprocessor Reset.                                                                                                                                                                                        |  |  |  |  |

| PCE#           | 82            | ı   | Enable Parity Check from Memory Encoding Register Bit 0. This input should be tied low for a model 60 system. (Parity check always enabled.)                                                                 |  |  |  |  |

| PO             | 83            | , 1 | Parity Error from DRAM for bits 0-7.                                                                                                                                                                         |  |  |  |  |

| P1             | 84            | 1   | Parity Error from DRAM for bits 8-15.                                                                                                                                                                        |  |  |  |  |

| P2             | 85            | J   | arity Error from DRAM for bits 16-23.                                                                                                                                                                        |  |  |  |  |

| P3             | 86            | ı   | Parity Error from DRAM for bits 24-31.                                                                                                                                                                       |  |  |  |  |

| PCHCK#         | 90            | 0   | Parity Error Output.                                                                                                                                                                                         |  |  |  |  |

| IOEN#          | 79            | J   | Active low signal from the Address Bus controller indicating a motherboard I/O device address.                                                                                                               |  |  |  |  |

| CHRDY          | 92            | 0   | Input to the Channel Ready Return logic to extend the current cycle.                                                                                                                                         |  |  |  |  |

| FDACK#         | 81            | 1   | FDC DACK# signal.                                                                                                                                                                                            |  |  |  |  |

| IOR            | 97            | 0   | I/O Read signal for motherboard devices (8042, 8259, etc.).                                                                                                                                                  |  |  |  |  |

| IOW            | 98            | 0   | I/O Write signal for motherboard devices.                                                                                                                                                                    |  |  |  |  |

| VMWR#          | 96            | Ò   | Memory write strobe to the VGA.                                                                                                                                                                              |  |  |  |  |

| VMRD#          | 95            | 0   | Memory read strobe to the VGA.                                                                                                                                                                               |  |  |  |  |

| INTA#          | 94            | 0   | INTA# Input to the 8259.                                                                                                                                                                                     |  |  |  |  |

| Α0             | 9             | В   | CPU and DMA Address 0. A0 will be driven by the Bus controller based on the byte enable signals when the 386 owns the bus. It is a Bus controller input in an 80386SX system, or when the DMA is master.     |  |  |  |  |

| A1             | 10            | В   | CPU and DMA Address 1. A1 will be driven by the Bus controller based on the byte enable signals when the 386 owns the bus. It is a Bus controller input in an 80386SX system, or when the DMA is master.     |  |  |  |  |

| BHE#           | 100           | ı   | Byte High Enable signal from the CPU and DMA.                                                                                                                                                                |  |  |  |  |

| BE0-3#         | 11-12, 14-15  | ı   | Byte Enable bits 0-3 from the 80386.                                                                                                                                                                         |  |  |  |  |

| UA0            | 3             | В   | Unbuffered Micro Channel Address bit 0. This signal is generated by the bus controller based on the byte enable signals and A0 from the DMA. It is also manipulated by the swap logic.                       |  |  |  |  |

| UA1            | 4             | В   | Unbuffered Micro Channel Address bit 1. This signal is generated by the bus controller based on the byte enable signals and A1 from the DMA. It is also manipulated by the swap logic.                       |  |  |  |  |

|                |               | 44  | NOTE: For 80386SX systems, UA1 is unconnected, and should be lightly pulled up (10K). The channel A1 is latched along with the upper address lines.)                                                         |  |  |  |  |

| UBHE#          | <b>16</b>     | В   | Unbuffered Micro Channel System Bus High Enable. This signal is generated from BE0-3# when the 386 owns the bus, or BHE# from the DMA. In 80386SX systems, UBHE# is a reflection of the 80386SX BHE# output. |  |  |  |  |

# 82308 Micro Channel Bus Controller Pin Definitions (Continued)

| Signal<br>Name | Pin<br>Number | 1/0 | Description                                                                                                                                                                                                                                                                 |

|----------------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UBE0-3#        | 5-8           | В   | Unbuffered Micro Channel Byte Enable bits 0-3. These byte enable signals are driven by the bus controller when the CPU or DMA is master. (An external PAL is required to generate the channel byte enables on behalf of a 16-bit channel master that requests translation.) |

| TR32           | 99            | 1   | Translate 32 from the Micro Channel to indicate 32 bit masters driving BE0-3# (when inactive). (Tie high for 80386SX system.)                                                                                                                                               |

| SAL            | 18            | 0   | Latch enable for the system address bus. This signal controls the address latch between the CPU bus and channel.                                                                                                                                                            |

| BEDIR          | 17            | 0   | Direction control for the UBE0-3# transceiver. It is high when the Bus controller is driving UBE0-3#.                                                                                                                                                                       |

| PBA#           | 48            | ı   | Indicates that the DMA or numeric coprocessor has been selected and is using the local data bus.                                                                                                                                                                            |

| ROMEN#         | 49            | ı   | Decode that inidicates that the BIOS ROM has been selected.                                                                                                                                                                                                                 |

| DS16RTN        | 50            | ı   | Micro Channel Data Size 16 signal.                                                                                                                                                                                                                                          |

| DS32RTN        | 53            | ı   | Micro Channel Data Size 32 signal.                                                                                                                                                                                                                                          |

| ARB/GNT#       | 54            | ı   | Micro Channel ARB/-GNT status.                                                                                                                                                                                                                                              |

| REFRESH#       | 55            | 1   | Refresh Indicator.                                                                                                                                                                                                                                                          |

| DMA#           | 56            | ı   | Indicates that the DMA owns the bus.                                                                                                                                                                                                                                        |

| HLDA           | 57            | ı   | CPU HLDA input. Indicates CPU controls local address and data bus if low.                                                                                                                                                                                                   |

| WDL            | 36            | 0   | Latch enable signal for latching data bus D0-31 for generating Micro Channel D0-31 signal. Insures Micro Channel write data hold time spec is met.                                                                                                                          |

| DBE1#          | 43            | 0   | Output Enable for driving data on CPU D0-7 onto Micro Channel D0-7 during CPU or DMA writes or Micro Channel DRAM reads.                                                                                                                                                    |

| DBE2#          | 44            | 0   | Output Enable for driving data on CPU D8-15 onto Micro Channel D8-15 during CPU or DMA writes or Micro Channel DRAM reads.                                                                                                                                                  |

| DWHE#          | 45            | 0   | Output Enable for driving data on CPU D16-31 onto Micro Channel D16-31.                                                                                                                                                                                                     |

| SBLW#          | 41            | 0   | Output enable for driving data on Micro Channel D0-15 onto CPU D0-15.                                                                                                                                                                                                       |

| SBHW#          | 42            | 0   | Output enable for driving data on Micro Channel D16-31 onto CPU D16-31.                                                                                                                                                                                                     |

| MDIR           | 32            | 0   | Direction control for transferring data between the CPU Data Bus and the DRAM memory data bus.                                                                                                                                                                              |

| MLW#           | 29            | 0   | Output enable for the transceiver between the CPU data bus D0-15 and the DRAM memory data bus.                                                                                                                                                                              |

| MHW#           | 30            | 0   | Output enable for the transceiver between the CPU data bus D16-31 and the DRAM memory data bus.                                                                                                                                                                             |

| ROMOE#         | 73            | 0   | Output Enable signal for the BIOS ROMs.                                                                                                                                                                                                                                     |

| SWAP1#         | 19            | 0   | Transceiver enable for transferring data between Micro Channel Data Bus 0-7 and 8-15.                                                                                                                                                                                       |

# 82308 Micro Channel Bus Controller Pin Definitions (Continued)

| Signal<br>Name | Pin<br>Number | 1/0          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|----------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SWAP2#         | 20            | 0            | Transceiver enable for transferring data between Micro Channel Data Bus 0-7 and 16-23.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SWAP3#         | 21            | 0            | Transceiver enable for transferring data between Micro Channel Data Bus 8-15 and 24-31.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| SWAP4#         | 22            | 0            | Transceiver enable for transferring data between Micro Channel Data Bus 0-7 and 24-31.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SWDIR          | 23            | 0            | Direction control for Micro Channel Data Bus transceivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| DBL1           | 33            | 0            | Latch enable for latching Micro Channel Data Bus 0-7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| DBL2           | 34            | 0            | Latch enable for latching Micro Channel Data Bus 8-15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| DBL3           | 35            | 0            | Latch enable for latching Micro Channel Data Bus 16-23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| SCLK           | 58            | ı            | Microprocessor Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| RESET          | 59            | ::. <b>1</b> | Synchronized reset input to synchronize the internal clock with the processor phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| RDYRTN#        | 80            | 1            | Channel Ready Return signal from Micro Channel (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| PRDYO#         | 93            | 0            | Microprocessor ready signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| FP             | 68            | ı            | Processor Speed Select. (20 MHz = 1, 16 MHz = 0.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| PRDYI#         | 60            | 1 "          | Synchronized microprocessor ready input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| FRC#           | 61            | .!           | Fast ROM Cycle Select. When tied low, ROM cycles are run as Micro Channel default read cycles. When tied high, additional wait states are inserted to accommodate slower ROMs.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RAMEN#         | 62            | 1            | Decode that indicates a system board DRAM access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| FCE#           | 63            | 1            | Input that directs BC to terminate a CPU system board DRAM access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| UM/IO#         | 64            | lads.F       | Micro Channel Memory/IO status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PD/C#          | 65            | 14.7%        | CPU D/C# output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| PW/R#          | 66            | ľ            | CPU W/R# output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| PADS#          | 67            | 1            | CPU ADS# output. (Indicates address valid.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| PNA#           | 71            | 0            | Next Address Signal for address pipelining.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| S0#, S1#       | 69, 70        | В            | DMA Status lines; input by the BC when DMA is master, and output by the BC when CPU is master.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| UADL#          | 78            | В            | Micro Channel Address Latch Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| UMMCMD#        | 40            | .0           | Micro Channel Matched Memory Command Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| UCMD#          | 72            | В            | Micro Channel Command Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| US0#, US1#     | 76, 77        | В            | Micro Channel Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| RSEL1<br>RSEL0 | 27, 31        |              | These two signals are used for hardware enforced I/O recovery. They are sampled at the leading edge of UCMD# during CPU initiated I/O cycles, and are used to select one of four possible I/O recovery times. At the end of the I/O cycle, an internal timer is triggered, and then times out after the selected I/O recovery time. The next I/O cycle is not allowed to proceed into the active UCMD# phase until the internal timer times out. RSEL1,0 can be strapped for a particular time, or else driven from a combinatorial address decode. |  |  |  |  |  |

# 82308 Micro Channel Bus Controller Pin Definitions (Continued)

| Signal<br>Name  | Pin<br>Number        | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIN             | 26                   |     | Asynchronous cache flush request input. A pulse on FIN causes a cache flush. Also, if FIN is left active for a long period of time, the 82385 will be kept in flush mode for as long as FIN is active. The exception to this is when the BC is directed to do a software initiated CPU reset when FIN is active. The BC will de-activate FLUSH for a period of time surrounding the falling edge of RSTCPU so as to prevent the 82385 from entering its self-test mode. If FIN is still active after the reset, then FLUSH will be re-activated. |

| FLUSH           | 46                   | 0   | Synchronous flush request to the 82385 Cache Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SNOOP#          | 47                   | В   | Synchronous strobe to the cache controller to indicate valid address during a non-processor memory write. SNOOP# is sampled at reset to indicate the presence of a cache. (1 = cache present, 0 = no cache.)                                                                                                                                                                                                                                                                                                                                     |

| PM/IO#          | 28                   | ı   | CPU M/IO# output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WS#             | 39                   | ı   | This input, if tied low, inserts an additional wait state into CPU reads from system board memory beyond the number of wait states requested via the FCE# input. It is primarily intended for cache applications, which typically require increased CPU data setup.                                                                                                                                                                                                                                                                              |

| NC              | 1, 25, 51,<br>52, 75 |     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD</sub> | 13, 37, 88           |     | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>SS</sub> | 2, 24, 38,<br>74, 89 |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

NOTE: NC = No Connect

## **82308 PARAMETRICS**

## **ABSOLUTE MAXIMUM RATINGS\***

Case Temperature under Bias ...  $-40^{\circ}$ C to  $+85^{\circ}$ C Storage Temperature ...  $-65^{\circ}$ C to  $+150^{\circ}$ C Voltage to Any Pin with Respect to Ground ... -0.3V to  $(V_{CC}+0.3)$ V DC Supply Voltage  $(V_{CC})$  ... -0.3V to +7.0V DC Input Current ...  $\pm 10$  mA

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTICE: Specifications contained within the following tables are subject to change.

## D.C. CHARACTERISTICS

$T_C = 0^{\circ}C$  to +70°C,  $V_{CC} = 5V \pm 10\%$

| Symbol          | Parameter                        | Min                   | Max | Units | Conditions                                           |

|-----------------|----------------------------------|-----------------------|-----|-------|------------------------------------------------------|

| V <sub>IL</sub> | Input Low Voltage                |                       | 0.8 | . V   |                                                      |

| V <sub>IH</sub> | Input High Voltage               | 2.0                   |     | ٧     |                                                      |

| V <sub>IL</sub> | Input Low Voltage                |                       | 0.8 | ٧     | SCLK                                                 |

| V <sub>IH</sub> | Input High Voltage               | V <sub>CC</sub> - 0.8 |     | ٧     | SCLK                                                 |

| V <sub>OL</sub> | Output Low Voltage               |                       | 0.4 | ٧     | I <sub>OL</sub> = 4 mA                               |

| V <sub>OH</sub> | Output High Voltage              | 2.4                   |     | ٧ -   | I <sub>OH</sub> = 4 mA                               |

| loc             | Power Supply Current             |                       | 180 | mA    | No DC Loads                                          |

| ILI             | Input Leakage Current            |                       | ±10 | μΑ    | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>CC</sub>  |

| loz             | Tri-State Output Leakage Current |                       | ±10 | μΑ    | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>CC</sub> |

## 82308 Micro Channel BUS CONTROLLER A.C. SPECS

$T_{C}$  = 0°C to +70°C,  $V_{CC}$  = 5V ±10%

|        |                                            | 82308<br>Kit 16 MHz |          | 823        | 308      | 82308HS    |       | 100                 | y 45   |              |  |

|--------|--------------------------------------------|---------------------|----------|------------|----------|------------|-------|---------------------|--------|--------------|--|

| Symbol | Parameter 2                                |                     |          | Kit 20 MHz |          | Kit 25 MHz |       | C <sub>L</sub> (pF) | Notes  | Conditions   |  |

|        |                                            | Min                 | Max      | Min        | Max      | Min        | Max   | 1                   |        |              |  |

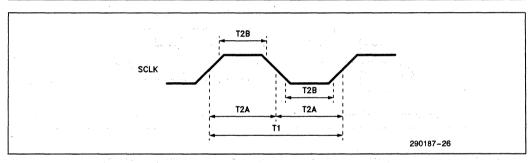

| T1     | SCLK PERIOD                                | 31.25               |          | 25         |          | 20         |       | 4 . 4               | 7 ()   |              |  |

| T2A    | SCLK HIGH/LOW TIME (50%)                   | 12                  |          | 10         |          | 8          |       | 1 %                 | 1.     | Note that    |  |

| T2B    | SCLK HIGH/LOW TIME (90%)                   | 8                   |          | 6.5        |          | 6          |       |                     | 4.1    | the state    |  |

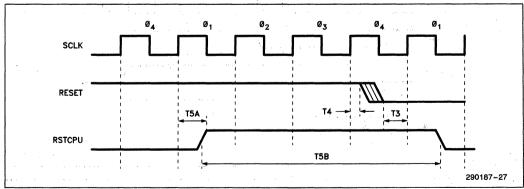

|        | RESET SETUP                                | 10                  |          | 10         |          | 10         |       |                     | 5 ;    |              |  |

| T4     | RESET HOLD                                 | 4                   |          | 4          |          | 4          |       | 1 1                 |        |              |  |

| T5A    | RSTCPU DELAY                               | 2                   | 30       | 2          | 30       | 2          | 27    | 25                  |        |              |  |

| T5B    | RSTCPU PULSE WIDTH                         | 1980                |          | 1580       |          | 1260       |       | 25                  | 14, 20 | 3            |  |

| T6A    | FLUSH DELAY                                | 5                   | 41       | 5          | 34       | - 5        | 28    | 50                  |        |              |  |

| Т6В    | FLUSH PULSE WIDTH                          | 240                 |          | 190        |          | 150        |       | 50                  | 15, 20 |              |  |

| 1      | SNOOP# DELAY                               | 5                   | 41       | 5          | 34       | 5          | 34    | 50                  |        | 1974         |  |

| i      | FIN PULSE WIDTH                            | 25                  |          | 25         |          | 25         |       |                     |        |              |  |

| T8A    | COMMAND I/O RECOVERY PULSE WIDTH           | 600                 |          | 600        |          | 600        |       |                     | 20     | RSEL1,0 = 01 |  |

| T8B    | COMMAND I/O RECOVERY PULSE WIDTH           |                     |          | 2500       |          | 2500       | 1.    |                     |        | RSEL1,0 = 10 |  |

|        | COMMAND I/O RECOVERY PULSE WIDTH           |                     |          | 10000      |          | 10000      | ug ti |                     | 1      | RSEL1,0 = 00 |  |

| 6 5 6  | COMMAND I/O RECOVERY PULSE WIDTH           | 1                   |          | 0          |          | 0          |       |                     | 20     | RSEL1,0 = 11 |  |

|        | RSEL0,1 SETUP                              | 15                  |          | 15         |          | 15         |       |                     | 4      |              |  |

| l I    | RSEL0.1 HOLD                               | 20                  |          | 20         |          | 20         | 2.00  | 5 to 1              | 4      |              |  |

|        | PW/R#, PD/C#, PM/IO# SETUP                 | 25                  |          | 22         |          | 13         |       |                     |        |              |  |

|        | PADS# SETUP                                | 25                  |          | 22         |          | 17         | 100   |                     |        |              |  |

|        | PADS#, PW/R#, PD/C#, PM/IO# HOLD           | 4                   |          | 4          |          | 4          |       | 3.1.2.5             | - 17   | 4.1          |  |

|        | UM/IO# SETUP TO UADL# \                    | 20                  |          | 20         |          | 20         |       |                     |        |              |  |

|        | UM/IO# SETUP TO SCLK                       | 20                  |          | 20         |          | 20         |       |                     | 8      |              |  |

|        | UM/IO# HOLD FROM UADL#↑ OR                 | 20                  |          | 16         | ,        | 16         |       |                     | 7      |              |  |

|        | UCMD# 1                                    |                     |          |            |          | '0         |       |                     | ٠.     |              |  |

|        | UM/IO# HOLD FROM SCLK                      | 20                  |          | 16         |          | 16         |       |                     | 8      |              |  |

|        | PRDYO# DELAY                               | 4                   | 30       | 4          | 24       | 3          | 20    | 75                  | ľ      |              |  |

|        | PRDYI# SETUP                               | 18                  | -        | 18         | -        | 15         |       |                     |        |              |  |

|        | PRDYI# HOLD                                | 3                   |          | 3          |          | 3          |       |                     |        |              |  |

|        | PNA# DELAY                                 | 0                   | 25       | 0          | 25       | 3          | 28    | 25                  |        |              |  |

| 1      | UADL# DELAY (TPHL)                         | 2                   | 24       | 2          | 24       | 2          | 22    | 25                  |        |              |  |

| 1      | UADL# DELAY (TPLH)                         | 2                   | 24       | 2          | 24       | 2          | 22    | 25                  |        |              |  |

|        | UCMD# DELAY (TPHL)                         | 2                   | 23       | 2          | 20       | 2          | 20    | 25                  | 2      |              |  |

|        | UCMD# DELAY (TPLH)                         | 2                   | 25       | 2          | 23       | 2          | 20    | 25                  | -      | ,            |  |

|        | UMMCMD# DELAY (TPHL)                       | 2                   | 23       | 2          | 20       | 2          | 20    | 25                  | 2, 5   |              |  |

|        | UMMCMD# DELAY (TPLH)                       | 2                   | 25       | 2          | 23       | 2          | 20    | 25                  | 2, 3   |              |  |

|        | US0#, US1# (TPHL) DELAY                    | 2                   | 27       | 2          | 26       | 2          | 24    | 25                  | 2      |              |  |

|        | US0#, US1# (TPLH) DELAY                    | 2                   | 27       | 2          | 26       | 2          | 24    | 25                  | _      |              |  |

|        | US0#, US1# (TPHL) DELAY FROM               | 0                   | 27       | 0          | 30       | 0          | 30    | 25                  |        |              |  |

|        | S0#, S1#                                   | "                   | 21       | "          | 30       | "          | 30    | 25                  | -      |              |  |

|        | S0#, S1#<br>S0#, S1# SETUP                 | 20                  |          | 20         |          | 15         |       |                     |        |              |  |

|        |                                            | 1                   | 25       | 1          | 20       | 1          | .00   | F0                  | ł      |              |  |

|        | S0#, S1# DELAY<br>A0, A1 DELAY FROM BE0-3# | 2                   | 35<br>35 | 2          | 30<br>30 | 2          | 22    | 50                  |        |              |  |

|        |                                            | -                   | 35       | -          | 30       | -          | 25    | 25                  |        |              |  |

|        | UBE0-3#, UA0-1#, UBHE#                     | ,                   | 20       |            | 20       |            | òn    | 05                  |        |              |  |

|        | DELAY FROM BE0-3#, A0-1, BHE#              | 2                   | 30       | 2          | 28       | 2          | 28    | 25                  |        | ·            |  |

|        | SAL DELAY                                  | 2                   | 36       | 2          | 30       | 2          | 27    | 100                 | 44 0-  |              |  |

|        | SBHW#, SBLW# INACTIVE DELAY                | 2                   | 30       | 2          | 25       | 2          | 32    | 50                  | 11, 21 |              |  |

|        | FROM SCLK                                  |                     | 40       |            | 40       |            | 40    | 50                  | 0.5    |              |  |

| T30B   | SBHW#, SBLW# DELAY FROM UADL#              | 2                   | 40       | 2          | 40       | 2          | 40    | 50                  | 25     |              |  |

## 82308 Micro Channel BUS CONTROLLER A.C. SPECS

$T_C = 0$ °C to +70°C,  $V_{CC} = 5V \pm 10$ % (Continued)

|        |                                       | 82                        | 308 | 82  | 308   | 823 | 08HS | ·     |            |     |

|--------|---------------------------------------|---------------------------|-----|-----|-------|-----|------|-------|------------|-----|

| Symbol | Parameter                             | Kit 16 MHz Kit 20 MHz Kit |     |     | Kit 2 |     |      | Notes | Conditions |     |

|        |                                       | Min                       | Max | Min |       | Min | Max  | - " ' |            |     |

| T30C   | SBHW#, SBLW# DELAY FROM UCMD#         | 5                         | 35  | 5   | 35    | 5   | 35   | 50    | 10, 25     |     |

| T30D   | SWDIR DELAY FROM UADL#                | 2                         | 40  | 2   | 40    | 2   | 40   | 100   | 12         |     |

|        | DWHE# DELAY FROM UADL#                | 2                         | 40  | 2   | 40    | 2   | 40   | 50    |            | . 9 |

| T30F   | DWHE# DELAY FROM UCMD#                | 5                         | 45  | 5   | 45    | 5   | 45   | 50    | 25         |     |

| T30G   | DBE1#, DBE2# DELAY FROM UADL#         | 2                         | 40  | 2   | 40    | 2   | 40   | 25    |            |     |

| T30H   | DBE1#, DBE2# DELAY FROM UCMD#         | -5.                       | 45  | 5   | 45    | 5   | 45   | 25    | 25 -       |     |

| T30I   | SWAP1-4# DELAY FROM UADL#             | 2                         | 40  | 2   | 40    | 2   | 40   | 25    | 25         |     |

| T30J   | SWAP1-4# DELAY FROM UCMD#             | 5                         | 35  | 5   | 35    | 5   | 35   | 25    | 13, 25     |     |

| T30K   | SBHW#, SBLW# ACTIVE DELAY FROM SCLK   | 2                         | 40  | 2   | 40    | 2   | 40   | 50    | 11         |     |

| T30L   | SWDIR DELAY FROM UCMD#                | 5                         | 40  | 5   | 40    | 5   | 40   | 100   | 13, 25     |     |

| T30M   | SWDIR DELAY FROM DS16RTN, DS32RTN     | 2                         | 35  | 2   | 35    | 2   | 35   | 100   | 12, 25     |     |

| T30N   | SWAP1-4# DELAY FROM UCMD#             | 2                         | 35  | 2   | 35    | 2   | 35   | 25    | 11, 25     | * - |

| T31    | DBL1-3 SETUP TO UCMD#, UMMCMD#        | -4                        |     | -4  | - 1   | -4  |      | 25    |            | ĺ   |

|        | WDL DELAY                             | 2                         | 32  | 2   | 26    | 2   | 21   | 50    |            | 1   |

| T33    | DBL1-3 DELAY↑                         | 2                         | 27  | 2   | 25    | 2   | 22   | 25    |            |     |

|        | MHW#, MLW# ACTIVE DELAY FROM SCLK↑    | 2                         | 30  | 2   | 25    | 2   | 25   | 50    | 16         |     |

| I      | MHW#, MLW# INACTIVE DELAY FROM SCLK 1 | 2                         | 30  | 2   | 25    | 2   | 32   | 50    | 17, 21, 24 |     |

| /T34C  | MDIR DELAY FROM SCLK                  | 2                         | 40  | 2   | 40    | 2   | 40   | 125   | 22, 24     | 1   |

| T34D   | MHW#, MLW# DELAY FROM UADL#           | 2                         | 45  | 2   | 45    | 2   | 45   | 50    | 25         |     |

| T34E   | MHW#, MLW# DELAY FROM UCMD#           | 5                         | 40  | 5   | 40    | 5   | 40   | 50    | 25         |     |

| T34F   | MDIR DELAY FROM UADL#                 | 2                         | 45  | 2   | 45    | 2   | 45   | 125   | 25         |     |

| T34H   | ROMOE# DELAY FROM SCLK                | 2                         | 28  | 2   | 28    | 2   | 28   | 50    |            |     |

| 1      | MHW#, MLW# ACTIVE DELAY FROM SCLK J   | 2                         | 35  | 2   | 35    | 2   | 35   | 50    | 18, 23, 25 |     |

| T34J   | MHW#, MLW# INACTIVE DELAY FROM SCLK 1 | 2                         | 35  | 2   | 35    | 2   | 35   | 50    | 19, 24, 25 |     |

| T35    | FCE# SETUP                            | 15                        |     | 15  |       | 10  |      |       |            |     |

| T36    | FCE# HOLD                             | 3                         |     | 3   |       | 3   |      |       |            |     |

| T37    | ROMEN#, RAMEN# SETUP                  | 20                        |     | 19  |       | 19  |      |       |            |     |

| T38A   | DS16RTN, DS32RTN SETUP TO SCLK        | 30                        |     | 30  |       | 25  |      |       | 6          |     |

| T38B   | DS16RTN, DS32RTN SETUP TO UADL#↑      | 15                        |     | 15  |       | 15  |      |       | 3          |     |

| T41    | RDYRTN# SETUP TO SCLK                 | 10                        |     | 10  |       | 10  |      | 1     | 9          | Ì   |

| T42    | RDYRTN# HOLD FROM SCLK                | 4                         |     | 4   |       | 4   |      |       |            |     |

| T43    | IOEN#, FDACK# SETUP TO UADL# ACTIVE   | 10                        |     | 10  |       | 10  |      | 1     | 25         |     |

| 1      | P0-P3 SETUP TO SCLK                   | 0                         |     | 0   |       | 0   |      |       | 11         |     |

| T44B   | P0-P3 SETUP TO UCMD#                  | 3                         |     | 3   |       | 3   |      |       | 13, 25     |     |

| T45    | P0-P3 HOLD                            | 12                        |     | 12  |       | 12  | *    | 1     | •          |     |

| T46A   | CHRDY DELAY FROM IOEN #               | 2                         | 30  | 2   | 30    | 2   | 30   | 25    |            |     |

| T46B   | CHRDY DELAY FROM STATUS               | 2                         | 25  | 2   | 25    | 2   | 25   | 25    | 25         |     |

| T46C   | CHRDY ACTIVE FROM MB COMMAND          | 100                       |     | 90  |       | 70  |      | 25    | 1, 20      |     |

| T47A   | MB COMMAND DELAY FROM UCMD# ACTIVE    | 75                        |     | 75  |       | 75  |      | 100   | 1, 20      |     |

| T47C   | MB COMMAND DELAY FROM UCMD# INACTIVE  | 3                         | 40  | 3   | 40    | 3   | 40   | 100   | 1, 25      |     |

|        | MB COMMAND PULSE WIDTH                | 250                       |     | 225 |       | 190 |      | 100   | 1, 12, 20  |     |

#### NOTES:

- 1. MB Commands include IOR, IOW, INTA#, VMRD# and VMWR#.

- 2. These specs and cycle edge definitions support a worst case "effective" data setup of 40 ns for a 385 system at 20 MHz. (Effective setup means setup to the "386-like" front end created by the 385.)

- 3. Spec applies only when master resides on Micro Channel.

- 4. RSEL0,1 should be tied high or low, or else driven from a combinatorial address decode.

- 5. UMMCMD# is only driven when the CPU is master.

- 6. Applies only when CPU is master.

- 7. T14A applies to the later of ADL# ↑ or CMD# ↓.

- 8. T13B, T14B apply to CPU or DMA master.

- 9. RDYRTN# is an asychronous input. Meeting T41 simply guarantees recognition at a particular clock edge.

#### NOTES:

- 10. Applies when DMA is master.

- 11. Applies when CPU is master.

- 12. Applies when CPU or DMA is master.

- 13. Applies when DMA or channel master is master.

- 14. Functional Spec . . . Not Tested (= 64 SCLK Periods).

- 15. Functional Spec ... Not Tested (= 8 SCLK Periods).

- 16. READS AND PIPELINED WRITES

- 17. READS

- 18. NON-PIPELINED WRITES

- 19. WRITES

- 20. Functional Spec . . . Not Tested

#### NOTES (82308HS-25 ONLY):

- 21. Contention will not occur when a write immediately follows a read because the 82385 insures at least one BTI state between a read followed by write sequence during which the data bus remains tri-stated.

- 22. MDIR is generated and speced from SCLK↑ instead of from SCLK↓ at it is in the 82308-16/20.

- 23. In non-piped writes, MHW# and MLW# are generated from the phase 2 SCLK↑ edge rather than from SCLK↓ as in the 82308-16/20.

- 24. Since MDIR toggles from the same clock edge that MHW# and MLW# are de-asserted from, contention is prevented by 82308-25 internal design such that MDIR is guaranteed to be slower than MHW# or MLW#.

- 25. Only tested when UADL#, UCMD#, US0#, and US1# are inputs; i.e., when Microchannel is master.

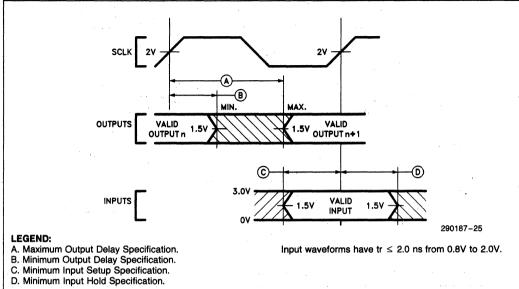

## DRIVE LEVELS AND MEASUREMENT POINTS FOR A.C. SPECIFICATIONS

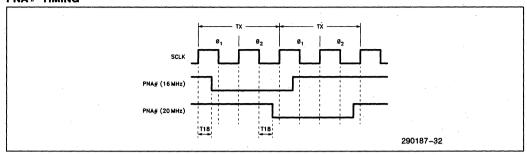

## PNA# TIMING

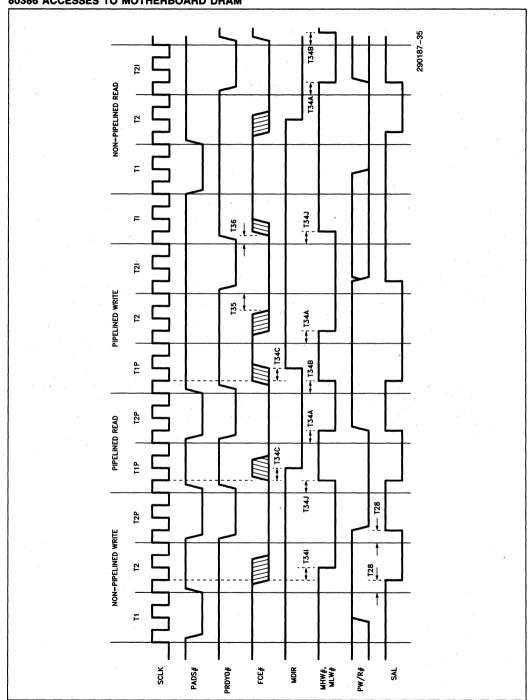

## MEMORY DATA BUFFER CONTROL 80386 ACCESSES TO MOTHERBOARD DRAM

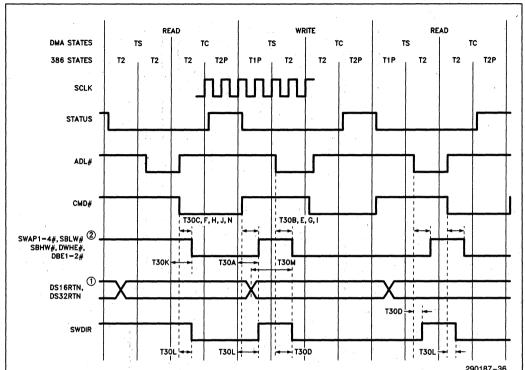

## Micro Channel DATA BUFFER CONTROL 386/DMA MASTER, DATA STEERING FOR CHANNEL MASTER TO CHANNEL SLAVE

©T30D applies to SWDIR only when all involved combinatorial data size inputs (DS16RTN, DS32RTN) are available early enough not to delay SWDIR.

<sup>@</sup> T30A and T30K apply only to SBHW# and SBLW#, and only when the 386 is master.

<sup>©</sup> T30B applies here when DMA data is routed to system board memory from the lower half of the data bus (D0-D15) to the upper half (D16-D31).

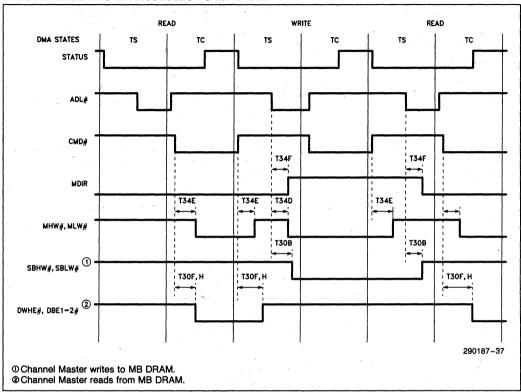

## MEMORY/Micro Channel DATA BUFFER CONTROL DMA/CHANNEL MASTER ACCESSES TO MB DRAM

## (HARDWARE ENFORCED) I/O RECOVERY TIMING