# 82503 DUAL SERIAL TRANSCEIVER (DST)

#### 82503 PRODUCT FEATURE SET OVERVIEW

- Single Component Ethernet\* Interface to Both 802.3 10BASE-T and AUI

- Automatic or Manual Port Selection

- Manchester Encoder/Decoder and Clock Recovery

- No Glue Interface to Industry-Standard LAN Controllers

- Intel 82586, 82590, 82593 and 82596

- AMD 7990 (LANCE\*)

- National Semiconductor 8390 and 83932 (SONIC\*)

- Western Digital 83C690

- Fujitsu 86950 (Etherstar\*)

- Diagnostic Loopback

- **■** Reset, Low Power Modes

- Network Status Indicators

- Defeatable Jabber Timer

- User Test Modes

- 10 MHz Transmit Clock Generator

- One Micron CHMOS\*\* IV (Px48)

Technology

- Single 5-V Supply

#### **INTERFACE FEATURES**

#### **TPE**

- Complies with 10BASE-T, IEEE Std. 802.3i-1990 for Twisted Pair Ethernet

- Selectable Polarity Switching

- Direct Interface to TPE Analog Filters

- On-Chip TPE Squelch

- Defeatable Link Integrity (LI)

- Support of Cable Lengths > 100m

#### AUI

- Complies with IEEE 802.3 AUI Standard

- Direct Interface to AUI Transformers

- On-Chip AUI Squelch

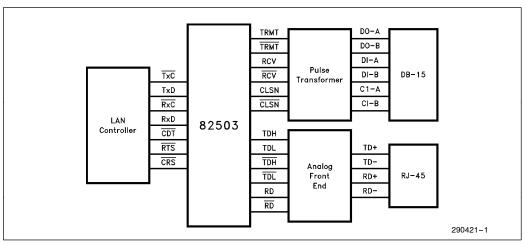

A block diagram of a typical application is shown in Figure 1. The 82503 Dual Serial Transceiver is a high-integration CMOS device designed to simplify interfacing industry standard Ethernet LAN Controllers to IEEE 802.3 local area network applications (10BASE5, 10BASE2, and 10BASE-T). The component supports both an attachment unit interface (AUI) and a Twisted Pair Ethernet interface (TPE). It allows OEMs to design a state-of-the-art media interface that is jumperless and fully automatic. The 82503 includes on-chip AUI and TPE drivers and receivers; it offers designers a cost-effective, integrated solution for interfacing LAN controllers to the wire medium.

LANCE is a registered trademark of Advanced Micro Devices.

Etherstar is a registered trademark of Fujitsu Electronics. Sonic is a registered trademark of National Semiconductor Corporation.

\*Other brands and names are the property of their respective owners information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errated COPYRIGHT © INTEL CORPORATION, 1996

October 1995

October 1995

Order Number: 290421-004

<sup>\*\*</sup>CHMOS is a patented process of Intel Corporation.

<sup>\*</sup>Ethernet is a registered trademark of Xerox Corporation.

# 82503 Dual Serial Transceiver (DST)

| CONTENTS                                           | PAGE       | CONTENTS                                        | PAGE    |

|----------------------------------------------------|------------|-------------------------------------------------|---------|

| 1.0 82503 PRODUCT FEATURES                         | <b>3</b> 3 | 4.0 RESET, LOW POWER AN MODES                   | ID TEST |

| 2.0 PIN DEFINITION                                 | 5          | 4.1 Reset                                       | 16      |

| 2.1 Power Pins                                     |            | 4.2 Low Power and High Im Modes                 | pedance |

| 2.3 AUI Pins                                       | 6          | 4.3 Diagnostic Loopback                         | 16      |

| 2.4 TPE Pins                                       |            | 4.4 Customer Test Modes ( AUI/TPE Transmit)     |         |

| 2.6 Mode Pins                                      |            | <b>5.0 APPLICATION EXAMPLE</b> 5.1 Introduction | 17      |

| <b>3.0 82503 ARCHITECTURE</b> 3.1 Clock Generation |            | 5.2 Design Guidelines 5.3 Layout Guidelines     |         |

| 3.2 Transmit Blocks                                |            | 6.0 PACKAGE THERMAL SPECIFICATIONS              | 19      |

| 3.4 Collision Detection                            | 13         | 7.0 ELECTRICAL SPECIFICA<br>AND TIMINGS         |         |

| 3.6 Jabber Function                                |            |                                                 |         |

| 3.8 SQE Test Function                              | 14         |                                                 |         |

| 3.9 Port Selection                                 | 14         |                                                 |         |

| 3.10 LED Description                               | 14         |                                                 |         |

| 3.11 Polarity Switching                            | 14         |                                                 |         |

| 3.12 Controller Interface                          | 15         |                                                 |         |

Figure 1. Application Block Diagram

#### 1.0 82503 PRODUCT FEATURES

The 82503 incorporates all the active circuitry required to interface Ethernet controllers to 10BASE-T networks or the attachment unit interface (AUI). It supports a direct no-glue interface to Intel's family of high-performance LAN controllers (82586, 82590, 82593, and 82596). The 82503 also provides a direct no-glue interface to the National Semiconductor 8390 and 83932 (SONIC), the Western Digital 83C690, the Advanced Micro Devices 7990 (LANCE) and 79C900 (ILACC), and the Fujitsu 86950 (Etherstar) controllers.

This component includes three advanced features: jumperless two-port design capability, automatic port selection, and polarity switching. The jumperless TPE or AUI port selection capability allows designers maximum ease-of-use and network flexibility. Automatic port selection ensures complete software compatibility with existing 10BASE2 and 10BASE5 software drivers. The 82503's polarity switching feature will detect and correct polarity errors on the twisted pair—the most common wiring fault in twisted pair networks.

The 82503 contains all the circuitry needed to meet the 10BASE-T specification, including link integrity, a jabber timer and internal predistortion. Deselecting link integrity allows the component to be used in some prestandard networks. The 82503's jabber timer prevents the station from continuously transmitting and is defeatable for simple design charac-

terization. The predistortion circuitry eliminates line overcharge and reduces jitter on 10BASE-T links.

The 82503 can also support twisted pair cable lengths of up to 200m when placed in TPE Extended Squelch Mode (XSQ).

This component incorporates six LED drivers to display transmit data, receive data, collision, link integrity, polarity faults and port selections, allowing for complete network monitoring by the user. The transmit, receive and collision LEDs indicate the rate of activity by the frequency of flashing. The 82503 also has a low power mode. During low power, many of the 82503's pins are in a high-impedance state to facilitate board-level testing.

The 82503's diagnostic loopback control enables it to route a transmission signal from the LAN controller through its Manchester encoder-decoder circuitry and back to the LAN controller. This provides effective network node fault detection and isolation capabilities. In addition, the 82503 supports diagnostic test modes that generate continuous tranmission of data through the twisted pair port, allowing designers to measure the analog performance of their design.

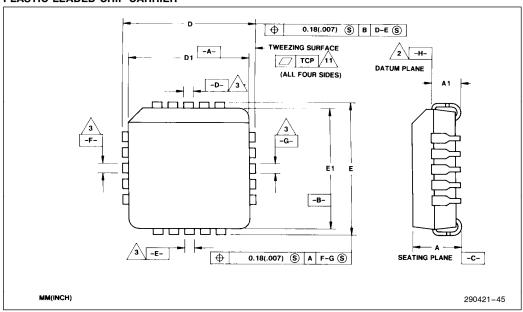

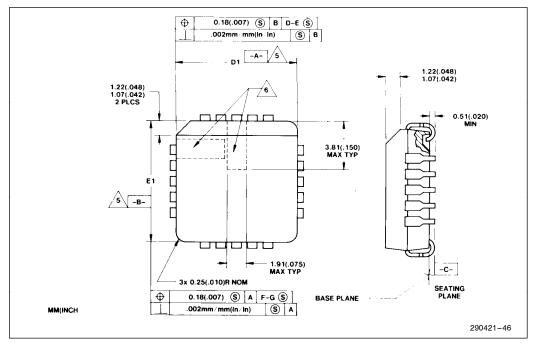

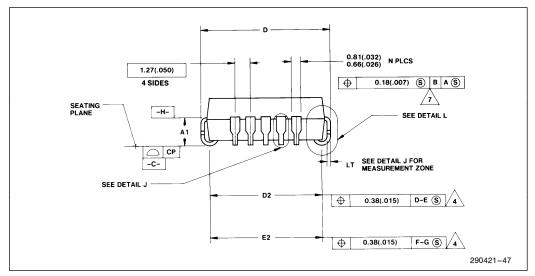

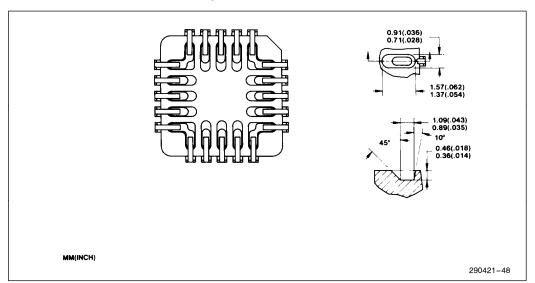

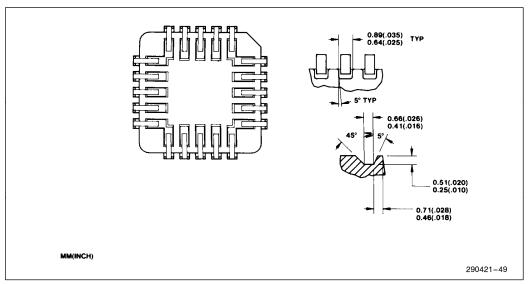

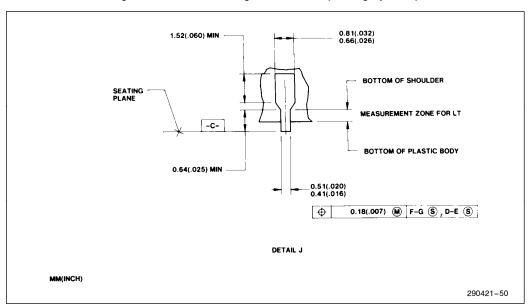

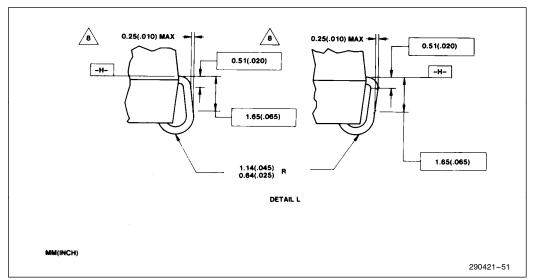

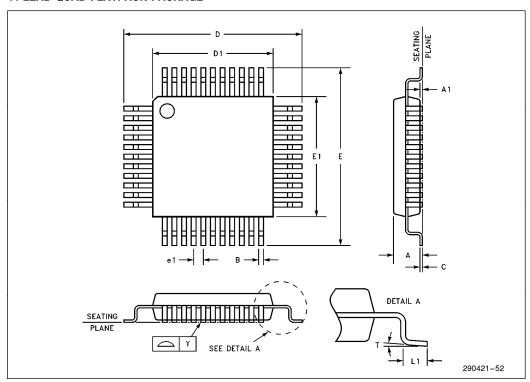

The 82503 is available in 44-lead PLCC and 44-lead QFP packages and is fabricated with Intel's low-power, high-speed, CHMOS IV technology using a single 5-V supply.

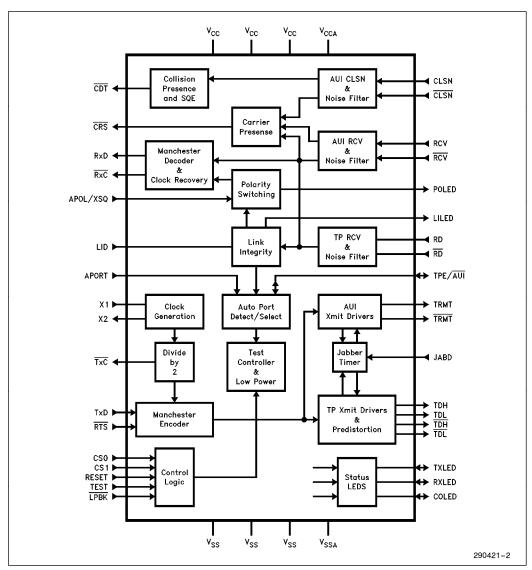

Figure 2. 82503 Functional Block Diagram

# 2.0 PIN DEFINITION

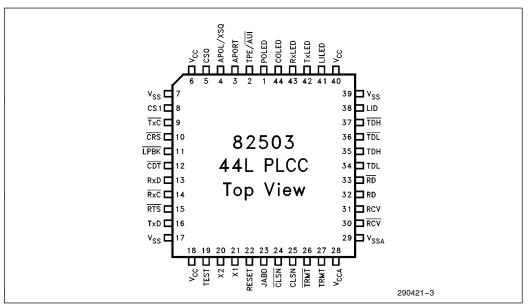

Figure 3. 44-Lead PLCC Pin Configuration

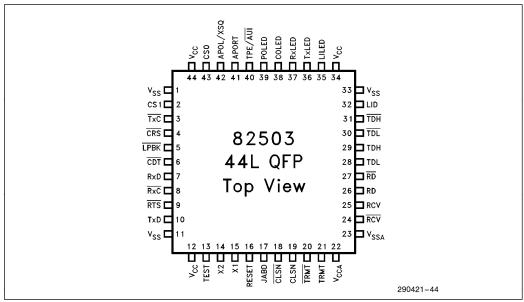

Figure 4. 44-Lead QFP Pin Configuration

5

# 2.1 Power Pins

| Symbol PLCC<br>Pin              |           | QFP<br>Pin | Туре   | Name and Function                                            |  |  |

|---------------------------------|-----------|------------|--------|--------------------------------------------------------------|--|--|

| V <sub>SS</sub> (1)             | 7, 17, 39 | 1, 11, 33  | Supply | Digital Ground.                                              |  |  |

| V <sub>CC</sub> <sup>(1)</sup>  | 6, 18, 40 | 44, 12, 34 | Supply | Digital V <sub>CC</sub> . A 5-V ± 5% Power Supply.           |  |  |

| V <sub>CCA</sub> <sup>(1)</sup> | 28        | 22         | Supply | <b>Analog V</b> <sub>CC</sub> . A 5-V $\pm$ 5% Power Supply. |  |  |

| V <sub>SSA</sub> (1)            | 29        | 23         | Supply | Analog Ground.                                               |  |  |

### NOTE:

# 2.2 Clock Pins

| Symbol | PLCC<br>Pin | QFP<br>Pin | Туре | Name and Function                                                                                                         |  |

|--------|-------------|------------|------|---------------------------------------------------------------------------------------------------------------------------|--|

| X1     | 21          | 15         | I    | CLOCK CRYSTAL. A 20 MHz crystal input. This pin can be driven with an external MOS level clock when X2 is left floating.  |  |

| X2     | 20          | 14         | 0    | CLOCK CRYSTAL. A 20 MHz crystal output. X1 can be driven with an external MOS level clock when this pin is left floating. |  |

# 2.3 AUI Pins

| 2.0 701      |             |            |      |                                                                                                                                                                                                                                                                                                                                                   |

|--------------|-------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol       | PLCC<br>Pin | QFP<br>Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                 |

| TRMT<br>TRMT | 27<br>26    | 21<br>20   | 0 0  | TRANSMIT PAIR. A differential output driver pair that drives the transmit pair of the transceiver cable. The output bit stream is Manchester encoded. Following the last transition, which is positive at TRMT, the differential voltage is reduced to zero volts.                                                                                |

| RCV<br>RCV   | 31<br>30    | 25<br>24   | 1    | RECEIVE PAIR. A differentially driven input pair which is tied to the receive pair of the Ethernet transceiver cable. The first transition on RCV is negative-going to indicate the beginning of the frame. The last transition is positive-going to indicate the end of the frame. The received bit stream is assumed to be Manchester encoded.  |

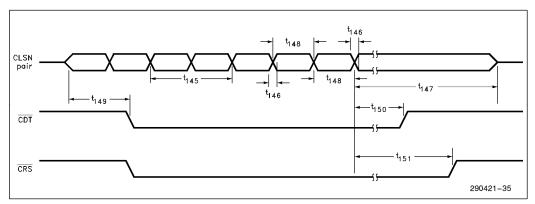

| CLSN<br>CLSN | 25<br>24    | 19<br>18   | I    | COLLISION PAIR. A differentially driven input pair tied to the collision presence pair of the Ethernet transceiver cable. The collision presence signal is a 10 MHz square wave. The first transition at CLSN is negative-going to indicate the beginning of the signal; the last transition is positive-going to indicate the end of the signal. |

V<sub>CC</sub> and V<sub>CCA</sub> must be connected to the same power supply. V<sub>SS</sub> and V<sub>SSA</sub> must be connected to the same ground. Separate decoupling and noise conditioning (e.g., ferrite beads) should be used.

# 2.4 TPE Pins

| Symbol                   | PLCC<br>Pin          | QFP<br>Pin           | Туре    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|----------------------|----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

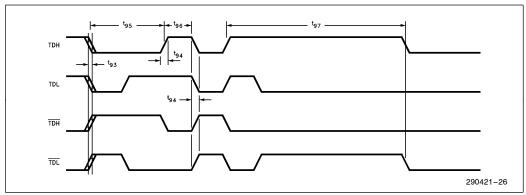

| TDH<br>TDH<br>TDL<br>TDL | 35<br>37<br>34<br>36 | 29<br>31<br>28<br>30 | 0 0 0 0 | TP TRANSMIT PAIR DRIVERS. These four outputs constitute the twisted-pair drivers, which have predistortion capabilities. The TDH/TDH outputs generate the 10 Mb/s Manchester Encoded data. The TDL/TDL outputs mirror the TDH/TDH outputs except for fat bit occurrences (100 ns pulses). During the second half of a fat bit (either high or low), the TDL/TDL outputs are inverted with respect to TDH/TDH outputs. This signal behavior reduces the amount of jitter by preventing overcharge on the twisted pair medium. |

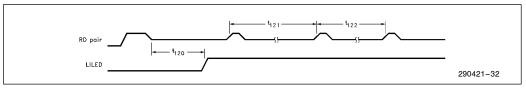

| RD<br>RD                 | 32<br>33             | 26<br>27             | I<br>I  | TP RECEIVE PAIR. The differential twisted pair receiver. The receiver pair is connected to the twisted pair medium and is driven with 10 Mb/s Manchester encoded data.                                                                                                                                                                                                                                                                                                                                                       |

# 2.5 Controller Interface Pins

| Symbol | PLCC<br>Pin | QFP<br>Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                    |

|--------|-------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

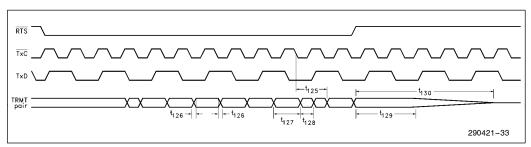

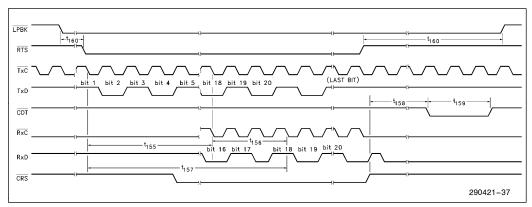

| TxC    | 9           | 3          | 0    | TRANSMIT CLOCK. A 10 MHz clock output tied directly to the transmit clock pin of the Ethernet controller. Changes sense depending on controller selected. Active low for Intel and Fujitsu controller interfaces, active high for National and AMD interfaces. Can drive one TTL load.                                                                               |

| TxD    | 16          | 10         | I    | <b>TRANSMIT DATA.</b> TTL input. NRZ serial data is clocked in on TxD from the Ethernet controller. Connects directly to the transmit data pin of the Ethernet controller.                                                                                                                                                                                           |

| RTS    | 15          | 9          | I    | <b>REQUEST TO SEND.</b> TTL input. An active low input signal synchronous to $\overline{\text{TxC}}$ which enables data transmission on the active port. Changes sense depending on controller selected. Active low for the Intel controller interface, active high for National, AMD, and Fujitsu interfaces.                                                       |

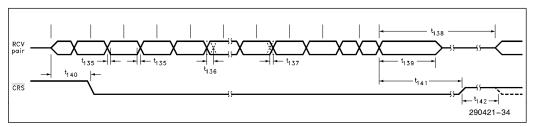

| RxC    | 14          | 8          | 0    | <b>RECEIVE CLOCK.</b> A 10 MHz clock output tied directly to the receive clock pin of the Ethernet controller. This clock is the recovered clock from incoming data on the active port. Changes sense depending on controller selected. Active low for Intel and Fujitsu controller interfaces, active high for National and AMD interfaces. Can drive one TTL load. |

| RxD    | 13          | 7          | 0    | <b>RECEIVE DATA.</b> Received NRZ data (synchronous to $\overline{\text{RxC}}$ ) passed to the Ethernet controller. Connect directly to the receive data pin of the controller. Can drive one TTL load.                                                                                                                                                              |

| CRS    | 10          | 4          | 0    | CARRIER SENSE. Output that alerts the Ethernet controller that data is present on the active port. Connects directly to the carrier sense pin of the Ethernet controller. Changes sense depending on controller mode selected. Active low for Intel controller interface, active high for National, AMD, and Fujitsu interfaces. Can drive one TTL load.             |

| CDT    | 12          | 6          | 0    | COLLISION DETECT. Output that indicates presence of a collision. Connects directly to the collision detect pin of the Ethernet controller. Changes sense depending on controller selected. Active low for Intel and Fujitsu controller interfaces, active high for National and AMD interfaces. Can drive one TTL load.                                              |

7

# 2.6 Mode Pins

| Symbol     | PLCC<br>Pin | QFP<br>Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------|-------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TPE/AUI    | 2           | 40         | I/O  | PORT SELECT. TTL input/LED output. If APORT is low, TPE/ĀŪİ is an input and selects either the TPE port (TPE/ĀŪİ high) or AUI port (TPE/ĀŪİ low). If APORT is high, the 82503 will indicate the port selected by driving TPE/ĀŪİ high (TPE) or low (AUI). TPE/ĀŪİ can drive an LED pull-up.                                                                                                                               |  |  |

| APORT      | 3           | 41         | I    | AUTOMATIC PORT SELECTION. TTL input. When high, 8250 will automatically select TPE or AUI port based on presence of valid link beats or frames on the TPE receive input. Mode selected will be indicated on TPE/AUI.                                                                                                                                                                                                      |  |  |

| APOL/XSQ   | 4           | 42         | I    | AUTOMATIC POLARITY CORRECTION/EXTENDED SQUELCH ENABLE. TTL input. When high, the extended squelch mode is disabled and automatic polarity correction is enabled. Both junctions (APOL and XSQ) are enabled when this pin is at a high impedance state. When low, both functions become disabled. The presence of a polarity fault on the TPE receive pair is indicated on POLED regardless of the state of APOL.          |  |  |

| LID        | 38          | 32         | I    | LINK INTEGRITY DISABLE. TTL input. If high, link integrity function is disabled. If low, link integrity function is enabled.                                                                                                                                                                                                                                                                                              |  |  |

| CS0<br>CS1 | 5<br>8      | 43<br>2    | I    | CONTROLLER SELECT. Selects the appropriate interface for the desired Ethernet controller. When CSO/1 = 0/0, supports Intel controllers. When CSO/1 = 0/1, supports Fujitsu controllers. When CSO/1 = 1/0, supports Western Digital and National controllers. When CSO/1 = 1/1, supports AMD controllers. (See Table 2.)                                                                                                   |  |  |

| LPBK       | 11          | 5          | l    | LOOPBACK. TTL input. An active low input signal that causes the 82503 to enter diagnostic loopback mode. The twisted pair or AUI medium will be removed from the circuit, thus isolating the node from the network. When not connected, this pin assumes the inactive (high) state. Diagnostic loopback does not disable the operation of the link integrity processor, link beat generator, or automatic port selection. |  |  |

| JABD       | 23          | 17         | I    | JABBER DISABLE. TTL input. When high, this pin disables the jabber function. When low, the jabber function is enabled and the device performs AUI or TP jabber protection for the active port. If this pin and TEST are asserted during a falling edge of RESET, the 82503 enters its low power mode; when either this pin or TEST deasserts, then the 82503 transitions to its normal operating mode.                    |  |  |

| TEST       | 19          | 13         | I    | TEST MODE ENABLE. TTL input. When TEST is high and RESET is deasserted, a customer test mode is directly accessed. When driven low, test mode is disabled. If this pin and JABD are asserted during a falling edge of RESET, the 82503 enters its low power mode; when either this pin or JABD deasserts, then the 82503 transitions to its normal operating mode.                                                        |  |  |

| RESET      | 22          | 16         | I    | <b>RESET.</b> TTL input. When high, resets internal circuitry. On the falling edge of RESET, either test mode or low power mode can be entered depending on the state of JABD and TEST.                                                                                                                                                                                                                                   |  |  |

# 2.7 LED Pins

| Symbol | PLCC<br>Pin | QFP<br>Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                              |  |

|--------|-------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

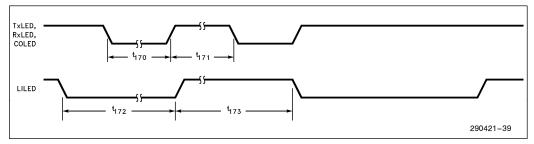

| TxLED  | 42          | 36         | 1/0  | TRANSMIT LED. LED output. Indicates transmit status of the AUI or TPE port. Normally off (high) output. Turns on to indicate transmission. Flashes at a rate dependent on the level of transmit activity. Upon entering a customer test mode, this pin must be driven high either through an LED, or a resistor.                               |  |

| RxLED  | 43          | 37         | 1/0  | RECEIVE LED. LED output. Indicates receive status of the AUI or TPE port. Normally off (high) output. Turns on to indicate reception Flashes at a rate dependent on the level of receive activity. Upon entering a customer test mode, this pin must be driven high either through an LED, or a resistor.                                      |  |

| COLED  | 44          | 38         | 1/0  | <b>COLLISION LED.</b> LED output. Indicates collision status of the AUI or TPE port. Normally off (high) output. Turns on to indicate collision. Flashes at a rate dependent on the level of collision activity. This pin is also used to determine which customer test modes are entered.                                                     |  |

| LILED  | 41          | 35         | 0    | LINK INTEGRITY LED. LED output. Normally on (low) output which indicates good link integrity on the TPE port during TPE mode. Remains on when link integrity function has been disabled. Turns of during AUI mode or when link integrity fails in TPE mode. Minimum off time is 100 ms, minimum on time is set by the link integrity function. |  |

| POLED  | 1           | 39         | 0    | <b>POLARITY INDICATION.</b> LED output. If the 82503 detects that the receive TPE wires are reversed, POLED will turn on (low) to indicate the fault. POLED remains on even if APOL/XSQ is high and the 82503 has automatically corrected for the reversed wires.                                                                              |  |

<sup>NOTE:

1. The LED outputs have a weak pull-up capable of sourcing 500 μA. They can sink 10 mA while still meeting TTL levels. All LEDs can be used as indication pins if no LED is needed. Some of these outputs include pulse width conditioning, which should be accounted for in software.</sup>

#### 3.0 82503 ARCHITECTURE

#### 3.1 Clock Generation

A 20 MHz parallel resonant crystal is used to control the clock generation oscillator, which provides the basic 20 MHz clock source. An internal divide-by-two counter generates the 10 MHz  $\pm 0.01\%$  clock required by the IEEE 802.3 specification.

We recommend a crystal that meets the following specifications be used.

- · Quartz Crystal

- $\bullet~$  20 MHz  $\pm~$  0.002% at 25°C

- Accuracy ± 0.005% over full operating temperature, 0°C to +70°C

- Parallel resonant with 20 pF Load Fundamental Mode

- Maximum Series Resistance:  $R_{SFRIFS} = 30\Omega$

Several vendors have such crystals; either-off-the shelf or custom made. Two possible vendors are:

M-Tron Industries, Inc. Yankton, SD 57078

Specifications;

Part No. HC49 with 20 MHz, 50 PPM over 0°C to +70°C, and 20 pF fundamental load.

Crystek Corporation 100 Crystal Drive Ft. Myers, FL 33907

Part No. 013212

The accuracy of the Crystal Oscillator frequency depends on the PC board characteristics, therefore it is advisable to keep the X1 and X2 traces as short as possible. The optimum value of C1 and C2 should be determined experimentally under nominal operating conditions. The typical value of C1 and C2 is between 22 pF and 35 pF.

An external 20 MHz MOS-level clock may be applied to pin X1, if pin X2 is left floating.

#### 3.2 Transmit Blocks

#### 3.2.1 MANCHESTER ENCODER

The 20 MHz clock is used to Manchester-encode data on the TxD input. This clock is also divided by two to produce the 10 MHz clock the LAN controller needs for synchronizing its  $\overline{\text{RTS}}$  and TxD signals.

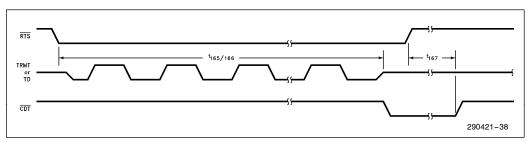

Data encoding and transmission begins with RTS asserting. Since the first bit of a transmission is a 1, the first transition is always negative on the transmit outputs (TRMT or TD pins). Transmission ends when RTS deasserts. The last transition is always positive at the transmit outputs (TRMT or TD pins) and may occur at the center of the bit cell if the last data bit to be transmitted is a 1, or at the boundary of the bit cell if the last data bit to be sent is a 0.

Immediately after the end of a transmission, all signals on the RCV pair (when AUI mode is selected) are inhibited for 4 to 5  $\mu$ s. This dead time is necessary for proper operation of the SQE (heartbeat) test.

#### 3.2.2 AUI CABLE DRIVER

The AUI cable driver (TRMT pair) is a differential circuit, which interfaces to the AUI cable through a pulse transformer.

High voltage protection is achieved by using a transformer to isolate the transmit pins (TRMT pair) from the transceiver cable. The total transmit circuit inductance, including the 802.3 transceiver transformers, should be a minimum of 27  $\mu$ H for Ethernet applications.

#### 3.2.3 TWISTED PAIR CABLE DRIVER

The twisted pair line drivers (TD pairs) begin transmitting the serial Manchester bit stream 3 bit times after RTS is asserted. The line drivers use a predistortion algorithm to improve jitter performance for up to 100 meters of twisted pair cable. The line drivers reduce their drive level during the second half of "fat" (100 ns) Manchester pulses and maintain a full drive level during all "thin" (50 ns) pulses and during the first half of the "fat" pulses. This reduces line overcharging during "fat" pulses, a major source of jitter.

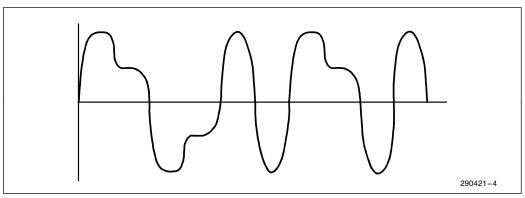

Figure 5. TPE Predistortion

#### 3.3 Receive Blocks

# 3.3.1 MANCHESTER DECODER AND CLOCK RECOVERY

The 82503 performs Manchester decoding and timing recovery of the incoming data in AUI and TPE modes.

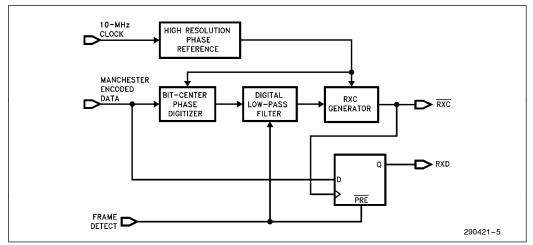

The Manchester-encoded data stream is decoded to separate the Receive Clock ( $\overline{\text{RxC}}$ ) and the Receive Data (RxD) from the differential signal. The 82503 uses an advanced digital technique to perform the decoding function. The use of digital circuitry instead of analog circuitry (e.g., a phase-lock loop) to perform the decoding ensures that the decoding function is less sensitive to variations in operating conditions.

A high-resolution phase reference is used to digitize the phase of the incoming data bit-center transition. The digitizer has a phase resolution of 1/32 of a bit time. The digitized phase is filtered by a digital low-pass filter to remove rapid phase variations, i.e., phase jitter. Slow phase variations, such as those caused by small differences between the data frequency and the clock frequency, are not filtered by the low-pass filter.

The  $\overline{\text{RxC}}$  generator digitally sets the phases of the two  $\overline{\text{RxC}}$  transitions to respectively lead and lag the bit-center transition by  $\frac{1}{4}$  bit time.  $\overline{\text{RxC}}$  is used to recover RxD by sampling the incoming data with an edge-triggered flip-flop.

Lock is achieved by reducing the time constant of the digital filter to zero at the start of a new frame. Any uncertainty in the bit-center phase of the first transition that is caused by jitter is subsequently removed by gradually increasing the filter time constant during the following preamble. By that time, the phase of the bit center is output by the filter, and lock is achieved. Lock is achieved within the first 14 bit times as seen by the AUI inputs. The maximum bit-cell timing distortion (jitter) tolerated by the Manchester decoder circuitry is  $\pm\,12$  ns (preamble),  $\pm\,18$  ns (data) for AUI, and  $\pm\,13.5$  ns for TPE (data and preamble).

Figure 6. Manchester Decoder and Clock Recovery

#### 3.3.2 AUI RECEIVE AND COLLISION BUFFERS

The AUI receive and collision inputs are driven through isolation transformers to provide high voltage protection and DC common mode voltage rejection. The incoming signals are converted to digital levels and passed to the Manchester decoder and collision detection circuitry.

# 3.3.3 AUI RECEIVE AND COLLISION SQUELCH CIRCUITS

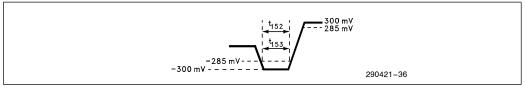

Both the receive (RCV) and collision (CLSN) pairs have the following squelch characteristics.

- The squelch circuits are turned on at idle.

- A pulse is rejected if the peak differential voltage is more positive than -160 mV regardless of pulse width.

- A pulse is considered valid if its peak differential voltage is more negative than -300 mV and its width, measured at -285 mV, is greater than 25 ns

- The squelch circuits are disabled by the first valid negative differential pulse on either the AUI receive (RCV) or the AUI collision (CLSN) pair.

- If a positive differential pulse occurs on either the AUI receive or collision pairs for greater than 160 ns, End of Frame (EOF) is assumed and the squelch circuitry is turned on.

# 3.3.4 TPE RECEIVE BUFFER

The TPE receive pins (RD and  $\overline{\text{RD}}$ ) are connected to the twisted pair medium through an analog front end. The analog front end contains the line coupling

devices and EMI filters necessary to conform to the 10BASE-T standards and local RF regulations. The input differential voltage range for the TPE receiver is greater than 500 mV and less than 3.1V differential.

#### 3.3.5 TPE RECEIVE SQUELCH CIRCUITS

The TPE receive buffer distinguishes valid receive differential data, link test pulses, and the idle condition according to the requirements of the 10BASE-T standard. Signals at the output of the EMI filter (thus at the RD and  $\overline{\text{RD}}$  pair) are rejected as follows:

- All differential pulses of peak magnitude less than 300 mV are rejected.

- All continuous sinusoids with a differential amplitude less than 6.2 V<sub>PP</sub> and a frequency less than 2 MHz are rejected.

- All sine waves of single cycle duration starting with phase 0° or 180° that have an amplitude less than 6.2 Vpp, and a frequency of 2 MHz to 16 MHz are rejected, if the single cycle is preceeded and followed by 4 bit times of silence (i.e., a signal less than 300 mV).

# 3.3.6 TPE Extended Squelch Mode

By placing the 82503 into TPE extended squelch mode, the 82503 can support cable lengths greater than the 100m specified in the 10Base-T IEEE standard (802.3i-1990). The squelch thresholds for the signals at the RD/ $\overline{\text{RD}}$  pair are typically reduced by 4.5 dB. This allows Grade 5 twisted-pair cable to be used to overcome attenuation and multipair crosstalk for cable lengths up to 200 meters.

TPE extended squelch mode is enabled by presenting a high-impedance (> 100  $\mathrm{K}\Omega$ ) at the APOL/XSQ pin. This can be done by floating the APOL/XSQ pin, tying APOL/XSQ low through a 100  $\mathrm{K}\Omega$  resistor, or driving APOL/XSQ with a three-state buffer. When driven high or low using a TTL driver or a low impedance pull-up or pull-down (<2  $\mathrm{K}\Omega$ ) extended squelch is disabled and the driven level at the APOL/XSQ pin determines the state of the polarity-correction function (APOL/XSQ = 1 enables polarity correction). The TPE extended squelch feature is transparent to previous steppings of the 82503. Polarity correction is always enabled when the TPE extended-squelch feature is enabled (APOL/XSQ = Z).

The APOL/XSQ pin senses a high-impedance state by an active-polling circuit implemented at the pin. Two small polling devices attempt to pull the APOL/XSQ pin up to  $V_{CC}$  and down to  $V_{SS}$ . If the pin is in a high-impedance state, the devices will be successful in pulling the APOL/XSQ pin high and low. If the pin is driven high or low, the polling devices will not be able to successfully pull the pin in the opposite direction. In this way, an internal state machine can correctly determine one of three states of the APOL/XSQ pin. The pin is polled every 25.6  $\mu$ s.

#### 3.4 Collision Detection

#### 3.4.1 AUI COLLISION DETECTION

Collision detection in the AUI mode is performed by the attached transceiver, and signalled to the 82503 on the CLSN pair. A 10 MHz +25%, or -15%, square wave with transition times between 35 ns and 70 ns indicates the collision. The 82503 reports this to the LAN controller on the  $\overline{\text{CDT}}$  pin.

#### 3.4.2 TPE COLLISION DETECTION

Collision detection in the TPE mode is indicated by simultaneous transmission and reception on the twisted pair link segment. The  $\overline{\text{CDT}}$  signal is asserted for the duration of both  $\overline{\text{RTS}}$  and the presence of received data;  $\overline{\text{CRS}}$  is asserted for the duration of either  $\overline{\text{RTS}}$  or the presence of received data. During a collision, the source of RxD will be the received data. If the received data stream ends before the transmit data stream, the RxD source will be changed to transmit data stream until it ends.

#### 3.5 Link Integrity

The 82503 supports the link integrity function as defined by 10BASE-T. During long periods of idle on the transmitter, link test pulses will be transmitted on

to the twisted pair medium as an indication to the remote MAU that the link is good. These pulses will be transmitted 8 ms to 24 ms after the end of the last transmission or link test pulse.

The link integrity function continuously monitors activity on the receive circuit. If neither valid data nor link test pulses are received, the link integrity processor declares the link bad, and disables transmission and reception on the media, loopback, and the SQE test function. Transmission of link test pulses and monitoring receive activity are not affected. The idle time required for the link integrity processor to determine the link is bad is 50 ms to 150 ms.

Once a frame or a sequence of 2 to 10 valid consecutive link test pulses are detected, the Link Integrity Processor declares the link is good, and reconnects the transmitter and receiver.

The link integrity function can be disabled by driving the LID pin high or by disabling automatic port selection (APORT = 0) and selecting the AUI port. This option is intended primarily for use with pre-10BASE-T networks.

### 3.6 Jabber Function

The 82503 contains a jabber timer to implement the jabber function. If a transmission continues beyond the limits specified, the jabber function inhibits further transmission and asserts the collision indicator, CDT. The limits for jabber transmission are 20 ms to 150 ms in TPE Mode, and 8 ms to 16 ms in AUI mode. For both AUI and TPE mode, the transmission inhibit period extends until the 82503 detects sufficient idle time (between 250 ms and 750 ns) on the RTS signal. The jabber function can be disabled by driving the JABD high.

In TPE mode the link integrity function continues to operate even if the jabber function is inhibiting transmission. Link test pulses continue to be sent and the receive circuit continues to be monitored. Additionally, the link integrity function reconnects to a restored link without waiting for the transmit input to go idle when the jabber function is inhibiting transmission.

# 3.7 TPE Loopback

In TPE mode the 82503 implements the transmit to receive loopback (DO to DI) mode specified in the 10BASE-T standard. This mode loops back transmitted data through the receive path.

This function is required to maintain full compatibility with coax MAUs where the data loopback is a natural result of the architecture.

The transmit to receive loopback function is disabled when the jabber function or link integrity function is inhibiting transmission.

#### 3.8 SQE Test Function

The 82503 supports the SQE test function when in TPE mode or in Diagnostic Loopback mode. The 82503 will assert its  $\overline{\text{CDT}}$  pin within 0.6  $\mu$ s to 1.6  $\mu$ s after the end of a transmission, and it will remain asserted for 5- to 15-bit times. If the 82503 is in the TPE mode and is not in diagnostic loopback mode, the link integrity function will disable the SQE test function when it detects a bad link.

#### 3.9 Port Selection

The 82503 features both manual and automatic port selection. To enable automatic port selection, connect APORT to  $V_{\text{CC}}$ . The 82503 then starts in TPE mode and monitors link integrity. If the link is good, the 82503 stays in TPE mode and pulls TPE/AUI high to indicate that the TPE port was selected. If link integrity fails, the 82503 switches to AUI mode and pulls TPE/AUI low to indicate that the AUI port is now active. TPE/AUI can drive an LED to indicate port selection (on for AUI, off for TPE mode). Note that LILED will be on if TPE mode is selected and off if AUI mode is selected. If link integrity is disabled while automatic port selection is enabled, the 82503 defaults to TPE mode. If the 82503 changes ports while RTS is active, transmission is terminated with an End of Frame marker on the old port. Transmission of the remaining packet fragment is not allowed on the new port. Transmissions will begin with a complete data packet.

The port can be manually selected by driving APORT low. TPE/ $\overline{AUI}=0$  selects AUI mode, and TPE/ $\overline{AUI}=1$  TPE mode. When the port is manually selected, the circuitry for the unused port is powered down. Changing ports requires 100  $\mu s$  to allow the circuitry for the new port to resume normal operation.

**Table 1. Port Selection**

|     | Configu | ration  | State                       |  |  |

|-----|---------|---------|-----------------------------|--|--|

| LID | APORT   | TPE/AUI |                             |  |  |

| Х   | 0       | 0       | AUI (TPE Port Powered Down) |  |  |

| Х   | 0       | 1       | TPE (AUI Port Powered Down) |  |  |

| 0   | 1       | X*      | Automatic Port Selection    |  |  |

| 1   | 1       | X*      | TPE                         |  |  |

#### NOTE:

#### 3.10 LED Description

The 82503 supports six LED pins to indicate the status of important states; TPE/AUI, TxLED, POLED, LILED, RxLED, COLED. Each pin is capable of directly driving an LED.

#### 3.10.1 TPE/AUI

When automatic port selection is enabled (APORT is high), TPE/AUI becomes an LED output and turns off if TPE mode is selected and on if AUI mode is selected

#### 3.10.2 TxLED

Transmit status. This LED is normally off and flashes at 2.5 Hz, 5 Hz, and 10 Hz to indicate respectively a low, medium, and high rate of transmit activity.

#### 3.10.3 RxLED

Receive LED. This LED is normally off and flashes at 2.5 Hz, 5 Hz, and 10 Hz to indicate respectively a low, medium, and high rate of receive activity.

#### 3.10.4 COLED

Collision LED. This LED is normally off and flashes at 2.5 Hz, 5 Hz, and 10 Hz to indicate respectively a low, medium, and high rate of collision activity.

#### 3.10.5 POLED

Polarity Fault. This LED is normally off and turns on to indicate a polarity fault in the receive pair of the 10BASE-T link. Operation of this pin is not affected by the state of the polarity correction function (APOL/XSQ = X).

#### 3.10.6 LILED

Link Integrity status. When Aport is enabled (APORT = 1), this LED is normally on (driven low) to indicate the presence of a valid 10BASE-T link when the TPE port is active. The LED will turn off (driven high) when the link fails. When link integrity is disabled (LID = 1) while APORT is enabled (APORT = 1) this LED is turned on (driven low). If APORT is disabled (APORT = 0) and the AUI port is manually selected (TPE/ $\overline{AUI}$  = 0) the LED output is tristated.

#### 3.11 Polarity Switching

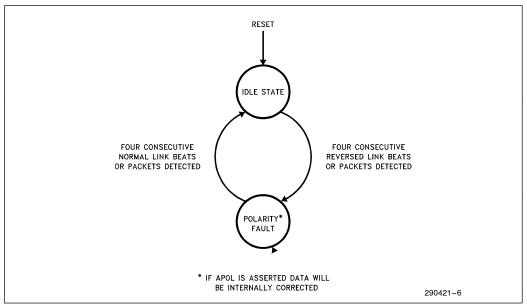

In TPE mode, the 82503 monitors receive link beats and end-of-frame delimiters for a possible receiver

<sup>\*</sup>TPE/ $\overline{AUI}$  is an output pin when APORT = 1.

Figure 7. Polarity Fault State Diagram

polarity error due to crossed wires. If Pin 4 of the 82503 is high and the TPE receive pins are reversed, the 82503 will correct the error by reversing the signals internally, and turn POLED on (low) to indicate that the fault has been detected and corrected. The polarity correction function is defeatable by driving the APOL/XSQ input low. However, the polarity fault will continue to be indicated on the POLED.

### 3.12 Controller Interface

Connecting the 82503 to one of the Intel Ethernet controllers (82586, 82590, 82593, 82596) requires no additional components. Simply drive CS0 and CS1 both low, and connect  $\overline{\text{TxC}}$ ,  $\overline{\text{TxD}}$ ,  $\overline{\text{RTS}}$ ,  $\overline{\text{RxC}}$ , RxD,  $\overline{\text{CRS}}$ ,  $\overline{\text{CDT}}$ , and  $\overline{\text{LPBK}}$  to the corresponding controller pins.

The 82503 also works with other Ethernet controllers without additional components, including the National Semiconductor 8390 and 83932 (SONIC), Western Digital 83C690, Fujitsu 86950 (Etherstar), depending on the state of and CS0 and CS1 inputs.

The interface of the 82503 to the AMD 7990 (LANCE) requires external logic to control the  $\overline{LPBK}$  pin of the 82503. Note that when an AMD LAN controller is used to interface to the 82503, the  $\overline{LPBK}$  pin of the 82503 becomes active high. That is, the 82503 enters diagnostic loopback mode when  $\overline{LPBK}$  pin is high and is in normal operation mode when  $\overline{LPBK}$  pin is low.

The logic sense of the 82503 controller pins will change and should be connected to the controller pins according to the following table.

| Table 2. 0 | Controller | Interface | Selection |

|------------|------------|-----------|-----------|

|------------|------------|-----------|-----------|

| 82503<br>Pin                     | Intel<br>Controller<br>825XX     |                                   | National, WD<br>Controllers<br>8390, 83C690,<br>83832 (SONIC) |                                                      | Cont<br>7990 (L                                  | MD<br>roller<br>.ANCE),<br>(ILACC)                   | Fujitsu<br>Controllers<br>86950 (Etherstar) |                                                           |

|----------------------------------|----------------------------------|-----------------------------------|---------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------|------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|

| CS0 <sup>(1)</sup><br>CS1        | 0                                |                                   | 1 0                                                           |                                                      | 1 1                                              |                                                      | 0                                           |                                                           |

| Pin                              | Pin                              | Sense                             | Pin                                                           | Sense                                                | Pin                                              | Sense                                                | Pin                                         | Sense                                                     |

| TxC TxD RTS RxC RxD CRS CDT LPBK | TxC TxD RTS RxC RxD CRS CDT LPBK | Low High Low Low High Low Low Low | TXC TXD TXE RXC RXD CRS COL LPBK                              | High<br>High<br>High<br>High<br>High<br>High<br>High | TCLK<br>TX<br>TENA<br>RCLK<br>RX<br>RENA<br>CLSN | High<br>High<br>High<br>High<br>High<br>High<br>High | TCKN TXD TEN RCKN RXD XCD XCOL LPBK         | Low<br>High<br>High<br>Low<br>High<br>High<br>Low<br>High |

#### NOTES:

- 1. CS0 and CS1 are intended to be static pins only. Switching CS0 and CS1 during network reception or transmission will produce unpredictable results.

- 2. Refer to Section 3.12.

# 4.0 RESET, LOW-POWER AND TEST MODES

#### 4.1 Reset

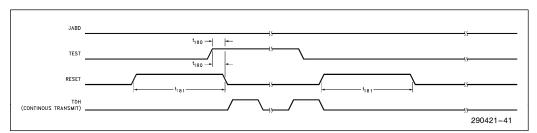

When RESET is asserted the device resets its internal circuits. RESET is required after power up, and before data can be transmitted or received. It is allowed any time thereafter, but any existing receive or transmit activity will be lost, and all state machines (Link integrity, Jabber, and Polarity Correction) return to their initial states. TEST must be held low for a device reset to prevent entering a test for low power mode. During RESET, TxC continues without interruption (in Fujitsu mode both TxC and RxC run continuously).

# 4.2 Low Power and High Impedance Modes

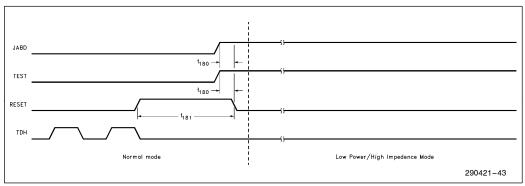

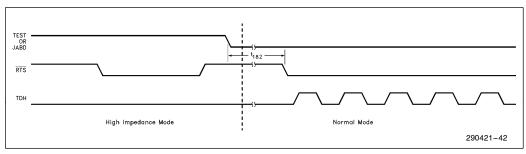

When RESET is deasserted while both TEST and JABD are held high, the 82503 enters its low power and high impedance modes. The majority of internal circuitry is powered down, and many inputs and outputs are three-stated. These pins are: APORT, APOL/XSQ, LID, TPE/AUI, POLED, LILED, RTS, LPBK, RxD, TxD, CRS and CDT. When either JABD or TEST is deasserted, the device begins a power on cycle which lasts less than 1 ms. During this cycle, all inputs are ignored and all transmissions are disabled. If RTS is active when the device returns to normal operation, the remainder of that packet fragment is not transmitted. Normal transmissions are resumed at the start of the first complete data packet.

### 4.3 Diagnostic Loopback

This is a diagnostic test mode to help in fault isolation and detection. Serial NRZ data input on TxD is Manchester encoded and then looped back through the Manchester decoder (TMD) appearing at the RxD output. Collision detect is asserted following each transmission to simulate the SQE test. Output cable drivers and input amplifiers are disconnected from the controller interface pins while in this mode. The link integrity and polarity fault detection functions are not inhibited by diagnostic loopback mode. If otherwise enabled, they continue to function.

# 4.4 Customer Test Mode (Continuous AUI/TPE Transmit)

In this mode, the 82503 continuously transmits data without the intervention of a LAN controller. Transmission is at 10 MHz (11-bit pattern), and can occur on either the TPE or AUI port. The jabber timer is disabled in this mode, allowing users to easily test the 10BASE-T harmonic content specification and the quality of their analog front end design without complex software exercisers.

Customer Test Mode—and Low Power Mode are selected at the deassertion of RESET as shown in the following table. (Note that the 82503 must be in non-loopback mode before it can enter the customer test mode.)

| Table 6. Test and Low I ower mode detection |      |      |                        |   |          |                |  |  |  |

|---------------------------------------------|------|------|------------------------|---|----------|----------------|--|--|--|

| RESET                                       | TEST | JABD | JABD TxLED(1) RxLED(1) |   | COLED(1) | Mode Selected  |  |  |  |

| <b>1</b>                                    | 0    | Х    | Х                      | Х | Х        | Normal Mode    |  |  |  |

| <b>1</b>                                    | 1    | 0    | 1                      | 1 | 1        | Cont Tx 10 MHz |  |  |  |

| $\downarrow$                                | 1    | 1    | Х                      | Х | Х        | Low Power      |  |  |  |

Table 3. Test and Low Power Mode Selection

#### NOTE:

1. A standard LED connection to these pins is sufficient to pull them to a logic 1.

The port on which the continuous transmit appears is determined by the APORT and TPE/ $\overline{AUI}$  pins. If automatic port selection is enabled (APORT = 1) then the TPE port broadcasts the continuous transmit. If manual port selection is enabled (APORT = 0), then TPE/ $\overline{AUI}$  selects the port (1 for TPE, 0 for AUI). Test mode is disabled when TEST is deasserted and the device is reset.

#### 5.0 APPLICATION EXAMPLE

#### 5.1 Introduction

The 82503 is designed to work directly with the Intel LAN controllers (82586, 82590, 82593, and 82596), as well as AMD's Am7990, National Semiconductor's 8390, Western Digital's 82C690, and Fujitsu's 86950. The serial interface signals connect directly between one of the aforementioned LAN controllers and the 82503 without the need for external logic.

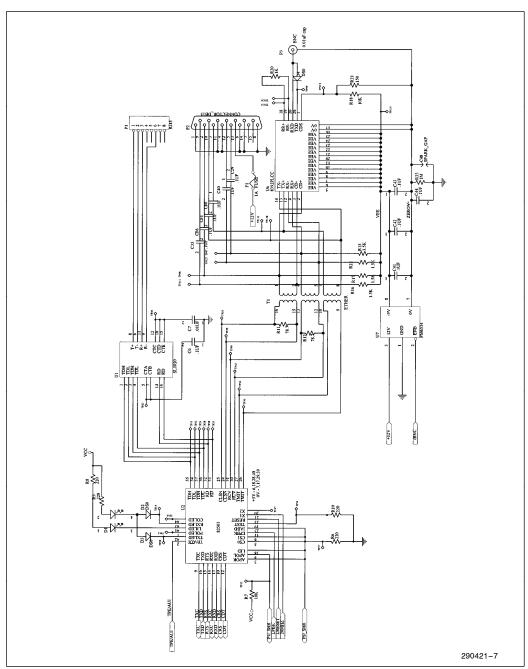

This example is targeted toward interfacing the 82503 to the Intel 82596 in a two-port (TPE/AUI) application.

### 5.2 Design Guidelines

# **AUI Pulse Transformer**

In order to meet the 16V fault tolerance specification of 802.3 a pulse transformer is recommended for the transmit, receive and collision pairs. The transformer should be placed between the TRMT, RCV, and CLSN pairs of the 503, and the DO, DI, and CI pairs respectively, of the AUI (DB-15 connector). The pulse transformer should have a parallel inductance of 75  $\mu\text{H}$  minimum (100  $\mu\text{H}$  recommended).

Several vendors stock such transformers. Two possible vendors are:

- 1. Pulse Engineering (P/N PE-64103)

- 2. Valor Electronics (P/N LT6003)

#### **Terminating Resistors**

The terminating resistors used across the receive and collision pairs are recommended to be 78.7  $\Omega$   $\pm$  1%.

#### **Analog Front-End**

The 82503 provides six TPE pins (TDH, TDH, TDL, TDL, RD, and RD) that connect to the Analog Front End through a resistor summing network (Figure 7). AFE solutions can be made discretely or purchased from several manufacturers. Two different solutions are described in Application Note 356. The example shown here uses a Pulse Engineering AFE package PE65434 which includes EMI filter, isolation transformer, and common mode choke. The output of the AFE connects directly to the 10BASE-T connector (RJ-45).

#### Decoupling

It is recommended that 0.01  $\mu F$  X7R and 0.001  $\mu F$  NPO decoupling capacitors be placed between the V<sub>CCA</sub> and V<sub>CCD</sub> of the 82503 to V<sub>SSA</sub> and V<sub>SSD</sub>.

#### **Clock Generation**

The clock input to the 82503 can be from a clock oscillator or a crystal. If a clock oscillator is used, X1 should be driven, and X2 left floating. If a crystal oscillator is used, refer to Section 3.1 for crystal specifications.

A complete 82596/82503 TPE/AUI Ethernet Solution is shown at the end of this section.

### 5.3 Layout Guidelines

#### General

The analog section, as well as, the entire board itself should conform to good high-frequency practices and standards to minimize switching transients and parasitic interaction between various circuits. To achieve this, the following guidelines are presented.

Figure 8. Application Example Schematic

Make power supply and ground traces as thick as possible. This will reduce high-frequency cross coupling caused by the inductance of thin traces.

Connect logic and chassis ground together.

Separate and decouple all of the analog and digital power supply lines.

Close signal paths to ground as close as possible to their sources to avoid ground loops and noise cross coupling.

Use high-loss magnetic beads on power supply distribution lines.

#### Crystal

The crystal should be adjacent to the 82503 and trace lengths should be as short as possible. The X1 and X2 traces should be symmetrical.

#### 82503 Analog Differential Signals

The differential signals from the 82503 to the transformers, analog front end, and the connectors should be symmetrical for each pair and as short as possible. Differential signal layout should be performed to a characteristic impedance of  $78\Omega$  (for AUI) or  $100\Omega$  (for TPE).

As a general rule, the trace widths should be one to three times the distance between the PCB layers to eliminate excessive trace inductance.

The differential signals should also be isolated from the high speed logic signals on the same layer as well as on any sublayers of the PCB.

Group each of the circuits together, but keep them separate from each other. Separate their grounds.

In layout, the circuitry from the connectors to the filter network, should have the ground plane removed from beneath it. This will prevent ground noise from being induced into the analog front end.

All trace bends should not exceed 45 degrees.

# 6.0 PACKAGE THERMAL SPECIFICATIONS

The 82503 Dual Serial Transceiver is specified for operation when case temperature ( $T_{\rm C}$ ) is within the range of 0°C to  $+85^{\circ}$ C. The case temperature can be measured in any environment, to determine if the 82503 is within the specified operating range. The case temperature should be measured at the center of the top surface opposite the pins.

The acceptable operating ambient temperature (T<sub>A</sub>) is guaranteed as long as T<sub>C</sub> is not violated. The ambient temperature can be calculated from the  $\theta_{ja}$  and  $\theta_{ic}$  from the following equations:

$$\begin{split} T_{J} &= T_{C} + P \times \theta_{jc} \\ T_{J} &= T_{A} + P \times \theta_{ja} \\ T_{A} &= T_{C} - P \times (\theta_{ja} - \theta_{jc}) \end{split}$$

Values for  $\theta_{ja}$  and  $\theta_{jc}$  are given in Table 4 for the 44-lead PLCC and 44-lead QFP packages. Various values for  $\theta_{ja}$  at different airflows. Table 5 shows the maximum  $T_A$  allowable (without exceeding  $T_C$ ) at various airflows.

Table 4. Thermal Resistance (°C/Watt)  $\theta_{ic}$  and  $\theta_{ja}$

|                 |             |          | $	heta_{ m ja}$ vs Airflow—ft/min (m/s |               |               |               |                |

|-----------------|-------------|----------|----------------------------------------|---------------|---------------|---------------|----------------|

| Package         | $\theta$ jc | 0<br>(0) | 200<br>(1.01)                          | 400<br>(2.03) | 600<br>(3.04) | 800<br>(4.06) | 1000<br>(5.07) |

| 44-Lead<br>PLCC | 19          | 57       | 48                                     | 43            | 41            | 39            | 37             |

| 44-Lead<br>QFP  | 26          | 98       | 94                                     | 78            | 70            | 66            | 64             |

Table 5. Maximum T<sub>A</sub> at Various Airflows

|                 |          | $	heta_{	extsf{ja}}$ vs Airflow—ft/min (m/s) |               |               |               |                |  |  |  |  |

|-----------------|----------|----------------------------------------------|---------------|---------------|---------------|----------------|--|--|--|--|

| Package         | 0<br>(0) | 200<br>(1.01)                                | 400<br>(2.03) | 600<br>(3.04) | 800<br>(4.06) | 1000<br>(5.07) |  |  |  |  |

| 44-Lead<br>PLCC | 66       | 71                                           | 73            | 74            | 75            | 76             |  |  |  |  |

| 44-Lead<br>QFP  | 49       | 51                                           | 59            | 63            | 65            | 66             |  |  |  |  |

### 7.0 ELECTRICAL SPECIFICATIONS **AND TIMINGS**

### **ABSOLUTE MAXIMUM RATINGS**

Case Temperature Under Bias . . . . . . 0°C to +85°C Storage Temperature .....-65°C to +140°C All Output and Supply Voltages  $\ldots -0.5V$  to +7VAll Input Voltages  $\dots -1.0V$  to +6.0V<sup>(1)</sup>

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

# **DC CHARACTERISTICS** ( $T_C = 0$ °C to +85°C, $V_{CC} = 5V \pm 5$ %, $V_{CCA} = 5V \pm 5$ %)

| Symbol                                 | Parameter                                                                                                           | Min                 | Max                              | Units                                              | Test Conditions                          |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------|----------------------------------------------------|------------------------------------------|

| V <sub>IL</sub> (TTL) <sup>(2)</sup>   | Input Low Voltage                                                                                                   | -0.3                | 0.8                              | ٧                                                  |                                          |

| V <sub>IH</sub> (TTL) <sup>(2)</sup>   | Input High Voltage                                                                                                  | 2.0                 | V <sub>CC</sub>                  | ٧                                                  |                                          |

| I <sub>LI</sub> (2)                    | Input Leakage Current                                                                                               |                     | ±10                              | μΑ                                                 | $0.0V \le V_I \le V_{CC}$ , RESET = 1    |

| V <sub>OL</sub> (MOS) <sup>(3)</sup>   | Output Low Voltage                                                                                                  |                     | 0.45                             | ٧                                                  | $I_{OL} = 4 \text{ mA}$                  |

| V <sub>OH</sub> (MOS)                  | Output High Voltage                                                                                                 | 3.9                 |                                  | ٧                                                  | $I_{OH} = -500 \mu A$                    |

| V <sub>OL</sub> (LED) <sup>(4)</sup>   | Output Low Voltage                                                                                                  |                     | 0.45                             | ٧                                                  | $I_{OL} = 10 \text{ mA}$                 |

| V <sub>OH</sub> (LED)                  | Output High Voltage                                                                                                 | 3.9                 |                                  | ٧                                                  | $I_{OH}=-500~\mu A$                      |

| I <sub>LP</sub>                        | Leakage Current, Low<br>Power Mode <sup>(5)</sup>                                                                   |                     | ± 10                             | μΑ                                                 | $0.0V \leq V_I \leq V_{CC}$              |

| R <sub>DIFF</sub>                      | Input Differential Resistance(6)                                                                                    | 10                  |                                  | kΩ                                                 | dc                                       |

| V <sub>IDF</sub> (TPE) <sup>(7)</sup>  | Input Differential Accept Input Differential Reject Input Differential Accept (XSQ) Input Differential Reject (XSQ) | ± 0.500<br>(Note 8) | ±3.1<br>±0.300<br>±3.1<br>±0.180 | V <sub>P</sub><br>V <sub>P</sub><br>V <sub>P</sub> | $5 \text{ MHz} \le f \le 10 \text{ MHz}$ |

| R <sub>S</sub> (TPE) <sup>(8)</sup>    | Output Source Resistance                                                                                            | 6                   | 13                               | Ω                                                  | $ I_{LOAD}  = 25 \text{ mA}$             |

| V <sub>IDF</sub> (AUI) <sup>(9)</sup>  | Input Differential Accept Input Differential Reject                                                                 | ±0.300              | ±1.5<br>±0.160                   | V <sub>P</sub>                                     |                                          |

| V <sub>ODF</sub> (AUI) <sup>(10)</sup> | Output Differential Voltage                                                                                         | ± 0.450             | ±1.20                            | ٧                                                  |                                          |

#### NOTES:

- 1. The voltage levels for RCV, CLSN, and RD pairs are -0.75V to +8.5V.

2. TTL Input Pins: TxD, RTS, TPE/AUI, APORT, APOL/XSQ, LID, CS0, CS1, LPBK, JABD, TEST, RESET.

3. MOS Output Pins: TxC, RxD, RxC, CRS, CDT.

4. LED Pins: TPE/AUI, TxLED, RxLED, COLED, POLED, LILED, V<sub>OL</sub> measured 10 ns after falling edge of TxC.

5. Pins: APORT, APOL/XSQ, LID, TPE/AUI, POLED, LILED, RTS, LPBK, RxD, TxD, CRS, CDT, LABD, TEST, and RESET.

- CDT, CS0, CS1, JABD, TEST, and RESET.

6. Pins: RD to RD, RCV to RCV, and CLSN to CLSN.

- 7. TPE Input Pins: RD, and  $\overline{\text{RD}}$ . See Section 3.3.4 and Section 3.3.5.

- 8. Typically it is  $-4.5 \text{ dB } \underline{\text{below}}$  normal squelch level.

- 9. TPE Output Pins: TDH,  $\overline{\text{TDH}}$ , TDL, and  $\overline{\text{TDL}}$ . R<sub>S</sub> measures V<sub>CC</sub> or V<sub>SS</sub> to Pin.

- 10. AUI Input Pins: RCV, and CLSN pairs.

- 11. AUI Output Pins: TRMT pair.

| DC CHARACTERISTICS | $T_C = 0$ °C to | $+85^{\circ}$ C, $V_{CC} = 5V$ | $/ \pm 5\%$ , $V_{CCA} =$ | = 5V $\pm$ 5%) (Continued) |

|--------------------|-----------------|--------------------------------|---------------------------|----------------------------|

|--------------------|-----------------|--------------------------------|---------------------------|----------------------------|

| Symbol                 | Parameter                                 | Min | Max  | Units | Test Conditions                           |

|------------------------|-------------------------------------------|-----|------|-------|-------------------------------------------|

| I <sub>OSC</sub> (AUI) | AUI Output Short Circuit Current          |     | ±150 | mA    | Short Circuit to V <sub>CC</sub> or GND   |

| V <sub>U</sub> (AUI)   | Output Differential Undershoot            |     | -100 | mV    |                                           |

| V <sub>ODI</sub> (AUI) | Differential Idle Voltage(11)             |     | ±40  | mV    |                                           |

| I <sub>CC</sub> (HOT)  | Power Supply Current <sup>(12)</sup>      |     | 65   | mA    | APORT = 1                                 |

| Icc                    | Power Supply Current                      |     | 75   | mA    | APORT = 1                                 |

| Icc                    | Power Supply Current                      |     | 60   | mA    | APORT = 0                                 |

| I <sub>CCSB</sub>      | Standby Supply Current(13)                |     | 1    | mA    | Low Power Mode, 20 $\mu$ A Typical        |

| PD (HOT)               | Power Dissipation(12)                     |     | 0.38 | W     | APORT = 1, Continuous Transmission on AUI |

| PD                     | Power Dissipation                         |     | 0.40 | W     | APORT = 1, Continuous Transmission on AUI |

| PD <sub>SB</sub>       | Standby Power Dissipation <sup>(13)</sup> |     | 5.25 | mW    | Low Power Mode, 105 μW Typical            |

| C <sub>IN</sub> (14)   | Input Capacitance                         |     | 10   | pF    | at f = 1 MHz                              |

#### NOTES:

- 11. Measured 8.0  $\mu s$  after last positive transition of data packet.

- 12.  $I_{CC}$  HOT measurements made at  $T_{C}=+85^{\circ}$ C. Additionally, TRMT,  $\overline{TRMT}$ , TDH,  $\overline{TDH}$ , TDL,  $\overline{TDL}$  are loaded with 20 pF and load resistors removed.

- 13. Pins CS0 and CS1 connected to  $V_{CC}$  or  $V_{SS}$  through a 2.5 k $\Omega$  (or less) resistor.  $I_{CCSB}$  is typically at 20  $\mu$ A after 30s from power down assertion—not tested.

- 14. Characterized, not tested. (Controller interface and mode pins only.)

# **AC TIMING CHARACTERISTICS**

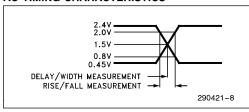

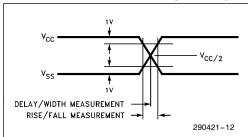

Figure 9. MOS Input Voltage Levels (TTL Compatible) for Timing Measurements (TxD, RTS, TPE/AUI, APORT, APOL/XSQ, LID, LPBK, JABD, TEST, and RESET).

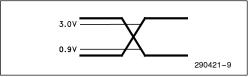

Figure 10. Voltage Levels for MOS Level

Output Timing Measurements

(TxC, RxD, RxC, CRS, and CDT).

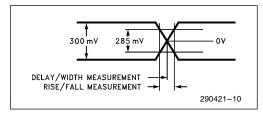

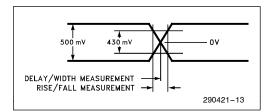

Figure 11. Voltage Levels for Differential Input Timing Measurements (RCV and CLSN Pairs).

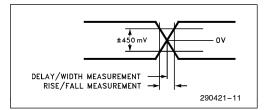

Figure 12. Voltage Levels for TRMT Pair Output Timing Measurements.

### AC TIMING CHARACTERISTICS (Continued)

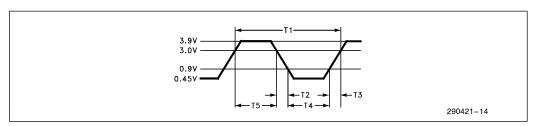

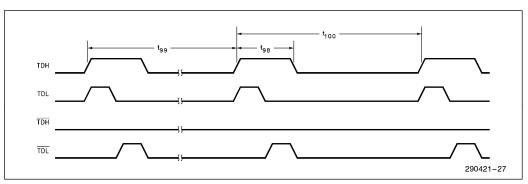

Figure 13. Voltage Levels for TDH, TDL, TDH, and TDL.

Figure 14. Voltage Levels for Differential Input Timing Measurements (RD Pair).

# **AC MEASUREMENT CONDITIONS**

- 1.  $T_C = 0$ °C to +85°C,  $V_{CC} = 5V \pm 5$ %.

- 2. The AC MOS, TTL and differential signals are referred to in Figures, 8, 9, 10, 11, 12, and 13.

- 3. AC loads

- a. MOS: 20 pF total capacitance to ground.

- b. AUI Differential: a 10 pF total capacitance from each terminal to ground and a load resistor of 78 $\Omega$   $\pm$ 1% in parallel with a 27  $\mu$ H  $\pm$ 1% inductor between terminals.

- c. TPE: 20 pF total capacitance to ground.

- 4. All parameters become valid 200  $\mu s$  after the supply voltage and input clock has stabilized, or after RESET deasserts.

### **CLOCK TIMING (15)**

| Symbol         | Parameter     | Min    | Тур | Max    | Units |

|----------------|---------------|--------|-----|--------|-------|

| t <sub>1</sub> | X1 Cycle Time | 49.995 |     | 50.005 | ns    |

| t <sub>2</sub> | X1 Fall Time  |        |     | 5      | ns    |

| t <sub>3</sub> | X1 Rise Time  |        |     | 5      | ns    |

| t <sub>4</sub> | X1 Low Time   | 15     |     |        | ns    |

| t <sub>5</sub> | X1 High Time  | 15     |     |        | ns    |

### NOTE:

15. Refers to External Clock Input.

Figure 15. X1 Input Voltage Levels for Timing Measurements

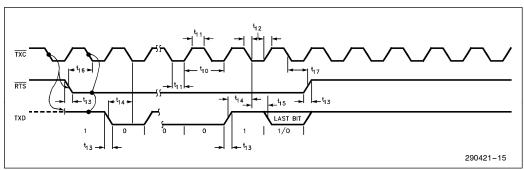

# **Controller Interface Timings (Intel Mode)**

# TRANSMIT TIMINGS (Intel)

| Symbol          | Parameter                  | Min   | Тур | Max    | Units |

|-----------------|----------------------------|-------|-----|--------|-------|

| t <sub>10</sub> | TxC Cycle Time             | 99.99 |     | 100.01 | ns    |

| t <sub>11</sub> | TxC High/Low Time          | 40    |     |        | ns    |

| t <sub>12</sub> | TxC Rise/Fall Time         |       |     | 5      | ns    |

| t <sub>13</sub> | TxD and RTS Rise/Fall Time |       |     | 10     | ns    |

| t <sub>14</sub> | TxD Setup Time to TxC ↓    | 45    |     |        | ns    |

| t <sub>15</sub> | TxD Hold Time from TxC ↓   | 0     |     |        | ns    |

| t <sub>16</sub> | RTS Setup Time to TxC ↓    | 45    |     |        | ns    |

| t <sub>17</sub> | RTS Hold Time from TxC ↓   | 0     |     |        | ns    |

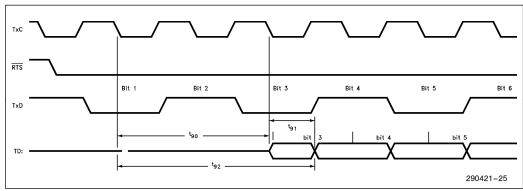

Figure 16. Transmit Timing (Intel)

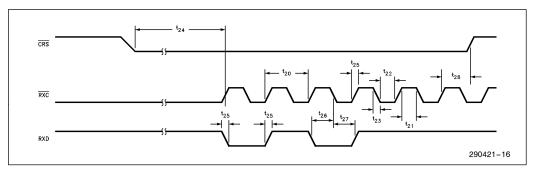

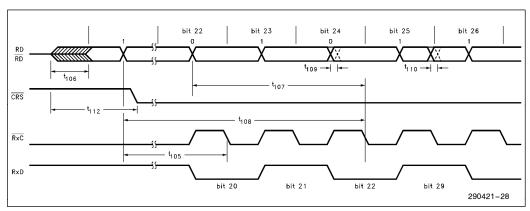

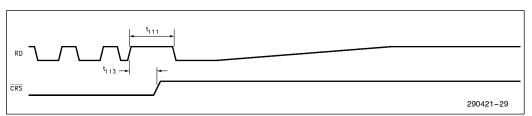

# RECEIVE TIMING (Intel)

| Symbol          | Parameter                               | Min | Тур  | Max  | Units |

|-----------------|-----------------------------------------|-----|------|------|-------|

| t <sub>20</sub> | RxC Cycle Time                          | 96  | 100  |      | ns    |

| t <sub>21</sub> | RxC High Time                           | 36  |      |      | ns    |

| t <sub>22</sub> | RxC Low Time                            | 40  |      |      | ns    |

| t <sub>23</sub> | RxC Rise/Fall Time                      |     |      | 5    | ns    |

| t <sub>24</sub> | RxC Delay from CRS ↓                    |     | 1100 | 1400 | ns    |

| t <sub>25</sub> | RxD Rise/Fall Time                      |     |      | 5    | ns    |

| t <sub>26</sub> | RxD Setup from RxC ↓                    | 30  |      |      | ns    |

| t <sub>27</sub> | RxD Hold from $\overline{\text{RxC}}$ ↓ | 30  |      |      | ns    |

| t <sub>28</sub> | CRS Deassertion Hold Time from RxC High | 10  |      | 40   | ns    |

Figure 17. Receive Timing (Intel)

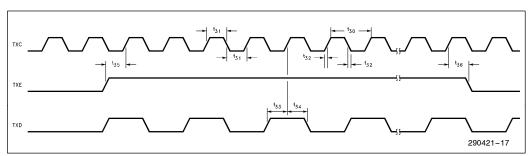

# **Controller Interface Timings (National Mode)**

# TRANSMIT TIMINGS (National)

| Symbol          | Parameter                        | Min   | Тур | Max    | Units |

|-----------------|----------------------------------|-------|-----|--------|-------|

| t <sub>30</sub> | TXC Cycle Time(16)               | 99.99 |     | 100.01 | ns    |

| t <sub>31</sub> | TXC High/Low Time                | 40    | 50  |        | ns    |

| t <sub>32</sub> | TXC Rise/Fall Time at 20% to 80% |       |     | 5      | ns    |

| t <sub>33</sub> | TXD Setup Time to TXC ↑          | 20    |     |        | ns    |

| t <sub>34</sub> | TXD Hold Time from TXC ↑         | 0     |     |        | ns    |

| t <sub>35</sub> | TXE Setup Time to TXC ↑          | 20    |     |        | ns    |

| t <sub>36</sub> | TXE Hold Time from TXC ↑         | 0     |     |        | ns    |

**NOTE:** 16. All delay and width measurements on TxC are made at 1.5V.

Figure 18. Transmit Timing (National)

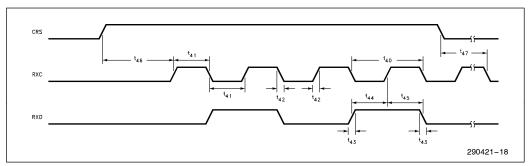

# **RECEIVE TIMINGS** (National)

| Symbol          | Parameter                        | Min | Тур | Max  | Units  |

|-----------------|----------------------------------|-----|-----|------|--------|

| t <sub>40</sub> | RxC Cycle Time                   | 96  | 100 |      | ns     |

| t <sub>41</sub> | RxC High/Low Time(17)            | 40  | 50  | 60   | ns     |

| t <sub>42</sub> | RxC Rise/Fall Time at 20% to 80% |     |     | 5    | ns     |

| t <sub>43</sub> | RXD Rise/Fall Time at 20% to 80% |     |     | 5    | ns     |

| t <sub>44</sub> | RXD Setup Time to RxC ↑          | 30  |     |      | ns     |

| t <sub>45</sub> | RXD Hold Time from RxC ↑         | 20  |     |      | ns     |

| t <sub>46</sub> | RxC Delay from CRS ↑             |     |     | 1400 | ns     |

| t <sub>47</sub> | RxC Continuing Beyond CRS ↓      |     |     | 5    | cycles |

NOTE: 17. All delay and width measurements on RXC are made at 1.5V.

Figure 19. Receiving Timings (National)

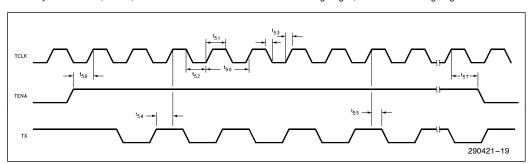

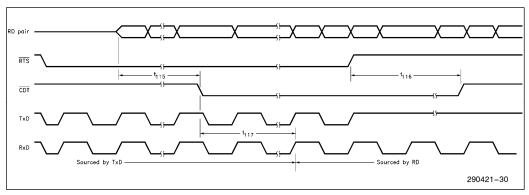

# **Controller Interface Timing (AMD Mode)**

# TRANSMIT TIMINGS(18) (AMD)

| Symbol          | Parameter                            | Min   | Тур | Max    | Units |

|-----------------|--------------------------------------|-------|-----|--------|-------|

| t <sub>50</sub> | TCLK Cycle Time                      | 99.99 |     | 100.01 | ns    |

| t <sub>51</sub> | TCLK High Time (@ 0.8V to 2.0V)      | 45    | 50  | 58     | ns    |

| t <sub>52</sub> | TCLK Low Time (@ 2.0V to 0.8V)       | 45    | 50  | 58     | ns    |

| t <sub>53</sub> | TCLK Rise/Fall Time (@ 0.8V to 2.0V) |       | 2.5 | 5      | ns    |

| t <sub>54</sub> | TX Setup Time to TCLK ↑              | 20    |     |        | ns    |

| t <sub>55</sub> | TX Hold Time from TCLK ↑             | 5     |     |        | ns    |

| t <sub>56</sub> | TENA Setup Time to TCLK ↑            | 20    |     |        | ns    |

| t <sub>57</sub> | TENA Hold Time from TCLK ↑           | 5     |     |        | ns    |

# NOTE:

18. Delay times for TX, TENA, and TCLK are measured from 0.8V for falling edges, and 2.0V for rising edges.

Figure 20. Transmit Timings (AMD)

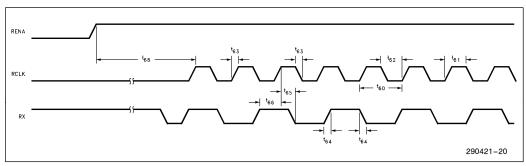

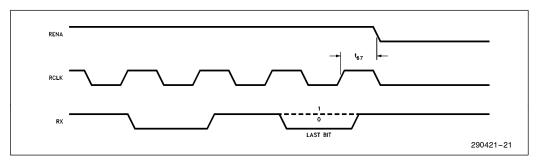

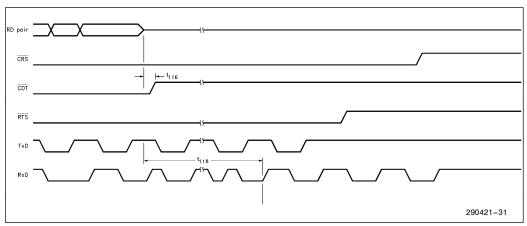

# RECEIVE TIMINGS(19) (AMD)

| Symbol          | Parameter                              | Min | Тур | Max | Units |

|-----------------|----------------------------------------|-----|-----|-----|-------|

| t <sub>60</sub> | RCLK Cycle Time                        | 96  | 100 |     | ns    |

| t <sub>61</sub> | RCLK High Time (@ 0.8V to 2.0V)        | 38  | 50  |     | ns    |

| t <sub>62</sub> | RCLK Low Time (@ 2.0V to 0.8V)         | 38  | 50  |     | ns    |

| t <sub>63</sub> | RCLK Rise/Fall Time (@ 0.8V to 2.0V)   |     | 2.5 | 5   | ns    |

| t <sub>64</sub> | RX Rise/Fall Time (@ 0.8V to 2.0V)     |     | 2.5 | 5   | ns    |

| t <sub>65</sub> | RX Hold time from RCLK ↑               | 10  |     |     | ns    |

| t <sub>66</sub> | RX Setup Time to RCLK ↑                | 45  |     |     | ns    |

| t <sub>67</sub> | RENA Deassertion Hold Time from RCLK ↑ | 40  | 50  | 80  | ns    |

| t <sub>68</sub> | RCLK Delay from RENA ↑                 |     |     | 450 | ns    |

### NOTE:

19. Delay times for RX, RENA, and RCLK are measured from 0.8V for falling edges and 2.0V for rising edges.

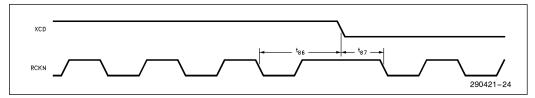

Figure 21. Receive Timings (AMD—Start of Frame)

Figure 22. Receive Timings (AMD—End of Frame)

# **Controller Interface Timings (Fujitsu Mode)**

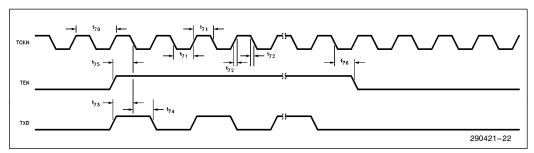

# TRANSMIT TIMINGS (Fujitsu)

| Symbol          | Parameter                          | Min   | Тур | Max    | Units |

|-----------------|------------------------------------|-------|-----|--------|-------|

| t <sub>70</sub> | TCKN Cycle Time                    | 99.99 |     | 100.01 | ns    |

| t <sub>71</sub> | TCKN High/Low Time <sup>(20)</sup> | 40    | 50  |        | ns    |

| t <sub>72</sub> | TCKN Rise/Fall Time at 20% to 80%  |       |     | 5      | ns    |

| t <sub>73</sub> | TXD Setup Time to TCKN ↓ (20)      | 20    |     |        | ns    |

| t <sub>74</sub> | TXD Hold Time from TCKN ↓ (20)     | 0     |     |        | ns    |

| t <sub>75</sub> | TEN Setup Time to TCKN ↓ (20)      | 20    |     |        | ns    |

| t <sub>76</sub> | TEN Hold Time from TCKN ↓ (20)     | 0     |     |        | ns    |

**NOTE:** 20. Timing measurements are referenced at 1.5V level.

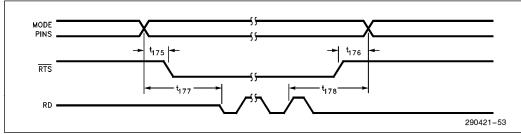

Figure 23. Transmit Timings (Fujitsu)

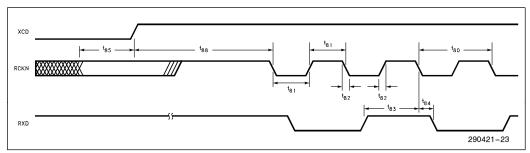

# RECEIVE TIMINGS (Fujitsu)

| Symbol          | Parameter                                   | Min | Тур | Max  | Units |

|-----------------|---------------------------------------------|-----|-----|------|-------|