# 8K x 8 Static RAM

#### Features

- 8K by 8 Static RAM with chip select powerdown, output enable

- □ Auto-Powerdown<sup>™</sup> design

- Advanced CMOS technology

- High speed to 20 ns worst case

- Low Power Operation Active: 290 mW typical at 45 ns Standby: 50 μW typical

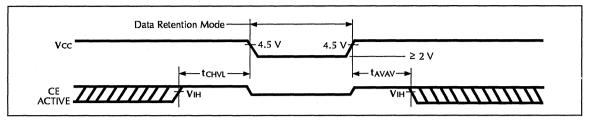

- Data retention at 2 V for battery backup operation

- Plug-compatible with IDT7164, Cypress CY7C185/186

- Package styles available:

- 28-pin Plastic DIP

- 28-pin Sidebraze, Hermetic DIP

- 28-pin CerDIP

- 28-pin Ceramic LCC

- 28-pin Plastic SOIC (Gull-Wing)

- 28-pinPlastic SOJ (J-Lead)

# Description

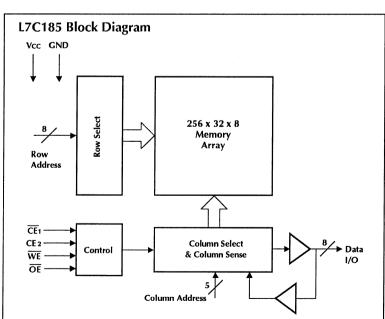

The L7C185 is a high-performance, low-power CMOS static RAM. The storage circuitry is organized as 8,192 words by 8 bits per word. The 8 Data In and Data Out signals share I/O pins. Parts are available in five speeds with worst-case access times from 20 ns to 85 ns.

Inputs and output are TTL compatible. Operation is from a single +5 V power supply. Power consumption is 290 mW (typical) at 45 ns. Dissipation drops to 25 mW (typical) when the memory is deselected (Enable is high).

Two standby modes are available. Proprietary Auto-Powerdown™ circuitry reduces power consumption automatically during read or write accesses which are longer than the minimum access time, or when the memory is deselected. In addition, data may be retained in inactive storage with a supply voltage as low as 2 V. The L7C185 consumes only 3 µW at 2 V (typical), for effective battery back-up operation.

The L7C185 provides asynchronous (unclocked) operation with matching access and cycle times. Two activelow Chip Enables and a three-state I/O bus with a separate output enable simplify the connection of several chips for increased storage capacity.

Memory locations are specified on address pins A0 through A12. Reading from a designated location is accomplished by presenting an address and then taking CE1 low and CE2 high while Write remains high. The data in the addressed memory location will then appear on the Data Out pin within one access time. The output pin stays in a high-impedance state when CE1 is high or CE2 or WE is low.

Writing to an addressed location is accomplished when the active-low  $\overline{CE}_1$  and  $\overline{WE}$  inputs are both low, and CE2 is high. Any of these signals may be used to terminate the write operation. Data In and Data Out signals have the same polarity.

Latchup and static discharge protection are provided on-chip. The L7C185 can withstand an injection current of up to 200 mA on any pin without damage.

LOGIC

DEVICES INCORPORATED

**Memory Products**

# 2

Maximum Ratings Above which useful life may be impaired (Notes 1, 2)

|   | Storage temperature                       | –65°C to +150°C  |

|---|-------------------------------------------|------------------|

| - | Operating ambient temperature             |                  |

|   | VCC supply voltage with respect to ground |                  |

|   | Input signal with respect to ground       | –3.0 V to +7.0 V |

|   | Signal applied to high impedance output   | –3.0 V to +7.0 V |

|   | Output current into low outputs           | 25 mA            |

|   | Latchup current                           | > 200 mA         |

**Operating Conditions** *To meet specified electrical and switching characteristics*

| Mode                         | Temperature Range (Ambient) | Supply Voltage                                             |

|------------------------------|-----------------------------|------------------------------------------------------------|

| Active Operation, Commercial | 0°C to +70°C                | $4.5 \text{ V} \leq \text{V} \text{cc} \leq 5.5 \text{ V}$ |

| Active Operation, Military   | –55℃ to +125℃               | $4.5 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$         |

| Data Retention, Commercial   | 0°C to +70°C                | $2.0 \text{ V} \le \text{Vcc} \le 5.5 \text{ V}$           |

| Data Retention, Military     | −55°C to +125°C             | $2.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$         |

# **Electrical Characteristics**

**Over Operating Conditions**

| Symbol | Parameter              | Test Condition                                     | Min  | Тур | Max          | Unit |

|--------|------------------------|----------------------------------------------------|------|-----|--------------|------|

| Vон    | Output High Voltage    | IOH = -4.0 mA, VCC = 4.5 V                         | 2.4  |     |              | V    |

| VOL    | Output Low Voltage     | IOL = 8.0 mA                                       |      |     | 0.4          | V    |

| Viн    | Input High Voltage     |                                                    | 2.0  |     | Vcc<br>+ 0.3 | V    |

| VIL    | Input Low Voltage      | Note 3                                             | -3.0 |     | 0.8          | V    |

| lıx    | Input Current          | Ground $\leq$ Vi $\leq$ Vcc                        | _10  |     | +10          | μΑ   |

| loz    | Output Leakage Current | Ground $\leq$ Vo $\leq$ Vcc, $\overline{CE} =$ Vcc | -50  |     | +50          | μΑ   |

| los    | Output Short Current   | Vo = Ground, Vcc = Max, Note 4                     |      |     | -350         | mA   |

| ICC 2  | VCC Current, Inactive  | Notes 5, 7                                         |      | 5.0 | 20           | mA   |

| ICC 3  | VCC Current, Standby   | Note 8                                             |      | 10  | 250          | μA   |

| ICC4   | Vcc Current, DR Mode   | Vcc = 2.0 V, Note 9                                |      | 1.5 | 50           | μΑ   |

| Сі     | Input Capacitance      | Ambient Temp = $25^{\circ}$ C, Vcc = 5.0 V         |      |     | 5            | рF   |

| Co     | Output Capacitance     | Test Frequency = 1 MHz, Note 10                    |      |     | 7            | pF   |

|        |                     |                |    | L7C185- |     |     |     |    |      |

|--------|---------------------|----------------|----|---------|-----|-----|-----|----|------|

| Symbol | Parameter           | Test Condition | 85 | 45      | 35  | 25  | 20  | 15 | Unit |

| ICC1   | Vcc Current, Active | Notes 5, 6     | 45 | 80      | 100 | 140 | 180 |    | mA   |

2

# Switching Characteristics

Over Operating Range (ns)

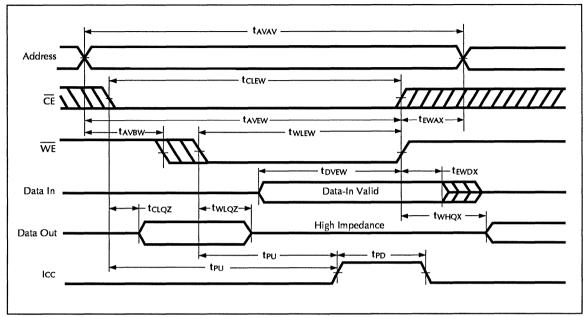

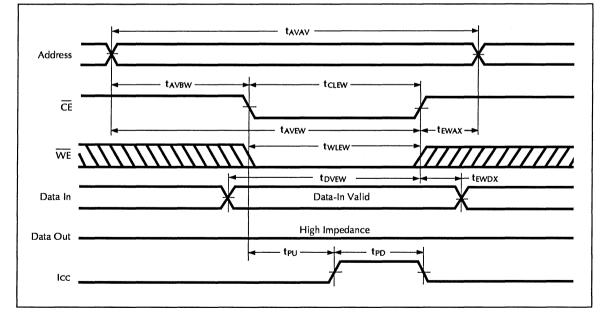

### Read Cycle (Notes 11, 12, 21, 22, 23, 24)

|               | L7C185-                                        |     |     |     |     |     |     |     |     |     |     |      |      |

|---------------|------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

|               |                                                |     | 85  |     | 45  |     | 35  |     | 25  |     | 20  |      | 5    |

| Symbol        | Parameter                                      | Min | Max | Min  | Max  |

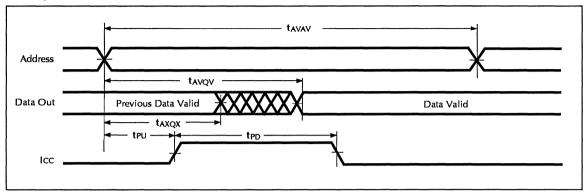

| <b>t</b> avav | Read Cycle Time                                | 85  |     | 45  |     | 35  |     | 25  |     | 20  |     | 15   |      |

| tavqv         | Addr Valid to Output Valid (13, 14)            |     | 85  |     | 45  |     | 35  |     | 25  |     | 20  | 22   |      |

| taxqx         | Addr Change to Output Change                   | 5   |     | 5   |     | 5   |     | 5   |     | 5   |     | 3    |      |

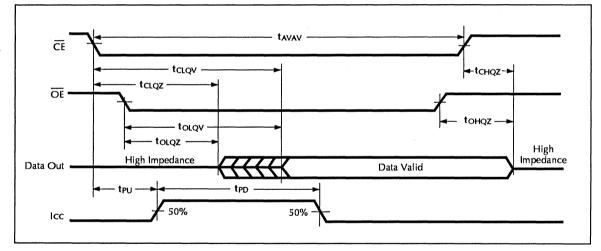

| <b>t</b> CLQV | Chip Enable Active to Output Valid (13, 15)    |     | 85  |     | 30  |     | 25  |     | 25  |     | 20  |      | 15   |

| <b>t</b> CLQZ | Chip Enable Active to Output Low Z (20, 21)    | 5   |     | 5   |     | 5   |     | 5   |     | 5   |     | 5    |      |

| <b>t</b> CHQZ | Chip Enable Inactive to Output High Z (20, 21) |     | 35  |     | 15  |     | 15  |     | 10  |     | 8   | ***  | 8    |

| tOLQV         | Output Enable Low to Output Valid              |     | 35  |     | 20  |     | 15  |     | 12  |     | 10  | 2000 | 8    |

| tolqz         | Output Enable Low to Output Low Z (20, 21)     | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | 3    |      |

| tonqz         | Output Enable High to Output High Z (20, 21)   |     | 30  |     | 15  |     | 12  |     | 10  |     | 8   |      | 8    |

| t₽U           | CE Active or WE Low to Power Up (10, 19)       | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0    | ise. |

| tPD           | Power Up to Power Down (10, 19)                |     | 85  |     | 45  |     | 35  |     | 25  |     | 20  |      | 20   |

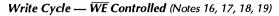

## Write Cycle (Notes 11, 12, 22, 23, 24)

|               |                                             | L7C185- |     |     |     |     |     |     |     |     |     |                 |              |

|---------------|---------------------------------------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------------|--------------|

|               |                                             | 8       | 5   | 4   | 5   | 3.  | 5   | 2   | 5   | 20  | 0   | 1               | 5            |

| Symbol        | Parameter                                   | Min     | Max | Min | Max | Min | Max | Min | Max | Min | Max | Min             | Max          |

| tavav         | Write Cycle Time                            | 75      |     | 40  |     | 25  |     | 20  |     | 20  |     | 15              |              |

| <b>t</b> CLEW | Chip Enable Active to End of Write Cycle    | 65      |     | 30  |     | 25  |     | 20  |     | 17  |     | 12 <sup>%</sup> |              |

| ta∨bw         | Address Valid to Beginning of Write Cycle   | 0       |     | 0   |     | 0   |     | 0   |     | 0   |     | 0               |              |

| <b>t</b> avew | Address Valid to End of Write Cycle         | 65      |     | 30  |     | 25  |     | 20  |     | 17  |     | 12              |              |

| <b>t</b> EWAX | End of Write Cycle to Address Change        | 0       |     | 0   |     | 0   |     | 0   |     | 0   |     | 0 🐇             | 0000<br>0000 |

| <b>t</b> WLEW | Write Enable Low to End of Write Cycle      | 45      |     | 30  |     | 20  |     | 20  |     | 17  |     | 12              |              |

| <b>t</b> DVEW | Data Valid to End of Write Cycle            | 35      |     | 15  |     | 15  |     | 15  |     | 13  |     | 10              |              |

| tewdx         | End of Write Cycle to Data Change           | 0       |     | 0   |     | 0   |     | 0   |     | 0   |     | 0               |              |

| twhqz         | Write Enable High to Output Low Z (20, 21)  | 5       |     | 5   |     | 5   |     | 5   |     | 5   |     | 5               |              |

| twlqz         | Write Enable Low to Output High Z (20, 21)  |         | 35  |     | 15  |     | 10  |     | 7   |     | 7   |                 | -7           |

| <b>t</b> CHVL | Chip Enable Inactive to Data Retention (10) | 0       |     | 0   |     | 0   |     | 0   |     | 0   |     | 0               |              |

# **Switching Waveforms**

### Read Cycle — Address Controlled (Notes 13, 14)

Read Cycle — CE/OE Controlled (Notes 13, 15)

2

Write Cycle — CE Controlled (Notes 16, 17, 18, 19)

# 8K x 8 Static RAM

#### Data Retention

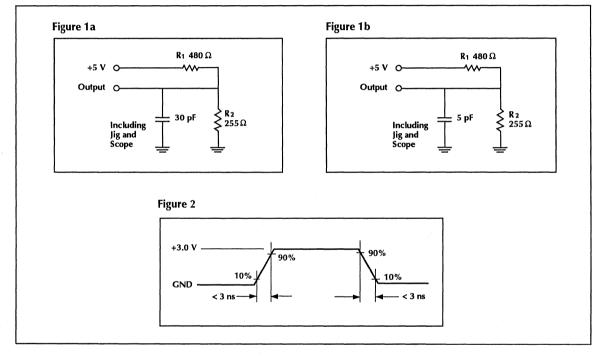

#### **Test Loads and Transition Times**

#### Notes

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability of the tested device.

2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

3. This product provides hard clamping of transient undershoot. Input levels below ground will be clamped beginning at -0.6 V. A current in excess of 100 mA is required to reach -2 V. The device can withstand indefinite operation with inputs as low as -3 V subject only to power dissipation and bond wire fusing constraints.

4. Duration of the output short circuit should not exceed 30 seconds.

5. 'Typical' supply current values are not shown but may be approximated. At a VCC of 5.0 V, an ambient temperature of +25°C and with nominal manufacturing parameters, the operating supply currents will be approximately 3/4 or less of the maximum values shown.

6. Tested with outputs open and all address and data inputs changing at the maximum read cycle rate. The device is continuously enabled for reading, i.e.,  $\overline{CE} \leq \text{VIL}$ ,  $\overline{WE} \geq \text{VIH}$ .

7. Tested with outputs open and all address and data inputs changing at the maximum read cycle rate. The device is continuously disabled, i.e.,  $\overline{CE} \ge VIH$ .

8. Tested with outputs open and all address and data inputs stable. The

DEVICES INCORPORATED

device is continuously disabled, i.e.,  $\overline{\text{CE}}$  = VCC. Input levels are within 0.5 V of VCC or ground.

9. Data retention operation requires that VCC never drop below 2.0 V.  $\overline{CE}$ must be  $\geq$  VCC - 0.3 V. For all other inputs VIN  $\geq$  VCC - 0.3 or VIN  $\leq$  0.3 V is required to ensure full power down.

10. These parameters are guaranteed but not 100% tested.

11. Test conditions assume input transition times of less than 3 ns, reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and output loading for specified IOL and IOH plus 30 pF.

12. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. tAVEW, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Access time, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

13.  $\overline{\text{WE}}$  is high for the read cycle.

14. The chip is continuously selected  $(\overline{CE} \text{ low})$ .

15. All address lines are valid priorto or coincident-with the  $\overrightarrow{CE}$  transition to low.

16. The internal write cycle of the memory is defined by the overlap of  $\overline{CE}$  low and  $\overline{WE}$  low. Both signals must be low to initiate a write. Either signal can terminate a write by going high. The address, data, and control input setup and hold times should be referenced to the signal that falls last or rises first.

17. If  $\overline{WE}$  goes low before or concurrent with  $\overline{CE}$  going low, the output remains in a high impedance state. 18. If  $\overline{CE}$  goes high before or concurrent with  $\overline{WE}$  going high, the output remains in a high impedance state.

19. Powerup from ICC2 to ICC1 occurs as a result of any of the following conditions:

- **a**. Falling edge of  $\overline{CE}$

- b. Falling edge of  $\overline{WE}$  ( $\overline{CE}$  active)

- c. Transition on any address line (CE active)

- d. Transition on any data line ( $\overline{CE}$  and  $\overline{WE}$  active)

The device automatically powers down from ICC1 to ICC2 after tPD has elapsed from any of the prior conditions. This means that power dissipation is dependent on only cycle rate, and is not on Chip Select pulse width.

20. At any given temperature and voltage condition, output disable time is less than output enable time for any given device.

21. Transition is measured  $\pm 200 \text{ mV}$ from steady state voltage with specified loading in Figure 1b. This parameter is sampled and not 100% tested.

22. All address timings are referenced from the last valid address line to the first transitioning address line.

23.  $\overline{CE}$  or  $\overline{WE}$  must be high during address transitions.

24. This product is a very high speed device and care must be taken during testing in order to realize valid test information. Inadequate attention to setups and procedures can cause a good part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the VCC and ground planes directly up to the contactor fingers. A 0.01  $\mu$ F high frequency capacitor is also required between VCC and ground. To avoid signal reflections, proper terminations must be used.

= Memory Products

# **Ordering Information**

#### Commercial Operating Range (0°C to +70°C)

|                                               | Performance |            |            |            |            |                                                                                                                |  |  |  |

|-----------------------------------------------|-------------|------------|------------|------------|------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| Package Style                                 | 85 ns       | 45 ns      | 35 ns      | 25 ns      | 20 ns      | 15 ns                                                                                                          |  |  |  |

| 28-pin Plastic DIP<br>(0.3") — P10            | L7C185PC85  | L7C185PC45 | L7C185PC35 | L7C185PC25 | L7C185PC20 |                                                                                                                |  |  |  |

| 28-pin Plastic DIP<br>(0.6") — P9             | L7C185NC85  | L7C185NC45 | L7C185NC35 | L7C185NC25 | L7C185NC20 |                                                                                                                |  |  |  |

| 28-pin SOIC U2 (0.300")                       | L7C185UC85  | L7C185UC45 | L7C185UC35 | L7C185UC25 | L7C185UC20 |                                                                                                                |  |  |  |

| 28-pin SOIC V2 (0.331")                       | L7C185VC85  | L7C185VC45 | L7C185VC35 | L7C185VC25 | L7C185VC20 |                                                                                                                |  |  |  |

| 28-pin SOJ — W2                               | L7C185WC85  | L7C185WC45 | L7C185WC35 | L7C185WC25 | L7C185WC20 | An an an an Anna an Anna an Anna an Anna an Anna A |  |  |  |

| 28-pin Sidebraze (0.3")<br>Hermetic DIP — D10 | L7C185DC85  | L7C185DC45 | L7C185DC35 | L7C185DC25 | L7C185DC20 |                                                                                                                |  |  |  |

| 28-pin Sidebraze (0.6")<br>Hermetic DIP — D9  | L7C185HC85  | L7C185HC45 | L7C185HC35 | L7C185HC25 | L7C185HC20 |                                                                                                                |  |  |  |

| 28-pin CerDIP (0.3") C5                       | L7C185CC85  | L7C185CC45 | L7C185CC35 | L7C185CC25 | L7C185CC20 |                                                                                                                |  |  |  |

| 28-pin CerDIP (0.6") C6                       | L7C185IC85  | L7C185IC45 | L7C185IC35 | L7C185IC25 | L7C185IC20 |                                                                                                                |  |  |  |

| 28-pin Ceramic LCC — K5                       | L7C185KC85  | L7C185KC45 | L7C185KC35 | L7C185KC25 | L7C185KC20 |                                                                                                                |  |  |  |

# Military Operating Range (-55°C to +125°C)

|                                               | Performance                              |                                          |                                          |                                          |       |  |  |  |  |

|-----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-------|--|--|--|--|

| Package Style                                 | 85 ns                                    | 45 ns                                    | 35 ns                                    | 25 ns                                    | 20 ns |  |  |  |  |

| 28-pin Sidebraze (0.3")<br>Hermetic DIP — D10 | L7C185DM85<br>L7C185DME85<br>L7C185DMB85 | L7C185DM45<br>L7C185DME45<br>L7C185DMB45 | L7C185DM35<br>L7C185DME35<br>L7C185DMB35 | L7C185DM25<br>L7C185DME25<br>L7C185DMB25 |       |  |  |  |  |

| 28-pin Sidebraze (0.6")<br>Hermetic DIP — D9  | L7C185HM85<br>L7C185HME85<br>L7C185HMB85 | L7C185HM45<br>L7C185HME45<br>L7C185HMB45 | L7C185HM35<br>L7C185HME35<br>L7C185HMB35 | L7C185HM25<br>L7C185HME25<br>L7C185HMB25 |       |  |  |  |  |

| 28-pin CerDIP (0.3") — C5                     | L7C185CM85<br>L7C185CME85<br>L7C185CMB85 | L7C185CM45<br>L7C185CME45<br>L7C185CMB45 | L7C185CM35<br>L7C185CME35<br>L7C185CMB35 | L7C185CM25<br>L7C185CME25<br>L7C185CMB25 |       |  |  |  |  |

| 28-pin CerDIP (0.6") — C6                     | L7C185IM85<br>L7C185IME85<br>L7C185IME85 | L7C185IM45<br>L7C185IME45<br>L7C185IMB45 | L7C185IM35<br>L7C185IME35<br>L7C185IMB35 | L7C185IM25<br>L7C185IME25<br>L7C185IMB25 |       |  |  |  |  |

| 28-pin Ceramic LCC — K5                       | L7C185KM85<br>L7C185KME85<br>L7C185KMB85 | L7C185KM45<br>L7C185KME45<br>L7C185KMB45 | L7C185KM35<br>L7C185KME35<br>L7C185KMB35 | L7C185KM25<br>L7C185KME25<br>L7C185KMB25 |       |  |  |  |  |

| Pin | Function | Pin | Function |

|-----|----------|-----|----------|

| 1   | NC       | 15  | l3/O3    |

| 2   | A12      | 16  | 14/04    |

| 3   | A7       | 17  | l5/O5    |

| 4   | A6       | 18  | l6/O6    |

| 5   | A5       | 19  | 17/07    |

| 6   | A4       | 20  | CE1      |

| 7   | A3       | 21  | A10      |

| 8   | A2       | 22  | ŌĒ       |

| 9   | A1       | 23  | A11      |

| 10  | Ao       | 24  | A9       |

| 11  | lo/Oo    | 25  | A8       |

| 12  | l1/O1    | 26  | CE2      |

| 13  | l2/O2    | 27  | WE       |

| 14  | GND      | 28  | Vcc      |

#### **Pin Assignments** (*P9, P10, D9, D10, C5, C6, U2, W2*)

Pin Assignments (K5)

| Pin | Function | Pin | Function |

|-----|----------|-----|----------|

| 1   | A12      | 15  | l3/O3    |

| 2   | A7       | 16  | l4/O4    |

| 3   | A6       | 17  | 15/O5    |

| 4   | NC       | 18  | 16/O6    |

| 5   | A5       | 19  | I7/O7    |

| 6   | A4       | 20  | CE1      |

| 7   | A3       | 21  | A10      |

| 8   | A2       | 22  | ŌĒ       |

| 9   | A1       | 23  | A11      |

| 10  | Ao       | 24  | A9       |

| 11  | lo/Oo    | 25  | A8       |

| 12  | l1/O1    | 26  | CE2      |

| 13  | l2/O2    | 27  | WE       |

| 14  | GND      | 28  | Vcc      |

4

© 1988, Logic Devices Incorporated. Reproduction of any portion hereof without written consent is prohibited. Information contained in this specification is intended as a general product description and is subject to change without notice. Logic Devices does not assume any responsibility for use of any product or circuit described and no patent license rights are implied.

628 East Evelyn Avenue • Sunnyvale, CA 94086 • Telephone 408-720-8630 • FAX 408-733-7690

DEVICES INCORPORATED

= Memory Products