**QUAD EIA-422 LINE DRIVER**

WITH THREE-STATE

# Quad Line Driver with Three-State Outputs

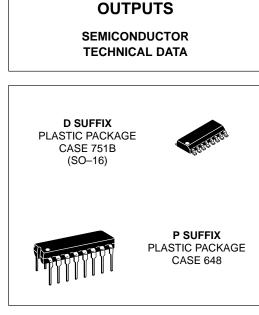

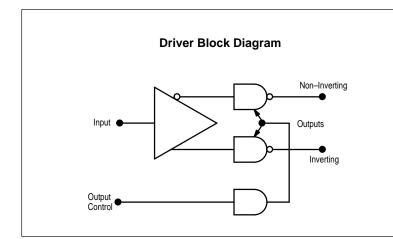

Motorola's Quad EIA–422 Driver features four independent driver chains which comply with EIA Standards for the Electrical Characteristics of Balanced Voltage Digital Interface Circuits. The outputs are three–state structures which are forced to a high impedance state when the appropriate output control pin reaches a logic zero condition. All input pins are PNP buffered to minimize input loading for either logic one or logic zero inputs. In addition, internal circuitry assures a high impedance output state during the transition between power up and power down. A summary of MC3487 features include:

- Four Independent Driver Chains

- Three–State Outputs

- PNP High Impedance Inputs (PIA Compatible)

- Fast Propagation Times (Typical 15 ns)

- TTL Compatible

- Single 5.0 V Supply Voltage

- Output Rise and Fall Times Less Than 20 ns

- DS 3487 Provides Second Source

#### **TRUTH TABLE**

| Input | Control Input | Non-Inverting Output | Inverting Output |

|-------|---------------|----------------------|------------------|

| н     | Н             | н                    | L                |

| L     | Н             | L                    | Н                |

| Х     | L             | Z                    | Z                |

L = Low Logic State

H = High Logic State

X = Irrelevant

Z = Third–State (High Impedance)

# ORDERING INFORMATION

| Device  | Operating<br>Temperature Range | Package     |

|---------|--------------------------------|-------------|

| MC3487P | T <sub>A</sub> = 0 to +70°C    | Plastic DIP |

| MC3487D | IA = 0 10 +70 C                | SO-16       |

### MAXIMUM RATINGS

| Rating                               | Symbol           | Value       | Unit |

|--------------------------------------|------------------|-------------|------|

| Power Supply Voltage                 | VCC              | 8.0         | Vdc  |

| Input Voltage                        | VI               | 5.5         | Vdc  |

| Operating Ambient Temperature Range  | TA               | 0 to +70    | °C   |

| Operating Junction Temperature Range | Тј               | 150         | °C   |

| Storage Temperature Range            | T <sub>stg</sub> | -65 to +150 | °C   |

**ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, specifications apply 4.75 V  $\leq$  V<sub>CC</sub>  $\leq$  5.25 V and 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C. Typical values measured at V<sub>CC</sub> = 5.0 V, and T<sub>A</sub> = 25°C.)

| Characteristic                                                                                                                                                                                                                                                         | Symbol                            | Min  | Тур | Max            | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|-----|----------------|------|

| Input Voltage – Low Logic State                                                                                                                                                                                                                                        | VIL                               | _    | -   | 0.8            | Vdc  |

| Input Voltage – High Logic State                                                                                                                                                                                                                                       | VIH                               | 2.0  | -   | -              | Vdc  |

| Input Current – Low Logic State<br>(V <sub>IL</sub> = 0.5 V)                                                                                                                                                                                                           | ΙL                                | _    | _   | - 400          | μΑ   |

| Input Current – High Logic State<br>$(V_{IH} = 2.7 V)$<br>$(V_{IH} = 5.5 V)$                                                                                                                                                                                           | lΗ                                |      |     | + 50<br>+ 100  | μA   |

| Input Clamp Voltage<br>(I <sub>IK</sub> = -18 mA)                                                                                                                                                                                                                      | VIK                               | -    | _   | - 1.5          | V    |

| Output Voltage – Low Logic State<br>(I <sub>OL</sub> = 48 mA)                                                                                                                                                                                                          | VOL                               | _    | -   | 0.5            | V    |

| Output Voltage – High Logic State<br>(I <sub>OH</sub> = -20 mA)                                                                                                                                                                                                        | VOH                               | 2.5  | _   | -              | V    |

| Output Short–Circuit Current<br>(VIH = 2.0 V, Note 1)                                                                                                                                                                                                                  | los                               | - 40 | _   | - 140          | mA   |

| $\begin{array}{l} \text{Output Leakage Current} - \text{Hi-Z State} \\ (\text{V}_{\text{IL}} = 0.5 \text{ V}, \text{ V}_{\text{IL}}(\text{Z}) = 0.8 \text{ V}) \\ (\text{V}_{\text{IH}} = 2.7 \text{ V}, \text{ V}_{\text{IL}}(\text{Z}) = 0.8 \text{ V}) \end{array}$ | IOL(Z)                            |      |     | ± 100<br>± 100 | μA   |

| Output Leakage Current – Power OFF<br>$(V_{OH} = 6.0 \text{ V}, V_{CC} = 0 \text{ V})$<br>$(V_{OL} = -0.25 \text{ V}, V_{CC} = 0 \text{ V})$                                                                                                                           | IOL(off)                          |      |     | + 100<br>- 100 | μΑ   |

| Output Offset Voltage Difference (Note 2)                                                                                                                                                                                                                              | V <sub>OS</sub> - V <sub>OS</sub> | _    | -   | ± 0.4          | V    |

| Output Differential Voltage (Note 2)                                                                                                                                                                                                                                   | V <sub>OD</sub>                   | 2.0  | -   | -              | V    |

| Output Differential Voltage Difference (Note 2)                                                                                                                                                                                                                        | ∆V <sub>OD</sub>                  | _    | -   | ± 0.4          | V    |

| Power Supply Current<br>(Control Pins = Gnd, Note 3)<br>(Control Pins = 2.0 V)                                                                                                                                                                                         | ICCX<br>ICC                       | -    |     | 105<br>85      | mA   |

NOTES: 1. Only one output may be shorted at a time. 2. See EIA Specification EIA–422 for exact test conditions. 3. Circuit in three–state condition.

| Characteristic                                                                                                                                                                                                          | Symbol                                                                                   | Min              | Тур              | Max                  | Unit |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|------------------|----------------------|------|--|

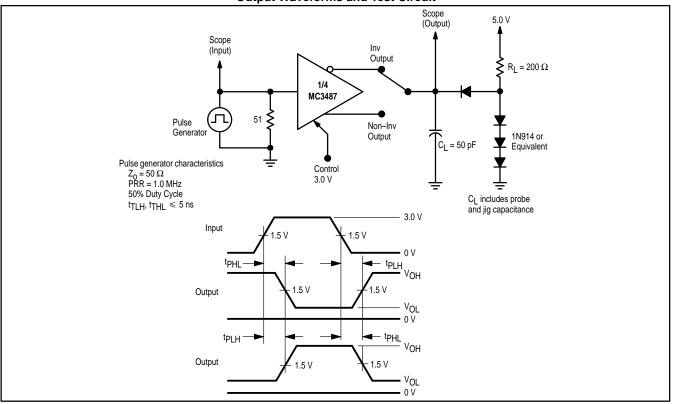

| Propagation Delay Times<br>High to Low Output<br>Low to High Output                                                                                                                                                     | <sup>t</sup> PHL<br><sup>t</sup> PLH                                                     |                  |                  | 20<br>20             | ns   |  |

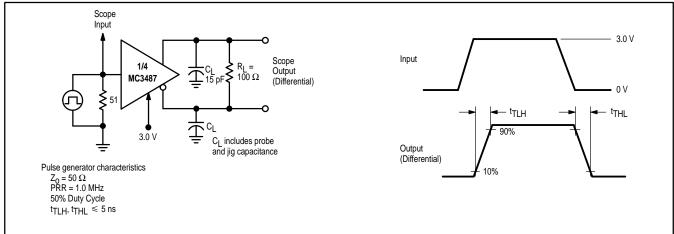

| Output Transition Times – Differential<br>High to Low Output<br>Low to High Output                                                                                                                                      | ↓<br>тн∟<br>тг⊥н                                                                         | -<br>-           |                  | 20<br>20             | ns   |  |

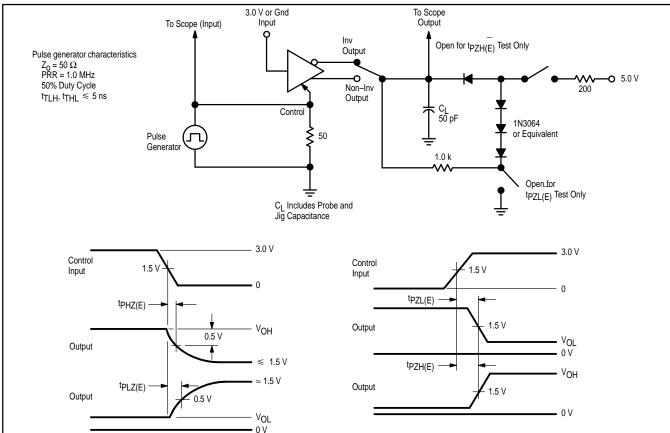

| Propagation Delay – Control to Output<br>( $R_L = 200 \ \Omega$ , $C_L = 50 \ pF$ )<br>( $R_L = 200 \ \Omega$ , $C_L = 50 \ pF$ )<br>( $R_L = \infty$ , $C_L = 50 \ pF$ )<br>( $R_L = 200 \ \Omega$ , $C_L = 50 \ pF$ ) | <sup>t</sup> PHZ(E)<br><sup>t</sup> PLZ(E)<br><sup>t</sup> PZH(E)<br><sup>t</sup> PZL(E) | -<br>-<br>-<br>- | -<br>-<br>-<br>- | 25<br>25<br>30<br>30 | ns   |  |

Figure 1. Three–State Enable Test Circuit and Waveforms

#### Figure 2. Propagation Delay Times Input to Output Waveforms and Test Circuit

### Figure 3. Output Transition Times Test Circuit and Waveforms

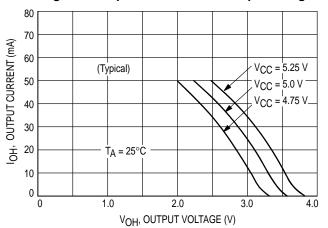

Figure 4. Output Current versus Output Voltage

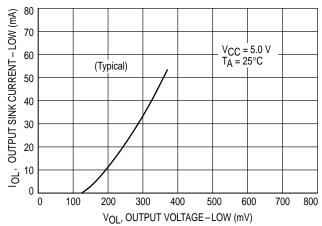

Figure 5. Output Sink Current versus Output Voltage

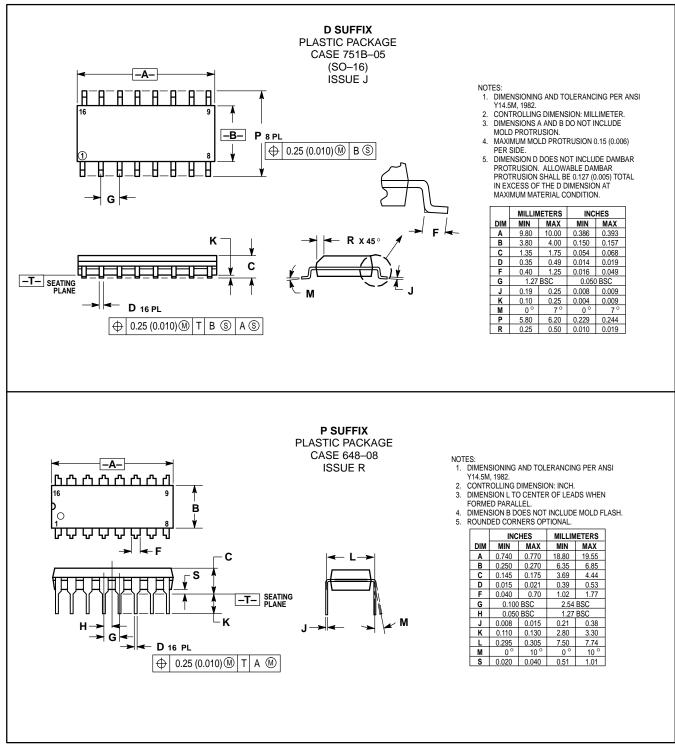

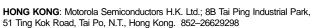

## OUTLINE DIMENSIONS

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death Motorola was negligent regarding the design or manufacture of the part. Motorola and **Motorola** and **Motorola** with such unintended or unauthorized to see, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **Motorola** and **Motorola** and **Motorola** context or indirectly. Are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244–6609 INTERNET: http://Design-NET.com

$\Diamond$

MC3487/D