NCR

Microelectronic Products Division Colorado Springs

## NCR 53C700

SCSI I/O Processor

Programmer's Guide Rev. 1.0

Copyright © 1990 by NCR Corporation, Dayton, Ohio U.S.A. All Rights Reserved, Printed in the U.S.A.

## PRINTING HISTORY

While the information herein presented has been checked for both accuracy and reliability, NCR Corporation assumes no responsibility for either its use or any inaccuracies.

Prepared by NCR Microelectronics Division

| Revision No. | Print Date | NCR internal Part No(s). covered by each manual |

|--------------|------------|-------------------------------------------------|

| Preliminary  | 10/89      | 609-3400616 only                                |

|              |            | 609-3400625/631 (up to and including)           |

| 1.0          | 3/90       | 609-3400634 (includes all previous revisions)   |

#### **Additional Information**

NCR 53C700 Data Manual

#### Trademarks

SCRIPTS is a registered trademark of NCR Corporation IBM, Micro Channel are registered trademarks of International Business Machines Corporation .

## **Table of Contents**

| Chapter | Description                                                                                                                                                                                                                                                           | Page                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1.      | Introduction                                                                                                                                                                                                                                                          | 1-1                                                  |

| 2.      | SCSI SCRIPTS <sup>™</sup> Machine Language Description<br>Block Move Command<br>I/O Command<br>Transfer Control Command                                                                                                                                               | 2-1<br>2-5                                           |

| 3.      | Developing NCR SCSI SCRIPTS<br>Single-Tasking SCSI Example                                                                                                                                                                                                            |                                                      |

| 4.      | NCR SCSI SCRIPTS Utilities                                                                                                                                                                                                                                            | 4-1                                                  |

| 5.      | The NCR SCSI SCRIPTS Language Syntax         Notation         Input Format         Language Directives         The SCSI SCRIPTS Instructions         Block Move Command         Jump Command         Call Command         Interrupt Command         SCSI I/O Commands | 5-1<br>5-2<br>5-3<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7 |

| 6.      | SCSI SCRIPTS to Support Use of Scatter/Gather                                                                                                                                                                                                                         | 6-1                                                  |

| 7.      | NCR SCSI SCRIPTS For An Initiator                                                                                                                                                                                                                                     | 7-1                                                  |

| 8.      | Unique Initiator Sequences For The 53C700<br>Disk Drive Initiator Sequence<br>Tape Drive Initiator Sequence<br>SCSI Character Oriented Device in the Initiator Role                                                                                                   | 8-1<br>8-2                                           |

| 9.      | Save Data Pointers (message that can be ignored)<br>Save Data Pointers message that must be processed by the Initiator                                                                                                                                                | 9-1                                                  |

| 10.     | Multi-Tasking I/O Using SCSI SCRIPTS<br>Using SCSI SCRIPTS to Implement Multi-threaded I/O                                                                                                                                                                            | 10-1<br>10-2                                         |

## Appendices

| Chapter | Description                                                      | Page        |

|---------|------------------------------------------------------------------|-------------|

| Α       | High Performance Considerations When Using the 53C700 vs. 53C90  | A-1         |

|         | Sample Input Data Structure                                      | A-1         |

|         | Initializing SCSI SCRIPTS for an I/O and Starting I/O Operations |             |

|         | Conclusion                                                       | A-2         |

| В       | 53C700 System Bus Utilization                                    | <b>B-</b> 1 |

|         | Host Bus Time to Fetch A SCSI SCRIPTS Command                    | B-1         |

|         | Conclusion                                                       | B-2         |

| С       | SCSI SCRIPTS Compiler                                            | <b>C-</b> 1 |

|         | SCSI SCRIPTS Compiler Pass 1                                     | C-1         |

|         | SCRIPT.xrf File Description                                      | C-2         |

|         |                                                                  |             |

| D       | Compiler SCRIPT Examples                                         | D-1         |

|         | SCSI SCRIPTS Compiler Pass 1 SCRIPT Source File                  | D-1         |

|         | SCSI SCRIPTS Compiler Pass 1<br>SCSI SCRIPTS Compiler Pass 2     | D-2<br>D-3  |

|         | SCSI SCRIPTS Cross Reference File Listing                        | D-4         |

| E       | SCRIPT Compiler Error Messages                                   | E-1         |

|         | Fatal Error:                                                     | E-1         |

|         | Error:                                                           |             |

|         | Warning:                                                         | E-4         |

## List of Figures

| Figure     | Description                                        | Page |

|------------|----------------------------------------------------|------|

| 1.         | Block Move Instructions                            |      |

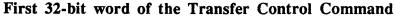

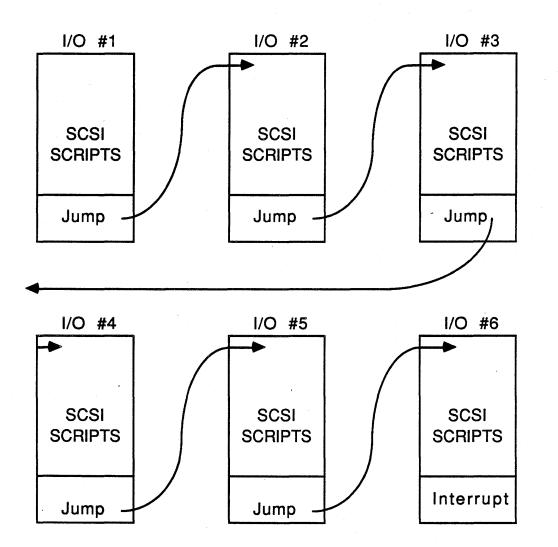

| 2.         | I/O Instructions<br>Transfer Control Command       |      |

| <b>4</b> . | Using SCSI SCRIPTS to implement Multi-Threaded I/O |      |

I

## Chapter 1 Introduction

## NCR SCSI I/O Processor (53C700)

#### I/O Performance

The demands on today's I/O interfaces are being pushed by increased performance of personal computers and workstations. Extremely fast CPU's, both CISC and RISC only provide marginal system performance if their I/O interfaces are not properly designed. Faster processors do not equal higher performance. Amdahl's Law describes this situation. "Assume I/O represents 10% of the system activity and its performance is kept constant. If CPU power is increased by a factor of 10:1, the net improvement is only 5:1. A 100:1 increase in CPU power is valueless if the net improvement in systems performance is only 10:1."

Interrupt service routines often take more than several hundred microseconds to execute and can be a large source of performance delays. Interrupts may be generated for exception conditions, I/O completion, saving/restoring buffer data pointers (for system checkpoint/restart), or low probability events available as options in todays SCSI definition. Interrupts can be reduced by using programmed I/O, however, this can be time consuming and requires much of the host computer cycle time. Therefore programmed I/O is not an adequate solution for multi-tasking operations.

Another performance issue is the scatter/gather operation. With virtual storage so common today, many I/O's gather the data from several physical addresses in system memory. Latencies inherent in the reinstruct DMA operation can cause serious performance degradation by allowing the disk drive to slip a latency while the DMA is being re-instructed.

#### I/O Flexibility

Options in bus protocol allow increased I/O flexibility. Need for I/O flexibility is partially responsible for the popularity of the SCSI standard. I/O flexibility allows configuration of systems for a wide range of peripherals (from high performance disk drives to hand held scanners). Additionally, I/O flexibility supports command queueing, asynchronous or synchronous data transfers, caching controllers, peer to peer communication, etc... Unfortunately, this implies firmware complexity. If these options are not carefully implemented, performance will suffer.

#### A Better Solution

First generation (NCR5380) SCSI devices are register oriented and require processor intervention to make the most fundamental protocol decisions. Users like the flexibility of these devices because the low-level firmware interface provides specific real time information about the SCSI bus and improved testability of the SCSI device. This generation of devices typically requires in excess of 4,000 lines of code to specify a SCSI-1 device implementation.

Second generation (NCR53C90) SCSI devices provide on-chip state machines. Some complex SCSI sequences can be performed automatically which reduces protocol overhead. However, these devices have no decision making capability, because the internal sequences are fixed in hardware at VLSI design time. This generation of devices typically requires in excess of 2,500 lines of driver software to support this class of SCSI device. The flexibility of the SCSI bus creates a dilemma for system integrators and OEM's alike. The dilemma is: should first and second generation SCSI devices be used as non-intelligent, stand-alone devices or should they be integrated into intelligent host adapter boards. Non-intelligent SCSI host ports or host bus adapters require a fair amount of processor intervention, but are inexpensive to implement. Intelligent host adapters are more expensive than non-intelligent adapters. They provide slower decision making capabilities (less powerful CPU's), experience interpretation delays (2-8 msec required to start any I/O), and suffer from interprocessor communication delays. In systems not requiring a complex buffering scheme, nonintelligent host adapters outperform their intelligent counterparts. For peripheral controllers, space is at a premium and complex peripheral interfaces require powerful microprocessors to transfer data at the high rates used by the peripheral interface. Therefore, SCSI chips requiring intense firmware can overwork the controller microprocessor making it unable to perform required tasks. Limited available space usually excludes adding an extra processor or replacing it with a more powerful one.

With MIPS increasing in the system CPU, the delays caused by intelligent host adapter cards and slow peripheral controllers pose problems for the system integrator. The simplest solution is to build complex, versatile H/W sequences inside the SCSI components or to add additional CPU power in the SCSI device board. Both solutions are costly (space and component cost) and do not adequately address the problem.

#### Third Generation Requirements

To accommodate the flexibility requirements of the SCSI bus (reducing interrupts and controlling board cost), an additional level of intelligence and integration is required for next generation SCSI devices. Third generation SCSI devices must make execution decisions based on phase changes on the SCSI bus and compare specific incoming data values which will result in a minimum number of interrupts to the external processor.

A programmable SCSI device that executes SCSI oriented commands is required. These new devices must reduce interrupt service routine complexities by providing unique status values to the external processor for any interrupts that do occur. Additionally, a fully integrated DMA channel would allow full use of available host bus bandwidth. This is the key to overall I/O performance given current use of virtual memory schemes which require the ability to support scatter/gather memory operations without processor intervention.

Third generation SCSI devices require <u>only</u> a few hundred lines of driver code. This code is required for exception conditions and for passing addresses of the user data buffer to the device. Error recovery occurs at the high level interface. In second generation chips, the firmware is required to manage every detail of the error recovery mechanism, because the high level interface is fixed and has only one entry point. Programmable SCSI chips allow error recovery using the high level interface, because the algorithm can be entered at any command and error specific SCSI SCRIPTS<sup>™</sup> can be developed.

# The NCR SCSI I/O Processor (SIOP)

The NCR 53C700 is the first intelligent SCSI host adapter on a chip. A high-performance re-usable SCSI core and an intelligent 32-bit bus master DMA have been integrated with a SCSI SCRIPTS processor to accommodate the flexibility requirements of SCSI-1, SCSI-2, and eventually SCSI-3. This flexibility is supported while solving the protocol performance problems that have plagued both intelligent and non-intelligent adapter designs.

## SCSI Component

In addition to the reliability components of NCR's other SCSI chips:

- 10K volts ESD protection

- >350 mV Bus Hystersis

- Immunity to bus reflections due to impedance mismatches

- Controlled bus assertion times which reduces generated RFI, improves reliability, and increases the chances for FCC approval

- Latch-up protection >100 mA

- Voltage feed-thru protection

The SCSI core in the 53C700 is reusable and designed to migrate to SCSI-2 wide and fast requirements. It offers synchronous transfers up to 6.25 MBytes/sec with asynchronous transfers greater than 5 MBytes/sec. Synchronous offsets up to 8 are supported.

The SCSI core offers low-level register access as well as the high-level control interface. Like first generation SCSI devices, the 53C700 SCSI core can be accessed as a register oriented chip. The ability to sample and assert any signal on the SCSI bus can used for manufacturing test and diagnostic procedures. Loopback diagnostics are supported, the SCSI core may perform selfselection and operate as both an initiator and a target to verify that internal data paths are operational. The 53C700 can test the SCSI pins for physical connection to the board or the SCSI bus.

Unlike previous generation devices, the 53C700 SCSI core is controlled by the integrated DMA through a high-level logical interface. High level programming language commands controlling the SCSI core may be chained from main host memory. These commands instruct the SCSI core to select, reselect, disconnect, wait for a disconnect, transfer user data, transfer SCSI information, change bus phases, and implement all aspects of the SCSI protocol.

Also, the SCSI SCRIPTS processor will transfer execution control (jump, call, return, and interrupt) based on SCSI bus phase comparisons. A value in the SCSI SCRIPTS command can be compared to the actual data value on the SCSI bus, allowing the same transfer of control based on input data compares. The SCSI SCRIPTS processor is a special 2 MIPS processor located on the SCSI chip.

#### DMA COMPONENT

The DMA component is a bus master DMA chip that attaches easily to the 80486, 80386, 80286, 80386SX, and 80376 processors. It is designed for 25 Mhz 80386 bus timings and may be externally adapted to ISA (AT), EISA, Micro Channel<sup>TM</sup>, etc..

The 53C700 supports 16 or 32-bit memory and automatically supports misaligned DMA transfers. As with the 80386, data bus enables are provided for each byte lane. An on-chip, 32 byte FIFO allows 2,4, or 8 long words to be burst across the memory bus interface, providing memory transfer rates in excess of 50 MBytes/sec.

The DMA is tightly coupled to the SCSI core through the SCSI SCRIPTS processor which supports uninterrupted scatter/gather memory operations with only a 500 nanosecond delay between memory segment transfers.

A Watchdog Timer provides a "bus safety" feature. The flexible arbitration scheme allows daisy chained or "ored" memory bus request implementations.

#### SCSI SCRIPTS<sup>™</sup> Processor

The SCSI SCRIPTS processor is a specially designed 2 MIPS processor that allows both DMA and SCSI instructions to be fetched from host memory. Algorithms written in the SCSI SCRIPTS language and then compiled control the SCSI and DMA cores and are executed from 16 or 32-bit system memory. Complex SCSI bus sequences are executed independently of the host CPU.

The SCSI SCRIPTS processor can begin a SCSI I/O operation in 500 nsec. This compares to the 2-8 msec required for traditional intelligent adapters. The SCSI SCRIPTS processor offers performance and customization. By designing your own algorithms, you can tune SCSI bus performance adjusting it to new bus device types (i.e. scanners, communication gateways, etc.) or changes in the SCSI logical bus definitions, or quickly incorporate new or popular options.

The SCSI SCRIPTS processor is how the 53C700, the NCR third generation SCSI chip implements flexibility without sacrificing I/O performance.

#### NCR SCSI SCRIPTS™ Description

SCSI SCRIPTS are independent of the CPU and system bus. SCRIPTS for an EISA implementation of a 80386 can therefore be identical to the scripts for a 80386SX Micro Channel<sup>™</sup> implementation.

After power up and initialization of the 53C700, the chip may be operated in one of two modes:

- 1) Low level register interface

- 2) SCSI SCRIPTS chained mode.

In the low level register interface, you have access to the DMA control logic and the SCSI bus control logic and can operate the chip like an NCR 53C80. Access by an external processor to the SCSI bus signals and the low level DMA signals, allows use of a complicated board level test algorithm. The interface provides backwards compatibility with SCSI chips requiring unique timings or bus sequences to operate properly. Another low level feature is loop back testing. In loop back mode, SCSI core can be directed to talk to the DMA core, this allows the internal data paths to be tested all the way to the chip's pad.

Operating in the SCSI SCRIPTS chained mode, the 53C700 requires only a SCSI SCRIPTS start address. All subsequent commands are fetched from external memory. Four bytes (or optionally two) at a time are fetched across the iAPX 286/386 DMA interface and loaded into the command register. Command fetch and decode time is minimal at about 500 nanoseconds. Commands are fetched until an interrupt command is encountered or until an external, unexpected event (e.g. hardware error detected) causes an interrupt to the external processor. The full set of SCSI features in the command set allow re-entry of the SCSI algorithm at any point. A high level interface is required for both normal and exception conditions. Therefore switching to a low level mode for error recovery as is the case with today's second generation SCSI VLSI is never necessary.

## Chapter 2 SCSI SCRIPTS ™ Machine Language Description

This chapter describes each SCSI SCRIPT<sup>TM</sup> command at the programmer, detailed, bit level. Normally you will use the SCSI SCRIPTS compiler described in following sections, but for debugging purposes, each command is described in detail. Each command description consists of a bit diagram of the command, a brief overview of the command and a description of each field within the command.

Bits 31-30 are SCSI I/O Processor opcodes.

- 00 equals Block Move Command

- 01 equals I/O Command

- 10 equals Transfer Control Command

- 11 equals NCR Reserved

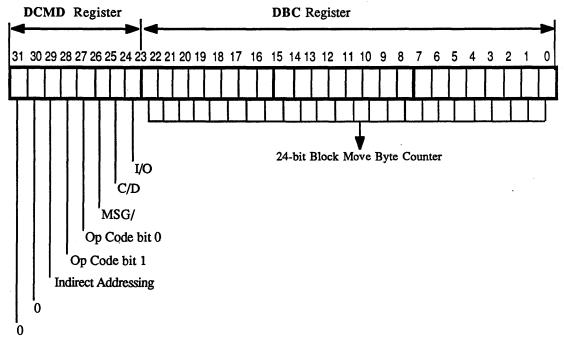

## **BLOCK MOVE COMMAND (00)**

First 32-bit word of the Block Move Instructions

|    |    |      |    |    |    |    |    |     |    |    |     |      |    |    |    |    | giste |              |    |    |     |   |     |      |     |    |    |   |   |   |           |

|----|----|------|----|----|----|----|----|-----|----|----|-----|------|----|----|----|----|-------|--------------|----|----|-----|---|-----|------|-----|----|----|---|---|---|-----------|

| 31 | 30 | ) 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15 | 14    | 13           | 12 | 11 | 10  | 9 | 8   | 7    | 6   | 5  | 4  | 3 | 2 | 1 | 0         |

|    |    |      |    |    |    |    |    |     |    |    |     | Γ    |    |    |    |    |       |              |    |    |     |   |     |      |     |    | Γ  | ſ | Γ | Γ | $\square$ |

|    |    |      |    |    |    | 1  | Se | cor | ıd | 32 | -bi | it v | wo | rd | of | th | e E   | <u> 31</u> 0 | ck | M  | lov | e | Ins | stru | uct | io | ns |   |   | - |           |

Figure 1. Block Move Instructions

## Overview

The Block Move command transfers data to(from) user memory from(to) the SCSI bus. No distinction is made between user data and SCSI information, such as command or message bytes. A series of SCSI SCRIPTS is written to move all types of data, with no requirement for separate firmware to distinguish between user and SCSI data. Note that the data may come from any memory address, so scatter/gather operations for user data are transparent to the chip and the external processor. Write a separate Block Move for each piece of data to be moved. Use the 32 byte DMA data buffer to speed data transfers between user memory and the I/O Processor. Synchronous SCSI data in transfers can use the 8 byte FIFO.

Note: The possible values for each field are given in binary.

## Block Move Command First SCRIPTS Word

#### Block Move opcode -- 00 Bits 31-30

#### Indirect data address flag (I) Bit 29

- 0 SCSI or user data is moved to(from) the 32-bit data start address for the block move. The value is loaded into the chip's address register and incremented as data is transferred.

- 1 The 32-bit SCSI or user data start address for the Block Move is the address of a pointer to the actual data buffer address. The value at the 32-bit data start address is loaded into the chip's DNAD register via a second long word (four byte transfer across the host computer bus).

This option implies three DMA long word transfers, rather than two transfers. Once the data buffer address is loaded, it is executed as if the chip operates in the direct mode. This indirect feature allows specification of a table of data buffer addresses. Using the NCR SCSI SCRIPTS compiler, the table offset is placed in the script at compile time. Then at the actual data transfer time, the offsets are added to the base address of the data address table by the external processor. This allows the logical I/O driver to build a structure of addresses for an I/O rather than treating each address individually. Also, this feature makes it possible to locate SCSI SCRIPTS in a PROM.

#### Block Move Opcodes Bit 28-27

The SCSI role (target or initiator) causes the chip to react differently, with respect to the phase line values. A primary difference between roles is whether the SCSI phase lines are sensed or driven. There are also major differences between the two roles in the command phase. Therefore, the Block Move functions are described for each SCSI role target and initiator.

#### Target Role Function--00

The target role allows DMA user or SCSI data First the chip determines whether the previous command has completed, or a reselect has occurred. The SCSI phase bits are asserted to the value requested by the Block Move command. If the command phase has been requested, the chip will:

- Wait for the first byte received.

- Decode the byte to determine the number of SCSI command bytes to receive.

- Write the command length into the DBC register.

An invalid group code value causes the chip to use the original value in the DBC register. A zero value stops processing, creates an interrupt with the first byte, and stops transferring command bytes.

• Transfer the correct number of bytes into the address designated by the Block Move command.

If any phase (other than command) is requested, the chip transfers the number of bytes requested to(from) the address requested. Should the initiator turn on attention at any time during the transfer, the transfer will be completed, and then an interrupt will occur.

#### Target Role Function--01,10, or 11

These are illegal values and will generate an invalid command interrupt if the chip is in the target role.

#### Initiator Role Function--00

#### Reserved

#### Initiator Role Function--01

In the initiator role, this operation waits for a valid phase and DMA data. After verification that the previous command is complete or a reselect has occurred, and the chip waits for a previously unserviced phase before executing the Block Move command. You can program the 53C700 to pause until the SCSI device it is communicating with goes to the next phase.

A comparison is made between the expected phase bits in the SCSI SCRIPTS and the latched phase value. If the two values are not equal, the chip issues a phase mismatch interrupt and halts execution. This wait capability is normally used to allow the target to pace the chip in the initiator role. When a phase change is expected, the wait synchronizes the expected phase with the Block Move for that phase.

#### Initiator Role Function--10, or 11

These are illegal values and will generate an invalid command interrupt if the chip is in the initiator role.

## SCSI Phase Lines Bit 26-24

These three SCSI phase lines perform comparisons to the actual SCSI bus phase lines. The SCSI bus phase value is latched when REQ goes active. The value is stored in SSTAT2 (bit 2 through bit 0 -- MSG, C/D, & I/O). Before any data is moved, the chip compares the expected value with the actual value (or waits for a new phase and compare).

## 24-Bit Byte Count, Bit 23-00

This count value specifies the exact number of data bytes to be moved between the SCSI bus and system memory. As the SCSI SCRIPTS command is decoded, the value is moved into the DBC register. When the user specified burst size of data is available in the DMA FIFO, the SCSI I/O Processor will:

- Gain access to the system bus.

- Transfer the burst size.

- Decrement the byte counter (byte count).

- Increment the next address register (data address).

The process will continue until the byte count is zero. At that time, the next SCSI SCRIPTS command will be fetched.

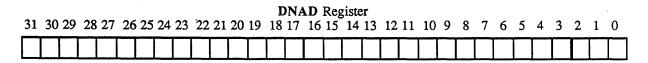

## Block Move Second SCRIPTS Word

#### Data Start Address for the Block Move Bits 31-00

This value specifies the address of data in memory (direct mode) or the address of the actual address (indirect mode). The DNAD register is updated with the address of the actual data and is incremented with each chip DMA transfer.

The Block Move command is very powerful for several reasons.

- 1) No distinction is made between user data and SCSI command, message, or status data.

- Data can be stored in any area of system memory with little performance impact (one command fetch).

- The indirect feature allows a table of addresses instead of requiring the address to be in the command.

A scatter/gather operation has little performance impact, because the only overhead is 500 nanoseconds (direct mode) or 750 nanoseconds (indirect mode). So, one Block Move command for each segment of data in memory is economical with the SCSI I/O processor architecture.

In the initiator role, the Block Move wait feature is useful for high performance SCSI SCRIPTS that do not compare for any unexpected phases before executing a Block Move command. If the phase does not match, then an external interrupt is generated.

For the high performance SCSI SCRIPTS algorithm, exceptions are abnormal and are handled by the external processor. Normally, the Conditional Transfer command (see I/O Command) compares actual to expected phase. The first Conditional Transfer command must have the "wait" option on (to synchronize the commands with the actual bus phase) and each subsequent command should have the "wait" option turned off.

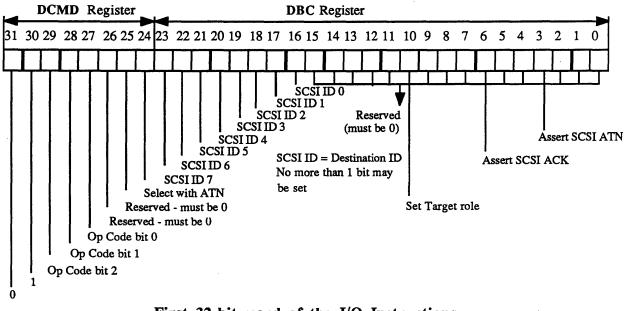

## I/O Command

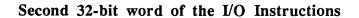

Figure 2. I/O Instructions

## Overview

The I/O command performs select and reselect SCSI operations. Each function defined is a direct command to the SCSI portion of the 53C700. The functions vary if the chip is in the target or initiator role, so the functions are described separately for each role.

## I/O Command First SCRIPTS Word

## SCSI I/O Processor opcode -- 01 Bits 31-30

#### I/O Command Opcodes Bits 29-27

Five functions are defined for target and initiator role, three are reserved for future expansion. Using the reserved function codes generates an illegal command interrupt stopping execution.

#### Target Role -- function 000

Perform reselection -- The chip arbitrates for the SCSI bus and then performs a reselection. Arbitration continues until the chip is successful, unless there is a bus initiated interrupt (e.g. selection). If arbitration terminates because of a bus initiated interrupt (selection or reselection) the chip will use the 32-bit jump address value to fetch the next instruction and begin execution at that address. If the command is successful, then the next sequential instruction is fetched and executed. Note that the target/initiator role automatically change to reflect what is actually happening on the bus.

After completion of the bus initiated interrupt processing (sequence goes to bus free), the chip reverts to the role set by the user in the registers. Some caution is required here. If the chip is set to an initiator role, gets selected, changes to the target role automatically, disconnects, does some processing, and then issues a reselect command (without being set to the target role by the external processor), a selection will occur. Because the chip was in the initiator role (at the time of selection), it reverts to that role after the disconnect and bus free.

<u>Target Role -- function 001</u> Perform disconnect -- The chip physically disconnects from the SCSI bus.

#### Target Role -- function 010

Wait for select -- The chip waits for a SCSI selection by another device on the SCSI bus. If the chip is already selected, then the next SCSI SCRIPTS is fetched and executed. When a bus initiated interrupt or reselect occurs, the chip changes to the initiator role and fetches the next command from the address pointed to by the 32-bit jump address, and continues execution.

#### Target Role -- function 011

Assert bit -- The chip asserts the latches in the SCSI output data register, but nothing is driven onto the SCSI bus. Consequently, this function should not be used in the target role.

#### Target Role -- function 100

Reset bit -- The chip resets the latches in the SCSI output data register, but nothing is reset on the SCSI bus. Consequently, this function should not be used in the target role.

## Target Role -- function 101, 110, 111

These are not currently defined and will cause an illegal command interrupt if used.

#### Initiator Role -- 000

Perform selection -- The chip arbitrates for the SCSI bus and then performs a selection. Arbitration continues until the chip is successful or a bus initiated interrupt (e.g. reselection) occurs. If arbitration terminates because of a bus initiated interrupt (as a result of a select or reselect), the chip uses the 32-bit jump address to fetch the next instruction and begin execution at that address. The target/initiator role automatically changes to reflect bus actions.

After completion of the bus initiated interrupt processing (sequence goes to bus free), the chip reverts to the role set by the user. If the selection is successful, the next instruction is fetched and executed. If bit 24 (the attention flag) is set, then the chip performs a select with attention.

#### Note:

Because the chip automatically changes roles and jumps to an alternate address if the select or reselect fails, a bus initiated interrupt can be processed by the chip with no external intervention. The alternate jump address should contain the address of an algorithm for a selection or reselection. Include in the address a wait for selection (target role) command. That command's alternate address is the reselection algorithm (initiator role). The 53C700 can determine exactly what happened and transfer control to the appropriate SCSI SCRIPTS algorithm.

#### Initiator Role -- 001

Wait for disconnect -- The initiator waits for a disconnect from the SCSI bus. A legal disconnect is defined as a loss of busy and select for the specified bus free time following a DISCONNECT message or a COMMAND COMPLETE message. If the disconnect is legal, the next SCSI SCRIPTS command will be executed, otherwise an unexpected disconnect interrupt will be generated.

#### Initiator Role -- 010

Wait for reselection -- The initiator waits for a reselection from a previously selected SCSI device. If the operation completes as expected, then the next instruction is fetched and executed by the 53C700. However, if the chip is selected, then the alternate jump address should contain the address of an algorithm for a selection. Include in the address a wait for selection (target role) command. That command's alternate address is the error recovery algorithm (for initiator role -- reselect). The chip can determine exactly what happened and transfer control to the appropriate SCSI SCRIPTS algorithm.

#### Note:

With the 53C700 byte compare capability of the transfer control command, the SCSI SCRIPTS algorithm can determine which target reselected the initiator and can jump to the correct algorithm for that particular target. SCSI SCRIPTS can be tuned for the various types of targets available and executed with no external processor intervention.

#### Initiator Role -- function 011

Assert bit -- The chip asserts the SCSI bus bits requested in the flags field. Currently three bits are defined, allowing the SCSI ACK target role and ATN bits to be set. Bit 10 is for target, bit 6 is for Acknowledge, and bit 3 is for Attention.

#### Initiator Role -- function 100

Reset bit -- The chip resets the SCSI bus bits requested in the flags field. Currently two bits are defined, allowing the SCSI ACK target role and ATN bits to be reset. Bit 10 is for target, bit 6 is for Acknowledge and bit 3 is for Attention. <u>Initiator Role -- function 101, 110, 111</u> These are not currently defined and will cause an illegal command interrupt if used.

#### SELECT WITH ATN - Bits 26-24

If bit 24 is set, then the initiator SELECT command will cause the SCSI attention line to be set during the SELECT operation. Attention on is valid only during the initiator function 000. The bit is invalid for all other functions and will cause an interrupt.

#### SCSI I.D. 7-0 - Bits 23-16

This eight bit field is the I.D. for the SCSI chip to be selected in the initiator role and reselected in the target role. Set only one bit for either of the functions requested. These bits are not used for any function other than select or reselect.

#### Flags Field - Bits 15-00

These bits are used during the set or clear command. Bit 10, on places the chip in the target/initiator role. Bit 6, on sets/resets the SCSI acknowledge. Bit 3, on sets/resets the SCSI attention. Use the clear ACK command after the last target message-in byte has been verified for each separate message data Block Move command. The initiator has the opportunity to set attention before acknowledging the last message byte of a Block Move command. On each byte, if a parity error was detected on the message in operation, the ASSERT SCSI ATN is issued before the clear acknowledge is issued to accept the message. Use set Acknowledge to handshake bytes across the SCSI bus. Clear attention should be issued after the target has serviced the request for a message out by the initiator.

## I/O Command Second SCRIPTS Word

#### Jump Address - Bit 31-00

If the select, wait reselect, or reselect command fails, this thirty-two bit field specifies from which memory address to fetch the next SCSI SCRIPTS for execution. Normally, the next instruction is fetched in sequence if the requested operation completes with no bus initiated interrupt.

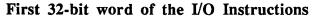

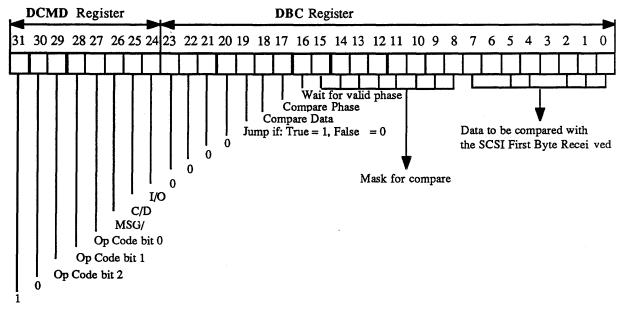

## **Transfer Control Command**

| _  |   | _   |   |    |    |    |    |     |     |    |     |      |     |    | DN | AD   | Re  | egist | er |      |     |    |     |    |   |    |    |     |   |   |   |   |

|----|---|-----|---|----|----|----|----|-----|-----|----|-----|------|-----|----|----|------|-----|-------|----|------|-----|----|-----|----|---|----|----|-----|---|---|---|---|

| 31 | 3 | 0 2 | 9 | 28 | 27 | 26 | 25 | 24  | 23  | 22 | 21  | 20   | 19  | 18 | 17 | 16   | 15  | 14    | 13 | 12   | 11  | 10 | 9   | 8  | 7 | 6  | 5  | 4   | 3 | 2 | 1 | 0 |

|    |   |     |   |    |    |    |    |     |     |    |     |      |     |    |    |      |     |       |    |      |     |    |     |    |   |    |    |     |   |   |   |   |

|    |   |     |   |    |    |    |    | Sec | con | d. | 32. | -bit | t w | or | do | of t | the | Tr    | an | Isfe | r ( | Co | ntr | ol | C | om | ma | ind | Ī |   |   |   |

Figure 3. Transfer Control Command

#### Overview

The Transfer Control Command contains the JUMP, CALL, RETURN, and INTERRUPT operation codes. Each opcode is conditionally performed based on compares of SCSI phase values and incoming SCIS data values. The Transfer control command allows comparisons of current phase values on the SCSI bus or the first byte of data on any incoming bytes and transfers control to another address depending on the results of the test. These commands allow SCSI algorithms to be written in SCSI SCRIPTS and give the 53C700 characteristics of a general purpose SCSI processor. With transfer control commands, you can program the chip, rather than simply buffering commands to be serially executed with no real-time decision making capabilities.

## Transfer Control Command First SCRIPTS Word

#### SCSI I/O Processor opcode -- 10 Bits 31-30

#### Transfer Opcodes - Bits 29-27

Four opcodes are currently defined that allow a transfer of control in the SCSI SCRIPTS language. All undefined opcodes cause an interrupt of illegal command.

#### JUMP Command -- 000

If the condition evaluates according to the sequence control bits so the jump must be taken, the next instruction is fetched from memory at the 32-bit jump address. Otherwise, the next sequential address will be used as the instruction fetch address.

#### CALL Command -- 001

If the condition evaluates according to the sequence control bits so the call must be taken, the next instruction is fetched from memory at the 32-bit call address. Otherwise, the next sequential address will be used as the instruction fetch address.

The address of the next sequential command is stored in the chip's TEMP register in anticipation of a subsequent return address. If two CALL instructions are executed without any intervening RETURN instruction, then the first return address in the chip's TEMP register is overwritten by the second CALL.

#### **RETURN Command -- 010**

If the condition evaluates according to the sequence control bits so the return must be taken, the next instruction will be fetched from memory at the 32-bit address contained in the TEMP register, where it was stored by the previous call instruction. Otherwise, the next sequential address will be used as the instruction fetch address. The contents of the TEMP register may be undefined if a call instruction was not previously executed.

#### **INTERRUPT** Command -- 011

If the condition evaluates according to the sequence control bits so the software interrupt must be taken, the chip halts execution and issues an interrupt request to the external processor. Otherwise, the next sequential address will be used as the instruction fetch address.

The 32-bit jump address in the instruction is available in the chip's command register at the time of the interrupt. You can post a four byte, user unique error status to be used by the external processor's interrupt service routine. Thus, the cause of the interrupt can be easily decoded by firmware which reduces firmware interrupt service routine overhead.

#### SCSI Phase Bits - Bits 26-24

In the SCSI initiator role, these bits compare the actual SCSI lines (MSG, C/D, and I/O), if the phase compare bit is set in the sequence control field. Actual SCSI lines are a copy of the last valid SCSI phase line values. These bits are set in the SCSI SCRIPTS command to compare with the current SCSI bus phase lines, then branch to the SCSI SCRIPT<sup>™</sup> that processes the particular phase that is currently active. Bit 26 is SCSI MSG, bit 25 is SCSI C/D, and bit 24 is SCSI I/O. In the target role, these bits are ignored.

#### Bits 23-20

These bits are reserved for future use and must be zero.

#### Sequence Control Bits - Bits 19-16

SCSI SCRIPTS can use the current conditions on the SCSI bus to determine where to transfer control and execute alternative algorithms using the sequence control bits. The bits are defined as follows:

• Bit 19 -- Transfer if True/False.

If the bit is set to 1, a transfer of control occurs if the phase or data values in the instruction are equal to the actual phase value on the SCSI bus or the first byte of the most recent asynchronous in phase. The byte could be a message in, data in, or status for the initiator and message out, command, or data out for the target role. When the bit is set to zero, the transfer control will occur if the comparison yields a false.

• Bit 18 -- Compare the data byte value (bit 7 - bit 0 in the instruction) to the first byte of the most recent data, message, command, or status byte received.

The user's SCSI SCRIPTS program can determine what routine to execute next, based on actual data values received across the SCSI bus. For example, the chip can compare for specific message values and process an extended message in SCSI SCRIPTS, with no external interrupt to the external processor.

• Bit 17 -- In the initiator role, compare the SCSI phase line value (bit 26 - bit 24) to the recent valid SCSI phase line values saved in the chip.

Using this feature, the chip can react to actual bus conditions and determine which routines to execute next based on SCSI bus phase line values. Unexpected phase values can be compared for and error conditions or low probability events can be processed by SCSI SCRIPTS inside the chip. In the Target role, bit 17 on causes the chip to test for the attention line on. If the initiator has set attention, the chip (in the target role) can jump to a message out routine to determine what the initiator needs. This is normally placed after each SCSI phase to allow the initiator to turn on attention if an error is detected during the transfer.

• Bit 16 -- In the initiator role, wait for a previously unserviced phase change.

You can program the chip to pause until the SCSI device it is communicating with has proceeded to the next phase. One normally uses this wait capability to pace the chip in the initiator role. When a phase change is expected, the wait is used to synchronize the expected phase with the actual phase detected on the SCSI bus. If both data and phase compare bits are set, the compare must be both true or both false for the transfer to occur.

#### Mask Bits - Bits 15-8

The mask bits allow selective comparison of bits within the data byte using SCRIPTS. During the compare, any bits that are on will cause the corresponding bit in the data byte to be ignored for the comparison. A user can code a binary sort to quickly determine the value of a byte.

For instance, a mask of '7F' and data compare of '80' allows the SCRIPTS processor to determine whether or not the high order bit is on.

#### Data Byte - Bits 7-0

Compare this data byte value to the first byte of the most recent asynchronous data, message, command, or status byte received. The user's SCSI SCRIPTS program can determine what routine to execute next based on actual data values received. Using a series of these compares, the algorithm can process complex sequences with no intervention required by the external processor.

## Transfer Control Command Second SCRIPTS Word

#### Data Jump Address - Bit 31-00

This value specifies the address of the next instruction in memory to transfer control. The value is ignored both return and interrupt commands. However, the address is loaded into the chip's command register and is available to be read by firmware in the case of an interrupt command.

If both data compare and phase compare bits are set, then both comparisons must be true or both must be false before the requested transfer will occur. There is no way to test one for false and the other for true.

If neither the phase or data bit are set, and if the true/false bit is 1, the operation is executed unconditionally.

If neither the phase nor the data bit is set and the true/false bit is 0, then the command has no operation assignment and can be used as a delay function, or to reserve SCSI SCRIPTS patch area.

## Chapter 3 Developing NCR SCSI SCRIPTS™

NCR Microelectronics has a 53C700 Software Development kit which supports the development of SCSI SCRIPTS. This kit includes:

- Sample SCRIPTS

- SCRIPTS Utilities

- Test/Diagnostic SCRIPTS

- A SCRIPTS compiler

- Hardware Test Support

Your local NCR Sales Office or Factory Representative will assist you with ordering information and current board level options.

To develop an executable SCSI SCRIPT, first define the SCSI functions required. Identify what functions will be executed in SCRIPTS and what functions must be contained in system firmware. Then design the specific algorithms for the functions that will be executed in the SCSI SCRIPTS portion of the SCSI logical I/O driver.

Use the SCRIPTS compiler to code the algorithms SCRIPTS. Then compile to create the object code required as input by the 53C700. The compiler output is like an object module, it includes relocation information required to load the SCRIPTS object module into main memory.

At load time, the SCRIPTS jump addresses must be resolved using one of the utilities furnished in the software package. At start I/O time, another utility is used to patch in the correct buffer addresses, byte counts, destination I.D., etc.

Writing a logical I/O driver is an easy task for the 53C700. This is illustrated in the first SCSI SCRIPTS example. This code will perform a read or write function using the 53C700 in the high level chained mode. Because SCSI algorithms are so simple when written in SCSI SCRIPTS, you can rapidly prototype SCSI algorithms for a proof of concept and concentrate on more complicated, realistic algorithms.

A SCSI SCRIPTS is comprised of two parts or areas:

- 1) Definition area

- 2) SCRIPT area

In this example, the definition area is comprised of variable and absolute values. These values may describe a variable memory address location, variable byte count or a fixed status byte value.

#### **Definition area INITIATOR ROLE**

; Target Device I.D. to be fixed at Start I/O time. EXTERNAL device

; Ten byte buffer for sending messages EXTERNAL sendmsg

; Ten byte buffer for receiving messages EXTERNAL rcvmsg

; Number of message bytes to send after selection EXTERNAL idcount

; Number of command bytes EXTERNAL cmd\_count

; Buffer for the SCSI command EXTERNAL cmd\_adr

; Number of user data bytes EXTERNAL data\_count

; Address of user data buffer EXTERNAL data\_adr ; Error -- not message out after selection

ABSOLUTE err1 = 0x0ff01

; Error -- unexpected SCSI phase before command phase ABSOLUTE err2 = 0x0ff02

; Error -- unexpected SCSI phase after a command transfer ABSOLUTE err3 = 0x0ff03

; Error -- expected status phase ABSOLUTE err4 = 0x0ff04

; No Error -- good I/O ABSOLUTE ok = 0x0ff00

; Error -- expected message outphase ABSOLUTE err5 = 0x0ff05

; Error -- expected message command complete ABSOLUTE err6 = 0x0ff06

#### Single-Tasking SCSI Example

The following is a simple SCSI SCRIPT that performs a single-tasking SCSI operation without disconnecting.

If an unpredictable event occurs on the SCSI bus, a unique interrupt status value is DNAD stored in the 53C700's register and is available for interrupt processing.

; select the device with attention on select atn device resel\_adr

; if the next phase is not message out, interrupt int err1 when not MSG\_OUT

; sent the i.d. message out to the target move idcount sendmsg when MSG\_OUT

; if the next phase is not command, interrupt int err2 when not CMD

; send the command bytes move cmd\_count cmd\_adr when CMD

; go to process cleanup if status phase jump end when STATUS

; process data in phase jump input\_data if DATA\_IN

; or data out phase jump output\_data if DATA\_OUT

; unexpected phase if here int err3

; process the data in phase input\_data: move data\_count data\_adr when DATA\_IN

; and go process status jump end

; process the data out phase output\_data: move data\_count data\_adr when DATA\_OUT

; interrupt if not status phase end: int err4 when not STATUS ; move the status byte into memory move 1 status\_adr when STATUS

; interrupt if message in is not next int err5 when not MSG\_IN

; move the command complete byte in move 1 rcvmsg when MSG\_IN

; interrupt if it is not a command complete message int err6 if not  $00\,$

; accept the message if there are no problems clear ack

; wait for a physical disconnect wait disconnect

; interrupt with an I/O complete int ok

# Chapter 4 NCR SCSI SCRIPTS ™ Utilities

The development package includes these utilities and the SCSI SCRIPTS Compiler.

## InitSIOP()

**Declaration:**

void InitSIOP( struct SIOP \* )

InitSIOP() accepts a pointer to an SIOP struct or NULL. If NULL then all the members in \_\_SCSIREGS\_\_ are assigned a value of 0. Otherwise copy the value from each member of the passed struct into \_\_SCSIREGS\_\_ and put those into the chip.

#### NOTE:

This function will, by default, assign one struct to another. This is ANSI compatible, but older compilers may not support it. Therefore by defined KR to 1 each member will be assigned in turn.

## SetPhaseMMInt()

Declaration: void SetPhaseMMInt( BOOL )

SetPhaseMMInt() turns the phase mismatch interrupt on or off.

## SetCompInt( BOOL )

Declaration: void SetCompInt( BOOL )

SetCompInt() turns the function complete interrupt on or off.

## SetSelTimeoutInt()

Declaration: void SetSelTimeoutInt( BOOL )

SetSelTimeoutInt() turns the select time out interrupt on or off.

## SetSelInt()

Declaration: void SetSelInt( BOOL )

SetSelInt() turns the select interrupt on or off.

## SetGrossErrInt()

Declaration: void SetGrossErrInt( BOOL )

SetGrossErrInt() turns the SCSI gross error interrupt on or off.

## SetUXDiscInt()

Declaration: void SetUXDiscInt( BOOL )

SetUXDiscInt() turns the Unexpected disconnect interrupt on or off.

## SetRSTInt()

Declaration: void SetRSTInt( BOOL )

SetRSTInt() turns the RST/ interrupt on or off.

## SetParInt()

Declaration: void SetParInt( BOOL )

SetParInt() sets the parity error interrupt on or off.

## Set286Mode()

Declaration: void Set286Mode( BOOL )

Set286Mode() puts the chip in 80286 mode when ON, otherwise it is in the 80386 mode.

## ClearDMAFifo()

Declaration: void ClearDMAFifo()

ClearDMAFifo() clears the DMA FIFO.

## SetIO()

Declaration: void SetIO( BOOL )

SetIO() tells the SIOP to transfer data to an I/O mapped device when ON, otherwise transfers are to memory mapped devices.

#### Set16BitDBus()

Declaration: void Set16BitDBus(BOOL)

Set16BitDBus() causes the SIOP to perform transfers 16-bits at a time when ON, otherwise transfers are 32-bits at a time.

## SetFixedAddr()

Declaration: void SetFixedA

oid SetFixedAddr(BOOL)

SetFixedAddr() disables the address pointer in the DNAD register so that it is ON, it will not increment.

## SetAbortInt()

Declaration: void SetAbortInt(BOOL)

SetAbortInt() makes the SIOP drive the INT/ signal when an abort condition is encountered and it is set to ON.

## SetINTInstInt()

Declaration: void SetINTInstInt( BOOL )

SetINTInstInt() allows the SIOP to drive the INT/ signal when it encounters an INT instruction in a script and it is set to ON.

## SetWatchDogInt()

Declaration: void SetWatchDogInt( BOOL )

SetWatchDogInt() allows the SIOP to drive the INT/ signal when the watch dog timer decrements to 0 and it is set to ON.

#### SetIllegalInstInt()

Declaration: void SetIllegalInstInt( BOOL )

SetIllegalInstInt() allows the SIOP to drive the INT/ signal when an illegal instruction is encountered in a SCRIPT and it is set to ON.

## Set16BitScripts()

Declaration: void Set16BitScripts( BOOL )

Set16BitScripts() makes the SIOP fetch script instructions 16-bits at a time when set to ON. Otherwise fetches are 32-bits at a time.

## SelClkFreq()

Declaration:

void SelClkFreq(UBYTE)

SetClkFreq() send the clock speed being used by the system to the SIOP. It accepts 1 of 3 values; SLOW, MED, or FAST.

| /* | 0 | FAST | 37.51 | to | 50 MHz   |

|----|---|------|-------|----|----------|

| /* | 1 | MED  | 25.01 | to | 37.5 MHz |

| /* | 2 | SLOW | 16.67 | to | 25 MHz   |

## SetHOSTID()

Declaration: BOOL SetHOSTID(UBYTE)

SetHOSTID() accepts a byte value to be placed into the SCID register. It will not allow a value of 255 (FF hex) to be placed into this register since the SIOP cannot talk to itself.

## SetParity()

Declaration: void SetParity( BOOL )

SetParity(), when ON, the SIOP checks the data bus for odd parity when receiving across the SCSI bus.

## SetAutoATN()

Declaration:

void SetAutoATN( BOOL )

SetAutoATN(), the SIOP asserts the ATN/ signal when a parity error is detected and it is ON.

## SetSlowBus()

Declaration: void SetSlowBus( BOOL )

SetSlowBus(), the SIOP adds 1 extra clock cycle to the data setup time when it is ON.

## GetPhysAddr()

Declaration: ULONG GetPhysAddr( UBYTE far \* )

GetPhysAddr() accepts a far pointer in the 80x86 format. Then It takes the segment portion, multiplies it by 16 and adds it to the offset portion to return a physical address.

## PatchLabels()

Declaration:

PatchLabels() patches a script that references labels within that script. Three ULONGs are passed to it.

The first ULONG is a pointer to the ULONG array SCRIPT that is going to be manipulated.

The second is a pointer to the ULONG PatchArray (LABELPATCHES), the array whose elements contain the offsets into the script to be manipulated.

The third ULONG is the count of the number of elements in the patch array.

void PatchLabels(Base, PatchArray, Count) ULONG Base[], PatchArray[]; ULONG Count;

## PatchRelative()

Declaration:

void PatchRelative (ScriptBase, RelBase,

|       | RelArray, Count)          |

|-------|---------------------------|

| ULONG | ScriptBase[], RelArray[]; |

| ULONG | RelBase, Count:           |

PatchRelative() requires a little programmer input. It is very similar to PatchLabels(). Passed to it are

a pointer to the ULONG Script array,

the physical relative data base address,

a pointer to the ULONG relative Data array, and

a count of the number of elements in the relative array.

## PatchID()

Declaration:

| void | PatchID(Ins | structior | ns, Location, Value) |

|------|-------------|-----------|----------------------|

|      | ULONG       | far       | *Instructions;       |

|      | ULONG       | Locat     | ion, Value;          |

## PatchPhase()

Declaration:

| void | PatchPhase | (Instructions, Location, Value) |

|------|------------|---------------------------------|

|      | ULONG      | far '*Instructions;             |

|      | ULONG      | Location, Value;                |

#### Notation

- { } Something enclosed in curly braces is optional.

- { }"... " The item enclosed in the curly braces can be repeated as often as desired.

- KEYWORD A word in all upper case is a keyword. Case is ignored by the compiler when looking for keywords.

**Phase** must be replaced with only one of the following keywords:

MSG\_IN, MSG\_OUT, DATA\_IN, DATA\_OUT, CMD, STATUS, RES4, RES5

The word 'address' means a 32-bit number.

The word 'value' means a 32-bit number.

The word 'count' means a 24 bit number.

The word 'id' means an eight bit number that has exactly one bit set.

The word 'data' means an eight bit number.

The word 'expression' denotes a mathematical expression with the form:

<identifier> [<addop> <identifier>]\*

<identifier> is any valid variable name or a numeric constant.

<addop> is the '+' or '-' character to denote addition or subtraction respectively.

An 'expression' may be used in any place that a numeric value would normally be used. The value of all 'expressions' are automatically extended to 32-bits. When expressions are used in a context where the evaluated value is less then 32-bits, the least significant bits will be used. For instance, if an 'expression' is used to represent a count for a move instruction, the evaluated value will be truncated to 24 bits. Notification that the expression has been truncated will occur if the value of the expression is changed.

The word 'name' represents a string of one or more consecutive characters chosen from the letters, the numbers, the underscore, and the dollar sign. Names used for labels, externals, and variables in the relative data area are passed on to the Host development system.

If the Host development system has restrictions on the format of such names, it is the responsibility of the SCSI SCRIPTS writer's to avoid using such names. For example, Turbo C, which is used as the Host development system for this application, does not allow names to begin with a digit or to contain a dollar sign. Therefore, the SCSI SCRIPTS writer for DOS and Turbo C should avoid using names of this form.

## Input Format

SCSI SCRIPTS consist of a series of lines. Blank lines, lines containing only white space, and anything after a semi-colon on an input line are ignored by the front end.

The compiler is "token" oriented. It reads the input stream and splits it up into tokens. White space and anything from a semicolon to the end of the line is not part of any token, and is ignored by the first pass of the compiler. There are two types of tokens. A token is any string of consecutive letters, numbers, dollar signs, or underscores; a character can be part of ONLY one token. The input stream is split into tokens to minimize the number of tokens. For example, the string "abc" would be treated as one token ("*abc*") rather than multiple tokens ("*a*" and "*bc*").

The second type of token consists of characters that are not part of other tokens. Anything that is not a letter, a digit, an underscore, or a dollar sign becomes a token. For example, the string

"xxx=0x123; assign value to xxx"

contains three tokens.

xxx = 0x123

Numeric values may be specified in decimal, hexadecimal, octal, or binary.

Decimal numbers are specified by a string of digits not beginning with zero.

Hex numbers are specified by a string consisting of "0x" or "0X" and the hex digits of the number. Both upper and lower case are allowed.

A binary number is similar to a hex number, except that "0b" or "0B" is used instead of "0x" or "0X".

An octal number is specified by a "0" followed by the octal digits.

#### Language Directives

Several keywords provide information to the front end about the compilation of the SCSI SCRIPTS. They define symbolic names and indicate things to be passed to the second pass of the compiler.

#### ENTRY label {,label...}

The ENTRY keyword indicates that the specified labels are SCSI SCRIPTS entry points. Their names and values are defined at the back end, which will also make them available to the Host development system.

ABSOLUTE name = expression...}

This declares symbolic names for numeric values. For example,

ABSOLUTE bad\_cmd = 0x1200"

allows the name

bad\_cmd

to be used instead of a number in the SCSI SCRIPTS. The SCSI SCRIPTS will be compiled as if the number 0x1200 had been specified instead of the name "bad\_cmd" in every instruction that uses "bad\_cmd".

#### EXTERNAL name {,name...}

This tells the compiler that the SCSI SCRIPTS will refer to variables with specified names that are declared outside of the SCSI SCRIPTS. Some host development systems are not able to support use of this word and SCSI SCRIPTS requiring this feature may not be portable to all hosts.

#### **RELATIVE** name = expression {,name = expression...}

Use to declare relative data variables.

Use to decidie relative data variables

- *name* the variable name.

- *expression* the offset from the start of the relative data area where the variable is located.

A name followed by a colon signifies a label. Use a label name wherever there is a call for an address.

#### The SCSI SCRIPTS Instructions

When an instruction calls specifies a count, use a 24-bit number or a symbolic constant (declared using the ABSOLUTE keyword).

When an instruction requires an address, use

a 32-bit number,

the label name,

- the variable name in the relative data area (previously declared with the RELATIVE keyword), or

- the external variable name (previously declared with the EXTERNAL keyword ).

Labels, external variables, and relative variables all share the same name space. If a name is declared more than once, the front end resolves the conflict. If a problem possibly exists, a warning will be issued.

If the address field of an instruction contains an undefined name, then the front end assumes that it refers to a label that will be defined later. This is called forward referencing. If the name is defined later as an external or relative variable, this will create a name conflict and the front end will resolve it. A possible problem warning is issued.

#### **Block MOVE Command**

There are several forms of the Block Move instruction.

| address<br>count | Specify the address and byte count<br>fields of the instruction. If the<br>optional keyword PTR is present,<br>then the indirect bit will be set. |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase            | Specifies the phase field of the instruction                                                                                                      |

| WITH or<br>WHEN  | Specify the Block Move function codes                                                                                                             |

|                  | WITH signals the target role which sets the phase values                                                                                          |

WHEN is the initiator "test for

phase" feature

The 53C700 waits for a valid phase (initiator) or drives the phase lines (target). In the initiator role, it performs a compare by looking for a match between the phase specified in the SCRIPT and the actual value on the bus. If the phases do not match, an external interrupt occurs. Data is then transferred in or out according to the phase lines. When the count goes to zero, the next sequential SCRIPTS instruction is fetched.

MOVE count, { PTR } address, WITH Phase MOVE count, { PTR } address, WHEN Phase

#### JUMP Command

The conditional JUMP instructions all have the same general form.

- Address The SCSI SCRIPTS address that will be transferred to if the JUMP is taken.

- WHEN Sets the Wait bit in the SEQ CNTL field.

IF Do not set the Wait bit.

If NOT follows WHEN or IF, then the True/False bit of the SEQ CNTL field is not set; otherwise, the bit will be set.

Phase When present, the compare Phase bit of SEQ CNTL will be set; otherwise, it will be cleared.

data When present, the compare Data bit of SEQ CNTL will be set; otherwise, it will be cleared. If both 'Phase' and 'data' are specified, they must be in that order and they must be separated by the keyword AND.

ATN The target role version which is required to test whether the initiator has set ATN on the bus.

NOT Used for the inverse test of WHEN and IF. "NOT Phase OR data" is the negation of "Phase AND data".

MASK Always use with an 'AND' or 'OR' keyword. The data following the keyword 'MASK' allows a SCRIPT to selectively compare the bits within the data byte.

Any bits that are ON eliminate the corresponding bit in the data byte at the time of the compare. Use this 'binary sort' to quickly determine the value of incoming bytes. For example, a mask of '7F' and a data compare of '80' allows the SCRIPTS processor to determine if the high order bit is ON.

| NOP           |                                       |

|---------------|---------------------------------------|

| JUMP address  |                                       |

| JUMP address, | IF ATN                                |

| JUMP address, |                                       |

| JUMP address, | IF Phase AND data, AND MASK data      |

| JUMP address, | WHEN Phase                            |

| JUMP address, |                                       |

| JUMP address, |                                       |

|               | WHEN Phase AND data                   |

|               | WHEN Phase AND data, AND MASK data    |

| JUMP address, | IF NOT ATN                            |

| JUMP address, |                                       |

| JUMP address, | IF NOT data                           |

| JUMP address, | IF NOT data, AND MASK data            |

| JUMP address, |                                       |

| JUMP address, | IF NOT ATN OR data, AND MASK data     |

| JUMP address, |                                       |

| JUMP address, | IF NOT Phase OR data, AND MASK data   |

| JUMP address, | WHEN NOT Phase                        |

| JUMP address, | WHEN NOT data                         |

| JUMP address, | WHEN NOT data, AND MASK data          |

| JUMP address, |                                       |

| JUMP address, | WHEN NOT Phase OR data, AND MASK data |

| •             | · · · · ·                             |

#### **CALL** Command

All conditional CALL instructions have the same general form.

- Address The SCSI SCRIPTS address transferred to if the JUMP is taken.

- WHEN Set the Wait bit in the SEQ CNTL field.

IF Do not set the Wait bit.

If WHEN or IF are followed by NOT, then the True/False bit of the SEQ CNTL field is not set. Otherwise, the bit will be set.

Phase When present, the compare Phase bit of SEQ CNTL will be set; otherwise, it will be cleared.

data When present, the compare Data bit of SEQ CNTL will be set; otherwise, it will be cleared. If both Phase and data are specified, they must be in that order and they must be separated by the keyword AND.

ie. ...WHEN Phase AND data...

- ATN The target role version which is required to test whether the initiator has set ATN on the bus.

- NOT Used for the inverse test of WHEN and IF.

"NOT Phase OR data" is the negation of "Phase AND data".

MASK Always use with an 'AND' or 'OR' keyword. The data following the keyword MASK allows a SCRIPT to selectively compare the bits within the data byte.

Any bits that are ON eliminate the corresponding bit in the data byte at the compare. Use this 'binary sort' to quickly determine value of incoming bytes. For example, a mask of '7F'and a data compare of '80' allows the SCRIPTS processor to determine if the high order bit is ON.

| CALL | address   |                                         |

|------|-----------|-----------------------------------------|

| CALL | address,  | IF ATN                                  |

| CALL | address,  | IF Phase                                |

|      | address,  |                                         |

|      |           | IF data, AND MASK data                  |

|      | address,  |                                         |

|      | address,  |                                         |

| CALL | address.  | IF Phase AND data                       |

| CALL | address,  | IF Phase AND data, AND MASK data        |

|      |           | WHEN Phase                              |

|      |           | WHEN data                               |

|      |           | WHEN data, AND MASK data                |

| CALL | address.  | WHEN Phase AND data                     |

|      |           | WHEN Phase AND data, AND MASK data      |

|      |           | IF NOT ATN                              |

|      | address,  |                                         |

|      |           | IF NOT data                             |

|      |           | IF NOT data, AND MASK data              |

|      |           | IF NOT ATN OR data                      |

|      | address,  |                                         |

|      |           | IF NOT Phase OR data                    |

|      |           | IF NOT Phase OR data, AND MASK data     |

| CALL | address.  | WHEN NOT Phase                          |

| CALL | address   | WHEN NOT data                           |

|      |           | WHEN NOT data, AND MASK data            |

| CALL | address   | WHEN NOT Phase OR data                  |

| CALL | addraee   | WHEN NOT Phase OR data, AND MASK data   |

|      | uuui 833, | WHEN NOT FILLIGO ON URLE, AND MASK URLE |

NCR 53C700, Programmer's Guide

#### **RETURN** Command

All conditional RETURN instructions have the same general form.

- Address The SCSI SCRIPTS address that will be transferred to if the JUMP is taken.

- WHEN Set the Wait bit in the SEQ CNTL field.

IF Do not set the Wait bit.

If WHEN or IF are followed by NOT, then the True/False bit of the SEQ CNTL field is not set. Otherwise, the bit will be set.

Phase When present the compare Phase bit of SEQ CNTL will be set; otherwise, it will be cleared.

data When present, the compare Data bit of SEQ CNTL will be set; otherwise, it will be cleared. If both Phase and data are specified, they must be in that order and they must be separated by the keyword AND.

- ATN The target role version which is required to test whether the initiator has set ATN on the bus.

- NOT Used for the inverse test of WHEN and IF. "NOT Phase OR data" is the negation of "Phase AND data".

- MASK Always use with an 'AND' or 'OR' keyword. The data following the keyword 'MASK' allows a SCRIPT to selectively compare the bits within the data byte.

Any bits that are ON eliminate the corresponding bit in the data byte at the time of the compare. Use this 'binary sort' to quickly determine value of incoming bytes. For example, a mask of '7F'and a data compare of '80' allows the SCRIPTS processor to determine if the high order bit is ON.

| RETURN  |                                       |

|---------|---------------------------------------|

| RETURN, | IF ATN                                |

|         | IF Phase                              |

| RETURN, | IF data                               |

| RETURN, | IF data, AND MASK data                |

|         | IF ATN AND data                       |

|         | IF ATN AND data, AND MASK data        |

| RETURN, | IF Phase AND data                     |

|         | IF Phase AND data, AND MASK data      |

| RETURN, | WHEN Phase                            |

| RETURN, | WHEN data                             |

| RETURN, | WHEN data, AND MASK data              |

| RETURN, | WHEN Phase AND data                   |

| RETURN, | WHEN Phase AND data, AND MASK data    |

| RETURN, | IF NOT ATN                            |

| RETURN, | IF NOT Phase                          |

|         | IF NOT data                           |

|         | IF NOT data, AND MASK data            |

| RETURN, | IF NOT ATN OR data                    |

| RETURN, | IF NOT ATN OR data, AND MASK data     |

|         | IF NOT Phase OR data                  |

|         | IF NOT Phase OR data, AND MASK data   |

|         | WHEN NOT Phase                        |

|         | WHEN NOT data                         |

| RETURN, | WHEN NOT data, AND MASK data          |

|         | WHEN NOT Phase OR data                |

| RETURN, | WHEN NOT Phase OR data, AND MASK data |

### **INTERRUPT** Command

All conditional INT instructions have the same general form.

- Address The SCSI SCRIPTS address that will be transferred to if the JUMP is taken.

- WHEN Set the Wait bit in the SEQ CNTL field.

- IF Do not set the Wait bit.

If WHEN or IF is followed by NOT, then the True/False bit of the SEQ CNTL field is not set. Otherwise, the bit will be set.

- Phase When present, the compare Phase bit of SEQ CNTL will be set; otherwise, it will be cleared.

- data When present, the compare Data bit of SEQ CNTL will be set; otherwise, it will be cleared.

If both Phase and data are specified, they must be in that order and they must be separated by the keyword AND.

- ATN The target role version which is required to test whether the initiator has set ATN on the bus.

- NOT Used for the inverse test of WHEN and IF. "NOT Phase OR data" is the negation of "Phase AND data".

- MASK Always use with an AND or OR keyword. The data following the keyword MASK allows a SCRIPT to selectively compare the bits within the data byte.

Any bits that are ON eliminate the corresponding bit in the data byte at the compare. Use this 'binary sort' to quickly determine value of incoming bytes. For example, a mask of '7F'and a data compare of '80' allows the SCRIPTS processor to determine if the high order bit is ON.

| INT address  |                                       |

|--------------|---------------------------------------|

| INT address, |                                       |

| INT address, |                                       |

| INT address, | IF data                               |

| INT address, | IF data, AND MASK data                |

|              | IF ATN AND data                       |

| INT address, | IF ATN AND data, AND MASK data        |

|              | IF Phase AND data                     |

| INT address. | IF Phase AND data, AND MASK data      |

|              | WHEN Phase                            |

| INT address, |                                       |

|              | WHEN data, AND MASK data              |

| INT address  | WHEN Phase AND data                   |

|              | WHEN Phase AND data, AND MASK data    |

| INT address, |                                       |

| INT address, | IF NOT Phase                          |

| INT address, | IF NOT date                           |

|              |                                       |

|              | IF NOT data, AND MASK data            |

|              | IF NOT ATN OR data                    |

|              | IF NOT ATN OR data, AND MASK data     |

|              | IF NOT Phase OR data                  |

|              | IF NOT Phase OR data, AND MASK data   |

| INT address, | WHEN NOT Phase                        |

| INT address, | WHEN NOT data                         |

| INT address, | WHEN NOT data, AND MASK data          |

| INT address. | WHEN NOT Phase OR data                |

|              | WHEN NOT Phase OR data, AND MASK data |

|              |                                       |

## SCSI I/O Commands

#### SELECT {ATN} ID, Address

Initiator mode function 0. If ATN is present, the "select with ATN" bit is turned on. 'id' specifies the destination SCSI ID.

#### **RESELECT** id, address

Target mode function 0

#### WAIT DISCONNECT

Initiator mode function 1

#### DISCONNECT

Target mode function 1