# MOS INTEGRATED CIRCUIT $\mu PD6355G$

## 16 Bit D/A CONVERTER

The  $\mu$ PD6355G is a 16-bit D/A converter for digital audio equipment. To facilitate application as an audio D/A converter, this LSI incorporates built-in sample-and-hold circuit, output operational amplfier, and zero-point offset circuit.

This COMS LSI operates on +5 V single power supply at low current consumption.

#### **FEATURES**

- +5 V single power supply

- CMOS configuration

- Built-in sample-and-hold circuit

- Built-in output operational amplifier

- Built-in 0-point offset circuit

- Resistance strings system

- 2 f<sub>S</sub> (2 channels X 88.2 kHz sampling) capability

- 28-pin MF package

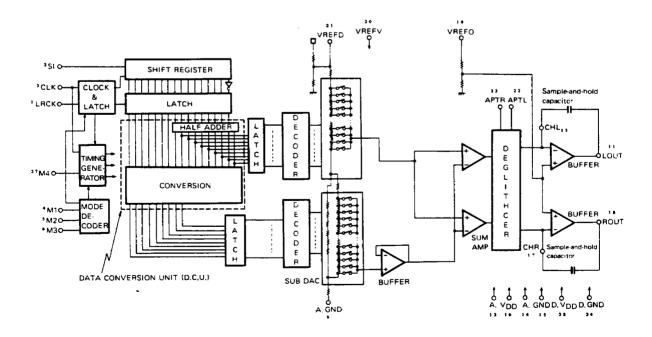

#### **BLOCK DIAGRAM**

## APP 64 FIRE

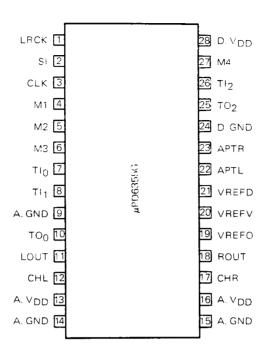

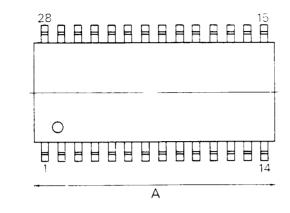

## CONNECTION DIAGRAM (Top View)

## ABSOLUTE MAXIMUM RATINGS (Ta=25 °C)

| Supply Voltage        | $V_{DD}$  | -0.3 to +7.0            | V  |

|-----------------------|-----------|-------------------------|----|

| Output Voltage        | Vout      | $-0.3$ to $V_{DD}$ +0.3 | V  |

| Input Voltage         | VIN       | $-0.3$ to $V_{DD}$ +0.3 | V  |

| Operating Temperature | $T_{opt}$ | -20 to +75              | °C |

| Storage Temperature   | $T_{stg}$ | -40 to +125             | °C |

# PDSSTREET

# RECOMMENDED OPERATING CONDITIONS ( $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$ )

| Parameter                | Symbol          | MIN.                | TYP. | MAX.                | Unit |

|--------------------------|-----------------|---------------------|------|---------------------|------|

| Supply Voltage           | V <sub>DD</sub> | 4.5                 | 5.0  | 5.5                 | V    |

| High-level Input Voltage | V₁H             | 0.7 V <sub>DD</sub> |      | VDD                 | V    |

| Low-level Input Voltage  | VIL             | 0                   |      | 0.3 V <sub>DD</sub> | V    |

# ELECTRICAL CHARACTERISTICS $(T_a=25 \, ^{\circ}C, \, V_{DD}=+5 \, V)$

| Parameter                   | Symbol          | MIN.         | TYP. | MAX. | Unit | Test Condition                    |

|-----------------------------|-----------------|--------------|------|------|------|-----------------------------------|

| Resolution                  | RES             |              | 16   |      | Bit  |                                   |

| Total Harmonic Distortion 1 | THD1            |              | .007 | .01  | %    | f <sub>IN</sub> =1 kHz, 0 dB      |

| Total Harmonic Distortion 2 | THD2            |              | .07  | :    | %    | f <sub>IN</sub> =1 kHz, -20 dB    |

| Full Scale Output Voltage   | V <sub>FS</sub> | 1.50         | 1.65 | 1.80 | V    |                                   |

| Cross Talk                  | C·T             | 77           | 83   |      | dB   | f <sub>IN</sub> =1 kHz            |

| S/N Ratio                   | S/N             | 84           | 90   | 1    | dB   |                                   |

| Load Resistance             | RL              | 5            |      | 1    | kΩ   | ROUT, LOUT terminal.              |

| Sampling Time               | T <sub>SP</sub> | 2            |      |      | μs   |                                   |

| Hold Time                   | THLD            | !            |      | 32   | μs   | Sample & hold capacitor is 47 pF. |

| Settling Time               | τ <sub>S</sub>  | 2            |      |      | μs   | <del>-</del>                      |

| 0                           | !               |              |      | 5    | MHz  | M4 is low level.                  |

| Clock Frequency             | fCLK            | <del>:</del> |      | 3    | MHz  | M4 is high level.                 |

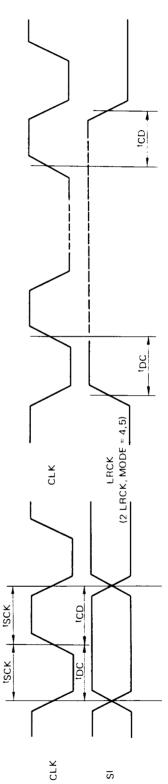

| Clock Pulse Width           | tSCK            | 100          |      |      | ns   |                                   |

| SCK, LRCK Setup Time        | <sup>t</sup> DC | 100          |      | 1    | ns   |                                   |

| SCK, LRCK Hold Time         | tCD             | 100          |      |      | ns   |                                   |

| Supply Current              | 1 <sub>DD</sub> |              | 13   | 20   | mA   |                                   |

## TERMINAL FUNCTION

| Termi-<br>na! No. | Symbol             | Terminal Name                 | Description                                                                                  | Input<br>Output |

|-------------------|--------------------|-------------------------------|----------------------------------------------------------------------------------------------|-----------------|

| 1                 | LRCK               | Left/Right Clock              | Input terminal for left right identification signal                                          | Input           |

| 2                 | SI                 | Series Input                  | Input terminal for serial data                                                               | Input           |

| 3                 | CLK                | Clock                         | Input terminal for serial input data read clock                                              | Input           |

| 4                 | M <sub>1</sub>     | Mode 1.                       |                                                                                              |                 |

| 5                 | M <sub>2</sub>     | Mode 2                        | input data mode switching terminal                                                           | Input           |

| 6                 | Мз                 | Mode 3                        |                                                                                              |                 |

| 7                 | τι <sub>0</sub>    | Test Input                    | The second to A CND                                                                          |                 |

| 8                 | TI <sub>1</sub>    | Test Input                    | Testing terminal. Normally connected to A. GND.                                              | Input           |

| 9                 | A. GND             | Analog Ground                 | Ground terminal for the analog circuit.                                                      |                 |

| 10                | тоо                | Test Out                      | Testing terminal. Normally kept open.                                                        | Output          |

| 11                | LOUT               | L-ch Output                   | Left analog signal output terminal.                                                          | Output          |

| 12                | CHL                | Hold Capacitance              | Terminal for left analog signal sample-and-hold capacitor connection.                        | Output          |

| 13                | A. V <sub>DD</sub> | Analog Power Supply           | Power supply terminal for the analog circuit.                                                |                 |

| 14                | A. GND             | Analog Ground                 |                                                                                              |                 |

| 15                | A. GND             | Analog Ground                 | Ground terminal for the analog circuit.                                                      |                 |

| 16                | A. V <sub>DD</sub> | Analog Power Supply           | Power supply terminal for the analog circuit.                                                |                 |

| 17                | CHR                | Hold Capacitance<br>R-channel | Terminal for right analog signal sample-and-hold capacitor connection.                       | Output          |

| 18                | ROUT               | R-channel Output              | Right analog signal output terminal                                                          | Output          |

| 19                | VREFO              | Voltage Reference             | Operational amplifier reference bias terminal. Normally connected to A. GND via a capacitor. |                 |

| 20                | VREFV              | Voltage Reference             | Normally connected to A. GND via a capacitor.                                                |                 |

| 21                | VREFD              | Voltage Reference             | Resistance strings bias terminal. Normally connected to A. GND via a capacitor.              |                 |

| 22                | APTL               | Aperture L-channel            | Termina! for sample and hold of the left analog output.                                      | Input           |

| 23                | APTR               | Aperture R-channel            | Terminal for sample and hold of the right analog output.                                     | Input           |

| 24                | D. GND             | Digital Ground                | Ground terminal for the logic circuit.                                                       |                 |

| 25                | TO <sub>2</sub>    | Test Out                      | Test terminal. Normally kept open.                                                           | Output          |

| 26                | T12                | Test                          | Test terminal. Normally connected to D. VDD                                                  | Input           |

| Termi-<br>nal No. | Symbol             | Terminal Name        | Description                                                                                                                                                                                                    | Input/<br>Output |

|-------------------|--------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 27                | М4                 | Mode 4.              | Selects the clock for the internal logic circuit. This terminal selects whether to divide the signal input from the CLK terminal. The signal is not divided at high level, or is divided in half at low level. | Input            |

| 28                | D. V <sub>DD</sub> | Digital Power Supply | Power supply terminal for the logic circuit.                                                                                                                                                                   |                  |

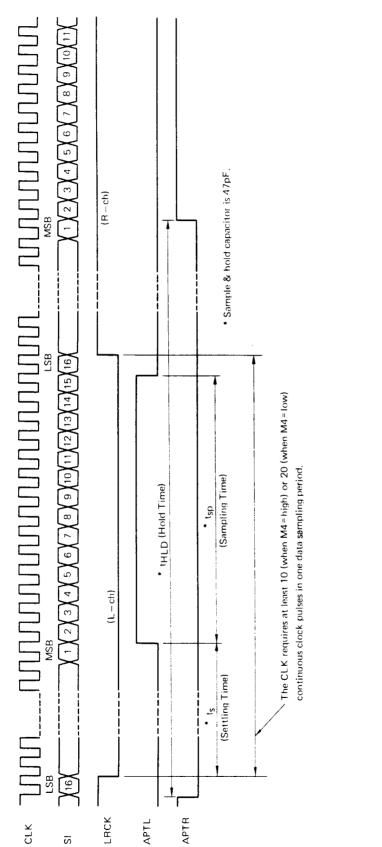

# SERIAL DATA INPUT TIMING

The  $\mu PD6355G$  conforms to multiple interface system with its mode switching terminals (M0, M1, M2).

### Mode List

| Mode | M <sub>3</sub> | M <sub>1</sub> | M <sub>2</sub> | APTL, APTR                    | Phase Relationship between LRCK and Serial Data (LSB) | 2's/BIN     |

|------|----------------|----------------|----------------|-------------------------------|-------------------------------------------------------|-------------|

| 0    | 0              | 0              | 0              |                               | Phase of LRCK and LSB are                             | 2's         |

| 2    | 0              | 0              | 1              | Input from external terminals | synchronous                                           | BIN         |

| 1    | 0              | 1              | 0              | APTL and APTR                 | L DOW hite 101 Kin advance of LCD                     | 2's         |

| 3    | 0              | 1              | 1              |                               | LRCK shifts 1CLK in advance of LSB                    | BIN         |

| 4    | 1              | 0              | 0              | Generated in the LSI by 2LRCK | Phases of LRCK and LSB are                            | <b>2</b> 's |

| 5    | 1              | 1              | 0              | (APTL terminal) and LRCK.     | synchronous                                           | BIN         |

| 6    | 1              | 0              | 1              | 1-1                           | _:L:_                                                 |             |

| 7    | 1              | 1              | 1              | Int                           | nibit                                                 |             |

## INPUT TIMING CHART

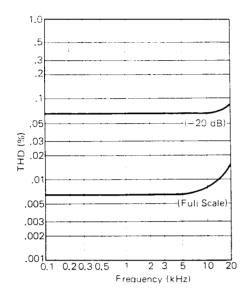

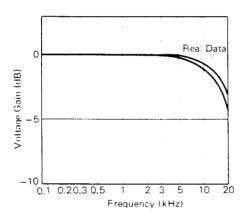

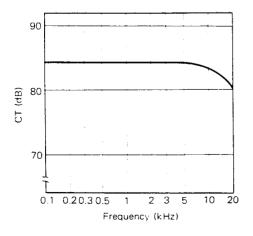

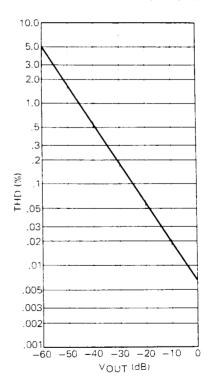

## TYPICAL CHARACTERISTICS (Ta=25 °C)

Note: 20 kHz Low Pass Filter is Toko (APQ-25).

Fig. 1 Total Harmonic Distortion (THD) VS Frequency

Fig. 3 Voltage Gain VS Frequency

Fig. 5 Cross Talk (CT) VS Frequency

Fig. 2 Total Harmonic Distortion (THD) VS VDD

Fig. 4 Total Harmonic Distortion (THD) VS V<sub>OUT</sub>

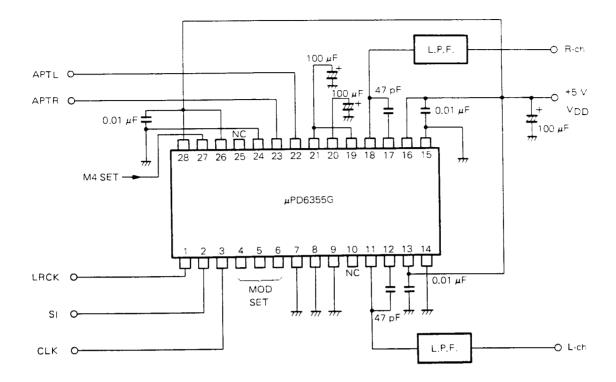

## EXAMPLE OF THE APPLICATION CIRCUIT

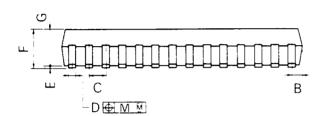

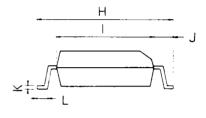

## 28PIN PLASTIC MINI FLAT (375 mil)

P28GM-50-375B

## NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS          | INCHES        |

|------|----------------------|---------------|

| Α    | 18.07 MAX.           | 0.712 MAX.    |

| В    | 0.78 MAX.            | 0.031 MAX.    |

| С    | 1.27 (T.P.)          | 0.050 (T.P.)  |

| D    | 0.40 -0 05           | 0.016 -0 003  |

| E    | 0.1 <sup>±0</sup> 1  | 0.004 +0 004  |

| F    | 2.9 MAX.             | 0.115 MAX.    |

| G    | 2.50                 | 0.098         |

| Н    | 10.3 <sup>±0.3</sup> | 0.406 - 0.013 |

| 1    | 7.2                  | 0.283         |

| J    | 1.6                  | 0.063         |

| K    | 0.15-0.05            | 0.006 - 0.004 |

| L    | 0.8 *0 2             | 0.031-0.009   |

| M    | 0.12                 | 0.005         |