### target spec

#### 262,144WORDS X 8BITS MULTIPORT DRAM

#### DESCRIPTION

The TC528257 is a 2M bit CMOS multiport memory equipped with a 262,144-words by 8-bits dynamic random access memory (RAM) port and a 512-words by 8-bits static serial access memory (SAM) port. The TC528257 supports three types of operations; Random access to and from the RAM port, high speed serial access to and from the SAM port and bidirectional transfer of data between any selected row in the RAM and the SAM. To realize a high performance graphic frame buffer system the TC528257 features various special operations such as the write - per - bit, the pipelined page mode, the block write and flash write function on the RAM port and the read and masked write transfer operations between the RAM and the SAM port. The TC528257 is fabricated using Toshiba's CMOS silicon gate process as well as advanced circuit designs to provide low power dissipation and wide operating margins.

#### **FEATURES**

- Single power supply of 5V ± 10% with a built-in V<sub>BB</sub> generator

- All inputs and outputs: TTL Compatible

- Organization

RAM Port: 262,144wordsX8bits SAM Port: 512wordsX8bits

RAM Port

Fast Page Mode, Read - Modify - Write,

Pipelined Fast Page Mode, CAS before RAS

Auto Refresh, Hidden Refresh, RAS only

Refresh, Write per Bit (New/Old Mask Mode),

Masked Flash Write (New/Old Mask Mode),

Block Write, Masked Block Write (New/Old

Mask Mode), Load Mask Register/Color

Register Cycle, 512 refresh cycles / 8ms

SAM Port

Serial Read / Write Capability Addressable TAP Capability Stop Address (Binary Boundary) Capability Fully Static Register, Single Register/Split Register Mode Capability

- RAM SAM Bidirectional Transfer Read / Real Time Read Transfer Masked Write Transfer Split Read / Masked Split Write Transfer

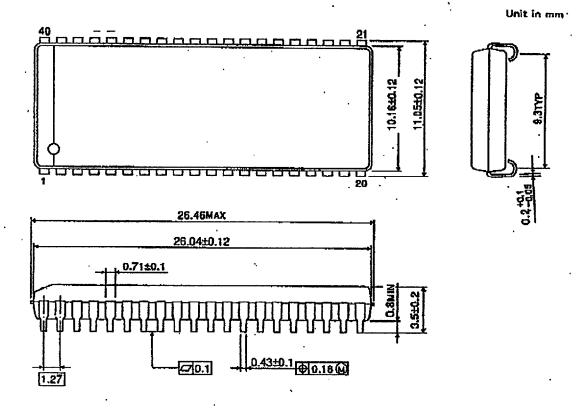

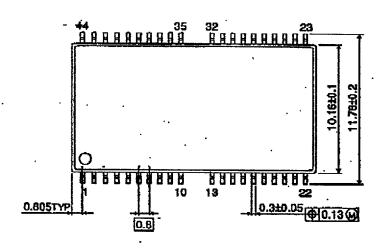

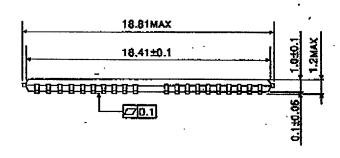

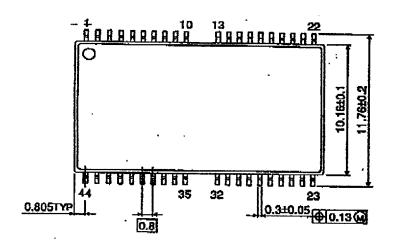

- Package

TC528257J : SOJ40-P-400 TC528257FT : TSOP44-P-400B TC528257TR : TSOP44-P-400C

#### **KEY PARAMETERS**

|                   | ITEM                                       | TC52        | 8257        |

|-------------------|--------------------------------------------|-------------|-------------|

|                   | 111741                                     | <b>—</b> 70 | <b>— 80</b> |

| t <sub>RAC</sub>  | RAS Access Time (Max.)                     | 70ns        | 80ns        |

| t <sub>CAC</sub>  | CAS Access Time<br>(Max.)                  | 20ns        | 20ns        |

| t <sub>AA</sub>   | Column Address Access<br>Time (Max.)       | 35ns        | 40ns        |

| t <sub>RC</sub>   | Cycle Time (Min.)                          | 130ns       | 150ns       |

| t <sub>PC</sub>   | Page Mode Cycle Time<br>(Min.)             | 45ns        | 50ns        |

| t <sub>SCA</sub>  | Serial Access Time<br>(Max.)               | 20ns        | 25ns        |

| t <sub>SCC</sub>  | Serial Cycle Time (Min.)                   | 25ns        | 30ns        |

| t <sub>RACP</sub> | t <sub>RAC</sub> in Pipelined Fast<br>Page | 90ns        | 95ns        |

| t <sub>CAC1</sub> | t <sub>CAC</sub> in Pipelined Fast<br>Page | 20ns        | 20ns        |

| t <sub>PCP</sub>  | Pipelined Fast Page<br>Mode Cycle Time     | 30ns        | 30ns        |

| I <sub>CC1</sub>  | RAM Operating Current (SAM : Standby)      | 100mA       | 85mA        |

| I <sub>CC2A</sub> | SAM Operating Current (RAM : Standby)      | 60mA        | 50mA        |

| I <sub>CC2</sub>  | Standby Current                            | 10mA        | 10mA        |

1/62

**TOSHIBA CORPORATION**

**9**097248 0027841 593 **1**

#### TC528257

#### **PIN NAME**

| A0~A8                            | Address inputs              |

|----------------------------------|-----------------------------|

| RAS                              | Row Address Strobe          |

| CAS                              | Column Address Strobe       |

| DT/OE                            | Data Transfer/Output Enable |

| WB/WE                            | Write per Bit/Write Enable  |

| DSF1<br>DSF2                     | Special Function Control    |

| W1/IO1 -W8/IO8                   | Write Mask/Data IN/OUT      |

| SC                               | Serial Clock                |

| SE                               | Serial Enable               |

| SIOI~SIO8                        | Serial Input/Output         |

| QSF                              | Special Flag Output         |

| V <sub>CC</sub> /V <sub>SS</sub> | Power(5V)/Ground            |

| N.C.                             | No Connection               |

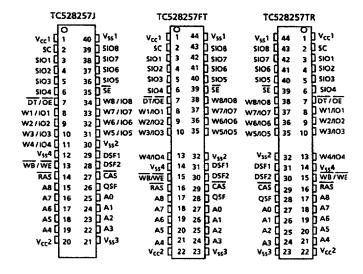

#### **PIN CONNECTION (TOP VIEW)**

2/62

TOSHIBA CORPORATION

■ 9097248 0027842 42T **■**

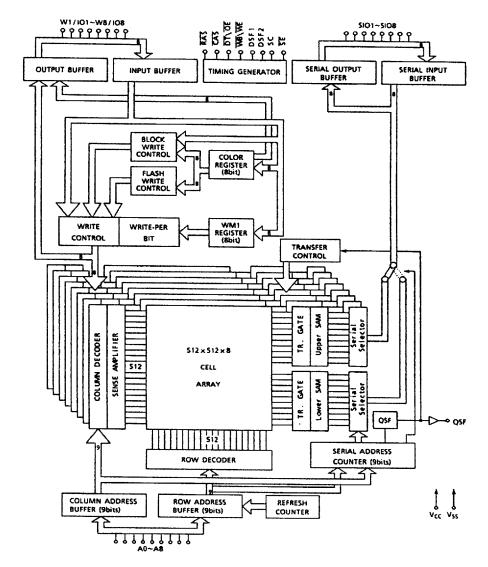

#### **BLOCK DIAGRAM**

3/62

**TOSHIBA CORPORATION**

**■ 366 E+87200 842790P**

#### TC528257

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL              | ITEM                         | RATING          | UNIT   | NOTE |

|---------------------|------------------------------|-----------------|--------|------|

| $V_{IN}, V_{OUT}$   | Input Output Voltage         | 1.0~7.0         | v      | 1    |

| v <sub>cc</sub>     | Power Supply Voltage         | - 1.0~7.0       | V      | 1    |

| T <sub>OPR</sub>    | Operating Temperature        | 0~70            | °C     | 1    |

| T <sub>STG</sub>    | Storage Temperature          | <b>— 55~150</b> | °C     | 1    |

| T <sub>SOLDER</sub> | Soldering Temperature • Time | 260-10          | °C•sec | 1    |

| $P_{D}$             | Power Dissipation            | 1               | w      | 1    |

| I <sub>OUT</sub>    | Short Circuit Output Current | 50              | mA     | 1    |

# RECOMMENDED D.C. OPERATING CONDITIONS (Ta = 0-70°C)

| SYMBOL          | PARAMETER            | MIN. | TYP. | MAX. | UNIT | NOTE |

|-----------------|----------------------|------|------|------|------|------|

| v <sub>cc</sub> | Power Supply Voltage | 4.5  | 5.0  | 5.5  | V    | 2    |

| $v_{iH}$        | Input High Voltage   | 2.4  | _    | 6.5  | V    | 2    |

| $V_{lL}$        | Input Low Voltage    | —1.0 | _    | 0.8  | V    | 2    |

# CAPACITANCE ( $V_{CC} = 5V$ , f = 1MHz, Ta = 25°C)

| SYMBOL          | PARAMETER                | MIN. | MAX. | UNIT |

|-----------------|--------------------------|------|------|------|

| C <sub>I</sub>  | Input Capacitance        |      | 7    |      |

| C <sub>IO</sub> | Input/Output Capacitance | _    | 9    |      |

| Co              | Output Capacitance (QSF) |      | 9    | pF   |

Note: This parameter is periodically sampled and is not 100% tested.

4/62

# D.C. ELECTRICAL CHARACTERISTICS (V $_{CC}$ = 5V $\pm$ 10%, Ta = 0~70°C)

| ITEM (RAM PORT)                                               | SAM PORT     | SYMBOL            | -70  |      | -80  |      | UNIT | NOTE    |

|---------------------------------------------------------------|--------------|-------------------|------|------|------|------|------|---------|

|                                                               | D.M. T. O.K. | BIMBOL            | MIN. | MAX. | MIN. | MAX. | ONI  | NOIL    |

| OPERATING CURRENT  RAS, CAS Cycling                           | Standby      | I <sub>CC1</sub>  |      | 100  | _    | 90   |      | 3, 4, 5 |

| $t_{RC} = t_{RC} \min$                                        | Active       | I <sub>CC1A</sub> | _    | 160  |      | 140  |      | 3, 4, 5 |

| STANDBY CURRENT $(\overline{RAS}, \overline{CAS} = V_{IH})$   | Standby      | I <sub>CC2</sub>  | _    | 10   | _    | 10   |      |         |

| in                                                            | Active       | I <sub>CC2A</sub> | _    | 65   | _    | 55   |      | 3, 4, 5 |

| RAS ONLY REFRESH CURRENT  RAS Cycling, CAS = V <sub>IH</sub>  | Standby      | I <sub>CC3</sub>  | -    | 100  | _    | 90   |      | 3, 4, 5 |

| $\begin{pmatrix} t_{RC} = t_{RC} \min. \end{pmatrix}$         | Active       | I <sub>CC3A</sub> | -    | 160  | _    | 140  |      | 3, 4, 5 |

| PAGE MODE CURRENT  RAS = V <sub>IL</sub> , CAS Cycling        | Standby      | I <sub>CC4</sub>  | _    | 90   | _    | 80   |      | 3, 4, 5 |

| $t_{PC} = t_{RC} \min$                                        | Active       | I <sub>CC4A</sub> |      | 150  | _    | 130  | mA.  | 3, 4, 5 |

| CAS BEFORE RAS REFRESH CURRENT  / RAS Cycling, CAS Before RAS | Standby      | I <sub>CC5</sub>  | _    | 100  | _    | 90   | "    | 3, 4, 5 |

| $t_{RC} = t_{RC} \min$                                        | Active       | I <sub>CC5A</sub> |      | 160  | _    | 140  |      | 3, 4, 5 |

| DATA TRANSFER CURRENT  / RAS, CAS Cycling                     | Standby      | I <sub>CC6</sub>  | _    | 135  | _    | 125  | ]    | 3, 4, 5 |

| $t_{RC} = t_{RC} \min$                                        | Active       | I <sub>CC6A</sub> | -    | 195  | _    | 175  |      | 3, 4, 5 |

| FLASH WRITE CURRENT  (RAS, CAS Cycling)                       | Standby      | I <sub>CC7</sub>  | _    | 100  |      | 90   |      | 3, 4, 5 |

| $t_{RC} = t_{RC} \min$                                        | Active       | I <sub>CC7A</sub> | _    | 160  | _    | 140  |      | 3, 4, 5 |

| BLOCK WRITE CURRENT  / RAS, CAS Cycling                       | Standby      | I <sub>CC8</sub>  |      | 110  | _    | 100  |      | 3, 4, 5 |

| $t_{RC} = t_{RC} \min$                                        | Active       | I <sub>CC8A</sub> | _    | 170  | _    | 150  |      | 3, 4, 5 |

| ITEM                                                                                     | SYMBOL            | MIN. | MAX | UNIT | NOTE |

|------------------------------------------------------------------------------------------|-------------------|------|-----|------|------|

| INPUT LEAKAGE CURRENT<br>$0V \le V_{IN} \le 6.5V$ , All other pins not under test = $0V$ | I <sub>I(L)</sub> | -10  | 10  | μА   |      |

| OUTPUT LEAKAGE CURRENT $0V \le V_{OUT} \le 5.5V$ , Output Disable                        | I <sub>O(L)</sub> | -10  | 10  | μА   | E    |

| OUTPUT "H" LEVEL VOLTAGE<br>I <sub>OUT</sub> = - 2mA                                     | V <sub>OH</sub>   | 2.4  | _   | v    |      |

| OUTPUT "L" LEVEL VOLTAGE<br>I <sub>OUT</sub> = 2mA                                       | V <sub>OL</sub>   | -    | 0.4 | v    |      |

5/62

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED A.C. OPERATING CONDITIONS ( $V_{CC}$ = 5V $\pm$ 10%, Ta = 0~70°C)(Notes: 6, 7, 8)

| SYMBOL            | PARAMETER                                   |      | -70                                              |      | -80      |      |          |

|-------------------|---------------------------------------------|------|--------------------------------------------------|------|----------|------|----------|

| SIMBUL            |                                             | MIN. | MAX.                                             | MIN. | MAX      | UNIT | NOTI     |

| t <sub>RC</sub>   | Random Read or Write Cycle Time             | 130  |                                                  | 150  |          |      |          |

| <sup>t</sup> RMW  | Read-Modify-Write Cycle Time                | 180  |                                                  | 200  |          |      |          |

| t <sub>PC</sub>   | Fast Page Mode Cycle Time                   | 45   |                                                  | 50   |          |      |          |

| 1 <sub>PRMW</sub> | Fast Page Mode Read-Modify-Write Cycle Time | 90   |                                                  | 90   |          |      |          |

| <sup>1</sup> RAC  | Access Time from RAS                        |      | 70                                               |      | 80       |      | 9, 15    |

| I <sub>AA</sub>   | Access Time from Column Address             |      | 35                                               |      | 40       |      | 9, 15    |

| I <sub>CAC</sub>  | Access Time from CAS                        |      | 20                                               |      | 20       |      | 9, 16    |

| L <sub>CPA</sub>  | Access Time from CAS Precharge              |      | 35                                               |      | 40       |      | 9, 16    |

| <sup>L</sup> CLZ  | CAS to Output in Low-Z                      | 0    |                                                  | 0    |          |      |          |

| OELZ              | OE to Output in Low-Z                       | 0    |                                                  | 0    |          | 1    |          |

| toff              | Output Buffer Turn-Off Delay                | 0    | 15                                               | 0    | 15       | 1    | 11       |

| t <sub>T</sub>    | Transition Time (Rise and Fall)             | 3    | 50                                               | 3    | 50       |      | 8        |

| t <sub>RP</sub>   | RAS Precharge Time                          | 50   |                                                  | 60   |          | 1    | $\vdash$ |

| t <sub>RAS</sub>  | RAS Pulse Width                             | 70   | 10000                                            | 80   | 10000    | 1    | $\vdash$ |

| 1 <sub>RASP</sub> | RAS Pulse Width (Fast Page Mode Only)       | 70   | 100000                                           | 80   | 100000   | 1    |          |

| l <sub>RSH</sub>  | RAS Hold Time                               | 20   |                                                  | 20   |          | 1    |          |

| <sup>1</sup> СSН  | CAS Hold Time                               | 70   |                                                  | 80   |          |      |          |

| <sup>L</sup> CAS  | CAS Pulse Width                             | 15   | 10000                                            | 20   | 10000    | 1    |          |

| t <sub>RCD</sub>  | RAS to CAS Delay Time                       | 20   | 50                                               | 20   | 60       | i    | 15       |

| t <sub>RAD</sub>  | RAS to Column Address Delay Time            | 15   | 35                                               | 15   | 40       | 1    | 15       |

| <sup>l</sup> RAL  | Column Address to RAS Lead Time             | 35   |                                                  | 40   |          | ns   | <u> </u> |

| t <sub>CRP</sub>  | CAS to RAS Precharge Time                   | 5    |                                                  | 5    | <u></u>  | 1    | -        |

| <sup>L</sup> CPN  | CAS Precharge Time                          | 10   |                                                  | 10   | <u> </u> | 1    | -        |

| <sup>L</sup> CP   | CAS Precharge Time (Fast Page Mode)         | 10   |                                                  | 10   |          | 1    |          |

| t <sub>ASR</sub>  | Row Address Set-Up Time                     | 0    |                                                  | 0    |          | 1    |          |

| t <sub>RAH</sub>  | Row Address Hold Time                       | 10   |                                                  | 10   |          | 1    |          |

| t <sub>ASC</sub>  | Column Address Set-Up Time                  | 0    |                                                  | 0    |          | 1    |          |

| t <sub>CAH</sub>  | Column Address Hold Time                    | 12   |                                                  | 15   |          | 1    |          |

| t <sub>RCS</sub>  | Read Command Set-Up Time                    | 0    |                                                  | 0    |          | 1    |          |

| t <sub>RCH</sub>  | Read Command Hold Time                      | 0    |                                                  | 0    |          | †    | 12       |

| t <sub>rrh</sub>  | Read Command Hold Time referenced to RAS    | 0    |                                                  | 0    |          | 1    | 12       |

| t <sub>wch</sub>  | Write Command Hold Time                     | 10   | · · · · · · · · · · · · · · · · · · ·            | 15   |          | 1    | <b></b>  |

| 1 <sub>WP</sub>   | Write Command Pulse Width                   | 10   | l                                                | 10   |          | 1    |          |

| t <sub>RWL</sub>  | Write Command to RAS Lead Time              | 20   |                                                  | 20   |          | 1    |          |

| <sup>L</sup> CWL  | Write Command to CAS Lead Time              | 15   | <del>                                     </del> | 20   | t        | 1    | -        |

| t <sub>DS</sub>   | Data Set-Up Time                            | 0    |                                                  | 0    |          | 1    | 13       |

| t <sub>DH</sub>   | Data Hold Time                              | 12   |                                                  | 15   | <u> </u> | 1    | 13       |

| twcs              | Write Command Set-Up Time                   | 0    |                                                  | 0    |          | 1    | 14       |

| t <sub>RWD</sub>  | RAS to WE Delay Time                        | 95   | <del>                                     </del> | 105  |          | 1    | 14       |

| t <sub>AWD</sub>  | Column Address to WE Delay Time             | 60   | <b>†</b>                                         | 65   |          | 1    | 14       |

| t <sub>CWD</sub>  | CAS to WE Delay Time                        | 45   |                                                  | 45   |          | 1    | 14       |

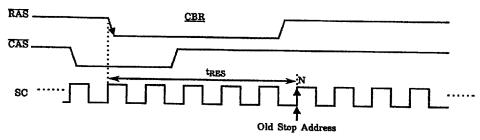

| t <sub>RES</sub>  | RAS to SC Boundary - reset time             | 30   | <del>                                     </del> | 30   | 1        |      | + -      |

6/62

| SYMBOL           | PARAMETER                                                                  | -70  |          | -80  |         |       | NOTE     |      |

|------------------|----------------------------------------------------------------------------|------|----------|------|---------|-------|----------|------|

| OTIMBOL          | TAKANETER                                                                  | MIN. | MAX      | MIN. | MAX.    | 70000 | UNIT     | NOTE |

| t <sub>DZC</sub> | Data to CAS Delay Time                                                     | 0    |          | 0    |         |       |          |      |

| t <sub>DZO</sub> | Data to OE Delay Time                                                      | 0    |          | 0    |         |       |          |      |

| t <sub>OEA</sub> | Access Time from OE                                                        |      | 20       |      | 20      |       | 9        |      |

| toez             | Output Buffer Turn-off Delay from OE                                       |      | 15       |      | 15      | 1     | 11       |      |

| t <sub>OED</sub> | OE to Data Delay Time                                                      | 15   |          | 15   |         |       |          |      |

| <sup>‡</sup> ОЕН | OE Command Hold Time                                                       | 15   |          | 15   |         | ns    |          |      |

| tods             | Output Disable Set up time                                                 | 0    |          | 0    |         | 1     |          |      |

| <sup>t</sup> roh | RAS Hold Time referenced to OE                                             | 15   |          | 15   |         | 1     |          |      |

| <sup>L</sup> CSR | CAS Set-Up Time for CAS Before RAS Cycle                                   | 5    |          | 5    |         |       |          |      |

| <sup>L</sup> CHR | CAS Hold Time for CAS Before RAS Cycle                                     | 10   |          | 15   |         | 1     |          |      |

| t <sub>RPC</sub> | RAS Precharge to CAS Active Time                                           | 0    |          | 0    |         | 1     |          |      |

| tref             | Refresh Period                                                             |      | 8        |      | - 8     | ms    |          |      |

| twsr             | WB Set-Up Time                                                             | 0    |          | 0    |         |       |          |      |

| t <sub>RWH</sub> | WB Hold Time                                                               | 10   |          | 15   |         | 1     |          |      |

| t <sub>FSR</sub> | DSF Set-Up Time referenced to RAS                                          | 0    |          | 0    |         | 1     |          |      |

| t <sub>RFH</sub> | DSF Hold Time referenced to RAS (1)                                        | 10   | -        | 15   |         | 1     |          |      |

| 1 <sub>FSC</sub> | DSF Set-Up Time referenced to CAS                                          | 0    |          | 0    |         | 1     |          |      |

| СЕН              | DSF Hold Time referenced to CAS                                            | 12   |          | 15   | ļ       | 1     | <b>-</b> |      |

| I <sub>MS</sub>  | Write-Per-Bit Mask Data Set-Up Time                                        | 0    |          | 0    |         | 1     |          |      |

| t <sub>MH</sub>  | Write-Per-Bit Mask Data Hold Time                                          | 10   |          | 15   |         | 1     | <b>-</b> |      |

| t <sub>THS</sub> | DT High Set-Up Time                                                        | 0    |          | 0    |         | 1     |          |      |

| t <sub>THH</sub> | DT High Hold Time                                                          | 10   |          | 15   |         | †     | $\vdash$ |      |

| t <sub>TLS</sub> | DT Low Set-Up Time                                                         | 0    |          | 0    | <b></b> | 1     |          |      |

| t <sub>TLH</sub> | DT Low Hold Time                                                           | 10   | 10000    | 15   | 10000   | 1     | -        |      |

| <sup>L</sup> RTH | DT Low Hold Time referenced to RAS<br>(Real Time Read Transfer)            | 60   | 10000    | 65   | 10000   | ns    |          |      |

| <sup>1</sup> ATH | DT Low Hold Time referenced to Column<br>Address (Real Time Read Transfer) | 25   |          | 25   |         | 1     |          |      |

| <sup>1</sup> СТН | DT Low Hold Time referenced to CAS (Real Time Read Transfer)               | 20   |          | 20   |         |       |          |      |

| t <sub>TRP</sub> | DT to RAS Precharge Time                                                   | 50   |          | 60   |         | 1     |          |      |

| t <sub>TP</sub>  | DT Precharge Time                                                          | 15   |          | 15   |         | 1     |          |      |

| t <sub>RSD</sub> | RAS to First SC Delay Time (Read Transfer)                                 | 70   |          | 80   |         | 1     |          |      |

| 1 <sub>ASD</sub> | RAS to First SC Delay Time (Read Transfer)                                 | 35   |          | 40   |         | 1     |          |      |

| t <sub>CSD</sub> | CAS to First SC Delay Time (Read Transfer)                                 | 20   |          | 20   |         | 1     |          |      |

| ITSL             | Last SC to DT Lead Time (Real Time Read Transfer)                          | 5    |          | 5    |         | 1     |          |      |

| t <sub>TSD</sub> | DT to First SC Delay Time (Read Transfer)                                  | 10   |          | 15   |         | 1     |          |      |

| t <sub>SRS</sub> | Last SC to RAS Set-Up Time (Serial Input)                                  | 25   |          | 30   |         | 1     |          |      |

| t <sub>SRD</sub> | RAS to First SC Delay Time (Serial Input)                                  | 20   | <b></b>  | 25   |         | 1     |          |      |

| t <sub>SDD</sub> | RAS to Serial Input Delay Time                                             | 45   | <u> </u> | 50   |         | 1     |          |      |

7/62

# TC528257

| SYMBOL            | PARAMETER                                             |          | 70                                               | -80         |                                                  |              |          |

|-------------------|-------------------------------------------------------|----------|--------------------------------------------------|-------------|--------------------------------------------------|--------------|----------|

| SIMBOL            | PARAMETER                                             | MIN.     | MAX.                                             | MIN.        | MAX.                                             | UNIT         | NOTE     |

| t <sub>SCC</sub>  | SC Cycle Time                                         | 25       |                                                  | 30          |                                                  |              |          |

| t <sub>SC</sub>   | SC Pulse Width (SC High Time)                         | 10       |                                                  | 10          |                                                  |              |          |

| 1 <sub>SCP</sub>  | SC Precharge Time (SC Low Time)                       | 5        |                                                  | 10          |                                                  |              |          |

| 1 <sub>SCA</sub>  | Access Time from SC                                   |          | 20                                               |             | 25                                               |              | 10       |

| <sup>1</sup> SOH  | Serial Output Hold Time from SC                       | 5        |                                                  | 5           |                                                  |              |          |

| l <sub>SDS</sub>  | Serial Input Set-Up Time                              | 0        |                                                  | 0           |                                                  |              |          |

| l <sub>SDH</sub>  | Serial Input Hold Time                                | 10       |                                                  | 15          |                                                  |              |          |

| I <sub>SEA</sub>  | Access Time from SE                                   |          | 20                                               |             | 25                                               |              | 10       |

| t <sub>SE</sub>   | SE Pulse Width                                        | 20       |                                                  | 25          |                                                  |              |          |

| t <sub>SEP</sub>  | SE Precharge Time                                     | 20       |                                                  | 25          |                                                  |              |          |

| t <sub>SEZ</sub>  | Serial Output Buffer Turn-off Delay from SE           |          | 15                                               |             | 20                                               |              | 11       |

| t <sub>SZE</sub>  | Serial Output Buffer Turn-off Delay from SE           | 0        |                                                  | 0           |                                                  |              |          |

| t <sub>SZS</sub>  | Serial Input to First SC Delay Time                   | 0        |                                                  | 0           |                                                  |              |          |

| t <sub>SWS</sub>  | Serial Write Enable Set-Up Time                       | 0        |                                                  | 0           |                                                  |              |          |

| t <sub>SWH</sub>  | Serial Write Enable Hold Time                         | 10       |                                                  | 15          |                                                  |              |          |

| 1 <sub>SWIS</sub> | Serial Write Disable Set-Up Time                      | 0        |                                                  | 0           |                                                  | 1            |          |

| t <sub>SWIH</sub> | Serial Write Disable Hold Time                        | 10       | ·                                                | 10          |                                                  | ļ            | <u> </u> |

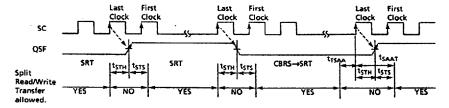

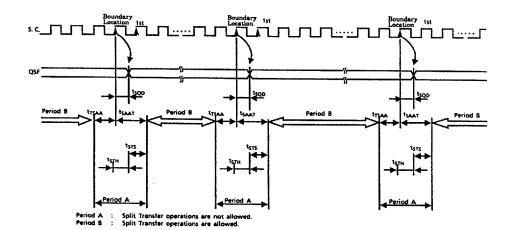

| t <sub>STS</sub>  | Split Transfer Set-Up Time                            | 25       |                                                  | 30          |                                                  |              |          |

| t <sub>STH</sub>  | Split Transfer Hold Time                              | 25       |                                                  | 30          |                                                  | i            |          |

| ISAAT             | Split Transfer SC Set-Up Time from RAS                | 45       |                                                  | 55          |                                                  | ns           |          |

| tSAA              | Split Transfer SC Hold Time from RAS                  | 0        |                                                  | 0           |                                                  | 1            | <u> </u> |

| t <sub>SQD</sub>  | SC-QSF Delay Time                                     | 1        | 20                                               |             | 25                                               | 1            | <b> </b> |

| t <sub>TQD</sub>  | DT-QSF Delay Time                                     |          | 20                                               |             | 25                                               | 1            | <b></b>  |

| <sup>L</sup> CQD  | CAS-QSF Delay Time                                    | <b></b>  | 20                                               |             | 25                                               | İ            |          |

| t <sub>RQD</sub>  | RAS-QSF Delay Time                                    | <u> </u> | 70                                               |             | 80                                               | 1            | <b></b>  |

| t <sub>RCDP</sub> | RAS to CAS Delay Time (Pipeline mode)                 | 20       | 40                                               | 20          | 45                                               |              |          |

| t <sub>CSHP</sub> | CAS Hold Time (Pipeline mode)                         | 50       | <b>†</b>                                         | 55          |                                                  | i            | <u> </u> |

| t <sub>RACP</sub> | Access Time from RAS (Pipeline mode)                  | <u> </u> | 90                                               |             | 95                                               | 1            |          |

| ₹CACI             | Access Time from CAS (1) (Pipeline mode)              | -        | 20                                               | <u> </u>    | 20                                               | 1            | 10       |

| <sup>L</sup> CAC2 | Access Time from CAS (2) (Pipeline mode)              |          | 50                                               |             | 50                                               | 1            | 10       |

| <sup>L</sup> CASP | CAS Pulse Width (Pipeline mode)                       | 10       | <del> </del>                                     | 10          |                                                  | 1            |          |

| t <sub>CPP</sub>  | CAS Precharge Time Pipeline mode)                     | 10       | <del>                                     </del> | 10          | <del>                                     </del> | 1            | -        |

| t <sub>PCP</sub>  | Fast Page Mode Cycle Time (Pipeline mode)             | 30       | <del>                                     </del> | 30          | <del>                                     </del> | 1            |          |

| <sup>t</sup> сон  | CAS Hold Time referenced to OE (Pipeline mode)        | 5        | <del> </del>                                     | 5           |                                                  | 1            |          |

| t <sub>RSH1</sub> | RAS Hold Time (1) (Pipeline mode)                     | 20       |                                                  | 20          | <del> </del>                                     | 1            | $\vdash$ |

| t <sub>RSH2</sub> | RAS Hold Time (2) (Pipeline mode)                     | 50       | 1                                                | 50          |                                                  | 1            |          |

| <sup>t</sup> CWLP | Write Command to CAS lead Time (Pipeline mode)        | 10       |                                                  | 10          |                                                  | 1            | -        |

| <sup>1</sup> CWP  | WE to CAS Delay Time (Pipeline mode)                  | 30       | <del></del>                                      | 30          |                                                  | 1            |          |

| LOFFP             | Outoff Buffer Turn-off Delay from RAS (Pipeline mode) | 0        |                                                  | <del></del> |                                                  | 1            | 11, 17   |

|                   | RAM Output Reference Level                            |          | <u></u>                                          | <u> </u>    | //0.8V                                           | <del>'</del> |          |

|                   | SAM Output Reference Level                            | +        |                                                  |             | 7/0.8V                                           |              |          |

|                   | RAM Output Load                                       | +        |                                                  |             | and 50PF                                         |              |          |

|                   | SAM Output Load                                       | +        |                                                  |             | and 30PF                                         |              |          |

8/62

TOSHIBA CORPORATION

**■ 9097248 0027848 948 ■**

#### NOTES:

- Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

- 2. All voltage are referenced to VSS.

- 3. These parameters depend on cycle rate.

- 4. These parameters depend on output loading. Specified values are obtained with the output open.

- Address can be changed once or less while RAS=V<sub>IL</sub>. In case of I<sub>CC4</sub>, it can be changed once or less during a fast page mode cycle (t<sub>PC</sub>).

- An initial pause of 200µs is required after power-up followed by any of 8 CAS before RAS initialization

cycles before proper device operation is achieved.

- 7. AC measurements assume  $t_T = 5$ ns.

- 8.  $V_{IH\,(min.)}$  and  $V_{IL\,(max.)}$  are reference levels for measuring timing of input signals. Also, transition times are measured between  $V_{IH}$  and  $V_{IL}$ .

- 9. RAM port outputs are measured with a load equivalent to 1 TTL load and 50pF.  $D_{OUT}$  reference levels :  $V_{OH}$  /  $V_{OL}$  = 2.0V / 0.8V.

- SAM port outputs are measured with a load equivalent to 1 TTL load and 30pF.

D<sub>OUT</sub> reference levels: V<sub>OH</sub> / V<sub>OL</sub> = 2.0V / 0.8V.

- t<sub>OFF</sub> (max.), t<sub>OEZ</sub> (max.), t<sub>OFFP</sub> (max.) and t<sub>SEZ</sub> (max.) define the time at which the outputs achieve the open circuit condition and are not referenced to output voltage levels.

- Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycles.

- These parameters are referenced to CAS leading edge of early write cycles and to WB / WE leading edge in OE-controlled-write cycles and read-modify-write cycles.

- 14. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min.), the cycle is an early write cycles and the data out pin will remain open circuit (high impedance) throughout the entire cycle; If t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min.), t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min.) and t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min.) the cycle is a read-modify-write cycle and the data out will contain data read from the selected cell: If neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- 15. Operation within the  $_{tRCD\ (max.)}$  limit insures that  $t_{RAC\ (max.)}$  can he met.  $t_{RCD\ (max.)}$  is specified as a reference point only: If  $t_{RCD}$  is greater than the specified  $t_{RCD\ (max.)}$  limit, then access time is controlled by  $t_{CAC}$ .

- 16. Operation within the t<sub>RAD</sub> (max.) limit insures that t<sub>RAC</sub> (max.) can be met. t<sub>RAD</sub> (max.) is specified as a reference point only: If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub> (max.) limit, then access time is controlled by t<sub>AA</sub>.

- 17. t<sub>OFFP</sub> timing is specified from either RAS or CAS rising edge, whichever occurs last.

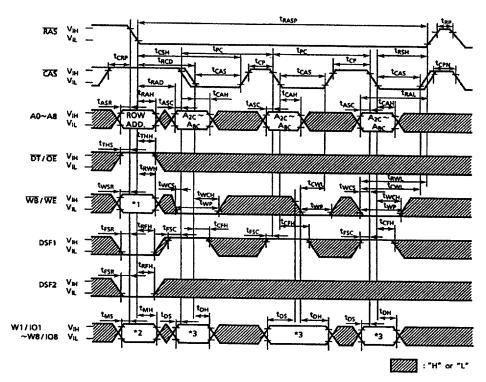

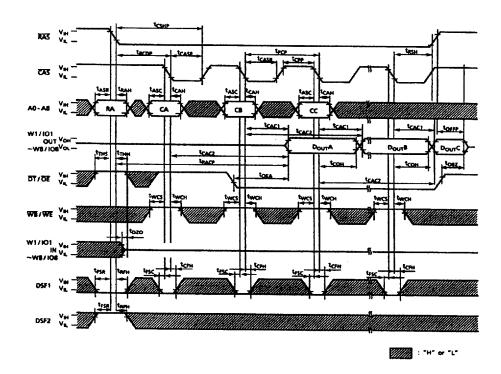

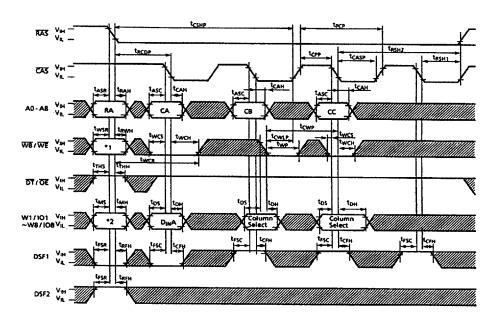

# TIMING WAVEFORM

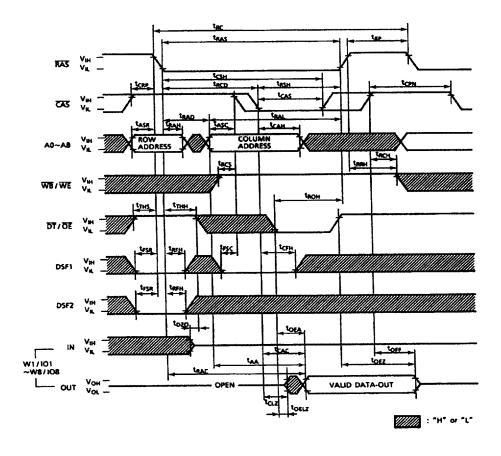

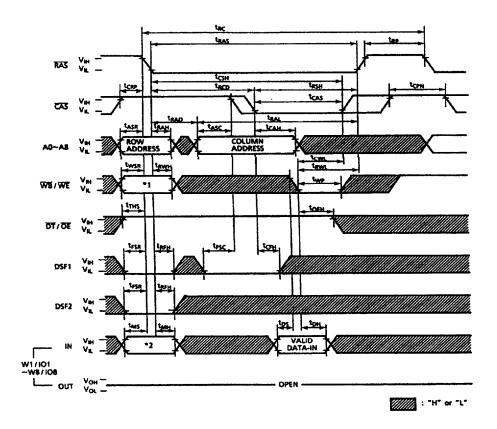

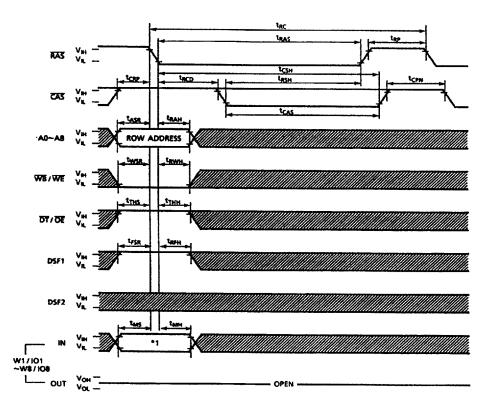

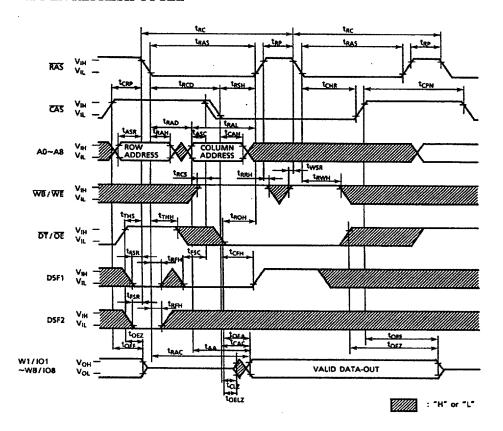

# READ CYCLE

10/62

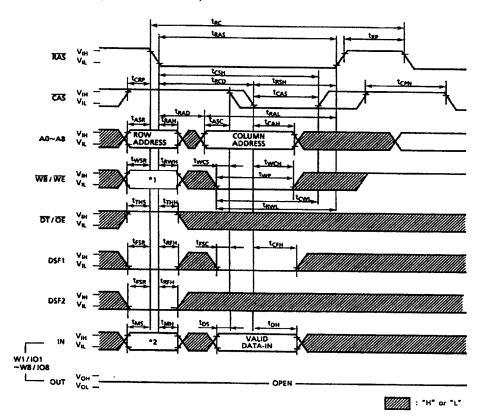

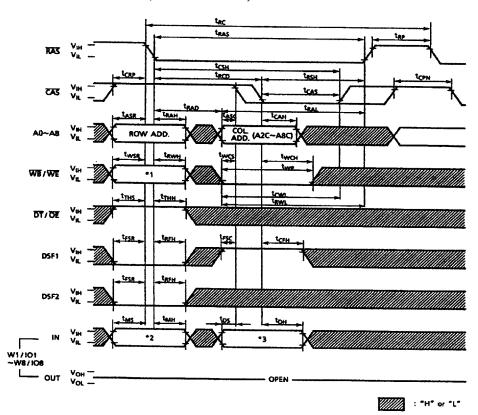

# WRITE CYCLE (EARLY WRITE)

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable 1: Write Enable

Don't care

: '1' or '0'

11/62

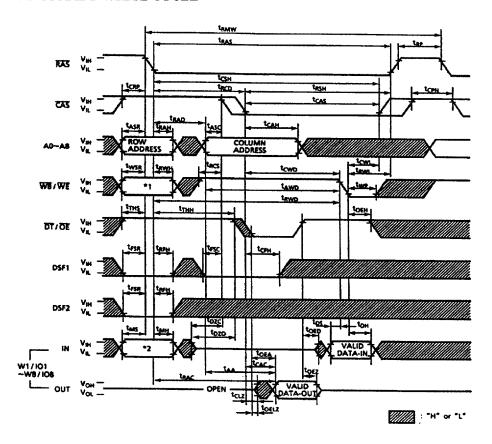

# WRITE CYCLE ( $\overline{\text{OE}}$ CONTROLLED WRITE)

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable

1: Write Enable

Don't care

: '1' or '0'

12/62

TOSHIBA CORPORATION

**9**097248 0027852 379 **3**

#### **READ-MODIFY-WRITE CYCLE**

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WMI data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable

Don't care

1: Write Enable

: '1' or '0'

13/62

TOSHIBA CORPORATION

9097248 0027853 205

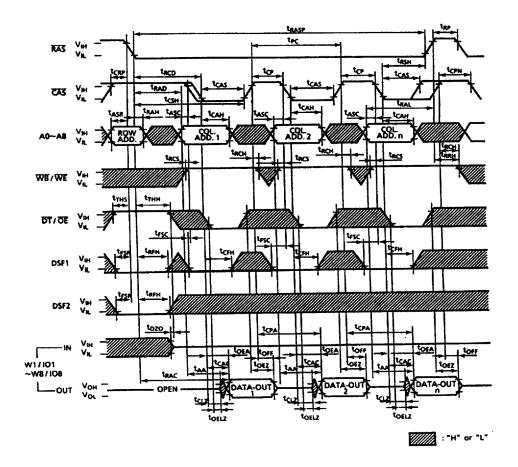

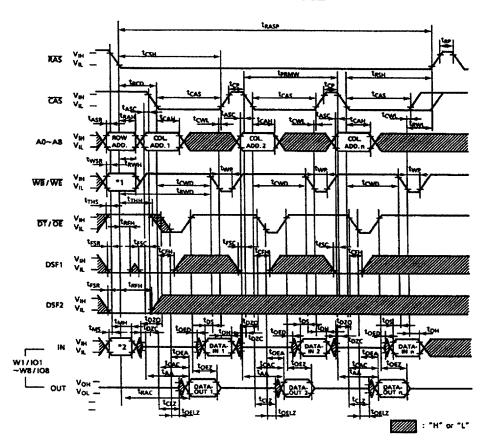

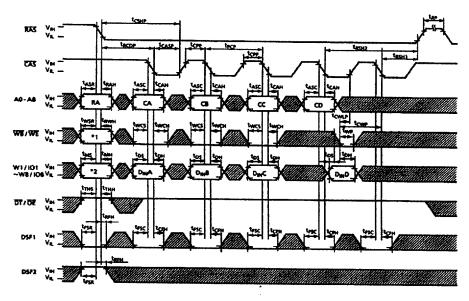

#### FAST PAGE MODE READ CYCLE

14/62

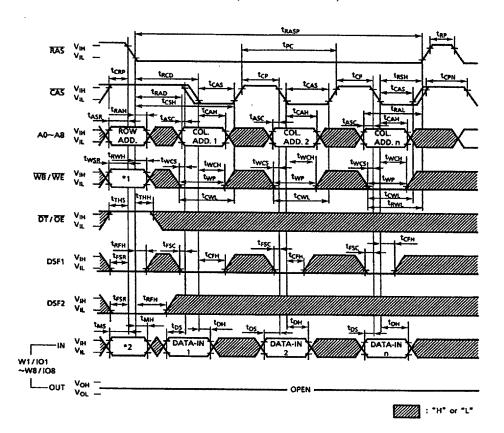

# FAST PAGE MODE WRITE CYCLE (EARLY WRITE)

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable

Don't care

1: Write Enable

: '1' or '0'

15/62

#### FAST PAGE MODE READ-MODIFY-WRITE CYCLE

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable 1: Write Enable

Don't care

: '1' or '0'

16/62

**TOSHIBA CORPORATION**

■ 9097248 0027856 T14 📟

#### FLASH WRITE CYCLE

| Mask Mode     | Cycle      |

|---------------|------------|

| New Mask Mode | WM1 data   |

| Old Mask Mode | Don't care |

WM1 data

0: Write Disable 1: Write Enable

Don't care

: '1' or '0'

17/62

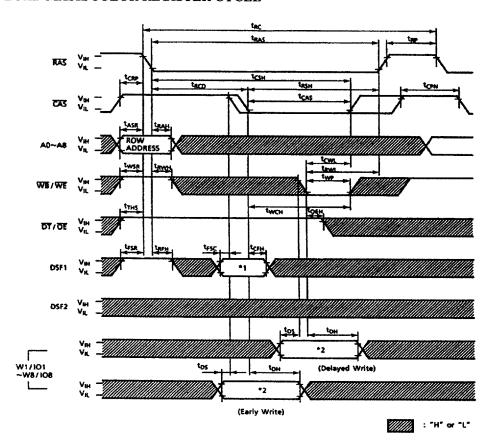

#### **BLOCK WRITE CYCLE (EARLY WRITE)**

| Mask Mode     | *1 | *2         |

|---------------|----|------------|

| No Mask Mode  | 1  | Don't care |

| New Mask Mode | 0  | WM1 data   |

| Old Mask Mode | 0  | Don't care |

\*3 COLUMN SELECT

$\begin{array}{l} \text{W1/IO1 - Column 0 } (A_{1C}=0,\,A_{0C}=0\\ \text{W2/IO2 - Column 1 } (A_{1C}=0,\,A_{0C}=1\\ \text{W3/IO3 - Column 2 } (A_{1C}=1,\,A_{0C}=0\\ \text{W4/IO4 - Column 3 } (A_{1C}=1,\,A_{0C}=1\\ \end{array} \\ \begin{array}{l} \text{Wn/IOn}\\ =0: \text{Disable}\\ =1: \text{Enable} \end{array}$

WM1 data

0: Write Disable

1: Write Enable

Don't care

: '1' or '0'

18/62

# BLOCK WRITE CYCLE (DELAYED WRITE)

\*3 COLUMN SELECT

| Mask Mode     | *1 | *2         |

|---------------|----|------------|

| No Mask Mode  | 1  | Don't care |

| New Mask Mode | 0  | WM1 data   |

| Old Mask Mode | 0  | Don't care |

WM1 data

0: Write Disable

1: Write Enable

Don't care

: '1' or '0'

able

19/62

TOSHIBA CORPORATION

= 0 : Disable = 1 : Enable

#### FAST PAGE MODE BLOCK WRITE CYCLE

| Mask Mode     | *1 | *2         |

|---------------|----|------------|

| No Mask Mode  | 1  | Don't care |

| New Mask Mode | 0  | WM1 data   |

| Old Mask Mode | 0  | Don't care |

\*3 COLUMN SELECT

= 0 : Disable = 1 : Enable

WM1 data

0: Write Disable

1: Write Enable

Don't care

: '1' or '0'

20/62

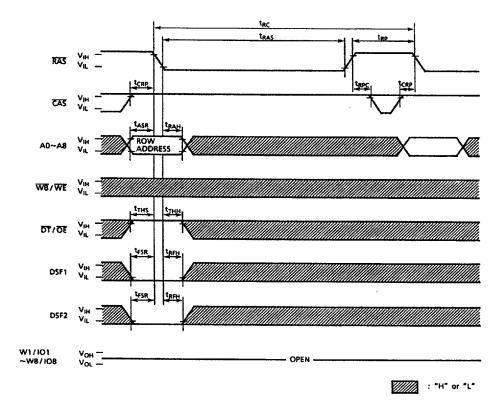

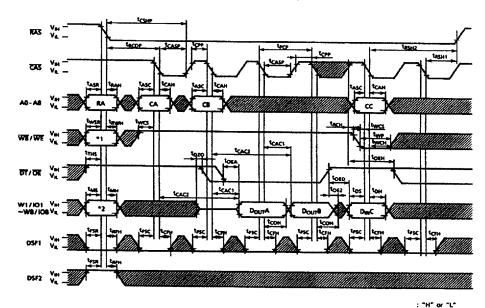

# **RAS** ONLY REFRESH CYCLE

21/62

#### HIDDEN REFRESH CYCLE

22/62

TOSHIBA CORPORATION

9097248 0027862 218

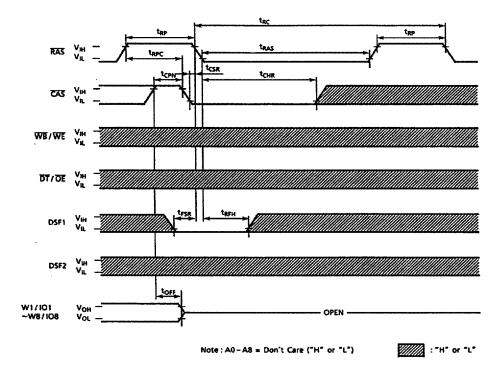

# CBR AUTO REFRESH CYCLE

23/62

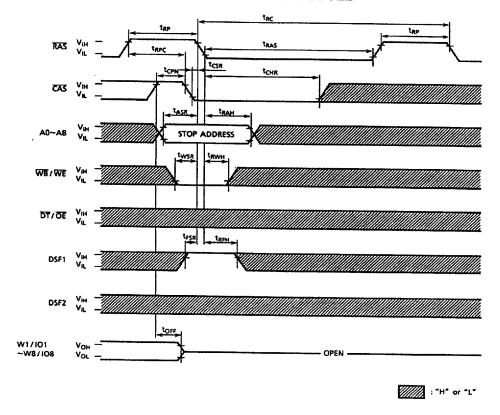

# CBR AUTO REFRESH & STOP REGISTER SET CYCLE

24/62

#### CBR AUTO REFRESH & RESET CYCLE

25/62

TOSHIBA CORPORATION

9097248 0027865 T27

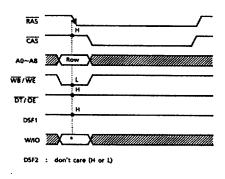

#### LOAD MASK/COLOR REGISTER CYCLE

| *1 | *2         | Function                  |

|----|------------|---------------------------|

| 0  | Mask data  | Load Mask Register Cycle  |

| 1  | Color data | Load Color Register Cycle |

26/62

#### READ MASK/COLOR REGISTER CYCLE

| *1 | *2         | Function                  |

|----|------------|---------------------------|

| 0  | Mask data  | Load Mask Register Cycle  |

| 1  | Color data | Load Color Register Cycle |

27/62

# PIPELINED FAST PAGE READ CYCLE

28/62

TOSHIBA CORPORATION

9097248 0027868 736

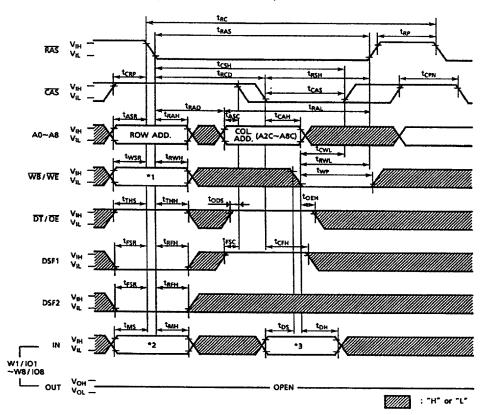

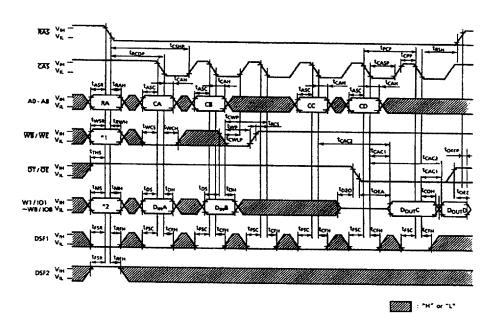

#### PIPELINED FAST PAGE WRITE CYCLE

| 111111 | ; | *H* | or | -L- |

|--------|---|-----|----|-----|

|        |   |     |    |     |

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable

1: Write Enable : '1' or '0'

Don't care

29/62

TOSHIBA CORPORATION

9097248 0027869 672 📟

#### PIPELINED FAST PAGE READ-WRITE CYCLE

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable

Don't care

1: Write Enable : '1' or '0'

30/62

TOSHIBA CORPORATION

**9097248 0027870 394**

# PIPELINED FAST PAGE WRITE-READ CYCLE

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

Don't care

WM1 data

0: Write Disable

Don't care

Old Mask Mode

1: Write Enable : '1' or '0'

31/62

TOSHIBA CORPORATION

Write per Bit

#### PIPELINED FAST PAGE WRITE-BLOCK WRITE CYCLE

|  | : | "H" | or | ~t." |  |

|--|---|-----|----|------|--|

|--|---|-----|----|------|--|

| Mask Mode     | *1 | *2         | Cycle         |

|---------------|----|------------|---------------|

| No Mask Mode  | 1  | Don't care | Normal Write  |

| New Mask Mode | 0  | WM1 data   | Write per Bit |

| Old Mask Mode | 0  | Don't care | Write per Bit |

WM1 data

0: Write Disable 1: Write Enable

Don't care

: '1' or '0'

32/62

TOSHIBA CORPORATION

**9**097248 0027872 167 **=**

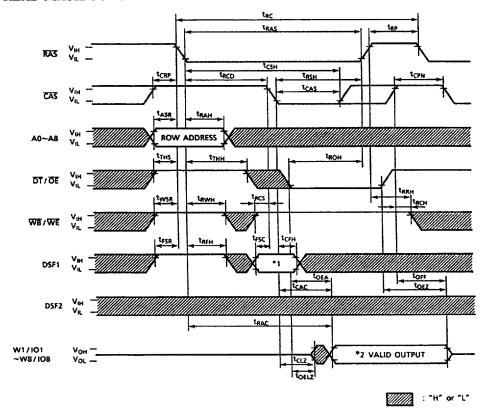

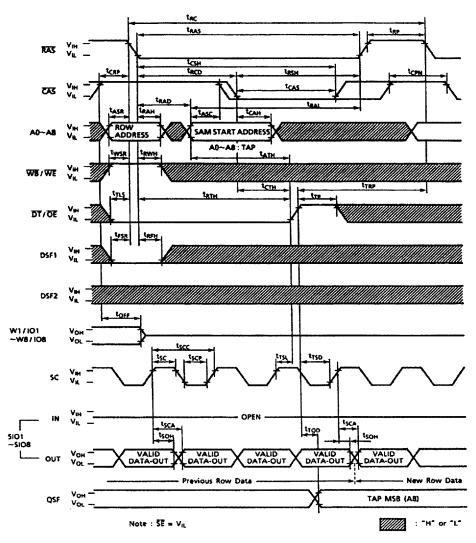

# READ TRANSFER CYCLE (Previous Transfer is Write Transfer Cycle)

33/62

# REAL TIME READ TRANSFER CYCLE

34/62 TOSHIBA CORPORATION

■ 9097248 0027874 T3T **■**

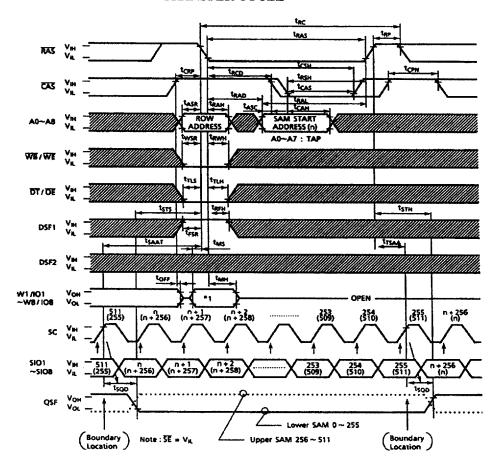

#### SPLIT READ TRANSFER CYCLE

35/62

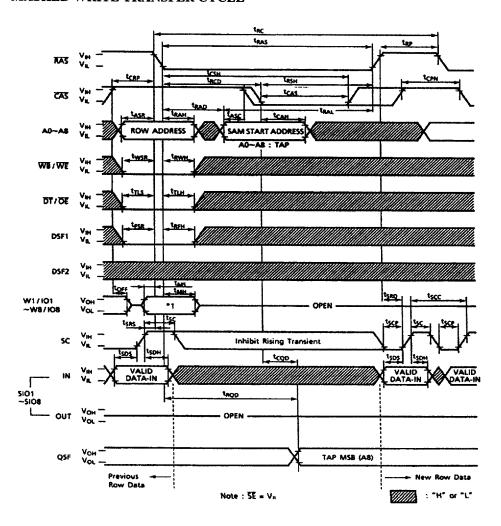

#### MASKED WRITE TRANSFER CYCLE

| Mask Mode     | *1         |  |

|---------------|------------|--|

| New Mask Mode | WM1 data   |  |

| Old Mask Mode | Don't care |  |

WM1 data

0: Write Disable 1: Write Enable

Don't care

: '1' or '0'

36/62

TOSHIBA CORPORATION

**---** 9097248 0027876 802 **---**

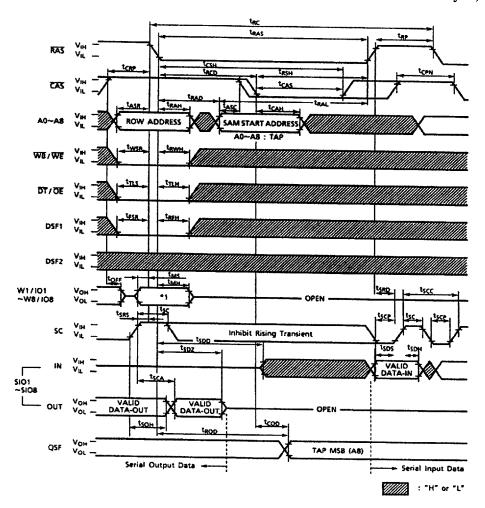

# MASKED WRITE TRANSFER CYCLE (Previous Transfer is Read Transfer Cycle)

| Mask Mode     | *1               |

|---------------|------------------|

| New Mask Mode | WM1 data         |

| Old Mask Mode | Don't care       |

| WM1 data      | 0: Write Disable |

1: Write Enable

Don't care

: '1' or '0'

37/62

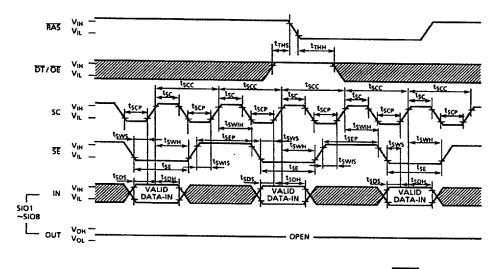

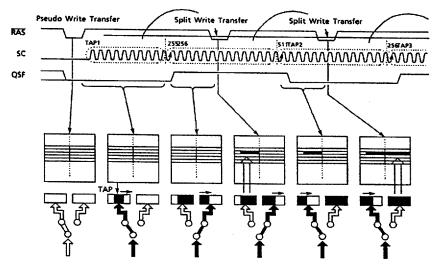

## MASKED SPLIT WRITE TRANSFER CYCLE

: "H" or "L"

| Mask Mode     | *1                               |  |  |  |

|---------------|----------------------------------|--|--|--|

| New Mask Mode | WM1 data                         |  |  |  |

| Old Mask Mode | Don't care                       |  |  |  |

| WM1 data      | 0: Write Disable 1: Write Enable |  |  |  |

| Don't care    | : '1' or '0'                     |  |  |  |

38/62

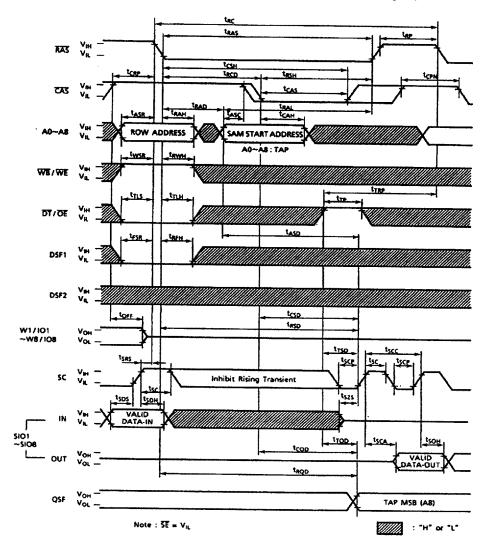

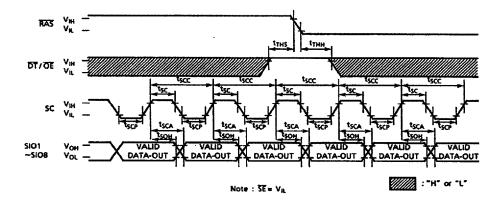

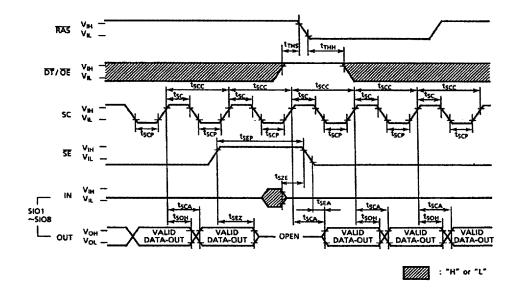

## SERIAL READ CYCLE $(\overline{SE} = V_{IL})$

## **SERIAL READ CYCLE (SE Controlled Outputs)**

39/62

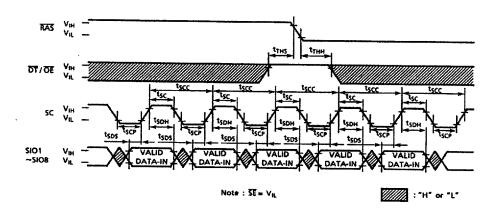

## SERIAL WRITE CYCLE $(\overline{SE} = V_{IL})$

## **SERIAL WRITE CYCLE (SE Controlled Inputs)**

: "H" or "L"

40/62

TOSHIBA CORPORATION

9097248 0027880 233

## PIN FUNCTION

## ADDRESS INPUTS: A<sub>0</sub>~A<sub>8</sub>

The 18 address bits required to decode 8 bits of the 2,097,152 cell locations within the dynamic RAM memory array and they are multiplexed onto 9 address input pins  $(A_0 \sim A_8)$ . Nine row address bits are latched on the falling edge of the row address strobe  $(\overline{RAS})$  and the following nine column address bits are latched on the falling edge of the column address strobe  $(\overline{CAS})$ .

### **ROW ADDRESS STROBE: RAS**

A random access cycle or a data transfer cycle begins at the falling edge of  $\overline{RAS}$ .  $\overline{RAS}$  is the control input that latches the row address bits and the states of  $\overline{CAS}$ ,  $\overline{DT/OE}$ ,  $\overline{WB/WE}$ , DSF1 and DSF2 to invoke the various random access and data transfer operating modes shown in Table 1.  $\overline{RAS}$  has minimum and maximum pulse widths and a minimum precharge requirement which must be maintained for proper device operation and data integrity. The RAM port is placed in standby mode when the  $\overline{RAS}$  control is held "high".

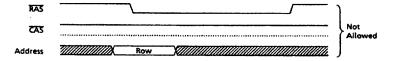

#### **COLUMN ADDRESS STROBE:** CAS

$\overline{\text{CAS}}$  is the control input that latches the column address bits which are also used for the tap address during the transfer operations. The state of the special function input DSF1 is read at the  $\overline{\text{CAS}}$  falling edge to select the block write mode or load register functions in conjunction with the  $\overline{\text{RAS}}$  control.  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh operations are selected if the signal is "low" at the  $\overline{\text{RAS}}$  falling edge.

#### DATA TRANSFER/OUTPUT ENABLE: DT/OE

The  $\overline{DT/OE}$  input is a multifunction pin. When  $\overline{DT/OE}$  is "high" at the falling edge of  $\overline{RAS}$ , RAM port operations are performed and  $\overline{DT/OE}$  is used as an output enable control. If it is "low", a data transfer operation is activated between the RAM and the SAM.

41/62

#### TC528257

## WRITE PER BIT/WRITE ENABLE: WB/WE

The  $\overline{WB/WE}$  input is also a multifunction pin. When the signal is "high" at the falling edge of  $\overline{RAS}$ , during the RAM port operations, it is used to write data into the memory array in the same manner as a standard DRAM. If the signal is "low" at the  $\overline{RAS}$  falling edge, the write-per-bit function is enabled. The  $\overline{WB/WE}$  input also determines the direction of data transfer between the RAM array and the SAM.

## WRITE MASK DATA/DATA INPUT AND OUTPUT: W1 /IO1~W8/IO8

Data is written into the RAM through  $W_1/IO_1 \sim W_8/IO_8$  pins during a write cycle. The input data is latched at the falling edge of either  $\overline{CAS}$  or  $\overline{WB/WE}$ , whichever occurs late. In a read cycle data is read out of the RAM on the  $W_i$  /  $IO_i$  pins after the specified access times from  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{DT/OE}$  and column address. The 4 least bits are also used as the column address mask during a block write cycle.

When the write-per-bit function is enabled, the mask data on the  $W_i/IO_i$  pins is latched into the write mask register at the falling edge of  $\overline{RAS}$ . In a load mask and color register cycles, the data on the  $W_i/IO_i$  pins is stored into the write mask register and the color register respectively.

## **SERIAL CLOCK: SC**

All operations of the SAM port are synchronized with the serial clock SC. Data is shifted in or out of the SAM registers at the rising edge of SC. The serial clock SC also increments the 9-bits serial pointer which is used to select the SAM address. The SC pin must be held at a constant V<sub>IH</sub> or V<sub>IL</sub> level during read and masked write transfer operations and should not be clocked while the SAM is in standby mode to prevent the SAM pointer from being incremented.

| 2/62 | TOSHIBA CORPORATION |

|------|---------------------|

|      |                     |

|      |                     |

9097248 0027882 006

#### SERIAL ENABLE: SE

The  $\overline{SE}$  input is used to enable serial access operation. In a serial read cycle,  $\overline{SE}$  is used as an output control. In a serial write cycle,  $\overline{SE}$  is used as a write enable control. When  $\overline{SE}$  is "high", serial access is disabled, however, the serial address pointer is still incremented while SC is clocked.

## SPECIAL FUNCTION CONTROL INPUT: DSF 1, DSF 2

DSF1 is latched at the falling edge of RAS and CAS to select the various TC5282571/Z/FT/TR operations. If the signal is kept "low", the basical functions featured in conventional multi-port DRAM are enabled. To use the block write, the flash write and the load register functions or the split transfer operations, the DSF1 signal needs to be controlled as shown in Table 1.

When the DSF2 signal is "high" at the falling edge of  $\overline{RAS}$ , pipelined page mode operations are enabled. The pipeline mode is supported with the read, write and block write functions.

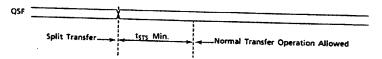

## SPECIAL FUNCTION OUTPUT: QSF

QSF is an output signal which, during split register mode, indicates which half of the split SAM is being accessed. QSF "low" indicates that the lower split SAM (Bit 0-255) is being accessed and QSF "high" indicates that the upper split SAM (Bit 256~511) is being accessed. QSF is monitored so that after it toggles and after allowing for a delay of t<sub>STS</sub>, split read/write transfer operation can be performed on the non-active split SAM.

## SERIAL INPUT/OUTPUT: SIO<sub>1</sub>, SIO<sub>8</sub>

Serial input and serial output share common I/O pins. Serial input or output mode is determined by the most recent read or masked write transfer cycle. After a read cycle, the SI/Oi pin is in the output mode. When a masked write transfer cycle is performed, the SI/Oi is switched from output mode to input mode,

#### **OPERATION MODE**

The RAM port and data transfer operating of the TG528257 are determined by the state of  $\overline{CAS}$ ,  $\overline{DT}/\overline{OE}$ ,  $\overline{WB}/\overline{WE}$ , DSF1 and DSF2 at the falling edge of  $\overline{RAS}$  and by the state of DSF1 at the falling edge of  $\overline{CAS}$ . The Table 1 shows the functional truth table for a listing of all available RAM port and transfer operations.

43/62

Table 1. Operaton Truth Table

|     |       | RAS   | _    |      | CAS → | Mnemonic Code | Function                                                   |  |  |

|-----|-------|-------|------|------|-------|---------------|------------------------------------------------------------|--|--|

| CAS | DT/OE | WB/WE | DSF1 | DSF2 | DSF1  | Whemome Code  | runction                                                   |  |  |

| 0   | *     | *     | 0    | *    | -     | CBR           | CBR Auto Refresh & Option Reset 1), 2)                     |  |  |

| 0   | *     | 0     | 1    | *    | -     | CBRS          | CBR Auto Refresh & Stop Register Set <sup>2)</sup>         |  |  |

| 0   | *     | 1     | 1    | *    | -     | CBRN          | CBR Auto Refresh                                           |  |  |

| ı   | 0     | 0     | 0    | *    | *     | MWT           | Write Transer (New/Old Mask) <sup>1)</sup>                 |  |  |

| ì   | 0     | 0     | 1    | *    | *     | MSWT          | Split Write Transfer (New/Old Mask) <sup>1)</sup>          |  |  |

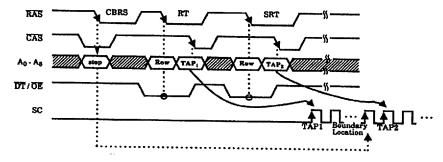

| 1   | 0     | 1     | 0    | *    | *     | RT            | Read Transfer                                              |  |  |

| 1   | 0     | 1     | 1    | *    | *     | SRT           | Split Read Transfer                                        |  |  |

| 1   | 1     | 0     | 0    | 0    | 0     | RWM           | Read Write (New/Old Mask)1)                                |  |  |

| 1   | 1     | 0     | 0    | 0    | 1     | вwм           | BlockWrite (New/Old Mask) <sup>1)</sup>                    |  |  |

| 1   | 1     | 0     | 1    | *    | *     | FWM           | FlashWrite (New/Old Mask) <sup>1)</sup>                    |  |  |

| 1   | 1     | 1     | 0    | 0    | 0     | RW            | Read Write (No Mask)                                       |  |  |

| 1   | 1     | 1     | 0    | 0    | 1     | BW            | Block Write (No Mask)                                      |  |  |

| 1   | 1     | 0     | 0    | 1    | 0     | RWM(P)        | PFP <sup>3)</sup> Read Write (New/Old Mask) <sup>1)</sup>  |  |  |

| 1   | 1     | 0     | 0    | 1    | 1     | BWM(P)        | PFP <sup>3)</sup> Block Write (New/Old Mask) <sup>1)</sup> |  |  |

| 1   | 1     | 1     | 0    | 1    | 0     | RW(P)         | PFP <sup>3)</sup> Read Write (No Mask)                     |  |  |

| 1   | 1     | 1     | 0    | 1    | 1     | BW(P)         | PFP <sup>3)</sup> Block Write (No Mask)                    |  |  |

| 1   | 1     | 1     | 1    | *    | 0     | LMR           | Load (Old) Mask Register <sup>1)</sup>                     |  |  |

| 1   | 1     | 1     | 1    | *    | 1     | LCR           | Load Color Register                                        |  |  |

Note:

- \* =0 or 1, = Not applicable

- After LMR operation, MWT, MSWT, RWM, BWM, FWM, RWM (P), BWM (P) use old mask. CBR operation resets the old mask mode to new mask mode.

- CBRS operation determines binary boundaries in the SAM. CBR operation resets the boundaries.

- 3) PFP stands for pipelined fast page mode

44/62

TOSHIBA CORPORATION

**9** 9097248 0027884 989 **5**

#### RAM PORT OPERATION

#### 1. READ WRITE FUNCTION: RW

The TC528257 is equipped with the read write function which is identical to the conventional dynamic RAM's one and supports read, early write,  $\overline{OE}$  controlled write and read-modify-write cycles as shown in the timing charts. Fast page and pipelined page modes are available with the read write cycles by performing multiple  $\overline{CAS}$  cycles during a single active  $\overline{RAS}$  cycle, a page.

## 2. WRITE-PER-BIT (MASKED WRITE) FUNCTION: RWM

The write-per-bit (masked write) function selectively controls the internal write enable circuits of the RAM port. When  $\overline{WB/WE}$  is held "low" at the falling edge of  $\overline{RAS}$ , during the RWM cycle, the write mask is enabled. At the same time, the mask data on the Wi/IOi pins is latched into the write-mask register. The I/O mask data maintains in a single  $\overline{RAS}$  cycle, a page (New Mask Mode). When a load mask register function (LMR) is performed, the write mask data on the Wi/IOi pins is latched into the write-mask register. After the LMR operation, the data at the falling edge of  $\overline{RAS}$  during the RWM cycle is ignored and the I/O mask data that was stored in the write-mask register is used (Old Mask Mode) until the mode is reset by CBR operation The truth table of the write-per-bit function is shown in Table 2.

Table 2. Truth table for write-per-bit function

|     | At the | falling edg | e of RAS                                | With Mad D          |                          |                          |  |

|-----|--------|-------------|-----------------------------------------|---------------------|--------------------------|--------------------------|--|

| CAS | DT/OE  | WB/WE       | W <sub>i</sub> /IO <sub>i</sub> (i=1~8) | Write Mask Register | Function                 |                          |  |

|     |        |             | 1                                       | <b>←</b>            | Write Enable             |                          |  |

| Н   | и      | L           | H L                                     | 0                   | <b>←</b>                 | Write Disable (New Mask) |  |

| "   | 11     |             | *                                       | 1                   | Write Enable             |                          |  |

|     |        |             | *                                       | 0                   | Write Disable (Old Mask) |                          |  |

Note: \* = 1 or 0,  $\leftarrow =$  The data on Wi/IOi is latched.

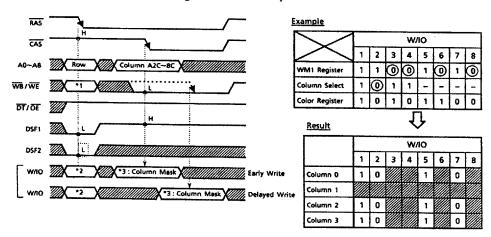

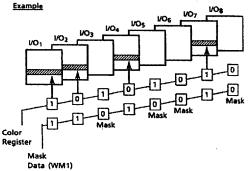

#### 3. BLOCK WRITE AND MASKED BLOCK WRITE: BW & BWM

Block write is a special RAM port write operation which, in a page, allows for the data in the color register to be written into 4 consecutive column address locations starting from a selected column address in a selected row. The block write operation can be selectively disabled on an I/O basis and a column mask capability is also available.

45/62

A block write cycle is performed by holding  $\overline{CAS}$ ,  $\overline{DT/OE}$  "high" and DSF1 "low" at the  $\overline{RAS}$  falling edge and by holding DSF1 "high" at the  $\overline{CAS}$  falling edge. If the DSF signal is "low" at the  $\overline{CAS}$  falling edge, a read write operation will occur. Therefore, a combination of block write, read and write operations can be performed during a fast page mode cycle. The state of  $\overline{WB/WE}$  input at the falling edge of  $\overline{RAS}$  determines whether or not the I/O mask is enabled ( $\overline{WB/WE}$  must be "low" to enable the I/O mask, BMW mode or "high" to disable it, BW mode). The I/O mask is provided on the Wi/IOi input at the  $\overline{RAS}$  falling edge. After LMR operation, however, the old mask is used for the I/O mask function. The column mask data on the Wi/IOi input must be provided at the  $\overline{CAS}$  or  $\overline{WB/WE}$  falling edge whichever is late, while the seven most significant column address (A2C~A8C) are latched at the falling edge of  $\overline{CAS}$ .

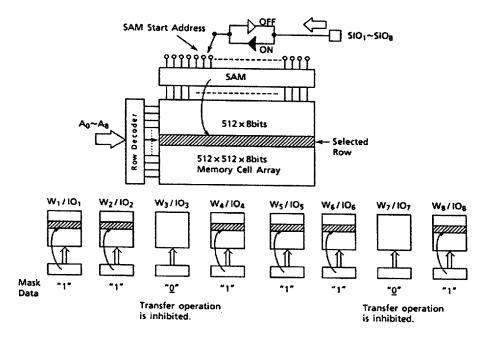

An example of the block write function is shown in Figure 1 with a mask on  $W_3/IO_3$ ,  $W_4/IO_4$ ,  $W_6/IO_6$ ,  $W_8/IO_8$  and column 1. The block write is most effective for window clear and fill operation in frame buffer applications.

Figure 1. Block Write Operation

| *1  | *2         | Mask Mode     |

|-----|------------|---------------|

| . 1 | Don't Care | No Mask Mode  |

| 0   | WM1        | New Mask Mode |

| 0   | Don't Care | Old Mask Mode |

## \*3 COLUMN SELECT

$\begin{array}{l} W_1 / IO_1 - Column~0~(A1C=0,~A0C=0\\ W_2 / IO_2 - Column~1~(A1C=0,~A0C=1\\ W_3 / IO_3 - Column~2~(A1C=1,~A0C=0\\ W_4 / IO_4 - Column~3~(A1C=1,~A0C=1\\ \end{array}$

46/62

**TOSHIBA CORPORATION**

**--** 9097248 0027886 75% **--**

#### 4. FLASH WRITE: FWM

Flash write is also a special RAM port operation which in a single RAS cycle, allows for the data in the color register to be written into all the memory locations of a selected row. Each bit of the color register corresponds to one of the DRAM I/O blocks and the flash write operation can be selectively controlled on an I/O basis in the same manner as the write-per-bit operation.

A flash write cycle is performed by holding CAS "high", WB/WE "low" and DSF1 "high" at the falling edge of RAS. The mask data must also be provided on the Wi/IOi inputs in order to enable the flash write operation for selected I/O blocks. After a LMR operation, however, the old mask in the mask register is used for the I/O block masking.

Flash write is most effective for fast plane clear operations in frame buffer applications. Selected planes can be cleared by performing 512 flash write cycle and by specifying a different row address location during each flash write cycle. Assuming a cycle time of 130ns, a plane clear operation can be completed in less than  $66.6 \mu$  sec.

Figure 2. Flash Write Operation

| *                   | Mask Mode     |

|---------------------|---------------|

| Mask Data           | New Mask Mode |

| Don't Care (H or L) | Old Mask Mode |

47/62

## 5. PIPELINED FAST PAGE MODE: RWM (P), BWM (P), RW (P), BW (P)

Pipelined fast page mode allows much faster access to the memory than the conventional page mode. Read, write and block write cycles are available at the pipelined fast page mode timings.

A pipelined fast page mode is performed by holding DSF2 "high" at the falling edge of  $\overline{RAS}$ . A pipelined fast page read, write and block write operations can run at 30ns cycle time for 70ns version. Also, those mode can be selected every  $\overline{CAS}$  cycle by the status of  $\overline{DT/OE}$ ,  $\overline{WB/WE}$  and DSF1 pin. There are, however, penalties on the performance as follows

- (1) Two CAS cycles are required for the read operation. The fast access, hence, takes longer than page mode. Also, one CAS cycle is needed to read out the data before the write cycle starts in the same page.

- (2) One dummy cycle is needed to complete the write and block write operation. The cycle is, thus, needed between the write and the read operation and is required before the page ends.

A system designer needs to carefully estimate the system performances with the pipelined page mode and the conventional page mode in order to decide which mode should be used.

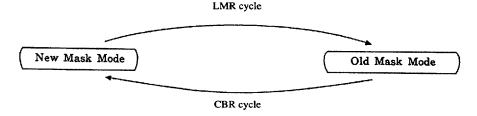

#### 6. LOAD (OLD) MASK REGISTER: LMR

The TC528257 has an on-chip 8-bit write-mask register which provides the I/O mask data during the masked functions such as the write-per-bit (RWM), masked block write (BWM), flash write (FWM) and write transfer (MWT, MSWT) functions. Each bit of the write-mask register corresponds to one of the DRAM I/O blocks. After the mask data is specified in the write-mask register by using the load mask register (LMR) cycle, the old mask mode is invoked during the masked functions. The I/O mask data in the write-mask register maintains until another LMR operation is performed during the old mask mode. The LMR cycle is initiated by holding  $\overline{CAS}$ ,  $\overline{DT/OE}$ ,  $\overline{WB/WE}$  and DSF1 "high" at the falling edge of  $\overline{RAS}$  and by DSF1 "low" at the falling edge of  $\overline{CAS}$ . The data presented on the Wi/IOi lines are subsequently latched into the write-mask register at the falling edge of either  $\overline{CAS}$  or  $\overline{WB/WE}$ , whichever occurs later. The old mask mode is reset to the new mask mode by a  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle (CBR). During the LMR cycle, the memory calls of the row address which is latched at the falling edge of  $\overline{RAS}$  are refreshed.

Figure 3. State Diagram of Mask Mode

48/62

**TOSHIBA CORPORATION**

9097248 0027888 524

#### 7. LOAD COLOR REGISTER: LCR

The TC528257 is provided with an on-chip 8-bits register (color register) for use during the block write or flash write function. Each bit of the color register corresponds to one of the DRAM I/O blocks. The load color register cycle is initiated by holding  $\overline{\text{CAS}}$ ,  $\overline{\text{WB/WE}}$ ,  $\overline{\text{DT/OE}}$  and DSF1 "high" at the falling edge of  $\overline{\text{RAS}}$ . The data presented on the Wi/IOi lines is subsequently latched into the color register at the falling edge of either  $\overline{\text{CAS}}$  or  $\overline{\text{WB/WE}}$ , whichever occurs later. During the load color register cycle, the memory cells on the row address latched at the falling edge of  $\overline{\text{RAS}}$  are refreshed.

#### 8. REFRESH

The data in the DRAM requires periodic refreshing to prevent data loss. Refreshing is accomplished by performing a memory cycle at each of 512 rows in the DRAM array within the specified 8 ms refresh period. The TC528257 supports the conventional dynamic RAM refresh operations such as  $\overline{RAS}$  only refresh,  $\overline{CAS}$  before  $\overline{RAS}$  refresh and hidden refresh.

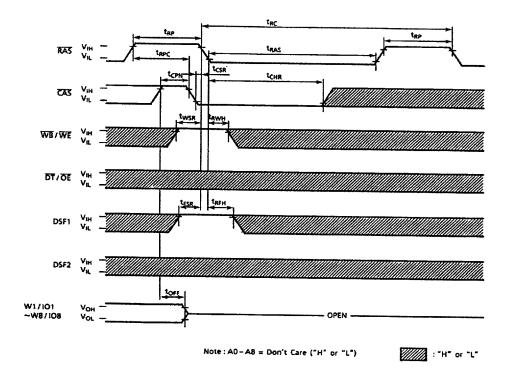

### 8.1 CAS before RAS Refresh and Option Reset: CBR

The CBR cycle reset the following functions, performing the  $\overline{CAS}$  before  $\overline{RAS}$  refresh operation at the same time.

- To reset the old mask mode to the new mask mode for the masked functions.

- · To reset the stop register and remove the binary boundaries for the split SAM operation,

The systems which implement neither the old mask mode nor the binary boundary in the SAM is recommended to use the CBR cycle for refresh operation.

| 10/00 |                     |

|-------|---------------------|

| 19/62 | TOSHIBA CORPORATION |

## 8.2 CAS before RAS Refresh: CBRN

The CBRN cycle performs only the  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh operation. The systems which implement either the old mask mode or the binary boundary in the SAM usually use the CBRN cycle for refresh operation except for at the required stop register set or option reset cycles. The CBRN cycle must not be used during the initialization after power-up.

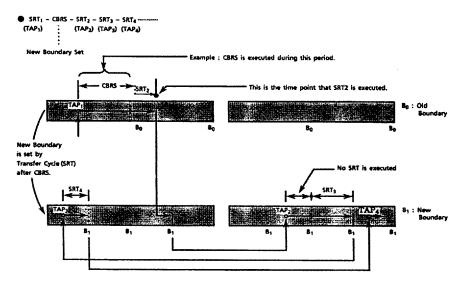

## 8.3 CAS before RAS Refresh and Stop Register Set: CBRS

The CBRS cycle sets the stop register to place binary boundaries in each half SAM, performing the  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh operation at the same time. The CBRS cycle is initiated by  $\overline{\text{CAS}}$  holding "low" and by  $\overline{\text{WB}}$  /WE and DSF1 "high" at the falling edge of  $\overline{\text{RAS}}$ . At the same time the data on the address pins,  $A_0$  -  $A_8$  is latched and the binary boundaries in each half SAM will be available when a split transfer operation is performed.

Figure 4 . Stop Register and Binary Boundary Location

| Stop Register Value<br>As - Ao | Binary Boundary Location                | ns                                                                                                                                                       |

|--------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01111111                       |                                         | Last Address of each block<br>255, 511 Default Case                                                                                                      |

| 001111111                      |                                         | 127, 255, 383, 511                                                                                                                                       |

| 000111111                      |                                         | 63, 127, 191, 255, 319, 383, 447, 511                                                                                                                    |

| 000011111                      |                                         | 31, 63, 95, 127, 159, 191, 223, 255, 287, 319, 351, 383, 415, 447, 479, 511                                                                              |

| 000001111                      |                                         | 15, 31, 47, 63, 79, 95, 111, 127, 143, 159, 175, 191, 207, 223, 239, 255, 271, 287, 303, 319, 335, 351, 367, 383, 399, 415, 431, 447, 463, 479, 495, 511 |

| 000000111                      | )                                       |                                                                                                                                                          |

| 000000011                      |                                         |                                                                                                                                                          |

| 000000001                      | These values are not allowed to be set. |                                                                                                                                                          |

| 000000000                      | J                                       |                                                                                                                                                          |

50/62 TOSHIBA CORPORATION

9097248 0027890 182

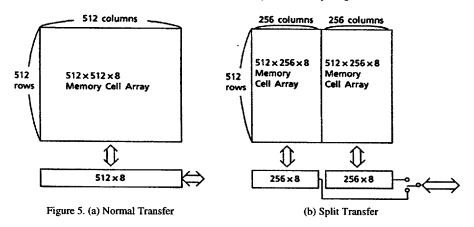

## **DATA TRANSFER OPERATION**

The TC528257 features two types of internal bidirectional data transfer capability between the RAM and the SAM, as shown in Figure 5. During a normal transfer, 512 words by 8-bits of data can be loaded from RAM to SAM (Read Transfer) or from SAM to RAM (Write Transfer), During a split transfer, 256 words by 8-bits of data can be loaded from the lower / upper half of the RAM into the lower / upper half of the SAM (Split Read Transfer) or from the lower/upper half of the SAM into the lower/upper half of the RAM (Split Write Transfer). The normal transfer and split transfer modes are controlled by the DSF1 input signal

Table 3. Shows the truth table of each Transfer Modes

|     | R     | AS    |      | Mnemonic | Mnemonic Transfer Mode              |                       | Transfer | 21177 117      |

|-----|-------|-------|------|----------|-------------------------------------|-----------------------|----------|----------------|

| CAS | DT/OE | WB/WE | DFS1 | Code     | Hanster Wode                        | Direction             | Bit      | SAM Port Mode  |

| Н   | L     | Н     | L    | RT       | Read Transfer                       | $RAM \rightarrow SAM$ | 512x8    | Input → Output |

| н   | L     | Ļ     | L    | WT       | Write Transfer (New/Old Mask)       | SAM → RAM             | 512x8    | Output → Input |

| Н   | L     | н     | Н    | SRT      | Split Read Transfer                 | RAM → SAM             | 256x8    | Not changed    |

| Н   | L     | L     | н    | SWT      | Split Write Transfer (New/Old Mask) | SAM → RAM             | 256x8    | Not changed    |

51/62

#### 9. READ TRANSFER CYCLE: RT

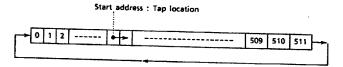

A read transfer consists of loading a selected row of data from the RAM array into the SAM register. A read transfer is invoked by holding  $\overline{CAS}$  "high",  $\overline{DT/OE}$  "low"  $\overline{WB/WE}$  "high" and DSF1 "low" at the falling edge of  $\overline{RAS}$ , The row address selected at the falling edge of  $\overline{RAS}$  determines the RAM row to be transferred into the SAM. At the same time, the SAM port is set into the output mode. The start address of the serial pointer of the SAM (TAP address) is determined by the column address selected at the falling edge of  $\overline{CAS}$ . By doing a tight timing control between the  $\overline{DT/OE}$  rising edge and SC falling edge, a real time read transfer operation can also be performed.

Figure 6 shows the operation block diagram for read transfer operation.

SAM

Serial Read

512 × 8bits

Selected Row

S12 × 512 × 8 bits

Memory Cell Array

Figure 6. Block Diagram for Read Transfer Operation

In a read transfer cycle (which is preceded by a write transfer cycle), the SC clock must be held at a constant  $V_{IL}$  or  $V_{IH}$ , after the SC high time has been satisfied. A rising edge of the SC clock must not occur until after the specified delay  $t_{TSD}$  from the rising edge of  $\overline{DT/OE}$  and the falling edge of  $\overline{RAS}$  and  $\overline{CAS}$ , as shown in READ TRANSFER CYCLE timing chart.

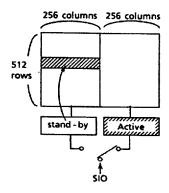

## 10. WRITE TRANSFER CYCLE: WT

A write transfer cycle consists of loading the content of the SAM register into a selected row of the RAM array. The write transfer is invoked by holding  $\overline{CAS}$  "high",  $\overline{DT/OE}$  "low",  $\overline{WB/WE}$  "low", and DSF1 "low" at the falling edge of  $\overline{RAS}$ . The row address selected at the falling edge of  $\overline{RAS}$  determines the RAM row address into which the data will be transferred. The column address selected at the falling edge of  $\overline{CAS}$  determines the start address of the serial pointer of the SAM (TAP address). After the write transfer is completed, the SIO lines are set in the input mode so that serial data synchronized with the SC clock can be loaded.

52/62

The write transfer is selectively controlled per RAM I/O block by setting the mask data on the Wi/IOi lines at the falling edge of RAS (some as in the write-per-bit operation). Before the serial clock starts loading the data into the SAM through SIO pins, the write transfer operation with all I/O blocks disabled must be performed in order to change the SAM port from output. Please note that the conventional pseudo write transfer is not available in the TC528257. The mask function is switched between the new and old mask mode by the LMR and CBR cycle.

Figure 7. Block Diagram for Write Transfer Operation

When consecutive write transfer operations are performed, new data must not be written into the serial register until the  $\overline{RAS}$  cycle of the preceding write transfer is completed. Consequently, the SC clock must be held at a constant  $V_{IL}$  or  $V_{IH}$  during the  $\overline{RAS}$  cycle. A rising edge of the SC clock is only allowed after the specified delay  $t_{SRD}$  from the rising edge of  $\overline{RAS}$ , at which time a new row of data can be written in the serial register.

53/62

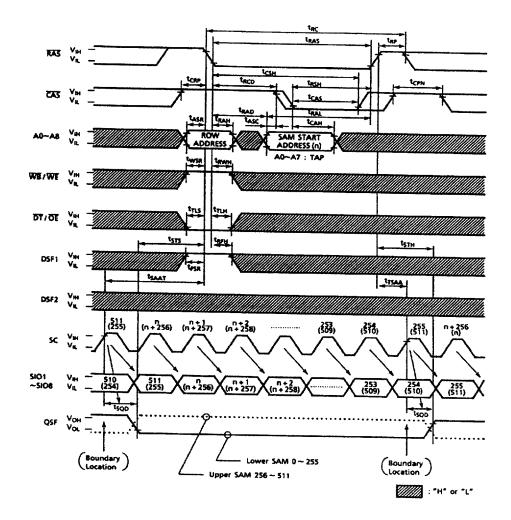

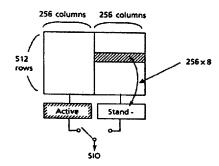

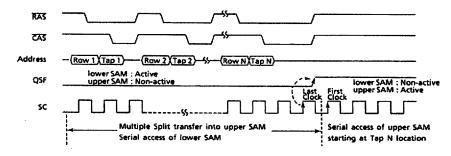

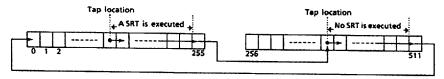

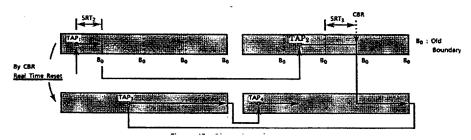

#### 11. SPLIT READ TRANSFER CYCLE: SRT

A split read transfer consists of loading 256 words by 8-bits of data from a selected row of the half RAM array into the corresponding half SAM in stand-by mode, Serial data can be shifted out of the other half of the SAM in active mode simultaneously, as shown in Figure 8. The most significant column address (A8C) is controlled internally to determine which half of the SAM will be reloaded from the RAM-array; During the split read transfer operation, the RAM port control signals do not have to be synchronized with the serial clock SC, thus eliminating the timing restrictions as in the case of real time read transfers. Prior to the execution of the split read transfer operation, a (normal) transfer operation must be performed to determine the absolute tap address location. QSF is an output that indicates which half of the SAM is in the active state.

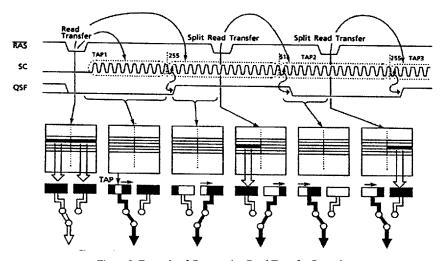

QSF changes state when the last SC clock is applied to the active SAM, as shown in Figure 9.

Figure 8. Split Read Transfer

Figure 9. Example of Consecutive Read Transfer Operations

54/62

**TOSHIBA CORPORATION**

**--** 9097248 0027894 828 **--**

#### 12. SPLIT WRITE TRANSFER: MSWT