# **VADEM VG-468**

# PC CARD SOCKET CONTROLLER

DATA MANUAL

**DECEMBER 1993**

REV. 02

Copyright © 1992 Vadem All Rights Reserved

Information furnished by Vadem is believed to be accurate and reliable. However, no responsibility is assumed by Vadem for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Vadem. Vadem reserves the right to change specifications at any time without notice.

Trademarks mentioned herein belong to their respective companies.

#### **Medical Disclaimer**

Vadem's products are not authorized for use in life support devices or systems or in any medical applications and cannot be used in such applications without the written consent of the President of Vadem.

# TABLE OF CONTENTS

#### Preface

| Product Overview . | <br> | <br> | 1 |

|--------------------|------|------|---|

| Product Features   | <br> | <br> | 2 |

#### **CHAPTER 1**

| Introduction       |   | <br> |   | 3 |

|--------------------|---|------|---|---|

| Signal Description | n | <br> | 4 | 4 |

| Pin Descriptions   |   | <br> |   | 6 |

#### **CHAPTER 2**

| Functional Description                      |

|---------------------------------------------|

| ISA Interface                               |

| PCMCIA/JEIDA PC Card Socket Interface       |

| PC Card Status                              |

| Control/Status Signal Multiplexers 14       |

| PC Card Insertion and Removal 14            |

| Memory and I/O Mapping 15                   |

| PC Card Memory Addressing 15                |

| PC Card I/O Addressing 17                   |

| Memory Paging                               |

| Attribute Memory Address Mapping 18         |

| Common Memory Address Mapping 18            |

| Power Management                            |

| Interrupt Handling                          |

| Configuration, Status and Control Registers |

| Register Addressing 19                      |

| Digital Audio Support 21                    |

| Full Vpp Support   21                       |

#### **CHAPTER 3**

| Register Summary           |

|----------------------------|

| General Setup Registers 23 |

| Interrupt Registers        |

| I/O Registers              |

| Memory Registers           |

| Unique Registers           |

#### **CHAPTER 4**

| Register Bit Declarations                                    |

|--------------------------------------------------------------|

| General Setup Registers 29                                   |

| Identification and Revision Register 00H, 40H 29             |

| Interface Status Register 01H, 41H 30                        |

| Power and RESETDRV Control Register 02H, 42H 31              |

| Card Status Change Register 04H, 44H 33                      |

| Address Window Enable Register 06H, 46H 35                   |

| Card Detect and General Control Register 16H, 56H 36         |

| Global Cotrol Register 39                                    |

| Interrupt Registers                                          |

| Interrupt and General Control Register 03H, 43H 41           |

| Card Status Change Interrupt Config. Register 05H, 45H 43    |

| I/O Registers                                                |

| I/O Control Register 07H, 47H 45                             |

| I/O Address Start Register Low Byte 08H, 0CH<br>48H, 4CH 46  |

| I/O Address Start Register High Byte 09H, 0DH<br>49H, 4DH 47 |

| I/O Address Stop Register Low Byte 0AH, 0EH<br>4AH, 4EH 47   |

| I/O Address Stop Register High Byte 0BH, 0FH<br>4BH, 4FH     |

| Memory Registers                                  |                                                                    |

|---------------------------------------------------|--------------------------------------------------------------------|

| System Memory Address Mapping                     |                                                                    |

| Start Register Low Byte                           |                                                                    |

|                                                   | 50H,58H,60H,68H,70H 48                                             |

| System Memory Address Mapping                     |                                                                    |

| Start Register High Byte                          |                                                                    |

|                                                   | 51,59H,61H,69H,71H 48                                              |

| System Memory Address Mapping                     |                                                                    |

| Stop Register Low Byte                            |                                                                    |

|                                                   | 52H,5AH,62H,6AH,72H 49                                             |

| System Memory Address Mapping                     |                                                                    |

| Stop Register High Byte                           | 13H,1BH,23H,2BH,33H<br>53H,5BH,63H,6BH,73H 49                      |

|                                                   | 55 <b>H</b> ,5 <b>B</b> H,05 <b>H</b> ,0 <b>B</b> H,75 <b>H</b> 49 |

| Card Memory Offset Address                        |                                                                    |

| Register Low Byte                                 | 14H,1CH,24H,2CH,34H<br>54H,5CH,64H,6CH,74H 50                      |

|                                                   | 5411,5011,0411,0011,7411 50                                        |

| Card Memory Offset Address<br>Register High Byte  | 1511 1011 2511 2011 2511                                           |

| Register High Byte                                | 55H,5DH,65H,6DH,75H 50                                             |

|                                                   |                                                                    |

| Unique Registers                                  |                                                                    |

| Control Register                                  | 38H, 78H 51                                                        |

| Timer Register                                    | 39H, 79H 53                                                        |

| Miscellaneous Register                            | 3AH, 7AH 54                                                        |

| GPIO Configuration Register                       | 3BH, 7BH 55                                                        |

| Programmable Chip Select Register                 | 3DH, 7DH 55                                                        |

| Programmable Chip Select Configuration Register - | 3EH, 7EH 56                                                        |

| ATA Register                                      | 3FH. 7FH                                                           |

|                                                   |                                                                    |

#### **CHAPTER 5**

| DC Specs and Maximum Ratings | 57 |

|------------------------------|----|

| DC Characteristics           | 57 |

| Capacitance                  | 57 |

| Absolute Maximum Ratings     | 57 |

| ICC Specifications           | 58 |

#### **CHAPTER 6**

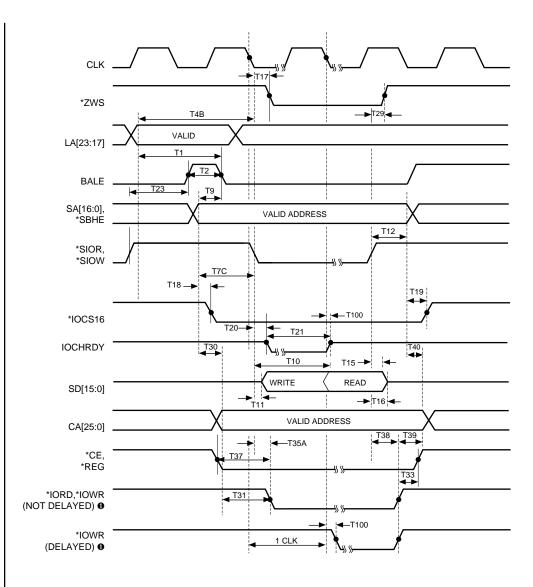

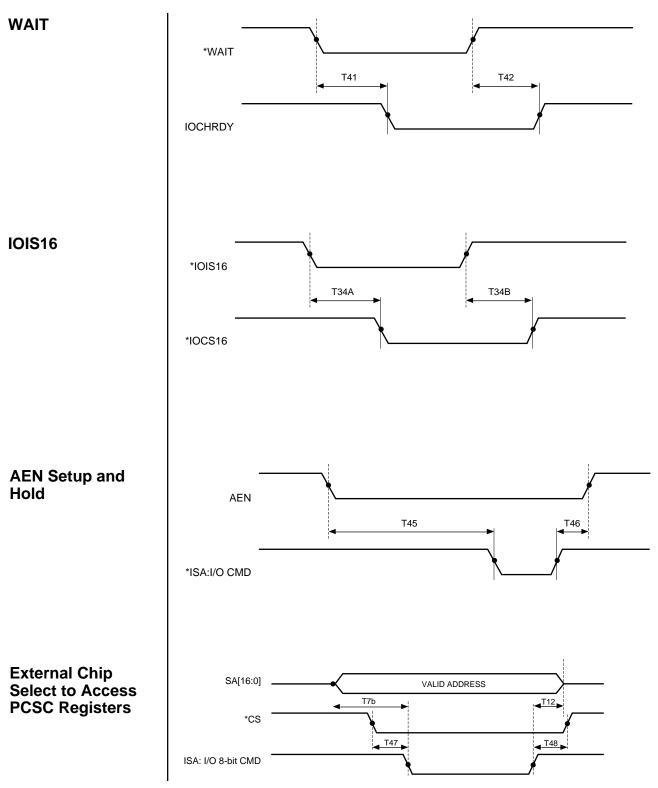

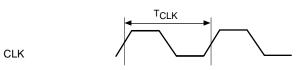

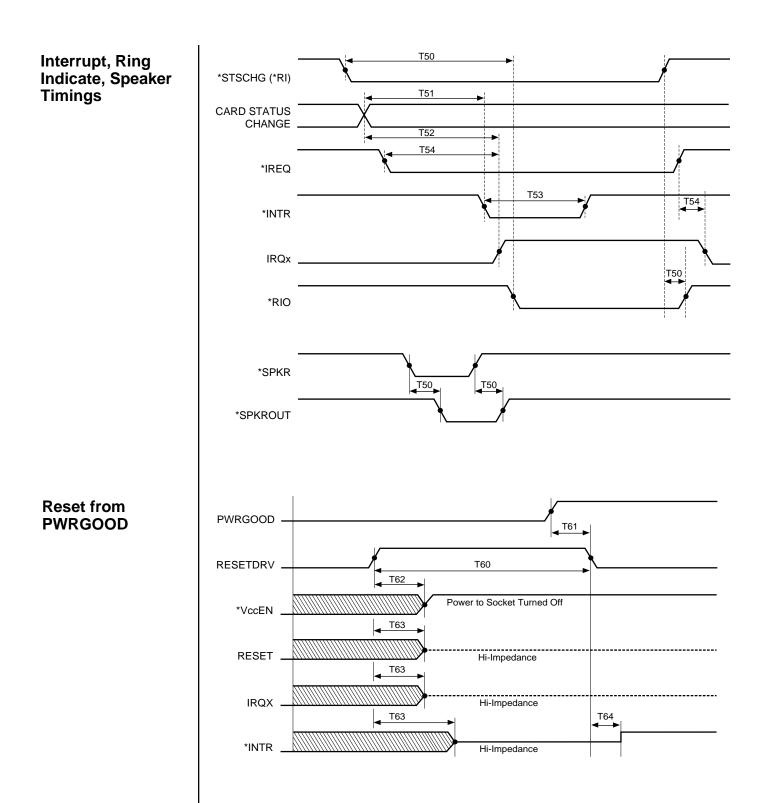

| AC Timing Diagrams 59                         |

|-----------------------------------------------|

| Memory: Standard/Extended/Zero Wait State 59  |

| I/O: Standard/Extended/Zero Wait State 60     |

| WAIT                                          |

| IOIS16                                        |

| AEN Setup and Hold                            |

| External Chip Select to Access PCSC Registers |

| CLK                                           |

| Interrupt, Ring Indicate, Speaker Timings     |

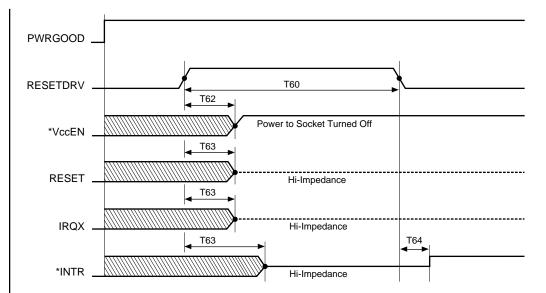

| Reset from PWRGOOD    63                      |

| Reset with Disable Resume 64                  |

#### CHAPTER 7

| AC Timing Table |  |  |  | 65 |

|-----------------|--|--|--|----|

|-----------------|--|--|--|----|

#### **CHAPTER 8**

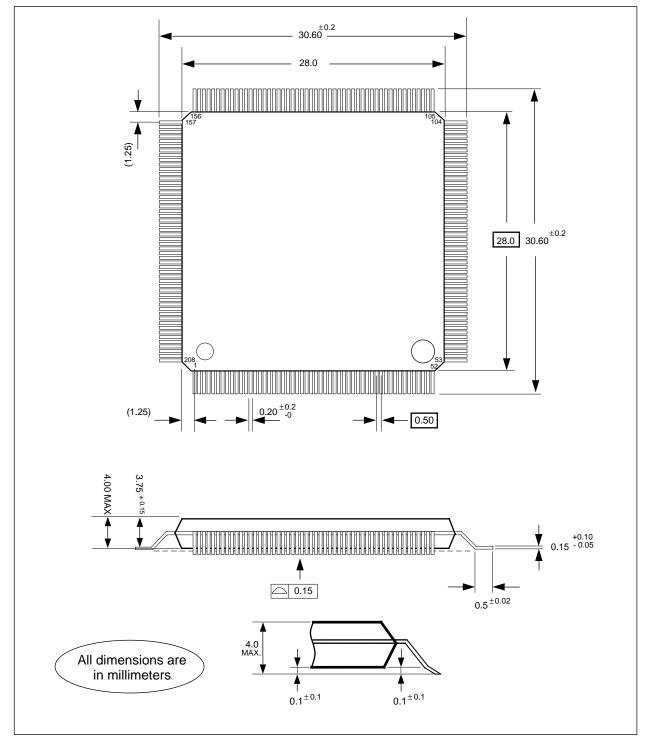

| Package Specification |  |  |  | <u>;</u> 9 |

|-----------------------|--|--|--|------------|

|-----------------------|--|--|--|------------|

#### List Of Illustrations

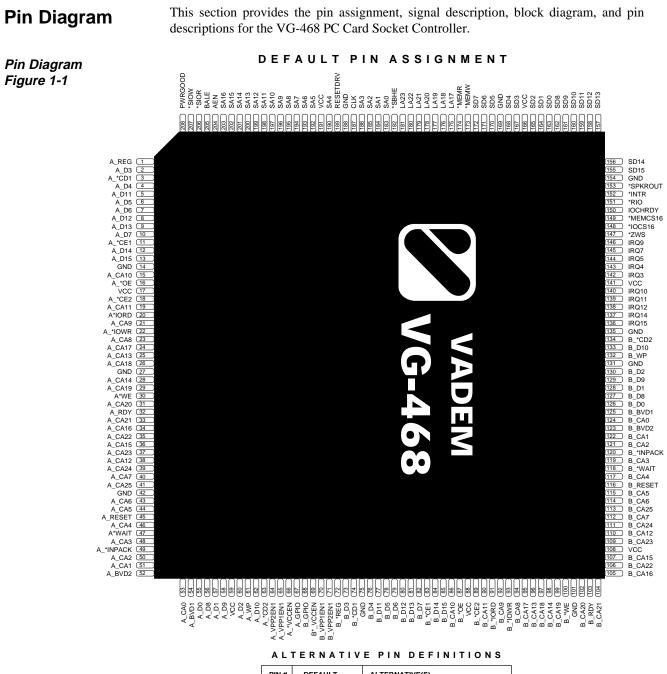

| VG-468 Pin Diagram                              | 3  |

|-------------------------------------------------|----|

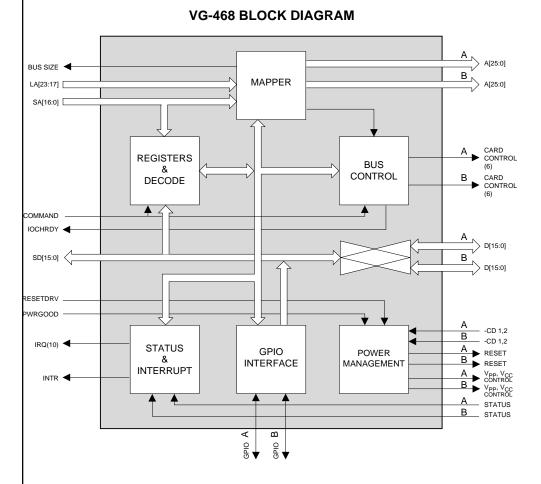

| VG-468 Functional Block Diagram 1               | 3  |

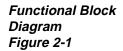

| Memory Map 1                                    | 6  |

| Package Specification (208 Lead Quad Flat Pack) | 59 |

### PRODUCT OVERVIEW

The Vadem VG-468 is a compact, highly integrated PC Card controller chip implementing the latest PCMCIA specifications along with ExCA<sup>TM</sup> extensions. It is register -compatible to the Intel<sup>®</sup> 82365SL. Supporting two PC Card sockets, it is uniquely designed for space-limited, cost-sensitive applications where battery life is an important factor. For systems requiring more than two sockets, the VG-468 can be cascaded to support up to eight sockets without external logic. With external decoder logic, unlimited cascading is possible. Typical VG-468 applications include small notebook computers, palmtops and other personal information devices.

The VG-468 supports the system bus timing of standard ISA and EISA architectures, including those based on the Intel 386SL. A programmable configuration mechanism allows the system manufacturer to control many PC Card setup parameters in software or firmware.

Power management based on activity monitoring together with the VG-468's very low current-draw combine to minimize its demand for battery power.

### PRODUCT FEATURES

- 208-pin chip provides full ExCA implementation of two PCMCIA PC Card sockets.

- Supports both memory cards and I/O cards (miniature peripherals).

- Supports PCMCIA-ATA hard disks and semiconductor disks.

- Memory-saving execute-in-place standard (XIP).

- Supports overlapping I/O windows across sockets and duplicate I/O cards via \*INPACK signal.

- All ExCA extensions.

- Cascadable up to eight sockets without "glue," unlimited cascading with external logic.

- Register-compatible with Intel 82365SL.

- Five mappable memory windows and two mappable I/O windows for each socket.

- Internal buffering supports "hot" insertion and removal of cards.

- Selectable programming voltage for various programmable devices.

- Integrated timer supports power management based on activity monitoring.

- Includes two GPIO pins.

# Chapter 1 Introduction

| PIN #  | DEFAULT  | ALTERNATIVE(S) |

|--------|----------|----------------|

| 32,103 | RDY/*BSY | *IREQ          |

| 52,123 | BVD2     | *SPKR          |

| 54,125 | BVD1     | *STSCHG, *RI   |

| 61,132 | WP       | *IOIS16        |

| 67,68  | GPIO     | *VPPVALID      |

(ALSO SEE PAGE 21)

#### **Signal Description**

| Pin #                                                                                                                                  | Signal Names       | Туре | Characteristics                               | # Pins |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-----------------------------------------------|--------|

| 204                                                                                                                                    | AEN                | Ι    | TTL Compatible                                | 1      |

| 205                                                                                                                                    | BALE               | Ι    | TTL Compatible                                | 1      |

| 54, 125                                                                                                                                | BVD1 (*STSCHG/*RI) | Ι    | CMOS Schmitt Trigger                          | 2      |

| 52, 123                                                                                                                                | BVD2 (*SPKR)       | Ι    | CMOS Schmitt Trigger                          | 2      |

| 15,19,21,<br>23-26,28,29<br>31,33-41,43<br>44,46,48,50<br>51,53,86,90<br>92,94-99,<br>102,104-107<br>109-115,117<br>119,121,122<br>124 | CA[25:0]           | 0    | 4mA Tri-State                                 | 52     |

| 63,3,134,74                                                                                                                            | *CD[2:1]           | Ι    | CMOS Schmitt Trigger                          | 4      |

| 89,83,18,11                                                                                                                            | *CE[2:1]           | 0    | 4mA Tri-State                                 | 4      |

| 187                                                                                                                                    | CLK                | Ι    | TTL Compatible                                | 1      |

| 2,4-10,12,13<br>55-58,60,62<br>73,76-82,84<br>85,126-130<br>133                                                                        | D[15:0]            | I/O  | I = TTL Compatible<br>O = 4mA Output          | 32     |

| 14,27,42,75<br>101,131,135<br>154,169,188                                                                                              | GND                |      |                                               | 10     |

| 67,68                                                                                                                                  | GPIO               | I/O  | I = CMOS Schmitt Trigger<br>O = 4mA Tri-State | 2      |

| 49,120                                                                                                                                 | *INPACK            | Ι    | TTL Compatible                                | 2      |

| 152                                                                                                                                    | *INTR              | I/O  | I = TTL Compatible<br>O = 4mA Tri-State       | 1      |

| 150                                                                                                                                    | IOCHRDY            | 0    | 16 mA Tri-State                               | 1      |

| 148                                                                                                                                    | *IOCS16            | 0    | 16 mA 5V Open Drain                           | 1      |

| 20,91                                                                                                                                  | *IORD              | 0    | 4mA Tri-State                                 | 2      |

| 22,93                                                                                                                                  | *IOWR              | 0    | 4mA Tri-State                                 | 2      |

| 136-140<br>146-142                                                                                                                     | IRQs               | 0    | 4mA Tri-State                                 | 10     |

# Signal Description (cont.)

| Pin #                                  | Signal Names     | Туре | Characteristics                         | # Pins |

|----------------------------------------|------------------|------|-----------------------------------------|--------|

| 181-175                                | LA[23:17]        | Ι    | TTL Compatible                          | 7      |

| 149                                    | *MEMCS16         | 0    | 16 mA 5V Open Drain                     | 1      |

| 174                                    | *MEMR            | Ι    | TTL Compatible                          | 1      |

| 173                                    | *MEMW            | Ι    | TTL Compatible                          | 1      |

| 16,87                                  | *OE              | 0    | 4mA Tri-State                           | 2      |

| 208                                    | PWRGOOD          | Ι    | Schmitt Trigger                         | 1      |

| 32,103                                 | RDY/*BSY (*IREQ) | Ι    | CMOS Schmitt Trigger                    | 2      |

| 1,72                                   | *REG             | 0    | 4mA Tri-State                           | 2      |

| 45,116                                 | RESET            | 0    | 4mA Tri-State                           | 2      |

| 189                                    | RESETDRV         | Ι    | Schmitt Trigger with pull-down          | 1      |

| 151                                    | *RIO/LED         | I/O  | I = TTL Compatible<br>O = 4mA Tri-State | 1      |

| 203-192,190<br>186-183                 | SA[16:0]         | Ι    | TTL Compatible                          | 17     |

| 182                                    | *SBHE            | Ι    | TTL Compatible                          | 1      |

| 206                                    | *SIOR            | Ι    | TTL Compatible                          | 1      |

| 207                                    | *SIOW            | Ι    | TTL Compatible                          | 1      |

| 155-162,<br>172-170,168<br>167,165-163 | SD[15:0]         | I/O  | I = TTL Compatible<br>O = 8mA Tri-State | 16     |

| 153                                    | *SPKROUT         | I/O  | I = TTL Compatible<br>O = 4mA Tri-State | 1      |

| 17,59,88,<br>108,141,166<br>191        | VCC              |      |                                         | 7      |

| 66,69                                  | *VCCEN           | 0    | 4mA Output                              | 2      |

| 65,70                                  | VPP1EN1          | 0    | 4mA Output                              | 2      |

| 64,71                                  | VPP2EN1          | 0    | 4mA Output                              | 2      |

| 47,118                                 | *WAIT            | Ι    | TTL Compatible                          | 2      |

| 30,100                                 | *WE/*PRGM        | 0    | 4mA Tri-State                           | 2      |

| 61,132                                 | WP (*IOIS16)     | Ι    | TTL Compatible                          | 2      |

| 147                                    | *ZWS             | 0    | 16mA 5V Open Drain                      | 1      |

#### **Pin Descriptions**

| Symbol                | Туре | Pin No.                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN                   | Ι    | 204                                                                                                                                      | System Address Enable. High during DMA cycles, low otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BALE                  | Ι    | 205                                                                                                                                      | Bus Address Latch Enable. An active high input used to latch LA[23:17] at the beginning of a bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                    |

| BVD1<br>(*STSCHG/*RI) | Ι    | 54,125                                                                                                                                   | If BVD1 is negated by a memory PC Card<br>with a battery, it indicates that the battery is<br>no longer serviceable and data is lost.                                                                                                                                                                                                                                                                                                                                                                      |

|                       |      |                                                                                                                                          | For I/O PC Cards, this signal is held high<br>when either or both the Signal on Change bit<br>and Changed bit in the Card Status Register<br>on the PC Card are set to zero. When both<br>the bits are one, the signal is held low. The<br>Changed bit is the logical OR of the bits<br>CVBAT1, CVBAT2, CWP and CBSYRDY<br>in the Pin Replacement Register on the PC<br>Card. Or this pin is connected to Ring<br>Indicate, which is qualified by Ring Indicate<br>Enable to be passed on to the *RIO pin. |

| BVD2<br>(*SPKR)       | Ι    | 52,123                                                                                                                                   | BVD1 and BVD2 are generated by memory<br>PC Cards with onboard batteries. These<br>signals indicate the health of the battery.<br>Both are asserted high when the battery is in<br>good condition. When BVD2 is negated<br>while BVD1 is still asserted, the battery<br>should be replaced, although data integrity on<br>the memory PC Card is still assured.                                                                                                                                             |

|                       |      |                                                                                                                                          | When the I/O interface is selected, BVD2<br>may be used to provide a single amplitude<br>Digital Audio waveform intended to be<br>passed through to the system's speaker<br>without signal conditioning.                                                                                                                                                                                                                                                                                                   |

| CA[25:0]              | Ο    | 15,19,21<br>23-26,28<br>28,31<br>33-41,43<br>44,46,48<br>50,51,53<br>86,90,92<br>94-99,102<br>104-107<br>109-115,11<br>119,121,12<br>124 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin | Descriptions |

|-----|--------------|

| (co | ntinued)     |

| Symbol   | Туре | Pin No.                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *CD[2:1] | Ι    | 63,3<br>134,74                                                           | Detects proper card insertion. The signals are<br>connected to ground internally on the PC<br>Card and will be forced low whenever a card<br>is placed in a host socket. Status is available<br>to software through the Interface Status<br>Register.                                                                                                                              |

| *CE[2:1] | 0    | 89,83<br>18,11                                                           | Active low card enable signals. *CE1 is used<br>to enable even bytes, *CE2 for odd bytes. A<br>multiplexing scheme based on A0, *CE1,<br>*CE2 allows 8-bit hosts to access all data on<br>Card Data[7:0] if desired.                                                                                                                                                               |

| CLK      | Ι    | 187                                                                      | System clock.                                                                                                                                                                                                                                                                                                                                                                      |

| D[15:0]  | I/O  | 2,4-10<br>12,13<br>55-58<br>60,62,73<br>76-82<br>84,85<br>126-130<br>133 | Card data.                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO     | I/O  | 67,68                                                                    | <ul> <li>General purpose input/output. May be used for one of several purposes.</li> <li>An active low input indicates that Vpp power line has reached the user specified range.</li> <li>An input indication a card eject or card insertion pending.</li> <li>An input source for generating a card status change interrupt.</li> <li>Programmable chip select output.</li> </ul> |

| *INPACK  | Ι    | 49,120                                                                   | Input Acknowledge. Asserted by some PC Cards during I/O read cycles. This signal is used by the VG-468 to control the enable of its input data buffer between the card and CPU.                                                                                                                                                                                                    |

Pin Descriptions (continued)

| Symbol    | Туре | Pin No.            | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *INTR     | I/O  | 152                | Interrupt Request output: Active low output<br>requesting a nonmaskable interrupt to the<br>CPU. Also, a resistor strapping input durin<br>RESETDRV to determine the mapping of<br>socket A and socket B to one of four groups.                                                                                                                                                                                        |

| IOCHRDY   | Ο    | 150                | I/O Channel Ready. This active high signal<br>indicates that the current I/O bus cycle has<br>completed. When a PC Card needs to exten<br>a Read or Write cycle, the VG-468 pull<br>IOCHRDY low. IOCHRDY can b<br>deasserted by either *WAIT, or b<br>programming to add wait states for 16-b<br>memory and I/O cycles. If *WAIT is used in<br>16-bit mode, the wait state generator has to<br>be set to 1 wait state. |

| *IOCS16   | Ο    | 148                | This active low I/O 16-bit chip select signal indicates to the host system the current I/C cycle is a 16-bit access. A 16-bit to 8-b conversion is done if it is inactive.                                                                                                                                                                                                                                             |

| *IORD     | 0    | 20,91              | I/O Read signal is driven active to read dat<br>from the PC Card's I/O space. The *REG<br>signal and at least one of the Card Enabl<br>signals must also be active for the I/O<br>transfer to take place.                                                                                                                                                                                                              |

| *IOWR     | 0    | 22,93              | I/O Write signal is driven active to write dat<br>to the PC Card's I/O space. The *REG signa<br>and at least one of the Card Enable signal<br>must also be active for the I/O transfer to<br>take place.                                                                                                                                                                                                               |

| IRQs      | 0    | 136-140<br>146-142 | IRQ[15, 14, 12:9, 7, 5:3].                                                                                                                                                                                                                                                                                                                                                                                             |

| LA[23:17] | Ι    | 181-175            | Local Address bus used to address memor<br>devices on the ISA-bus. Together with the<br>system address signals, they address up to<br>16MB on the ISA bus.                                                                                                                                                                                                                                                             |

| *MEMCS16  | 0    | 149                | This active low 16-bit memory chip select<br>signal indicates to the host system that the<br>current memory cycle is a 16-bit access. A<br>16-bit to 8-bit conversion is done if it is<br>inactive.                                                                                                                                                                                                                    |

| <b>Pin Descriptions</b> |

|-------------------------|

| (continued)             |

| Symbol              | Туре | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *MEMR               | Ι    | 174     | Active low signal indicates a memory read cycle.                                                                                                                                                                                                                                                                                                                                                               |

| *MEMW               | Ι    | 173     | Active low signal indicates a memory write cycle.                                                                                                                                                                                                                                                                                                                                                              |

| *OE                 | 0    | 16,87   | Active low signal used to gate memory reads from memory cards.                                                                                                                                                                                                                                                                                                                                                 |

| PWRGOOD             | Ι    | 208     | Power Good is an active high signal which<br>indicates that power to the system is stable.<br>Combined with RESETDRV, it will indicate<br>to VG-365 whether a cold reset, or a resume<br>reset has occurred, to decide whether to reset<br>the slot configuration registers. System<br>implementations without a "POWERGOOD"<br>as resume indication should tie this signal low.                               |

| RDY/*BSY<br>(*IREQ) | Ι    | 32,103  | Memory PC Cards drive Ready / *Busy low<br>to indicate that the memory card circuits are<br>busy processing a previous write command.<br>It is set high when they are ready to accept a<br>new data transfer command.                                                                                                                                                                                          |

|                     |      |         | For I/O PC Cards, this pin is used as an interrupt request and driven low to indicate to the host that a device on the I/O PC Card requires service by the host software. The signal is held at the inactive level when no interrupt is requested.                                                                                                                                                             |

| *REG                | Ο    | 1,72    | Select attribute memory. This signal is set<br>inactive (high) for all accesses to common<br>memory of a PC Card. When it is active,<br>access is limited to Attribute Memory when<br>*WE or *OE are active, and to I/O ports<br>when *IORD or *IOWR are active. I/O PC<br>Cards will not respond to *IORD or *IOWR<br>when the *REG signal is inactive. During<br>DMA operations the *REG signal is inactive. |

# Pin Descriptions (continued)

| Symbol   | Туре | Pin No.                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET    | 0    | 45,116                                     | Provides a hard reset to a PC Card and clears<br>the Card Configuration Option Register, thus<br>placing card in an unconfigured (memory<br>interface) state.                                                                                                                                                                                                                                                     |

| RESETDRV | Ι    | 189                                        | Active high indicates a main system reset.                                                                                                                                                                                                                                                                                                                                                                        |

| *RIO/LED | I/O  | 151                                        | Ring Indicate Output. Pass through of Ring<br>Indicate output from I/O PC Card. VG-460<br>can also be configured to activate *RIO of<br>card detect changes. *RIO will be functional<br>in *CS controlled power down. When dish<br>drive LED enable is set this signal becomes<br>driver for disk drive LED. Also, a resistor<br>strapping input during RESETDRV to<br>determine the functions of pin B_CA[11:4]. |

| SA[16:0] | Ι    | 203-192<br>190<br>186-183                  | System Address bus used to address memory<br>and I/O devices on the ISA bus. These<br>signals are latched and are valid throughout<br>the bus cycle.                                                                                                                                                                                                                                                              |

| *SBHE    | Ι    | 182                                        | System Byte High Enable. When asserted<br>this active low signal indicates that a dat<br>transfer is occurring on the upper byte of the<br>system data bus.                                                                                                                                                                                                                                                       |

| SD[15:0] | I/O  | 155-162,<br>172-170,<br>168,167<br>165-163 | System Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                  |

| *SIOR    | Ι    | 206                                        | This active low I/O read signal instructs the VG-468 to drive data onto the data bus.                                                                                                                                                                                                                                                                                                                             |

| *SIOW    | Ι    | 207                                        | This active low I/O write signal instructs the VG-468 to latch the data on the data bus.                                                                                                                                                                                                                                                                                                                          |

| *SPKROUT | I/O  | 153                                        | Digital audio signal which provides a single<br>amplitude (digital) audio waveform to drive<br>the system's speaker. Passes through *SPKF<br>from an I/O PC Card. This signal must be<br>held high when no audio signal is present<br>Also, a resistor strapping input during<br>RESETDRV to determine the mapping o<br>socket A and socket B to one of four groups.                                              |

# Pin Descriptions (continued)

| Symbol          | Туре | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *VCCEN          | 0    | 66,69   | Power Control signal for card Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VPP1EN1         | 0    | 65,70   | Power Control signal for card Vpp1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VPP2EN1         | 0    | 64,71   | Power Control signal for card Vpp2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *WAIT           | Ι    | 47,118  | This signal is driven by the PC Card to delay completion of the memory or I/O cycle in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *WE/*PRGM       | 0    | 30,100  | The host uses *WE for gating memory write data, and for memory PC Cards that employ programmable memory.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WP<br>(*IOIS16) | Ι    | 61,132  | Reflects the status of the Write Protect switch<br>on some memory PC Cards. If the memory<br>PC Card has no write protect switch, the card<br>will connect this line to ground (the card can<br>always be written) or to Vcc (permanently<br>write protected).                                                                                                                                                                                                                                                                  |

|                 |      |         | When the I/O interface is selected, this pin is<br>used for the "I/O is 16-bit Port" function:<br>asserted by the PC Card when the address on<br>the bus corresponds to an address to which<br>the PC Card responds, and the I/O Port<br>which is addressed is capable of 16-bit<br>access. If this signal is not asserted during a<br>16-bit I/O access, the system will generate 8-<br>bit references to the even and odd byte of the<br>16-bit port being accessed. If 8-bit window<br>size is selected, *IOIS16 is ignored. |

| *ZWS            | 0    | 147     | Zero Wait State. An active low output<br>indicates that the PC Card wishes to<br>terminate the present bus cycle without<br>inserting additional wait states. This cycle                                                                                                                                                                                                                                                                                                                                                        |

will not be driven during a 16-bit I/O access.

NOTES 🖎

This section provides a description of the functional blocks that comprise the VG-468 PC Card Socket Controller (VG-468). Chief functional blocks of the VG-468 include the ISA bus interface, PC Card socket interface, memory and I/O window mapping, power management support, interrupt handling, configuration, status and control registers and GPIO.

| ISA INTERFACE                               | The VG-468 interfaces directly to a synchronous or asynchronous ISA bus. No external buffers or transceivers are needed. For systems based on the 386SL, the VG-468 provides the special signals PWRGOOD, *SPKROUT, and *INTR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCMCIA/JEIDA PC<br>CARD SOCKET<br>INTERFACE | The 68-pin PCMCIA/JEIDA PC Card socket interface consists of 60 signals and 8 power connections. A single VG-468 supports two PC Card sockets directly. Up to eight PC Card sockets may be supported by cascading VG-468's. If an external decoder is used, any number of sockets can be supported. Each VG-468 is uniquely selected using pull-up/pull-down resistors (see Register Addressing section on page 19).                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PC Card Status                              | The status of the PC Card including detection of card insertion or removal, memory write protect status, battery voltage warnings, PC Card power status, and Ready/Busy is accessible through the interface status register. A change in status can cause a card status change interrupt (such as when a PC Card is inserted or removed). The various sources of the interrupt may be enabled separately.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Control/Status<br>Signal Multiplexers       | The VG-468 supports two PC Card types (either memory or I/O) interchangeably. A number of the PC Card signals have different uses based on the PC Card type. The VG-468 incorporates multiplexers to redirect the appropriate signals that are defined differently for memory and I/O PC Cards. These signals are configured correctly based upon the setting of the PC Card type bit in the Interrupt and General Control Register.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PC Card Insertion<br>and Removal            | The VG-468 incorporates power sequencing time delays specified by ExCA and PCMCIA, which can be enabled under software control.<br>When installing a card, there is a 65 ms minimum debounce time on the card detects. Card removal is detected immediately and is not debounced. Three bits in the Power and RESETDRV Control Register are involved: Output Enable, Auto Power Switch Enable, and PC Card Power Enable.<br>When installing a PC Card, if Auto Power Switch Enable and PC Card Power Enable are true, card power goes on after the debounce time. If Auto Power Switch Enable is false, PC Card Power Enable controls card power directly, and card detects have no effect on card power. At least 330 ms after debounced card detect is true and card power is on, the card interface signal outputs will be enabled if Output Enable is true. |

|                                             | When a PC Card is removed, the interface signal outputs are tristated after a minimum of 500 microseconds delay. If a bus cycle is in progress the outputs will not turn off until the end of the cycle. If Auto Power Switch Enable is true, card power also turns off 500 microseconds after that. If Auto Power Switch Enable is false, card power remains on.<br>At any time, clearing PC Card Output Enable tristates the card interface signal outputs immediately, and clearing PC Card Power Enable turns card power off immediately. When                                                                                                                                                                                                                                                                                                              |

|                                             | card power turns off, the card interface signal outputs also turn off immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MAPPINGI/O range. The VG-468 allows the operating system to map PC Card memory into u<br>separate memory ranges, and PC Card I/O into two separate I/O ranges, thus a<br>system configuration conflicts.The VG-468 provides I/O address mapping, memory paging and memory address n<br>for both PC Card attribute and common memory. The VG-468 includes register<br>provide access to the card information structure and card configuration registers w<br>Card's attribute memory described by the PCMCIA/JEIDA PC Card Standard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | napping<br>rs which                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| PC Card Memory<br>Addressing       The VG-468 provides logic to map portions of the 64MB common memory ad/or<br>attribute memory spaces found on PC Cards into the smaller 16MB system (ISA)<br>space. These mapping functions allow expansion of the system address space up to<br>64MB PC Card capability.         The VG-468 supports 5 independently enabled and controlled system memory<br>mapping windows. Each system memory window may map into either the con<br>attribute memory space of the PC Card and may independently control memory<br>width, system bus wait states, software write protect, and card enable.         Mapping of each system memory window starts and stops on any 4K byte boundar<br>system memory above 64K. The VG-468 does not allow mapping of a system<br>window between 0 and 64K in the system address space. Only I/O address wind<br>allowed to be mapped into that range. This limitation allows the VG-468 to resolved<br>when accessing I/O PC Cards that contain memory. | address<br>o the full<br>address<br>nmon or<br>data bus<br>y of ISA<br>memory<br>lows are |

#### **Opening a Window**

To open a window, software sets the system memory start address (Start), system memory stop address (Stop), and PC Card memory offset appropriately. If Start = Stop, the minimum size of 4K bytes is realized. The offset address is set by the software to be equal to the 2's complement of the difference between Start and the start address of the PC Card , and is added to the system address to generate the address for the PC Card.

PC Card memory is accessed only when all of the following conditions are satisfied:

- 1. The system memory address mapping window is enabled.

- 2. The system memory address is greater than or equal to the system memory address mapping start register A[23:12].

- 3. The system memory address is less than or equal to the system memory address mapping stop register A[23:12].

|                           | <ul> <li>All the system memory address mapping windows can be configured by software to be independently used, or can be used together for special memory mapping requirements, like LIM/EMS or XIP.</li> <li>Multiple ROM executable images on a single PC Card may be organized by the system memory address mapping windows. These images must be aligned to start on a 4 K byte boundary of the memory PC Card. Software can access these ROM executable images by setting the size of a system memory address mapping window to the size of the executable image (minimum 4 K block), and setting the PC Card memory offset from the system memory start address (Start) to generate the address of the first byte of the executable image on the PC Card.</li> <li>The PC Card memory offset can be either a positive or negative value. Furthermore, the VG-</li> </ul> |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | 468 does not check for a window whose size and offset allow it to wrap from the last PC Card address to the first PC Card address. <i>Software must check to prevent address wrapping</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PC Card I/O<br>Addressing | The ISA system bus is limited to 768 bytes of common I/O address space between I/O addresses 100H and 3FFH. The VG-468 supports system I/O address decode from 0 to 64K. A PC Card can request specific common I/O address locations or it can request a block of I/O space by the size required. When I/O space is requested by size, the system is free to locate the PC Card anywhere in the 64K system I/O address space. The PC Card decodes the *CE[2:1], *IORD, and *IOWR signals to respond to an I/O access.                                                                                                                                                                                                                                                                                                                                                          |

|                           | The VG-468 provides two independently enabled and controlled I/O address windows which are defined by 16-bit addresses to achieve a 1 byte resolution. Each window has independent control of I/O data bus width, zero wait state system bus access, and generation of *IOCS16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                           | A PC Card I/O address is accessed only when all of the following conditions are satisfied:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                           | 1. The I/O address window is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           | <ol> <li>The system address is greater than or equal to the I/O address start register A[15:0].</li> <li>The system address is less than or equal to the I/O address stop register A[15:0].</li> <li>The access is not a DMA transfer. AEN = 0 to access the I/O PC Card.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           | It is the responsibility of the system software to account for each I/O address range assigned to a particular PC Card. The reservation of a particular I/O address range for each PC Card can reduce card power consumption since only one PC Card is enabled during each I/O access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                           | The VG-468 can directly map the system I/O address space to the PC Card I/O ports with single byte granularity. Each PC Card is guaranteed a reserved system I/O address space, and an I/O cycle will be generated to the PC Card only within the assigned space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Memory Paging                       | System memory paging is supported in the VG-468 through the use of multiple system memory address mapping windows. When using LIM or XIP, software should assign a window to each page required to support the LIM/XIP function. The software has the responsibility to set up the system memory address mapping windows to be in one contiguous system address space with each window controlling a single page in the PC Card memory. When changing the page pointer only the PC Card memory offset address value needs to be altered to change the mapping. |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Attribute Memory<br>Address Mapping | PC Card attribute memory can be accessed through any of the system memory address<br>mapping windows. Software sets the REG active bit in the Card Memory Offset Address<br>Register to one. The system memory window to attribute memory can be mapped from any<br>ISA address above 64K to any PC Card address.<br>Multiple system memory address mapping windows to separate attribute memory address<br>and a compared simultaneously. Each of these windows can be configured to use a                                                                    |

|                                     | spaces can be opened simultaneously. Each of these windows can be configured to use a different number of wait states, software write protect, and data width.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Common Memory<br>Address Mapping    | PC Card common memory can be accessed through any of the system memory address<br>mapping windows. Software sets the REG active bit in the Card Memory Offset Address<br>Register to zero. The system memory window into PC Card common memory can be<br>mapped from any ISA address above 64K to any PC Card memory address.                                                                                                                                                                                                                                  |

|                                     | Multiple system memory address mapping windows into separate PC Card common<br>memory address spaces can be opened simultaneously. Each of these windows can be<br>configured to use a different number of wait states, software write protect, and data width.                                                                                                                                                                                                                                                                                                |

| POWER<br>MANAGEMENT                 | The VG-468 implements power management for each PC Card socket. Programming the Power and RESETDRV control register controls socket power management. Power sequencing time delays specified by ExCA and PCMCIA are implemented in hardware.                                                                                                                                                                                                                                                                                                                   |

|                                     | The VG-468 will automatically enter into lower power consumption state when memory windows and I/O windows are disabled, and when sockets become empty. Further, the lowest power consumption level can be achieved by putting the VG-468 into *CS controlled power down mode. This mode is entered by disabling all the I/O, memory windows, output buffers, enabling the power down mode, and driving the *CS to high.                                                                                                                                       |

|                                     | During the *CS controlled down, VG-468's Vcc will still be powered up, and the internal register contents will be maintained. The interrupt (IRQs) can still be generated to the host system from either card status change, or PC Card interrupt requests. *RIO can still be armed to route either *RI or Card detect change. *INTR can still be armed for card status change interrupts but will not be generated until power down mode is exited.                                                                                                           |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      | A unique feature is provided to VG-468 to support host system suspend/resume operation. When the host system enters suspend mode, the VG-468 can be powered at 3.3V, and still maintain the ability to route the *RI signals from both sockets to *RIO signal as the resume indication to the host system.                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERRUPT<br>HANDLING                                | Since multiple PC Cards in a system can conflict if they try to utilize the same interrupt, the VG-468 can be programmed to eliminate this conflict by routing each PC Card interrupt request to a different system interrupt. Based upon four bits in the Interrupt and General Control Register, the interrupt request signal (*IREQ) from an I/O PC Card will be directed to one of ten interrupt request lines on the system bus.                                                                                                                                                                                                                                                                          |

|                                                      | The VG-468 provides a card status change interrupt which can notify the system of a change in the battery voltage levels, card insertion/removal detection, Ready/*Busy condition, and status change. It can be directed to one of the ten interrupt request lines on the system bus based upon four bits in the Card Status Change Interrupt Configuration Register. When used with a CPU that supports SMI, it should be configured as the *INTR signal and connected to the *EXTSMI input of the CPU.                                                                                                                                                                                                       |