# 1.0 DESCRIPTION

## 1.1 WD76C30/LV FEATURES

- Two fully programmable and independent serial I/O ports configurable as PC/AT compatible (WD16C452) or PS/2 compatible (WD16C552)

- Loopback controls for communications link fault isolation for each ACE

- ° Line break generation and detection for each ACE

- ° Complete status reporting capabilities

- Generation and stripping of serial asynchronous data control bits (start, stop, parity)

- ° Programmable baud rate generator and MODEM control signals for each port

- ° Programmable baud rate generator input clock

- ° Optional 16 byte FIFO buffers on both transmit and receive of each port for CPU relief during high speed data transfer

- ° Programmable FIFO threshold levels of 1, 4, 8, or 14 bytes on each port

- Parallel port configurable as a fully Centronics or PS/2 compatible, bidirectional parallel port

- Independently programmable parallel port

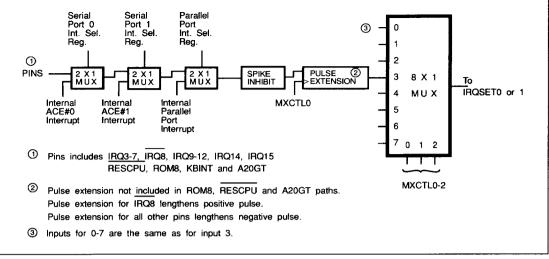

- Interrupt multiplexing logic

- Selectable multiplexing logic for connecting PC/AT interrupt request lines to the WD76C10 single chip AT controller

- Clock generation circuitry

- ° 80287 coprocessor clock generation

- ° WD76C10 and floppy controller clock generation

- ° 8042 keyboard clock generation

- Built-in testability features

- Hardware or software controllable sleep mode

- CMOS implementation for high speed and low power requirements

- Pulse extension on IRQ inputs

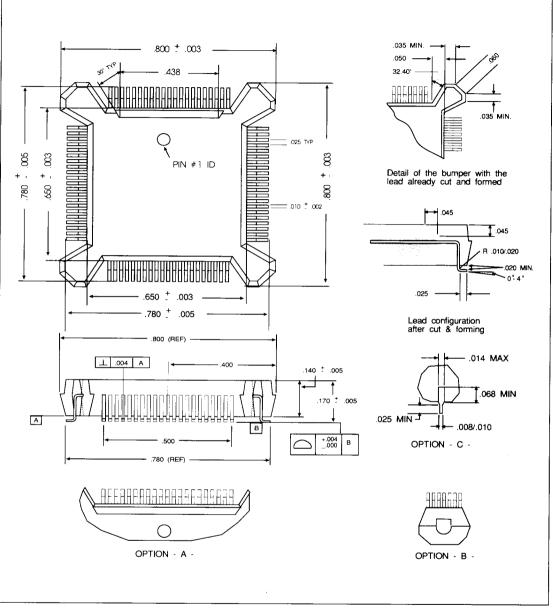

- 84-pin PLCC and PQFP packages

# 1.2 GENERAL

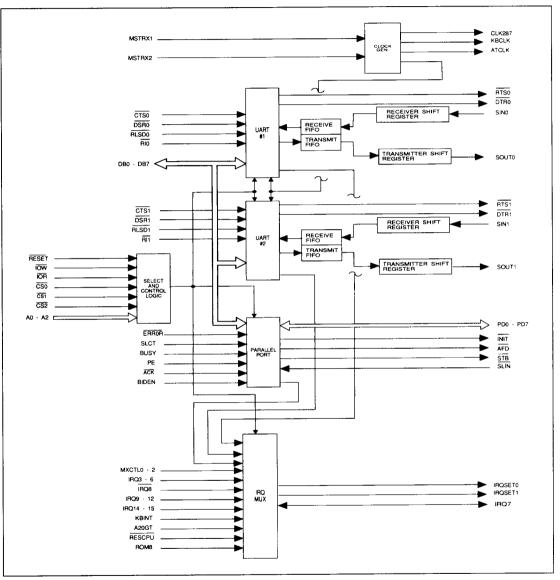

The WD76C30/LV device provides three functional groups. It is a Peripheral Controller, Interrupt Multiplexer, and Clock Generator.

The low power CMOS WD76C30/LV is a single device solution which provides interrupt multiplexing logic, clock generation, two serial ports, and one bidirectional parallel port.

Interrupt multiplexing logic interfaces the PC/AT interrupt request lines with the WD76C10 Single Chip AT Controller.

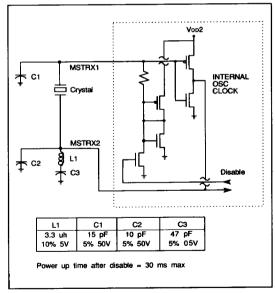

Integrated clock generation circuitry uses the 48 MHz input signal to generate the 1.8462, 3.072, and 8.0 MHz clocks used internally for the two serial ports, a 9.6 MHz signal used for the keyboard controller and floppy controller, a programmable duty/frequency clock for the 80287 coprocessor, and a 16 MHz clock for driving the WD76C10 Single Chip AT Controller, and floppy controller.

For low power implementations such as laptops, oscillator disable and sleep modes are available to power down unused logic.

The bidirectional parallel port is software configurable as either a PC/AT or a PS/2 compatible port. The parallel port data lines and open drain printer signals have high current drive capabilities.

Each ACE is programmable as either a WD16C550 or WD16C450 compatible device. Each WD16C550 configured ACE is capable of buffering up to 16 bytes of data upon reception, relieving the CPU of interrupt overhead. Buffering of data also allows greater latency time in interrupt servicing which is vital in a multitasking environment. Each ACE has a maximum recommended data rate of 512 Kbaud.

# 1.3 WD76C30/LV DIFFERENCES

Both the WD76C30 and WD76C30LV operate with two power supplies. The WD76C30 logic is powered by a 5.0 volt supply, while the WD76C30LV logic is powered by a 3.3 volt supply. The parallel and serial port interfaces are only supported by the WD76C30.

## 1.4 PERIPHERAL CONTROLLER

The peripheral controller is functionally equivalent to the WD16C452/552. The mode of operation of the serial ports and parallel port is selectable via the Mode Select Register. Each serial port is configurable as either a FIFO enhanced ACE (WD16C550 compatible) or a standard ACE (WD16C450). The parallel port is configurable as either a PS/2 bidirectional parallel port or a PC/AT compatible parallel port. A detailed description of the Mode Selection Register is described in the parallel port section.

# 2.0 PIN DESCRIPTION

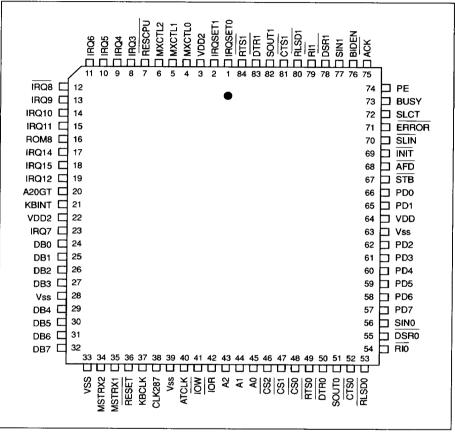

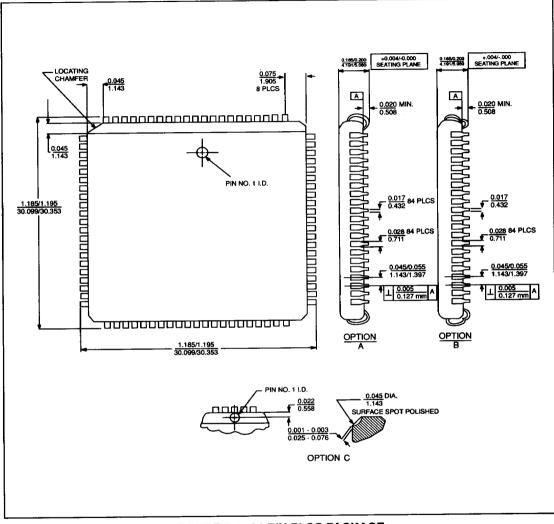

Table 2-1 provides a description of the signals serviced by the WD76C30/LV. A drawing of the 84-pin QUAD package, showing the pin and signal

locations, is provided in Figure 2-1. The DC operating characteristics and timing are presented in section 6. The DC Operating Characteristics for the WD76C30LV are presented in the Appendix.

FIGURE 2-1. 84-PIN PLCC - SIGNAL/PIN ASSIGNMENT

ADVANCED INFORMATION 11/19/91

WD76C30/LV

6

| MNEMONIC       | SIGNAL NAME                                                                                                          | I/O                                                                                                                                                                                                                                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                         |

|----------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIDEN          | Bidirectional<br>Enable                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                   | When de-asserted, the BIDEN enables the<br>parallel port data lines as outputs. When as-<br>serted, BIDEN works in conjunction with the<br>DIR bit (see Table 4-3) to control the direction<br>of the parallel port data bit.                                       |

| DSR1, DSR0     | Data Set Ready                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                   | The communication link asserts these signals<br>to indicate that it is ready to exchange data with<br>the associated Asynchronous Communications<br>Element (ACE). Bit 5 of the associated<br>MODEM Status Register reflects the logical<br>state of DSR.           |

| RI1, RIO       | Ring Indicator                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                   | When asserted, these signals indicate that a ringing signal for the associated ACE is being received by the MODEM or data set. This logical value is reflected in bit 6 of the associated MODEM Status Register.                                                    |

| RLSD1<br>RLSD0 | Received Line<br>Signal Detect                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                   | The Data Circuit-terminating Equipment (DCE)<br>asserts these signals when the associated ACE<br>is receiving a signal that meets its signal quality<br>conditions. Bit 3 of the associated MODEM<br>Status Register reflects this value.                           |

| SOUT1<br>SOUT0 | Serial Data<br>Output                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                   | SOUT1 is the transmitted Serial Data Output<br>from ACE#1 to the communication link.<br>SOUT0 is the transmitted Serial Data Output<br>from ACE#0 to the communication link. The<br>SOUT signals are set to a marking condition<br>(logical 1) upon a Master Reset. |

| SIN1, SINO     | Serial Data<br>Inputs                                                                                                |                                                                                                                                                                                                                                                                                                                                                                     | SIN1 is the received Serial Data Input from the communication link to ACE#1. SIN0 is the received Serial Data Input from the communication link to ACE#0.                                                                                                           |

|                |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     | Data on the serial data inputs are disabled<br>when exercising loop back mode and internally<br>connected to their respective SOUT lines.                                                                                                                           |

| DTR1, DTR0     | <u>Data T</u> erminal<br>Ready                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                   | When asserted, the Data Terminal Ready in-<br>forms the MODEM or data set that the as-<br>sociated ACE is ready to receive. This value is<br>reflected in bit 0 of the MODEM Control<br>Register.                                                                   |

| RTS1, RTS0     | Request To<br>Send                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                   | When asserted, the Request To Send informs<br>the MODEM or data set that the associated<br>ACE is ready to transmit data. This value is<br>reflected in bit 1 of the MODEM Control<br>Register.                                                                     |

|                | BIDEN<br>DSR1, DSR0<br>RI1, RI0<br>RI1, RI0<br>RLSD1<br>RLSD0<br>SOUT1<br>SOUT1<br>SOUT0<br>SIN1, SIN0<br>DTR1, DTR0 | BIDEN       Bidirectional<br>Enable         DSR1, DSR0       Data Set Ready         RI1, RI0       Ring Indicator         RLSD1<br>RLSD0       Received Line<br>Signal Detect         SOUT1<br>SOUT0       Serial Data<br>Output         SIN1, SIN0       Serial Data<br>Inputs         DTR1, DTR0       Data Terminal<br>Ready         RTS1, RTS0       Request To | BIDENBidirectional<br>EnableIDSR1, DSR0Data Set Ready1RI1, RI0Ring IndicatorIRLSD1<br>RLSD0Received Line<br>Signal DetectISOUT1<br>SOUT0Serial Data<br>OutputOSIN1, SIN0Serial Data<br>InputsIDTR1, DTR0Data Terminal<br>ReadyORTS1, RTS0Request ToO                |

# TABLE 2-1. PIN DESCRIPTION

| PIN<br>NUMBER       | MNEMONIC   | SIGNAL NAME                  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                            |

|---------------------|------------|------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81, 52              | CTS1, CTS0 | Clear to Send                | I   | The DCE asserts the Clear To Send to signal<br>the associated ACE that a remote device is<br>ready to transmit. This value is reflected in bit<br>4 of the MODEM Status Register.                                                                                                      |

| 32 - 29,<br>27 - 24 | DB7 - DB0  | Data Bits                    | 1/0 | The Data Bits are tri-state, bidirectional com-<br>munication lines between the WD76C30/LV<br>and Data Bus.                                                                                                                                                                            |

|                     |            |                              |     | DB0 is the least significant bit and the first serial bit to be transmitted or received.                                                                                                                                                                                               |

| 43 - 45             | A2, A1, A0 | Address lines<br>A2-A0       | 1   | Address Lines A2 - A0 are used to select the registers internal to the WD76C30/LV.                                                                                                                                                                                                     |

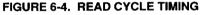

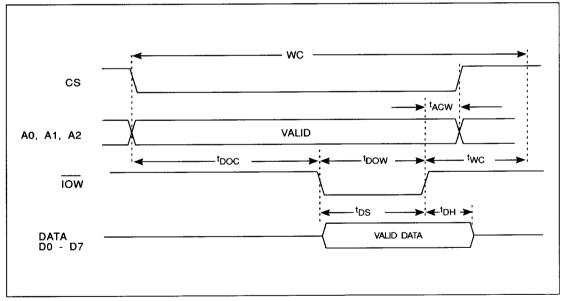

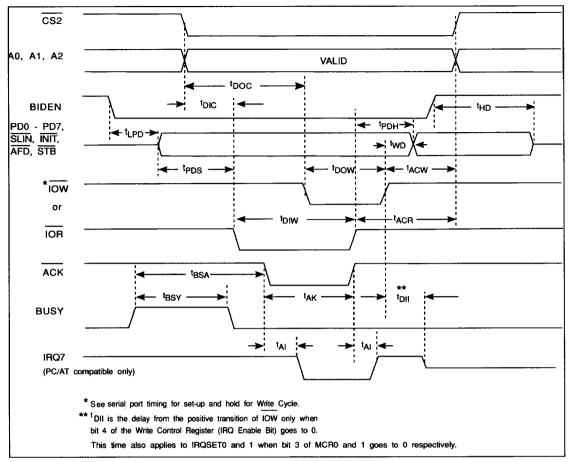

| 41                  | IOW        | Input/Output<br>Write Strobe | 1   | When Input/Output Write Strobe is asserted,<br>data is written to the Port's addressed register<br>from the Data Bus (DB7 - DB0). The register is<br>addressed by Address Lines A2 - A0. ACE#0,<br>ACE#1, or the Parallel Port is selected by CS0,<br>CS1, or CS2 respectively.        |

| 42                  | IOR        | Input/Output<br>Read Strobe  | l   | When Input/Output Read Strobe is asserted,<br>data is read from the Port's addressed register<br>and placed on the Data Bus (DB7 - DB0). The<br>register is addressed by Address Lines A2 - A0.<br>ACE#0, ACE#1, or the Parallel Port is selected<br>by CS0, CS1, or CS2 respectively. |

| 48                  | CS0        | Chip Select 0                | Ι   | Chip Select 0 when asserted, selects serial port 0.                                                                                                                                                                                                                                    |

| 47                  | CS1        | Chip Select 1                | Ι   | Chip Select 1 when asserted, selects serial port 1.                                                                                                                                                                                                                                    |

| 46                  | CS2        | Chip Select 2                | I   | Chip Select 2 when asserted, enables the parallel port.                                                                                                                                                                                                                                |

| 36                  | RESET      | Reset                        | I   | When asserted, RESET forces the WD76C30/LV into an idle mode in which all serial data activities are terminated. The IRQ MUX is forced into a non-compatible mode. The WD76C30/LV remains in the idle state until programmed to begin data activities.                                 |

| 57 - 62,<br>65 - 66 | PD7 - PD0  | Parallel Data<br>Bits        | I/O | Bidirectional data port, providing parallel input<br>and output to the parallel port.                                                                                                                                                                                                  |

## TABLE 2-1. PIN DESCRIPTIONS Cont.

| PIN<br>NUMBER | MNEMONIC  | SIGNAL NAME                 | 1/0 | DESCRIPTION                                                                                                                                                                                         |

|---------------|-----------|-----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67            | STB 1     | Line Printer<br>Strobe      | 0   | When asserted, the Line Printer Strobe signals the line printer to latch the data currently on the parallel port (PD7 - PD0).                                                                       |

| 68            | AFD ①     | Line Printer<br>Autofeed    | ο   | When asserted, the Line Printer Autofeed sig-<br>nals the line printer to autofeed continuous form<br>paper.                                                                                        |

| 69            | INIT ①    | Line Printer<br>Initialize  | 0   | When asserted, Line Printer Initialize signals the line printer to begin an initialization routine.                                                                                                 |

| 70            | SLIN ①    | Line Printer<br>Select      | 0   | When asserted, Line Printer Select selects the printer.                                                                                                                                             |

| 23            | IRQ7/IRQ7 | Interrupt<br>Request 7      | 1/0 | IRQ7/IRQ7 is an input to the IRQ MUX when<br>the WD76C30/LV is <u>not</u> in the Stand Alone<br>Mode.                                                                                               |

|               |           |                             |     | IRQ7/IRQ7 is output as the Parallel Port Inter-<br>rupt when the WD76C30/LV is in the Stand<br>Alone Mode (refer to section 5.6, 5.7).                                                              |

|               |           |                             |     | When operating as the Parallel Port Interrupt,<br>IRQ7/IRQ7 is a tristate signal and must be<br>enabled by bit 4 in the Write Control Register<br>(refer to section 4.0).                           |

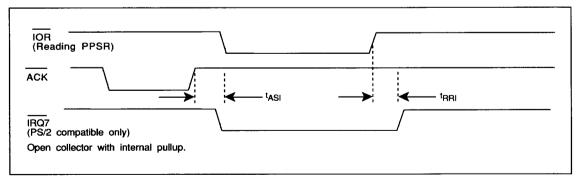

|               |           |                             |     | When the Parallel Port Interrupt is PC/AT com-<br>patible, this signal is IRQ7 and is asserted at<br>the rising edge of ACK and de-asserted at the<br>falling edge of ACK.                          |

|               |           |                             |     | When the Parallel Port is PS/2 compatible, this signal is IRQ7 and is asserted at the rising edge of ACK and de-asserted at the rising edge of IOR, when reading the Parallel Port Status Register. |

| 71            | ERROR     | Line Printer<br>Error       | 1   | The printer asserts this signal to inform the parallel port of a deselect condition, PE, or other error condition.                                                                                  |

| 72            | SLCT      | Line Printer<br>Select      | 1   | The line printer asserts the Line Printer Select signal when it has been selected.                                                                                                                  |

| 73            | BUSY      | Line Printer<br>Busy        | 1   | The line printer asserts the Line Printer Busy signal when it has an operation in progress.                                                                                                         |

| 74            | PE        | Line Printer<br>Paper Empty | 1   | The line printer asserts the Line Printer Paper<br>Empty signal when it is out of paper.                                                                                                            |

|               |           |                             |     | Empty signal when it is out of pape                                                                                                                                                                 |

TABLE 2-1. PIN DECSRIPTION Cont.

## WD76C30/LV

6

| MNEMONIC                                            | SIGNAL NAME                                                                                                       | 1/0                                                                                                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                         |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK                                                 | Line Printer<br>Acknowledge                                                                                       | 1                                                                                                                                                                                                                                                  | The line printer asserts the Line Printer Ac-<br>knowledge signal to confirm that the data trans-<br>fer from the WD76C30/LV to the printer was<br>successful.                                                                                      |

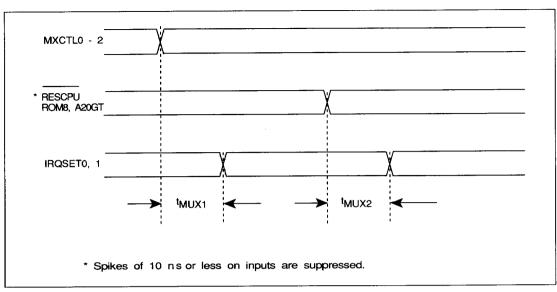

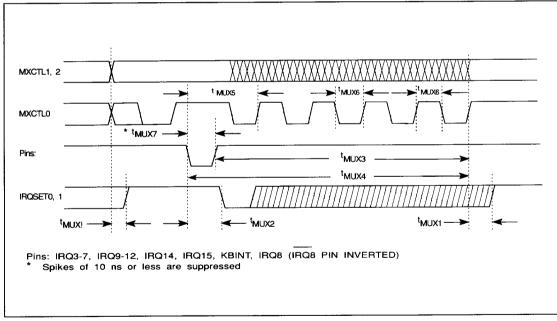

| MXCTL0 -<br>MXCTL2                                  | IRQ MUX<br>Control                                                                                                | 1                                                                                                                                                                                                                                                  | MXCTL0 - MXCTL2 are encoded select signals<br>generated by the WD76C10 for sampling the<br>IRQ inputs.                                                                                                                                              |

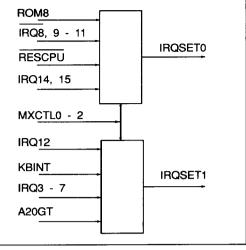

| <u>IRQ3</u> - 6<br>IRQ8<br>IRQ9-11<br>IRQ14, 15, 12 | IRQ MUX<br>Inputs                                                                                                 | I                                                                                                                                                                                                                                                  | These 11 interrupt signals, along with IRQ7,<br>RESCPU, ROM8, KBINT, and A20GT are mul-<br>tiplexed into IRQSET0 and IRQSET1 at a<br>period rate defined by MXCTL0 - MXCTL2.                                                                        |

| RESCPU                                              | Reset CPU                                                                                                         | 1                                                                                                                                                                                                                                                  | The keyboard controller asserts $\overrightarrow{\text{Reset}}$ $\overrightarrow{\text{CPU}}$ when the CPU should be reset.                                                                                                                         |

| ROM8                                                | 8-bit ROM                                                                                                         | I                                                                                                                                                                                                                                                  | ROM8 is multiplexed into the IRQSET1 signal<br>and, when asserted, indicates to the WD76C10<br>that the system ROM is eight bits, when de-as-<br>serted it is 16 bits.                                                                              |

| KBINT                                               | Keyboard<br>Interrupt                                                                                             | 1                                                                                                                                                                                                                                                  | KBINT is multiplexed into the IRQSET1 signal<br>and indicates to the WD76C10 that a keyboard<br>interrupt is pending.                                                                                                                               |

| A20GT                                               | Address 20<br>Signal                                                                                              | I                                                                                                                                                                                                                                                  | A20GT is multiplexed into the IRQSET1 signal<br>and reflects the state of the address 20 signal.<br>This allows compatibility with the 8086 and<br>80286 processors when addressing memory<br>in the 64 Kbyte boundary above 1 Mbyte.               |

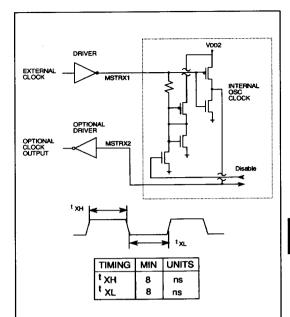

| MSTRX1 ①                                            | Master Clock 1                                                                                                    | 1                                                                                                                                                                                                                                                  | The Master Clock 1 signal can be driven by<br>either a 16 MHz crystal or 48 MHz TTL oscil-<br>lator.                                                                                                                                                |

| MSTRX2 ①                                            | Master Clock 2                                                                                                    | 0                                                                                                                                                                                                                                                  | Master Clock 2 is connected to the 16 MHz<br>crystal to generate Master Clock 1 for the clock<br>generation circuitry. This pin is left discon-<br>nected if Master Clock 1 is being driven by a 48<br>MHz TTL oscillator.                          |

| CLK287                                              | 80287 Clock                                                                                                       | 0                                                                                                                                                                                                                                                  | CLK287 clock drives the 80287 coprocessor.<br>CLK287 is programmable via the Clock Selec-<br>tion Register. A variety of clock frequencies<br>and duty cycles provide compatibility with a<br>variety of 80287 or 80287 compatible<br>coprocessors. |

|                                                     | ACK<br>MXCTL0 -<br>MXCTL2<br>IRQ3 - 6<br>IRQ9-11<br>IRQ14, 15, 12<br>RESCPU<br>ROM8<br>KBINT<br>A20GT<br>MSTRX1 ① | ACKLine Printer<br>AcknowledgeMXCTL0 -<br>MXCTL2IRQ MUX<br>ControlIRQ3 - 6<br>IRQ9-11<br>IRQ14, 15, 12IRQ MUX<br>InputsRESCPUReset CPUROM88-bit ROMKBINTKeyboard<br>InterruptA20GTAddress 20<br>SignalMSTRX1 ①Master Clock 1MSTRX2 ①Master Clock 2 | ACKLine Printer<br>AcknowledgeIMXCTL0 -<br>MXCTL2IRQ MUX<br>ControlIIRQ3 - 6<br>IRQ9-11<br>IRQ14, 15, 12IRQ MUX<br>InputsIRESCPUReset CPUIROM88-bit ROMIKBINTKeyboard<br>InterruptIA20GTAddress 20<br>SignalIMSTRX1 ①Master Clock 1I                |

① Third overtone of 16 MHz crystal is used to generate the 48 MHz clock.

# TABLE 2-1. PIN DESCRIPTION Cont.

| PIN<br>NUMBER     | MNEMONIC           | SIGNAL NAME                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|-------------------|--------------------|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37                | KBCLK              | Keyboard Clock                   | 0   | Keyboard Clock is a 9.6 MHz clock used to<br>drive the keyboard controller. This signal can<br>be used to drive the WD37C65 Floppy Disk<br>Controller for systems not using the WD76C20<br>Storage Controller.                                                                                             |

| 40                | ATCLK              | AT Clock                         | 0   | AT Clock is a 16 MHz clock used to drive the<br>ATCLK input to the WD76C10. AT Clock<br>provides a fixed reference that allows the<br>PC/AT bus state machine to run with 8 MHz<br>compatible timing. This signal can be used to<br>drive the Floppy Disk Controller in the<br>WD76C20 Storage Controller. |

| 1<br>2            | IRQSET0<br>IRQSET1 | Interrupt<br>Request<br>Set 0, 1 | 0   | These signals are outputs of the IRQ multiplex-<br>ing logic. When in the Stand Alone Mode<br>IRQSET0 and IRQSET1 become the tristate<br>interrupt outputs from Serial Port 0 and 1<br>respectively. (Refer to section 5.6)                                                                                |

| 64                | VDD                | Power Supply                     |     | WD76C30, +5V power supply to the serial and<br>parallel port logic. This supply can be turned<br>off.                                                                                                                                                                                                      |

|                   |                    |                                  |     | WD76C30LV, +3.3 power supply to the serial<br>and parallel port logic. This supply can be<br>turned off.                                                                                                                                                                                                   |

| 3, 22             | VDD2               | Power Supply                     |     | +5V power supply to the WD76C30, excluding the serial and parallel ports.                                                                                                                                                                                                                                  |

|                   |                    |                                  |     | +3.3V power supply to the WD76C30LV, excluding the serial and parallel ports.                                                                                                                                                                                                                              |

| 28, 39,<br>63, 33 | Vss                | Ground                           |     | System signal ground.                                                                                                                                                                                                                                                                                      |

TABLE 2-1. PIN DESCRIPTION Cont.

# 3.0 SERIAL PORT REGISTERS

The WD76C30/LV contains two serial ports, therefore, the following registers exist in duplicate, one per port.

# 3.1 SERIAL PORT REGISTER ADDRESSING

# 3.1.1 Chip Select (CS0, CS1)

When  $\overline{CS0}$  is low, registers for serial port 0 can be accessed, and when  $\overline{CS1}$  is low, registers for serial port 1 can be accessed. No more than one  $\overline{CS}$ ( $\overline{CS0}$ ,  $\overline{CS1}$ , or  $\overline{CS2}$ ) should ever be low at any time, unless all three are low for Sleep Mode.

## Power Down Reset:

In the Parallel Port, asserting Mode Selection Register bit 3 (PUD) described in section 5.5, causes the ACE to reset to the condition listed in Table 3-2.

## Software Reset:

A software reset is performed by writing to the Divisor Latches, forcing the transmitter and receiver to an idle mode. Registers are not reset by this operation. Prior to enabling interrupts, the LSR and RBR registers should be read to clear out any data, returning them to a known state without resetting the system.

Chip Select ( $\overline{CS0}$ ,  $\overline{CS1}$ ) and register select (A0, A1, A2) signals must be stable for the duration of a read or write operation.

## 3.1.2 Register Select (A0, A1, A2)

To select a register for read or write operation, see Table 3-1.

#### NOTE

Divisor Latch Access Bit (DLAB) is the MSB of the Line Control Register. DLAB must be programmed high (logic 1) by the system software to access the Baud Rate Generator Divisor Latches.

| DLAB   | A2 | A1 | <b>A</b> 0 | REGISTER                                        |  |

|--------|----|----|------------|-------------------------------------------------|--|

| 0      | 0  | 0  | 0          | Receiver Buffer Register (read)                 |  |

| 0      | 0  | 0  | 0          | Transmitter Holding Register (write)            |  |

| 0      | 0  | 0  | 1          | Interrupt Enable Register                       |  |

| X<br>X | 0  | 1  | 0          | Interrupt Identification Register (read)        |  |

| x      | 0  | 1  | 0          | FIFO Control Register (write)                   |  |

| x      | 0  | 1  | 1          | Line Control Register                           |  |

| x      | 1  | 0  | 0          | MODEM Control Register                          |  |

| Х      | 1  | 0  | 1          | Line Status Register (read only)                |  |

| X      | 1  | 1  | 0          | MODEM Status Register                           |  |

| x      | 1  | 1  | 1          | Scratch Pad Register                            |  |

| 1      | 0  | 0  | 0          | Divisor Latch Register (least significant byte) |  |

| 1      | 0  | 0  | 1          | Divisor Latch Register (most significant byte)  |  |

#### TABLE 3-1. REGISTER ADDRESSING

# 3.2 ACE OPERATIONAL DESCRIPTION

#### 3.2.1 Master Reset

Asserting RESET on pin 36 causes the ACE to reset to the condition listed in Table 3-2.

3.2.2 ACE Accessible Registers

The system programmer has access to any of the registers as summarized in Table 3-3. For individual register descriptions, refer to the following pages under register heading.

| REGISTER/SIGNAL                                      | RESET CONTROL                                                              | RESET STATE                                                                                |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Receiver Buffer Register                             | First Word Received                                                        | Data                                                                                       |  |  |

| Transmitter Holding Register                         | Writing into the Transmitter<br>Holding Register                           | Data                                                                                       |  |  |

| Interrupt Enable Register                            | Master Reset or PUD = 1                                                    | All Bits Low (0-3 forced<br>and 4-7 permanent)                                             |  |  |

| Interrupt Identification Register                    | Master Reset or PUD = 1                                                    | Bit 0 is High and Bits 1-3; 6<br>and 7 are forced Low. Bits 4<br>and 5 are Permanently Low |  |  |

| Line Control Register                                | Master Reset or PUD = 1                                                    | All Bits Low                                                                               |  |  |

| MODEM Control Register                               | Master Reset or PUD = $1$                                                  | All Bits Low                                                                               |  |  |

| Line Status Register                                 | Master Reset or PUD = 1                                                    | All Bits Low, except Bits 5<br>and 6 are High                                              |  |  |

| MODEM Status Register                                | Master Reset or PUD = 1<br>MODEM Signal Inputs                             | Bits 0-3 Low,<br>Bits 4-7 at Input Signal                                                  |  |  |

|                                                      | Writing into the Latch                                                     | Data                                                                                       |  |  |

| Divisor Latch (low order byte)                       | Writing into the Latch                                                     | Data                                                                                       |  |  |

| Divisor Latch (high order byte)                      | Master Reset or PUD = 1                                                    | High                                                                                       |  |  |

| SOUT                                                 | Master Reset or PUD = 1                                                    | High                                                                                       |  |  |

| RTS                                                  | Master Reset or PUD = 1                                                    | High                                                                                       |  |  |

| DTR                                                  | MR or FCR1• FCR0 or $\Delta$ FCR0 or PUD = 1                               | All Bits Low                                                                               |  |  |

| RCVR FIFO Counter                                    | MR or FCR2 • FCR0 or $\triangle$ FCR0 or PUD = 1                           | All Bits Low                                                                               |  |  |

| XMIT FIFO Counter                                    | MR or FCR2 • FCR0 of $\Delta$ FCR0 of $10D = 1$<br>Master Reset or PUD = 1 | All Bits Low                                                                               |  |  |

| FIFO CONTROL                                         |                                                                            | Tri-State                                                                                  |  |  |

| D7 - D0 Data Bus Lines                               | In Tristate Mode,<br>Unless IOR = Low                                      | Data (ACE to CPU)                                                                          |  |  |

| A LL Only sting Desigtor                             | Master Reset                                                               | All Bits Low                                                                               |  |  |

| Address Selection Register                           | Master Reset                                                               | All Bits Low                                                                               |  |  |

| Clock Selection Register                             | Master Reset                                                               | All Bits Low                                                                               |  |  |

| CLK Disable Register<br>Serial Port Interrupt        | Master Reset                                                               | All Bits Low                                                                               |  |  |

| Selection Register                                   | M. J. Breat                                                                | All Bits Low                                                                               |  |  |

| Serial Port Interrupt<br>Selection Register          | Master Reset                                                               | · ··· = ··- = ·                                                                            |  |  |

| Parallel Port Interrupt<br>Selection Register        | Master Reset                                                               | All Bits Low                                                                               |  |  |

| Mode Selection Register                              | Master Reset                                                               | All Bits Low                                                                               |  |  |

| Parallel Port Control                                | Master Reset or PUD = 1                                                    | Bits 7 - 6 High, Bits 5 - 0 Lov                                                            |  |  |

| Parallel Port Data                                   | Master Reset or PUD = 1                                                    | All Bits Low                                                                               |  |  |

|                                                      | None                                                                       |                                                                                            |  |  |

| Parallel Port <u>Status</u><br>SLIN, INIT, AFD, STB, | Master Reset or PUD = 1                                                    | High, Low, High, High                                                                      |  |  |

PUD is bit 3 of the Mode Selection Register

# TABLE 3-2. RESET CONTROL OF REGISTERS AND PINOUT SIGNALS

6-10

|            |                                    | F                                   | REGISTER ADDI                                                                 | RESS ②                                  |                                               |                                          |

|------------|------------------------------------|-------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|------------------------------------------|

|            | DLAB = 0<br>A2-A0 = 0<br>Read Only | DLAB = 0<br>A2-A0 = 0<br>Write Only | DLAB = 0<br>A2-A0 = 1                                                         | DLAB = X<br>A2-A0 = 2<br>Read Only      | DLAB = X<br>A2 - A0 = 2<br>Write Only         | DLAB = X<br>A2 - A0 = 3                  |

|            |                                    |                                     | REGISTER T                                                                    | ITLE                                    |                                               |                                          |

| Bit<br>No. | Receiver<br>Buffer<br>Register     | Transmitter<br>Holding<br>Register  | Interrupt<br>Enable<br>Register                                               | Interrupt<br>Identification<br>Register | FIFO Control<br>Register                      | Line<br>Control<br>Register              |

| 0          | Data Bit 0                         | Data Bit 0                          | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBFI)               | "0" if<br>Interrupt<br>Pending<br>(IP)  | FIFO<br>Enable<br>(FEWO)                      | Word Length<br>Select Bit 0<br>(WLS0)    |

| 1          | Data Bit 1                         | Data Bit 1                          | Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt<br>(ETBEI) | Interrupt<br>ID Bit 1<br>(IID)          | Rcvr<br>FIFO<br>Reset<br>(RFR)                | Word Length<br>Select Bit<br>1 (WLS1)    |

| 2          | Data Bit 2                         | Data Bit 2                          | Enable<br>Receiver<br>Line Status<br>Interrupt<br>(ERLSI)                     | Interrupt<br>ID Bit 2<br>(IID)          | Transmitter<br>FIFO<br>Reset<br>(TFR)         | Number of<br>Stop Bits<br>(STB)          |

| 3          | Data Bit 3                         | Data Bit 3                          | Enable<br>MODEM<br>Status<br>Interrupt<br>(EDSSI)                             | Interrupt<br>ID Bit 3<br>(IID) ①        | Not<br>Used                                   | Parity<br>Enable<br>(PEN)                |

| 4          | Data Bit 4                         | Data Bit 4                          | 0                                                                             | 0                                       | Reserved                                      | Even<br>Parity<br>Select<br>(EPS)        |

| 5          | Data Bit 5                         | Data Bit 5                          | 0                                                                             | 0                                       | Reserved                                      | Stick Parity<br>(STP)                    |

| 6          | Data Bit 6                         | Data Bit 6                          | 0                                                                             | FIFO<br>Enabled ①<br>(FERO)             | Rcvr FIFO<br>Trigger Level<br>(LSB)(RFTL)     | Set Break<br>Control<br>(SBR)            |

| 7          | Data Bit 7                         | Data Bit 7                          | 0                                                                             | FIFO<br>Enabled ①<br>(FERO)             | Rcvr FIFO<br>Trigger Level<br>(MSB)<br>(RFTL) | Divisor<br>Latch<br>Access Bit<br>(DLAB) |

# TABLE 3-3. ACCESSIBLE WD76C30 SERIAL PORT REGISTERS

ADVANCED INFORMATION 11/19/91

6-11

|                | DLAB = X<br>A2-A0 = 4              | DLAB = X<br>A2-A0 = 5                              | <b>ISTER ADDR</b><br>DLAB = X<br>A2-A0 = 6           | DLAB = X<br>A2-A0 = 7      | DLAB = 1<br>A2-A0 = 0     | DLAB = 1<br>A2-A0 = 1     |  |  |  |

|----------------|------------------------------------|----------------------------------------------------|------------------------------------------------------|----------------------------|---------------------------|---------------------------|--|--|--|

| REGISTER TITLE |                                    |                                                    |                                                      |                            |                           |                           |  |  |  |

| Bit<br>No.     | MODEM<br>Control<br>Register       | Line<br>Status<br>Register                         | MODEM<br>Status<br>Register                          | Scratch<br>Pad<br>Register | Divisor<br>Latch<br>(LSB) | Divisor<br>Latch<br>(MSB) |  |  |  |

| 0              | Data<br>Terminal<br>Ready<br>(DTR) | Data<br>Ready<br>(DR)                              | Delta<br>Clear to<br>Send<br>(DCTS)                  | Bit 0                      | Bit 0                     | Bit 8                     |  |  |  |

| 1              | Request<br>to Send<br>(RTS)        | Overrun<br>Error<br>(OE)                           | Delta<br>Data Set<br>Ready<br>(DDSR)                 | Bit 1                      | Bit 1                     | Bit 9                     |  |  |  |

| 2              | Not<br>Connected<br>(NC)           | Parity<br>Error<br>(PE)                            | Trailing<br>Edge Ring<br>Indicator<br>(TERI)         | Bit 2                      | Bit 2                     | Bit 10                    |  |  |  |

| 3              | Interrupt<br>(Int)                 | Framing<br>Error<br>(FE)                           | Delta<br>Receive<br>Line Signal<br>Detect<br>(DRLSD) | Bit 3                      | Bit 3                     | Bit 11                    |  |  |  |

| 4              | Loop                               | Break<br>Interrupt<br>(BI)                         | Clear to<br>Send<br>(CTS)                            | Bit 4                      | Bit 4                     | Bit 12                    |  |  |  |

| 5              | 0                                  | Transmitter<br>Holding<br>Register<br>Empty (THRE) | Data Set<br>Ready<br>(DSR)                           | Bit 5                      | Bit 5                     | Bit 13                    |  |  |  |

| 6              | 0                                  | Transmitter<br>Empty<br>(TEMT)                     | Ring<br>Indicator<br>(RI)                            | Bit 6                      | Bit 6                     | Bit 14                    |  |  |  |

| 7              | 0                                  | Error in<br>RCVR<br>FIFO ①<br>(EIRF)               | Received<br>Line Signal<br>Detect<br>(RLSD)          | Bit 7                      | Bit 7                     | Bit 15                    |  |  |  |

TABLE 3-3. ACCESSIBLE WD76C30 SERIAL PORT REGISTERS (Cont.)

## 3.3 LINE CONTROL REGISTER

The Line Control Register provides control over the word length, number of Stop Bits, Parity, Break Control and selection of the Receiver Buffer, Transmitter Holding Register and Interrupt Enable Register.

Address A2-A0 = 3, DLAB = X - Read and Write

| 7    | 6   | 5   | 4   | 3   | 2   | 1    | 0    |

|------|-----|-----|-----|-----|-----|------|------|

| DLAB | SBR | STP | EPS | PEN | STB | WLS1 | WLS0 |

|      |     |     |     |     |     |      |      |

| Signal      |  |  |  |  |  | Default After |

|-------------|--|--|--|--|--|---------------|

| Name        |  |  |  |  |  | Master Reset  |

| All signals |  |  |  |  |  | 0             |

#### Bit 7 - DLAB, Divisor Latch Access

DLAB = 0 -

Access the Receiver Buffer, Transmitter Holding Register or Interrupt Enable Register.

#### DLAB = 1 -

Access the Divisor Latches of the Baud Rate Generator during a Read or Write operation.

#### Bit 6 - SBR, Set Break Control

The SBR feature enables the CPU to alert a terminal in a computer communications system.

SBR = 0 -

Serial Output (SOUT) follows the output of the transmitter.

SBR = 1 -

The Serial Output (SOUT) is forced to the Spacing (logic 0) State and remains there (until reset by a low-level SBR), regardless of other transmitter activity.

#### Bit 5 - STP, Stick Parity

STP = 0 -

When parity is enabled by PEN (bit 3), it is represented as indicated by the state of EPS (bit 4).

STP = 1 -

When parity is enabled by PEN, the Parity bit is transmitted and then detected by the receiver in the opposite state indicated by EPS.

## Bit 4 - EPS, Even Parity Select

#### EPS = 0 -

When PEN (bit 3) equals 1 and STP equals 0, an odd number of logic 1's are transmitted or checked in the data word bits and Parity bit.

EPS = 1 -

When PEN equals 1 and STP equals 0, an even number of bits are transmitted or checked.

#### Bit 3 - PEN, Parity Enable

PEN = 0 -

No parity is generated or checked.

PEN = 1 -

Parity is generated on transmitted data or checked on received data between the last data word bit and Stop bit of the serial data. The Parity bit is used to produce an even or odd number of 1's when the data word bits and the Parity bit are summed.

#### Bit 2 - STB, Number Of Stop Bits

This bit specifies the number of Stop Bits in each transmitted serial character.

STB = 0 -

One Stop Bit is generated in the transmit data.

STB = 1 -

When WLS1 and WLS0 (bits 1 and 0) select a 5-bit word length, 1-1/2 Stop bits are generated.

When WLS1 and WLS0 select a 6, 7 or 8-bit word length, two Stop bits are generated.

## Bits 1, 0 - WLS1, WLS0, Word Length Select

WLS1 and WLS0 specify the number of bits in each transmitted or received serial character.

| WLS1 | WLS0 | Word Length |

|------|------|-------------|

| 0    | 0    | 5 bits      |

| 0    | 1    | 6 bits      |

| 1    | 0    | 7 bits      |

| 1    | 1    | 8 bits      |

#### 3.4 ACE PROGRAMMABLE BAUD RATE GENERATOR

The ACE contains a programmable Baud Rate Generator with a programmable input clock of 1.843 MHz. 3.0 MHz or 8 MHz clocks. as well as a 48 MHz input for test purposes. The output frequency of the Baud Generator is 16 times the baud rate. Two 8-bit latches store the divisor in a 16-bit binary format. These Divisor Latches must be loaded during initialization in order to insure desired operation of the Baud Rate Generator. Upon loading either of the Divisor Latches, a 16-bit Baud counter is immediately loaded. This prevents long counts on initial load. Loading of either divisor Latch forces the Transmitter and Receiver into the Idle Mode. The transmitter does not enter the Idle Mode until after the character in the shift register has been transmitted.

Tables 3-3, 3-4 and 3-5 illustrate the use of the Baud Generator with three different driving frequencies. One is referenced to a 1.8432 MHz clock, another is a 3.072 MHz clock and the third is an 8.0 MHz clock.

#### NOTE

The maximum operating frequency of the Baud Rate Generator is 8.0 MHz.

The data rate should never be greater than 512 Kbaud.

| DESIRED<br>BAUD<br>RATE                                                                                                                                                                                         | DIVISOR USED<br>TO GENERATE<br>16 TIMES CLOCK                                                                | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| RATE           50           75           110           134.5           150           300           600           1200           1800           2000           2400           3600           4800           7200 | 16 TIMES CLOCK<br>2304<br>1536<br>1047<br>857<br>768<br>384<br>192<br>96<br>64<br>58<br>48<br>32<br>24<br>16 | DESIRED AND ACTORE                                        |

| 9600<br>19200<br>38400<br>56000                                                                                                                                                                                 | 12<br>6<br>3<br>2                                                                                            | <br><br>2.860                                             |

TABLE 3-4. BAUD RATES USING 1.8432 MHz CLOCK

6-14

| DESIRED<br>BAUD<br>RATE | DIVISOR USED<br>TO GENERATE<br>16 TIMES CLOCK | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 50                      | 3840                                          |                                                           |

| 75                      | 2560                                          | _                                                         |

| 110                     | 1745                                          | 0.026                                                     |

| 134.5                   | 1428                                          | 0.034                                                     |

| 150                     | 1280                                          |                                                           |

| 300                     | 640                                           |                                                           |

| 600                     | 320                                           | _                                                         |

| 1200                    | 160                                           |                                                           |

| 1800                    | 107                                           | _                                                         |

| 2000                    | 96                                            | _                                                         |

| 2400                    | 80                                            |                                                           |

| 3600                    | 53                                            | 0.628                                                     |

| 4800                    | 40                                            |                                                           |

| 7200                    | 27                                            | 1.230                                                     |

| 9600                    | 20                                            |                                                           |

| 19200                   | 10                                            |                                                           |

| 38400                   | 5                                             | —                                                         |

| <b>TABLE 3-5.</b> 1 | BAUD RA | TES USING | 3.072 MHz | CLOCK |

|---------------------|---------|-----------|-----------|-------|

|---------------------|---------|-----------|-----------|-------|

| DESIRED<br>BAUD<br>RATE | DIVISOR USED<br>TO GENERATE<br>16 TIMES CLOCK | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 50                      | 10000                                         |                                                           |

| 75                      | 6667                                          | 0.005                                                     |

| 110                     | 4545                                          | 0.010                                                     |

| 134.5                   | 3717                                          | 0.013                                                     |

| 150                     | 3333                                          | 0.010                                                     |

| 300                     | 1667                                          | 0.020                                                     |

| 600                     | 833                                           | 0.040                                                     |

| 1200                    | 417                                           | 0.080                                                     |

| 1800                    | 277                                           | 0.080                                                     |

| 2000                    | 250                                           |                                                           |

| 2400                    | 208                                           | 0.160                                                     |

| 3600                    | 139                                           | 0.080                                                     |

| 4800                    | 104                                           | 0.160                                                     |

| 7200                    | 69                                            | 0.644                                                     |

| 9600                    | 52                                            | 0.160                                                     |

| 19200                   | 26                                            | 0.160                                                     |

| 38400                   | 13                                            | 0.160                                                     |

| 56000                   | 9                                             | 0.790                                                     |

| 128000                  | 4                                             | 2.344                                                     |

| 256000                  | 2                                             | 2.344                                                     |

| 512000                  | 1                                             | 2.344                                                     |

# TABLE 3-6. BAUD RATE USING 8.0 MHz CLOCK

## 3.5 LINE STATUS REGISTER

The Line Status Register provides status information to the CPU concerning the data transfer.

Address A2-A0 = 5, DLAB = X - Read

| 7    | 6    | 5    | 4  | 3  | 2  | 1  | 0  |

|------|------|------|----|----|----|----|----|

| EIRF | темт | THRE | BI | FE | PE | OE | DR |

|      |      |      |    |    |    |    |    |

| Signa<br>Name | al<br>Ə |   |   |   |   |   |   |   |   |   |    |   |   | Default After<br>Master Reset |

|---------------|---------|---|---|---|---|---|---|---|---|---|----|---|---|-------------------------------|

| EIRF          |         |   |   |   |   |   |   |   |   | - |    |   |   | 0                             |

| TEM           | Г       |   |   |   |   |   |   |   |   |   | •  | · | • | 1                             |

| THRE          | Ξ       |   | - |   |   |   |   |   |   | • | •  | · |   | 1                             |

| Bl            |         |   | - |   |   |   |   |   |   |   |    |   | • | 0                             |

| FE            |         |   |   |   |   |   | - |   |   | • | •  | • | • | 0                             |

| PE            |         |   |   |   |   |   |   |   |   | • | •  |   |   | 0                             |

| OE            |         |   |   |   |   |   |   |   | • |   |    | · | • | 0                             |

| DR            | •       | • | • | • | • | · | · | • | · | · | •. | · | • | 0                             |

#### Bit 7 - EIRF, Error in RCVR FIFO

EIRF = 0 -

When in Character Mode, EIRF is always 0.

When in FIFO Mode, a 0 indicates no error in the RCVR.

#### EIRF = 1 -

There is at least one parity error, framing error or break indication in the FIFO. EIRF is set to 0 when the Line Status Register is read and there are no additional errors in the FIFO.

#### Bit 6 - TEMT, Transmitter Empty

TEMT = 0 -

When in the Character Mode, at least one byte has been written into the Transmitter Holding Register.

When in the FIFO Mode, at least one byte has been written into the XMIT FIFO.

TEMT = 1 -

When in the Character Mode, the Transmitter Holding Register and Transmitter Shift Register are idle (empty).

In the FIFO Mode, the XMIT FIFO and XMIT Shift Registers are empty.

# Bit 5 - THRE, Transmitter Holding Register Empty

#### Character Mode:

THRE indicates that the ACE is ready to accept a new character for transmission. THRE also causes the ACE to issue an interrupt to the CPU when the Transmit Holding Register Empty interrupt enable is set high.

THRE = 0 -

The CPU has loaded the Transmitter Holding Register.

#### THRE = 1 -

A character has been transferred from the Transmitter Holding Register into the Transmitter Shift Register.

#### FIFO Mode:

#### Normally

THRE responds immediately when the XMIT FIFO is emptied or when the first character is written into the XMIT FIFO.

The first transmitter interrupt after changing the first bit of FIFO Control Register will be immediate if the Transmit Holding Register Interrupt is enabled.

#### Exception

The Transmitter FIFO empty indications are delayed one character time, minus the last Stop Bit time, whenever the Transmitter FIFO is empty and there have not been at least two characters in Transmitter FIFO at the same time since the last time that Transmitter FIFO was empty.

#### THRE = 0 -

At least one character has been written into the XMIT FIFO.

#### THRE = 1 -

The XMIT FIFO is empty.

#### Bit 4 - BI, Break Interrupt

BI indicates that the received character is a Break.

Bl = 0 -

The CPU read the contents of the Line Status Register. Restarting after a break is received requires the SIN pin to be high for at least one half bit time.

BI = 1 -

When in the Character Mode, the received data input has been held in the Spacing (Logic 0) state for longer than a full word transmission time (that is, the total time of Start Bit + data bits + Parity + Stop Bits).

When in FIFO Mode, BI is associated to the particular character in the FIFO, and is set when the associated character is in the top of the FIFO.

## Bit 3 - FE, Framing Error

FE indicates that the received character did not have a valid Stop Bit.

FE = 0 -

The CPU read the contents of the Line Status Register.

FE = 1 -

In the Character Mode, the Stop Bit following the last data bit or parity bit was detected as a zero bit (Spacing Level).

In the FIFO Mode, an FE is associated with a particular character in the FIFO and is set when the associated character is at the top of the FIFO.

## Bit 2 - PE, Parity Error

PE indicates that the received data character does not have the correct even or odd parity, as selected by the even-parity-select bit.

PE = 0 -

The CPU read the contents of the Line Status Register.

PE = 1 -

In the Character Mode, a parity error has been detected.

In the FIFO Mode, a parity error is associated with a particular character in the FIFO, and PE is set when the associated character is at the top of the FIFO.

#### Bit 1 - OE, Overrun Error

OE indicates that an Overrun Error occurred.

OE = 0 -

The CPU read the contents of the Line Status Register.

OE = 1 -

In the Character Mode, the data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register. This destroyed the previous character.

When in FIFO Mode, an OE occurs after the RCVR FIFO is full and the Receiver Shift Register has completely received the next character. An OE is indicated to the CPU as soon as it happens. The character in the shift register will be written over but nothing will be transferred to the FIFO.

## Bit 0 - DR, Receiver Data Ready

DR = 0 -

In the Character Mode, the CPU read the data in the Receiver Buffer Register.

In the FIFO Mode, the receiver FIFO is empty.

DR = 1 -

In the Character Mode, a complete incoming character has been received and transferred into the Receiver Buffer Register.

In the FIFO Mode, a complete incoming character has been received and transferred into the RCVR FIFO.

#### NOTE

Bits 4 through 1 are the error conditions that produce a Receiver Line Status interrupt whenever any of the corresponding conditions are detected and Receiver Line Status interrupt is enabled. All bits of the Line Status Register, except bit 7, can be set or reset by writing to the register.

## 3.6 INTERRUPT IDENTIFICATION REGISTER

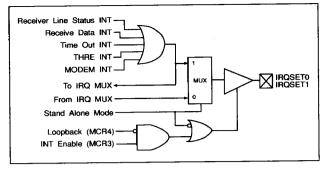

The ACE has an interrupt capability that allows for complete flexibility in interfacing with all popular microprocessors presently available. In order to provide minimum software overhead during data character transfers, the ACE prioritizes interrupts into four levels. Listed according to their priority the four levels of interrupt conditions are:

Receiver Line Status Received Data Ready Transmitter Holding Register Empty MODEM Status

Information indicating that a prioritized interrupt is pending and source of that interrupt is stored in the Interrupt Identification Register (IIR).

The IIR, when addressed during chip-select time, freezes the highest priority interrupt pending and no other interrupts are acknowledged until the particular interrupt is serviced by the CPU. Bits 3-0 are further described in Table 3-7.

## Address A2-A0 = 2, DLAB = X - Read only

| 7 | 6   | 5 | 4 | 3 | 2  | 1 | 0 |

|---|-----|---|---|---|----|---|---|

| F | ERO | 0 | 0 |   | ĪP |   |   |

|   |     |   |   |   |    |   |   |

| Signal<br>Name |   |  |  |   |   |   |   | Default After<br>Master Reset |

|----------------|---|--|--|---|---|---|---|-------------------------------|

| FERO           |   |  |  |   |   |   |   | 00                            |

| <u>IID</u> .   |   |  |  | - |   | · | · | 000                           |

| ĪP.            | • |  |  | - | • | • | • | 1                             |

## Bits 7, 6 - FERO, FIFO Enable

The FERO bits identify whether the FIFO Control Register bit 0, has placed the device in the Character Mode or FIFO Mode.

FERO = 0 0 -The device is in the Character Mode

FERO = 11-

The device is in the FIFO Mode.

Bits 5, 4 - These bits are always logic 0.

#### Bits 3-1 - IID, Interrupt ID

The IID bits identify the highest priority interrupt pending (see Table 3-7).

#### Bit 0 - IP, Interrupt Pending

The IP bit can be used in either a hardwired prioritized or polled environment to indicate whether an interrupt is pending.

#### $\overline{IP} = 0$ -

An interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine.

#### ĪP = 1 -

No interrupt is pending and polling (if used) continues.

| INTER | RUPT IDI<br>REGIS <sup>-</sup> |       | ATION       |                   | INTERRUPT S                                 | ET AND RESET FU                                                                                                                                                             | NCTIONS                                                                                                           |

|-------|--------------------------------|-------|-------------|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Bit 3 | IID<br>Bit 2                   | Bit 1 | TP<br>Bit 0 | Priority<br>Level | Interrupt<br>Flag                           | Interrupt<br>Source                                                                                                                                                         | Interrupt<br>Reset Control                                                                                        |

| 0     | 0                              | 0     | 1           |                   | None                                        | None                                                                                                                                                                        |                                                                                                                   |

| 0     | 1                              | 1     | 0           | Highest           | Receiver<br>Line Status                     | Overrun Error<br>or Parity Error<br>or Framing Error<br>or Break Interrupt                                                                                                  | Reading the<br>Line Status<br>Register                                                                            |

| 0     | 1                              | 0     | 0           | Second            | Received Data<br>Available                  | Receiver Data<br>Available                                                                                                                                                  | Reading the<br>Receiver Buffer<br>Register or FIFO<br>dropping below<br>the trigger level                         |

| 1     | 1                              | 0     | 0           | Second            | Character<br>Timeout<br>Identification      | No Characters<br>have been input<br>or removed from<br>RCVR FIFO<br>during the last<br>4 character times,<br>and at least one<br>character occupies<br>it during this time. | Reading the<br>Receiver Buffer<br>Register                                                                        |

| 0     | 0                              | 1     | 0           | Third             | Transmitter<br>Holding<br>Register<br>Empty | Transmitter<br>Holding<br>Register<br>Empty                                                                                                                                 | Reading the IIR<br>Register (if source<br>of interrupt) or<br>Writing into the<br>Transmitter<br>Holding Register |

| 0     | 0                              | 0     | 0           | Fourth            | MODEM<br>Status                             | Clear to Send<br>or Data Set or<br>Ring Indicator<br>or Received Line<br>Signal Detect                                                                                      | Reading the<br>MODEM Status<br>Register                                                                           |

| <b>TABLE 3-7.</b> | INTERRUPT | CONTROL  | FUNCTIONS |

|-------------------|-----------|----------|-----------|

|                   |           | 00111102 |           |

## 3.7 INTERRUPT ENABLE REGISTER

When INT (bit 3 of Modern Control Register) is a logic 1, the Interrupt Enable Register controls the selection of the four interrupt sources of the ACE, making it possible to separately activate the device's internal Interrupt signals.

It is possible to disable the entire interrupt system, or selected interrupts by configuring bits three though zero of the Interrupt Enable Register.

Disabling the interrupt system inhibits the Interrupt Identification Register and the active internal interrupt signal. All other system functions operate in their normal manner, including the setting of the Line Status and MODEM Status Registers.