### 1.0 INTRODUCTION

This introduction contains the following information:

- Product Scope

- Product Features

- General Description

### 1.1 SCOPE

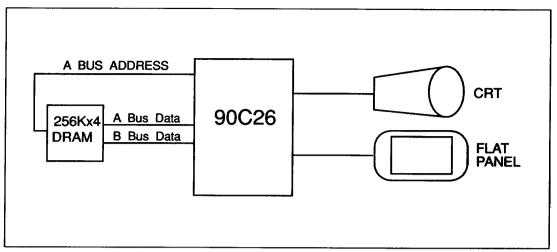

The WD90C26 VGA Laptop Display Controller allows control of a flat-panel display, along with simultaneous display on a traditional CRT. The WD90C26 supports all of today's mono and color flat-panel technologies.

The WD90C26 has improved power management capabilities and a performance-scaling capability that makes it an ideal video solution for low battery drain portable computer applications.

### 1.2 FEATURES

- True 64-gray scale in including 640 by 480 by 256 mode

- Simultaneous display (with all types of flatpanels)\*

- WD90C26LV low voltage version available

- On-board VGA compatible RAMDAC

- Zero wait-state performance

- Adjustable video FIFO depth and fast page mode memory timing

- System interface write buffering

- Flexible display memory configuration (2, 3 or four 256K by 4 DRAMs or one 256K by 16 DRAM)

- 8- or 16-bit I/O and memory interface

- True 16-bit CPU to display memory data transfer in all modes

- 27K colors on 9-bit TFT color LCD panel, 256K colors on 9-bit STN LCD panel, and 4K undithered direct colors on 12-bit TFT color LCD panel

- Full screen presentation in simultaneous display mode

- Hardware auto-centering and vertical expansion

- Up to 16 loadable fonts

- Supports 800 by 600 by 256 and 1024 by 768 by 16 non-interlaced modes on CRT display

- Hidden register support for 100% hardware compatibility with IBM's VGA standards

- 100% compatibility with CGA, MDA, Hercules Graphics

- Typical power dissipation of 450 mW at 5V operation

- Up to 65 MHz maximum video clock rate on CRT display

- Up to 45 MHz maximum video clock rate on LCD display

- Up to 45 MHz maximum memory clock rate

- On-chip 8/16-bit ISA Bus (AT bus) interface

- On-chip 8- or 16-bit Micro Channel interface

- I/O mapping improves board level testability

- Enhanced power down management modes

- 144-pin EIAJ package

- Compatible with WD90C55 color STN LCD interface

- \* Patent pending

### 1.3 GENERAL DESCRIPTION

The Western Digital WD90C26 is a 0.9 micron CMOS VGA controller designed to simultaneously drive a flat-panel display and the traditional analog CRT with a minimum of external components. The only additional components required for a complete flat-panel VGA subsystem are 1, 2, 3, or 4 DRAMs and video/memory clock sources. Contained onboard are a RAMDAC and a flat-panel interface. The full-featured RAMDAC is capable of directly driving P/S2 style analog color or monochrome

16

monitors. The full-featured flat-panel interface is capable of supporting LCD, plasma, and EL and other flat-panel technologies.

The WD90C26's scalable architecture allows it to be used with either 2, 3, or 4 external 256K by 4 DRAMs or one 256K by 16 DRAM. Basic VGA performance is available with the minimum 2 DRAM configuration or the single 256K by 16 DRAM configuration. Added panel support and enhanced VGA modes are available using 3 or 4 256K by 4 DRAMs. 16-bit video memory performance is also available using the 4 256K by 4 DRAM configuration or the single 256K by 16 DRAM configuration or the single 256K by 16 DRAM configuration. DRAM utilization is firmware controllable, allowing the scaling of DRAM power consumption or increasing performance.

Western Digital's superior orthogonal 64-gray scale to 64-gray scale mapping technology allows system developers to 'hand tune' each of the shades in the 64-gray scale to provide the most realistic linear gray scale shading for a particular panel. This is achieved through use of a firmware programmable 64-word gray scale lookup table on-board the WD90C26.

As with all Western Digital VGA offerings, the WD90C26 is 100% compatible with IBM VGA, CGA, MDA, and Hercules video systems. Through the use of its hidden, or 'shadow' registers, the WD90C26 can be programmed to support fixed-LCD screen sizes, yet appear to the host as capable of displaying the variety of screen pitches available with analog monitors. System routine modifications to video system registers, thus shadowed or hid-

den, do not destroy the WD90C26's ability to display the desired information on a flat-panel display as well.

The WD90C26's auto-centering and vertical expansion features provide full-screen flat-panel displays even in video modes with lower resolutions than those of the panel. A unique expansion algorithm provides for realistic appearance of both text and graphics on expanded displays, without requiring the use of special expanded display fonts.

Advanced power management features include:

- Separate supply pins for certain functions so that parts of the chip may be externally powered off

- The capability to slow down internal clocks to conserve power and to deactivate or tristate I/O pins during power-down and reset modes

- Power sequencing that can be used to control power supply and interface signals, and to prevent panel burnout

Also included in the WD90C26 is an advanced TFT support circuit that allows display from a palette of 27K colors on 9-bit interface color panels.

The WD90C26 directly supports TFT displays with 12-bit interfaces with undithered 12-bit direct colors from a 4K palette for optimum 12-bit display performance.

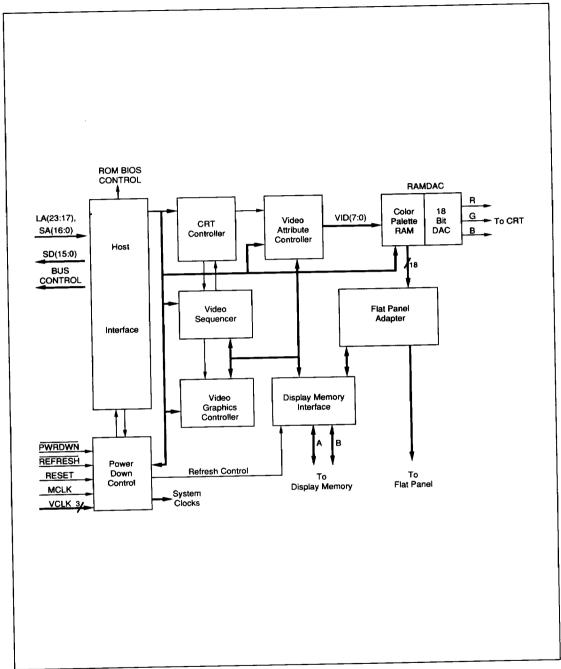

### 2.0 ARCHITECTURE

This section describes the architecture of the WD90C26. A block diagram of the architecture is shown in Figure 2-1. The components described are:

- System Interface Logic

- CRT Controller

- · Video Sequencer

- Video Graphics Controller

- Video Attribute Controller

- RAMDAC

- Flat Panel Adapter

- Display Memory Interface

- Power-Down Control

### 2.1 SYSTEM INTERFACE LOGIC

The WD90C26 includes a host system interface for direct connection to an ISA standard bus or IBM compatible Micro Channel. The interface allows the following features:

- Full 16-bit I/O and memory cycles

- Zero wait-state performance capability

- 16-bit to 8-bit data path conversion

- Full decoding of 16 MBytes of memory space for mapping of video memory, without requiring external decode logic

- Internal buffering of system operations to speed performance

- External video BIOS ROM

### 2.2 CRT CONTROLLER

A VGA-compatible CRT controller includes the following functions:

Generates video buffer addresses for screen refresh operations

- Generates monitor synchronization signals

- Controls an alpha-numeric cursor

- May be set with remapped register locations to operate as a CGA, MDA, or Hercules

- Register shadowing

### 2.3 VIDEO SEQUENCER

The VGA compatible video sequencer is the central timing and memory control section of the WD90C26. Its functions include the following:

- · Generation of memory handshake signals

- Control of CRT controller timings

- Provision of general interface timing and control signals to the balance of the WD90C26

### 2.4 VIDEO GRAPHICS CONTROLLER

The VGA video graphics controller performs VGA graphics operations on video data such as AND, OR, XOR, rotate, and color comparison functions.

### 2.5 VIDEO ATTRIBUTE CONTROLLER

The WD90C26's video attributes are added to display data by the Video Attribute Controller. Data added includes:

- Standard text attributes

- VGA graphics mode attributes

- Cursor display

- Screen border color

The Video Attribute Controller also performs data conversion from modes like packed pixel, planar, or text mode into video data to be presented to the RAMDAC.

### 2.6 RAMDAC

Integrated into the WD90C26 is a fully VGA-compatible high-speed 18-bit RAMDAC. This RAMDAC directly drives VGA and super-VGA color or monochrome analog monitors.

### 2.7 FLAT-PANEL ADAPTER

The flat-panel adapter takes video information from the WD90C26's internal RAMDAC color palette RAM and converts it into the format appropriate for the type of panel to be attached.

The following functions occur in the flat-panel adapter:

- "Digital DAC" color to monochrome gray scale conversion

- Gray scale mapping

- Gray shade dithering

- Color STN LCD panel dithering circuitry

- Row buffering

- Frame buffering

- Panel format conversion

# 2.7.1 Color to Gray Scale Conversion

For monochrome flat-panel display of what normally would be a color analog video output, a digital equivalent of the RAMDAC function is required to sum color information together into video signals. This function is accomplished through use of a digital equivalent of the DAC function, which takes the RGB color to gray scale weighting color palette RAM outputs and converts them to their digitally weighted monochrome equivalent. Weighting is performed using NTSC standard algorithms, and may be disabled for Monochrome Display Adapter emulation applications.

# 2.7.2 Gray Scale Mapping

The WD90C26's flat-panel adapter circuitry incorporates an orthogonal 64-word by 64 gray-scale to gray-shade mapping RAM. This mapping RAM serves as a firmware-programmable lookup table that may be configured to map gray scale value from

color-to-gray scale conversion into the dithered gray-scale shades best suited to a particular panel model.

Maximum flexibility in 'tuning' the WD90C26 to work with a particular panel model's characteristics is possible via this mapping RAM. Its size also allows finer control when selecting dithering patterns from the 64-shade monochrome dithering circuitry, allowing any monochrome panel to perform to its best in displaying visually accurate gray scales.

Control of gray scale selection is facilitated by the WD OEM User Utility. Please refer to the application note for details.

# 2.7.3 Gray Shade Dithering

Monochrome gray shade dithering circuitry provides a total of 64 shades of gray on monochrome flat-panel displays. All 64 shades may be simultaneously displayed. Simultaneous display of 64 shades in VGA modes is possible in 256 color modes only.

# 2.7.4 Color STN Dithering

For color 4-bit interface STN panels, the WD90C26 dithering circuitry supports color display from the full 256K VGA palette.

# 2.7.5 Color TFT Panel Dithering Circuitry

For Color TFT panels, dithering circuitry supports a total of 27K colors 9-bit interface panels.

# 2.7.6 Direct 12-bit TFT Panel Support

The WD90C26 drives 12-bit TFT panels with direct undithered color for a palette of 4K colors.

# 2.7.7 Row Buffering

Monochrome dual-panel displays (most monochrome LCDs) can be directly supported by the WD90C26 due to its capability to internally buffer alternate panel rows.

When simultaneous display on CRT and monochrome dual panel displays is not required, no external frame buffer memory is needed to support a monochrome dual-panel style LCD.

# 2.7.8 Frame Buffering

The WD90C26 includes a frame buffering capability that allows simultaneous display on a CRT and on a dual-panel monochrome display. This function requires that a 256K by 4 DRAM be attached to the Bank B memory interface.

When simultaneous display is not required, the WD90C26's internal row buffering provides all the required support for a dual-panel display.

### 2.7.9 Panel Format Conversion

The internal panel format conversion circuit provides the flexibility to reformat color or monochrome panel data into the particular pixel grouping required.

# 2.8 DISPLAY MEMORY INTERFACE

The display memory interface that maps videomemory DRAM is controlled by two separate external memory buses. These buses allow the accommodation of the changing needs of peformance, support feature, and power conservation. Descriptions of these buses follow.

The Bank A bus is used for interfacing to 8-bit video memory configurations, or as the lower byte 16-bit video memory configurations.

The Bank B bus is used as the frame buffer interface when simultaneous display on a CRT and a dual-panel display is desired.

When simultaneous display with a dual-panel display is not required, the Bank B bus can either be used to access the upper byte of a 16-bit video memory, or shut down to conserve power.

### 2.9 POWER-DOWN CONTROL

The WD90C26's ability to control power consumption allows it to work successfully in portable applications. Power consumption is managed by the power-down control block, which performs the following functions:

- Turns off clocks to unused portions of the WD90C26

- Provides refresh signals to video memory when normal refresh functions are shut down

- Controls wakeup/sleep cycling

- Reduces chip power during power-down mode

- Sequences chip reset operations

FIGURE 2-1. WD90C26 BLOCK DIAGRAM

#### 3.0 **INTERFACES**

#### 3.1 INTRODUCTION

This section describes the following WD90C26 interfaces:

- System Interface Allows the WD90C26 to directly interface to ISA bus-based systems or to Micro Channel-based systems

- BIOS Support Interface Allows the WD90C26 to provide an enable output for external video BIOS memory

- Video Memory Interface Allows connection of either 2, 3, or 4 256K by 4 DRAMS or one 256K by 16 DRAM

- Video Interface Alllows direct connection to most PC-compatible CRTs and to a wide range of industry-standard flat-panel types

- Clock Interface Controls clock oscillators or allows up to four separate frequency inputs

- Power Management Interface Allows control of chip power consumption

#### 3.2 SYSTEM INTERFACE

The WD90C26 is designed to directly interface to ISA bus based systems or to Micro Channel based systems.

System interface selection is done by pulling high or low a video memory data line at time of chip reset.

For both Micro Channel and ISA Bus operations. the WD90C26 is mapped into the system I/O address space as the standard set of video I/O registers for the particular video system being emulated.

Four extensively indexed registers at locations 3B5h/3D5h and 3C5h and 3CFh are used to control the vast amount of features beyond those of standard VGA operation.

The WD90C26 has a 1-1/2 word write buffer which operates as a 2-cycle write buffer. This allows the WD90C26 to operate with a very high percentage of true zero wait state performance.

The WD90C26 is designed to be a portable computing device where driving a large capacitive bus, such as found in traditional PCs, is not a factor. To reduce power consumption, the WD90C26's system interface has been designed to drive typical loadings found in laptop applications where bus devices are few and closely grouped.

### 3.2.1 ISA Bus Interface

The WD90C26 interfaces to an ISA bus at bus clock rates of up to 12.5 MHz. The WD90C26 supports full 16-bit memory and I/O transfers. Support of 16-bit memory transfers is independent of whether the WD90C26 has an 8-bit or 16-bit video memory path, although increased performance occurs when a 16-bit video memory is available.

The following ISA Bus signals are directly supported by the WD90C26:

| LA[23:17]   | ĪOW        |

|-------------|------------|

| SA [16:0]   | MEMCS16    |

| <u>BALE</u> | IOCS16     |

| SBHE        | IOCHRDY    |

| AEN         | SRDY (OWS) |

| SD[15:0]    | REFRESH    |

| MEMR        | RESET      |

| MEMW        | IRQ        |

| IOR         |            |

LA addresses are latched internal to the WD90C26 by the ALE signal to eliminate bus timing problems in some common system implementations.

16

FIGURE 2-2. 90C26 BLOCK DIAGRAM, FLAT PANEL ADAPTER SECTION

### 3.3 MICROCHANNEL INTERFACE

The WD90C26 directly supports the following Micro Channel interface signals:

| <u>A[23</u> :0] | SBHE          |

|-----------------|---------------|

| ADL             | <u>50</u>     |

| CDSFDBK         | <del>S1</del> |

| M/IO            | IRQ           |

| D[15:0]         | CDSETUP       |

| CDDS16          | CHRESET       |

| CDCHRDY         | REFRESH       |

| CMD             | MADE24        |

In addition, the WD90C26 supports both an internal and external decode of I/O address 3C3 bit 0 as a video memory and I/O decode enable.

For full Micro Channel compatibility, only the lower 16 bits of system address bus are decoded for I/O accesses.

### 3.4 BIOS SUPPORT INTERFACE

The WD90C26 can be configured to provide an enable output for external video BIOS memory. The WD90C26 can support 8- or 16-bit BIOS widths and can be configured to automatically map this external BIOS in to the system memory map at time of reset, and then selectively map it in or out thereafter. Decodes of the 32K of VGA video BIOS address space as defined in the VGA architecture are provided, with an ability to dynamically map out the highest 2K of the 32K space.

### 3.5 VIDEO MEMORY INTERFACE

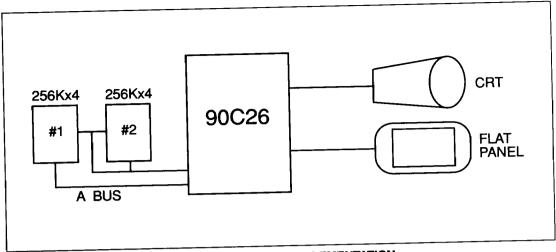

The WD90C26 is designed to operate with either 2, 3, or 4 256K by 4 DRAMs or a single 256K by 16 DRAM, with a variety of performance available at each step. The figure on the next page illustrates this implementation.

FIGURE 3-1. 2 DRAM IMPLEMENTATION

# 3.5.1 2 DRAM Implementation

In this implementation, the WD90C26 can support the following:

- simultaneous display on a CRT and any nondual-panel flat-panel display such as active matrix (TFT), multiplexed (STN) color, plasma, and EL.

- non-simultaneous display with a dual-panel multiplexed (STN) LCD or mono.

256 color mode in a 640 by 400 resolution display.

This memory configuration provides for the lowest active power utilization since only two external DRAMs are active. During this time, Bus B memory connections are held static or tri-stated for minimum power dissipation.

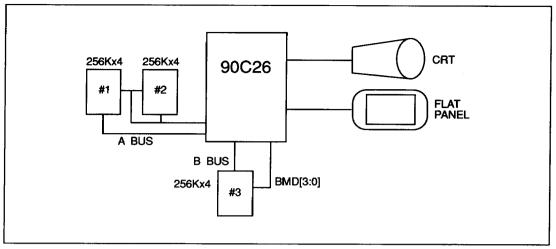

FIGURE 3-2. 3 DRAM IMPLEMENTATION

### 3.5.2 3 DRAM Implementation

When 3 DRAMs are used, the WD90C26 can additionally support the following:

simultaneous display of a CRT and a dualpanel multiplexed(STN) LCD display.

The upper nibble of the B bus memory data BMD[7:4] remains tri-stated during the three DRAM mode.

DRAM #3 may be disabled under firmware control when this simultaneous display feature is not needed, allowing power savings when the two displays are not simultaneously connected or when the flat-panel is not a dual-panel type.

16

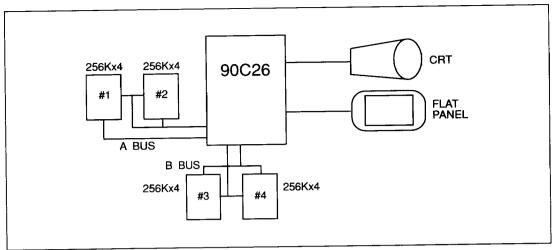

FIGURE 3-3. 4 DRAM IMPLEMENTATION

### 3.5.3 4 DRAM Implementation

In addition to the features of the 2 DRAM and 3 DRAM modes, the following feature is supported:

the ability to use 16-bit 512K video RAM except in those occasional times when a dual panel multiplexed display and a CRT are used simultaneously.

Bank B of DRAM may also be disabled by firmware for power reduction, and as before DRAM #3 may be used alone for simultaneous display support of a dual panel display and CRT, while DRAM #4 is disabled.

FIGURE 3-4. SINGLE 256K BY 16 IMPLEMENTATION

# 3.5.4 Single 256K by 16 DRAM implementation

The WD90C26 may be used with a single 2 CAS 256K by 16 DRAM, providing 512K of video memory and 16-bit memory performance. Simultaneous display operation with all flat-panel types except dual-panel LCD's Is allowed.

### 3.6 VIDEO INTERFACE

The WD90C26 supports a number of video interfaces allowing it to directly connect to most PC compatible CRTs and to a wide range of industry-standard flat-panel types. This support is achieved through configurable CRT and flat-panel interfaces.

### 3.6.1 Flat Panel Interface

One of the key features of the WD90C26 is a configurable video output port designed for support of a number of flat-panel technologies. This port is designed to directly support the following flat-panel types without requiring external interface formatting circuitry:

- Monochrome STN multiplexed dual panel LCD displays with one upper panel pixel and one lower panel pixel per clock, one bit per pixel interfaces.

- Monochrome plasma panel displays with one pixel per clock, 4 bits per pixel interfaces.

- Monochrome EL panel displays with one pixel per clock, 4 bits per pixel interfaces.

- Monochrome TFT panel displays with one pixel per clock, 4 bits per pixel interfaces

- Color STN single panel multiplexed LCD displays with one pixel triad per clock, 3 bits per pixel triad (one red, one green, one blue) interfaces.

- Color single panel active matrix TFT LCD displays with one pixel per clock, 3 bits per pixel interfaces.

- Color single panel active matrix TFT LCD displays with one pixel per clock, 4 bits per pixel interfaces.

Programmable flat-panel timing signals allow wide degrees of flexibility in configuring panel interfaces, making the WD90C26 usable with most popular flat-panel designs for PC applications.

For flat panel designs with more unique timing requirements, the WD90C26 is designed to directly interface with the WD90C55 Color Interface Device.

### 3.6.2 Analog CRT Interface

The WD90C26 includes a complete VGA compatible CRT interface with on-board 256 by 18-bit RAMDAC, which can directly drive analog VGA compatible color or monochrome displays. The interface is also capable of driving older EGA or monochrome compatible displays.

# 3.6.3 External RAMDAC Interface

For applications where use of an external RAMDAC or equivalent external function is desired, the WD90C26's flat-panel interface can be configured as an industry-standard RAMDAC interface instead of flat-panel pixel data. This allows the WD90C26 to be used in applications where a 24-bit RAMDAC is needed or where special panel pixelization techniques are required.

### 3.7 CLOCK INTERFACE

The WD90C26 has four clock input signal pins:

- VCLK0

- VCLK1

- VCLK2

- VCLK3

Three of these (VCLK 2, 1, and 0) are normally connected to oscillators. VCLK1 and VCLK2 may be configured to control an external clock multiplexor or clock generator. In this configuration, VCLK0 becomes the clock input while VCLK1 and VCLK2 become outputs used to drive the multiplexor select inputs.

The memory clock input, MCLK, is used by the internal logic to generate all memory timing and may be up to 45 MHz for 70nsec DRAMs.

# 3.8 POWER MANAGEMENT INTERFACE

The WD90C26's power management interface controls power-down mode operations including DRAM refresh modes and four power reduction modes are available providing a range of function and power savings.

# 4.0 SIGNAL DESCRIPTIONS

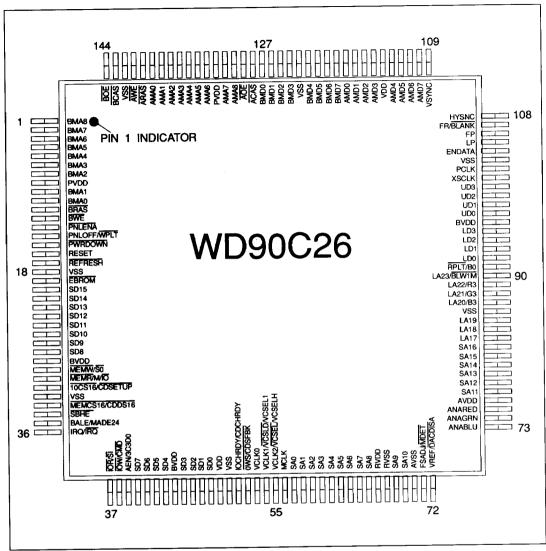

### 4.1 INTRODUCTION

This section contains a pin diagram, a pin table, and a signal description summary for the following groups of pins:

### **Clock Generation Interface**

VCLK0/VCKIN

VCLK1/VCSLD/VCSEL1

MCLK

VCLK2/VCSEL/VCSELH

### **System Interface Pins**

| SD[15:8]       |

|----------------|

| MEMR/M/IO      |

| MEMCS16/CDDS16 |

| BALE/MADE24    |

| IOR/S1         |

| AEN/3C3D0      |

| OWS/CDSFBK     |

| LA[19:17]      |

| LA22/R3        |

| LA20/B3        |

| IRQ/IRQ        |

|                |

### Panel Interface

| HSYNC    | VSYNC  |

|----------|--------|

| FR/BLANK | XSCLK  |

| ENDATA   | LP     |

| FP       | PNLENA |

### **Power Down Control Pins**

| <b>PWRDWN</b> | RESET |

|---------------|-------|

| REFRESH       |       |

### **Display Buffer Memory Interface Pins**

| BMA[8:0] | BRAS     |

|----------|----------|

| BWE      | ACAS     |

| AOE      | AMA[8:0] |

| ARAS     | BCAS     |

| AWE      | BOE      |

### **Power Pins**

| VDD  | VSS  |

|------|------|

| PVDD | BVDD |

| AVDD | AVSS |

| RVDD | RVSS |

| BVDD | BVSS |

### Internal DAC Analog Interface

| ANARED     | ANAGRN       |

|------------|--------------|

| ANABLU     | PNLOFF/WPLT  |

| FSADJ/MDET | VREF/DACDISA |

FIGURE 4-1. WD90C26 PIN DIAGRAM, 144-PIN JEDEC PQFP PACKAGE

|      | PIN - NAME  |      | ME PIN - NAME |       | IN - NAME  | PIN - NAME    |  |

|------|-------------|------|---------------|-------|------------|---------------|--|

| 1 -  | BMA8        | 38 - | IOW/CMD       | 75 -  | ANARED     | 112 - AMD5    |  |

| 2 -  | BMA7        | 39 - |               | 76 -  | AVDD       | 113 - AMD4    |  |

| 3 -  | BMA6        | 40 - | SD7           | 77 -  | SA11       | 114 - VDD     |  |

| 4 -  | BMA5        | 41 - | SD6           | 78 -  | SA12       | 115 - AMD3    |  |

| 5 -  | BMA4        | 42 - | SD5           | 79 -  | SA13       | 116 - AMD2    |  |

| 6 -  | BMA3        | 43 - | SD4           | 80 -  | SA14       | 117 - AMD1    |  |

| 7 -  | BMA2        | 44 - |               | 81 -  | SA15       | 118 - AMD0    |  |

| 8 -  | PVDD        | 45 - | SE3           | 82 -  | SA16       | 119 - BMD7    |  |

| 9 -  | BMA1        | 46 - | SD2           | 83 -  | LA17       | 120 - BMD6    |  |

| 10 - | BMA0        | 47 - | SD1           | 84 -  | LA18       | 121 - BMD5    |  |

| 11 - | BRAS        | 48 - | SD0           | 85 -  | LA19       | 122 - BMD4    |  |

| 12 - | BWE         | 49 - | VDD           | 86 -  | VSS        | 123 - VSS     |  |

| 13 - | PNLENA      | 50 - | VSS           | 87 -  | LA20/B3    | 124 - BMD3    |  |

| 14 - | PNLOFF/WPLT | 51 - | IOCHRDY/      | 88 -  | LA21/G3    | 125 - BMD2    |  |

|      |             | •    | CDCHRDY       | 1 .   |            |               |  |

| 15 - | PWRDOWN     | 52 - | OWS/CDSBFK    | 89 -  | LA22/R3    | 126 - BMD1    |  |

| 16 - | RESET       | 53 - | VCLK0         | 90 -  | LA23/BLW1M | 127 - BMD0    |  |

| 17 - |             | 54 - | VCLK1/        | 91 -  | RPLT/B0    | 128 - ACAS    |  |

| ''   |             | •    | VCSLD/        | ••    | 2.,20      | 120 7.07.0    |  |

|      |             |      | VCSEL1        |       |            |               |  |

| 18 - | VSS         | 55 - | VCLK2/        | 92 -  | LD0        | 129 - AOE     |  |

|      |             | "    | VCEL/         |       |            | 123 1.02      |  |

|      |             |      | VCSELH        |       |            |               |  |

| 19 - | EBROM       | 56 - | MCLK          | 93 -  | LD1        | 130 - AMA8    |  |

| 20 - | SD15        | 57 - | SA0           | 94 -  | LD2        | 131 - AMA7    |  |

| 21 - | SD14        | 58 - | SA1           | 95 -  | LD3        | 132 - PVDD    |  |

| 22 - | SD13        | 59 - | SA2           | 96 -  | BVDD       | 133 - AMA6    |  |

| 23 - | SD12        | 60 - | SA3           | 97 -  | UD0        | 134 - AMA5    |  |

| 24 - | SD11        | 61 - | SA4           | 98 -  | UD1        | 135 - AMA4    |  |

| 25 - | SD10        | 62 - | SA5           | 99 -  | UD2        | 136 - AMA3    |  |

| 26 - | SD9         | 63 - | SA6           | 100 - | UD3        | 137 - AMA2    |  |

| 27 - | SD8         | 64 - | SA7           | 101 - |            | 138 - AMA1    |  |

| 28 - | BVDD        | 65 - | SA8           |       | PCLK       | 139 - AMA0    |  |

| 29 - | MEMW/SO     | 66 - | RVDD          |       | VSS        | 140 - ARAS    |  |

| 30 - | MEMR/M/IO   | 67 - | RVSS          |       | ENDATA     | 141 - AWE     |  |

| 31 - | IOCS16/     | 68 - | SA9           | 105 - |            | 142 - VSS     |  |

| 1.75 | CDSETUP     | 1 7  |               |       |            | - · · · · ·   |  |

| 32 - | VSS         | 69 - | SA10          | 106 - | FP         | 143 - BCAS    |  |

| 33 - | MEMCS16/    | 70 - | AVSS          | 107 - | FR/BLANK   | 144 - BOE     |  |

| =    | CDDS16      | -    |               |       |            | , <del></del> |  |

| 34 - | SBHE        | 71 - | FSADJ/MDET    | 108 - | HSYNC      | 145 - N/A     |  |

| 35 - | BALE/MADE24 | 72 - | VREF/DACDISA  |       | VSYNC      | , , ,         |  |

| 36 - | IRQ/IRQ     | 73 - | ANABLU        | 110 - |            |               |  |

| 37 - | IOR/S1      | 74 - | ANAGRN        | 111 - | AMD6       |               |  |

|      |             |      |               |       |            |               |  |

**TABLE 4-1. PIN ASSIGNMENTS**

### 4.2 SYSTEM INTERFACE PINS

The following table describes each System Interface pin on the WD90C26. The WD90C26 system interface can be configured for either ISA bus or Micro Channel interface support by setting DCONF/2 high or low by pulling high or low the AMD2 pin at reset. Other configuration options may also be selected by setting configuration bits high or low at reset through pulling memory data lines high or low.

| PIN | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 16  | RESET    | I   | WD90C26's Initialization Signal Typical usage in ISA Bus based system: connected to ISA Bus RESET signal. Typical usage in Micro Channel based system: connected to Micro Channel RESETDRV signal.                                                                                                                                                                                                                                                                                                                   |  |

| 17  | REFRESH  | -   | Input Active Low DRAM Refresh The WD90C26 uses this input to initiate refresh operations to its video buffer memory. It also uses this signal as a negative qualifier for memory read operations.                                                                                                                                                                                                                                                                                                                    |  |

| 19  | EBROM    | 0   | Enable BIOS ROM In BIOS ROM Map-in mode, where CONF(0)=0 the WD90C26 drives this output low when it decodes system accesses to video BIOS ROM and a memory read operation is requested from an address range identified within the WD90C26 as a video BIOS ROM address. If CONF(0)=1 this pin remains inactive high.                                                                                                                                                                                                 |  |

| 29  | MEMW/S0  |     | Memory Write MEMW if CONF(2)=1 (ISA Bus Mode). Memory write input from ISA bus.  Decode MicroChannel Bus Cycles S0 if CONF(2)=0 (Micro Channel Mode).  When the WD90C26 is in ISA Bus mode. This pin is the industry standard MEMW bus signal, and indicates to the WD90C26 that a memory write bus cycle is occurring.  When the WD90C26 is in Micro Channel mode, this pin is the Micro Channel S0 channel status input, which the WD90C26 uses, along with S1, M/IO, and CMD, to decode Micro Channel bus cycles. |  |

**TABLE 4-2. SYSTEM INTERFACE PINS**

| PIN  | MNEMONIC       | I/O         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30   | MEMR/M/IO      | ı           | Memory Read MEMR if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                                                                                                                         |

|      |                |             | When the WD90 <u>C26 is in ISA</u> Bus mode, this pin is the industry-standard MEMR bus signal. This indicates to the WD90C26 that a memory read bus cycle is occurring.                                                                                                                                                                                                              |

|      |                |             | Because MEMR may also be active during refresh cycles, the WD90C26 internally gates MEMR with REFRESH.                                                                                                                                                                                                                                                                                |

|      |                |             | Memory/IO Cycle<br>M/IO if CONF(2)=0 (Micro Channel Mode)                                                                                                                                                                                                                                                                                                                             |

| 1000 |                |             | When the WD90C26 is in Micro Channel mode, this pin is the M/IO signal from the Micro Channel bus. A high input at this pin is interpreted by the WD90C26 as a Micro Channel Bus Memory cycle. A signal at this pin indicates a Micro Channel Bus I/O cycle to the WD90C26.                                                                                                           |

| 31   | IOCS16/CDSETUP | I/O<br>O.C. | I/O Chip Select 16 IOCS16 if CONF(2)=1 (ISA Bus Mode). Open collector                                                                                                                                                                                                                                                                                                                 |

| -    |                |             | Indicates the WD90C26 supports 16-bit I/O operations at the "current"I/O address.                                                                                                                                                                                                                                                                                                     |

|      |                |             | In ISA Bus mode, pin 31 becoming active low is an indication to the ISA Bus that it supports 20-bit I/O transfers at the 16-bit I/O address being presented to it. Otherwise this pin is in a high-impedance state. IOCS16 is not gated by any other signals. Its function is independent of other bus control lines, bus modes, or register settings. IOCS16 is not affected by AEN. |

|      |                |             | Card Setup CDSETUP if CONF(2)=0 (Micro Channel Mode).                                                                                                                                                                                                                                                                                                                                 |

|      |                |             | In Micro Channel mode, this pin is the card setup input indicating to the WD90C26 to perform setup functions.                                                                                                                                                                                                                                                                         |

**TABLE 4-2. SYSTEM INTERFACE PINS (Continued)**

| PIN | MNEMONIC           | I/O       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33  | MEMCS16/<br>CDDS16 | O<br>O.C. | Memory Chip Select 16 MEMCS16 if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                                                                                                                   |

|     |                    |           | In ISA bus mode, pin 33 is an indication to the system that the WD90C26 supports 16-bit memory transfers at the system address being presented.                                                                                                                                                                                                                                              |

|     |                    |           | In ISA Bus applications, pin 33 is typically connected to the ISA Bus MEMCS16 signal.                                                                                                                                                                                                                                                                                                        |

|     |                    |           | Card Data Size 16 CDDS16 if CONF(2)=0 (Micro Channel Mode)                                                                                                                                                                                                                                                                                                                                   |

|     |                    |           | In Micro Channel applications pin 33 indicates a 16-bit resource available at the address.                                                                                                                                                                                                                                                                                                   |

| 34  | SBHE               |           | System Byte Hi Enable SBHE indicates to the WD90C26 the mapping of bytes into high or low registers on write operations and the ordering of high and low bytes during read operations.                                                                                                                                                                                                       |

| 35  | BALE/MADE24        | 1         | Address Latch Enable BALE if CONF(2)=1 (ISA Bus Mode)                                                                                                                                                                                                                                                                                                                                        |

| 5   |                    |           | Typical usage in ISA Bus based system: connected to ISA Bus BALE signal.                                                                                                                                                                                                                                                                                                                     |

|     |                    |           | When the WD90C26 is in ISA Bus mode this pin is the industry standard BALE signal input to the WD90C26. A high level is interpreted by the WD90C26 as an indication that the system address is setting up on its SA bus inputs to be latched on the falling edge of this signal. To ensure compatibility across a variety of platforms, the WD90C26 latches LA17-LA23 with the fall of BALE. |

|     |                    |           | Memory Address Enable 24 MADE24 if CONF(2)=0 (Micro Channel Mode).                                                                                                                                                                                                                                                                                                                           |

|     |                    |           | When the WD90C26 is in Micro Channel mode, this pin is the Micro Channel MADE24 input to the WD90C26 and is used by the WD90C26 as an indication that the system address is in the below-16 MBtye range.                                                                                                                                                                                     |

**TABLE 4-2. SYSTEM INTERFACE PINS (Continued)**

| PIN | MNEMONIC | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                    |

|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36  | IRQ/IRQ  | O   | Interrupt Request Active high if CONF(2)=1 (ISA Bus Mode), Active Low if in Micro Channel mode. Open Collector in Micro Channel mode.                                                                                                                                          |

|     |          |     | Description of function of IRQ in both ISA and Micro Channel Modes is as follows: When bit 5 of the VGA Vertical Retrace End Register (I/O Address-3?5h index 11) is set to 0, this signal is set active at the occurrence of the end of vertical display of a frame of active |

|     |          |     | video. IRQ stays active until cleared by momentarily setting bit 4 of the Vertical Retrace End Register to 0 and then back to 1.                                                                                                                                               |

|     |          |     | When bit 5 of the VGA Vertical Retrace End Register is set to 0 the activation of this pin is disabled, forcing its output to be low in ISA bus mode or high impedance in Micro Channel mode.                                                                                  |

|     |          |     | NOTE: This pin can only be configured or the interrupt cleared if the Vertical Retrace End Register is unlocked by setting PR3 bit 0 high.                                                                                                                                     |

| 37  | IOR/S1   | l   | I/O Read IOR if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                      |

|     |          |     | When the WD90C26 is in ISA Bus Mode, this pin indicates to the WD90C26 that an I/O read bus cycle is to occur. IOR may also be active during DMA cycles and is therefore internally qualified by AEN.                                                                          |

|     |          |     | S1 Cycle Decode<br>S1 if CONF(2)=0(Micro Channel Mode).                                                                                                                                                                                                                        |

|     |          |     | When the WD90C26 is in Micro Channel mode (AMD2 low at reset), this pin is the Micro Channel S1 channel status input, which the WD90C26 uses, along with S0, M/IO, and CMD, to decode Micro Channel bus cycles.                                                                |

| 38  | IOW/CMD  | ı   | I/O Write IOW if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                     |

|     |          |     | When the WD90C26 is in ISA Bus mode, this pin indicates to the WD90C26 that an I/O read bus cycle is to occur. The WD90C26 internally qualifies IOW write requests with AEN.                                                                                                   |

|     |          |     | <u>Com</u> mand<br>CMD if CONF(2)=0 (Micro Channel Mode)                                                                                                                                                                                                                       |

|     |          |     | When the WD90C26 is in Micro Channel mode, this pin is interpreted by the WD90C26 as the CMD signal from a Micro Channel bus. The WD90C26 uses this signal to properly decode cycle types.                                                                                     |

**TABLE 4-2. SYSTEM INTERFACE PINS (Continued)**

| PIN | MNEMONIC            | I/O       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39  | AEN/3C3D0           |           | Address Enable AEN if CONF(2)=1 (ISA Bus Mode).  When active high, this signal disables the WD90C26 from performing ISA bus read or write accesses. When low, system accesses to the WD90C26 are enabled.  Video Subsystem Enable Port, Data Bit 0 Input 3C3D0 if CONF(2)=0 (Micro Channel Mode).  This signal typically comes from bit 0 of I/O port 3C3h. A high input at this pin enables the WD90C26's ability to respond to Micro Channel bus accesses. In Micro Channel mode, I/O writes to the WD90C26 of a '1' to I/O port 3C3 bit 0 also enables the WD90C26.                                                                                                              |

| 51  | IOCHRDY/<br>CDCHRDY | O<br>O.C. | I/O Channel Ready Status IOCHRDY if CONF(2)=1 (ISA Bus Mode). I/O Channel Ready status when active high.  When the WD90C26 is in ISA Bus Mode (see section on configuration bits for description of use of AMD2 as a mode configuration pin), pin 51 is the industry-standard IOCHRDY bus signal, and indicates readiness of the WD90C26 in responding to ISA bus read and write cycles. When the WD90C26 cannot complete the desired bus cycle within the standard or 0 wait cycle times, it will de-assert IOCHRDY until it is ready to complete the transfer.                                                                                                                    |

|     |                     |           | Channel Ready CDCHRDY if CONF(2)=1 (Micro Channel Mode).  When the WD90C26 is in Micro Channel Mode, CONF(2)=0), pin 51 is the CDCHRDY signal to a Micro Channel bus. The WD90C26 drives this pin low when additional cycle time is required.  In Micro Channel mode, CDCHRDY is brought to its high-impedance inactive state by the rising edge of the signal to pin 48, CMD.  Under typical conditions of video memory speeds and bus rates, the WD90C26 does not cause IOCHRDY or CDCHRDY to go inactive low or cause CDCHRDY to occur later than the minimum requirement, except in certain instances when a write operation results in an internal write data buffer overflow. |

**TABLE 4-2. SYSTEM INTERFACE PINS (Continued)**

| PIN | MNEMONIC | 1/0  | DESCRIPTION                                                                                                                                                                                                                                                                                      |

|-----|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52  | ows      | 0    | Zero Wait State                                                                                                                                                                                                                                                                                  |

|     | CDSFBK   | O.C. | 0WS if ISA Bus Mode CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                                    |

|     |          |      | This pin is the WD90C26's indication of readiness to support zero wait state option. The description of PR32 includes information on how to configure the WD90C26's support of 0WS. The WD90C26 drives this signal low when 0 wait cycles can be supported. Otherwise this signal is tri-stated. |

|     |          |      | Card Selected Feedback                                                                                                                                                                                                                                                                           |

|     |          |      | CDSFBK if CONF(2)=1 (Micro Channel Mode).                                                                                                                                                                                                                                                        |

|     |          |      | Feedback to the Micro Channel interface of CD status.                                                                                                                                                                                                                                            |

|     |          |      | Driven active low by the WD90C26 as an acknowledgment of its selection. Does not go active if CDSETUP is active low. It is tri-stated when not being driven active low.                                                                                                                          |

**TABLE 4-2. SYSTEM INTERFACE PINS (Continued)**

# 4.2.1 System Interface Data Signals

SD3

SD2

SD1 SD1

45

46

47

48

| PIN     | MNEMONIC                                                                                                                                                                                                   | I/O        | DESCRIPTION                                                                                       |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------|--|--|--|

| bus arc | SD15 is the MSB and SD0 is the LSB of the 16-bit system data bus in ISA bus and Micro Channel bus architectures.  The WD90C26's system data signals may be directly connected to the host system data bus, |            |                                                                                                   |  |  |  |

| provide | d the WD90C26 drive                                                                                                                                                                                        | ers are ad | equate when host system data bus loading considerations are ecifics about bus drive capabilities. |  |  |  |

| 20      | SD15                                                                                                                                                                                                       | I/O        | System Data 15                                                                                    |  |  |  |

| 21      | SD14                                                                                                                                                                                                       | I/O        | System Data 14                                                                                    |  |  |  |

| 22      | SD13                                                                                                                                                                                                       | I/O        | System Data 13                                                                                    |  |  |  |

| 23      | SD12                                                                                                                                                                                                       | 1/0        | System Data 12                                                                                    |  |  |  |

| 24      | SD11                                                                                                                                                                                                       | I/O        | System Data 11                                                                                    |  |  |  |

| 25      | SD10                                                                                                                                                                                                       | I/O        | System Data 10                                                                                    |  |  |  |

| 26      | SD9                                                                                                                                                                                                        | I/O        | System Data 9                                                                                     |  |  |  |

| 27      | SD8                                                                                                                                                                                                        | I/O        | System Data 8                                                                                     |  |  |  |

| 40      | SD7                                                                                                                                                                                                        | 1/0        | System Data 7                                                                                     |  |  |  |

| 41      | SD6                                                                                                                                                                                                        | I/O        | System Data 6                                                                                     |  |  |  |

| 42      | SD5                                                                                                                                                                                                        | 1/0        | System Data 5                                                                                     |  |  |  |

| 43      | SD4                                                                                                                                                                                                        | I/O        | System Data 4                                                                                     |  |  |  |

TABLE 4-3. SYSTEM INTERFACE DATA SIGNALS

System Data 3

System Data 2

System Data 1

System Data 0

I/O

I/O

1/0

I/O

### 4.2.2 System Interface Address Signals

| PIN    | MNEMONIC            | I/O      | DESCRIPTION                                                   |

|--------|---------------------|----------|---------------------------------------------------------------|

| SA9-SA | 0 are used by the W | D90C26 a | s the I/O address during ISA bus or Micro Channel I/O cycles. |

SA16-SA0 are used as the lower 17 bits of the WD90C26's 24-bit memory address during ISA bus or Micro Channel memory cycles.

SA16 is the MSB and SA0 is the LSB of the 17-bit system address bus.

| OA TO I | CATO IS THE WICD AND CAO IS THE LOD OF THE 17-DIT SYSTEM ADDRESS DUS. |     |                   |  |  |

|---------|-----------------------------------------------------------------------|-----|-------------------|--|--|

| 57      | SA0                                                                   | 1   | System Address 0  |  |  |

| 58      | SA1                                                                   | 1   | System Address 1  |  |  |

| 59      | SA2                                                                   | ı   | System Address 2  |  |  |

| 60      | SA3                                                                   | 1   | System Address 3  |  |  |

| 61      | SA4                                                                   | i   | System Address 4  |  |  |

| 62      | SA5                                                                   | 1 . | System Address 5  |  |  |

| 63      | SA6                                                                   | t   | System Address 6  |  |  |

| 64      | SA7                                                                   | 1   | System Address 7  |  |  |

| 65      | SA8                                                                   | 1   | System Address 8  |  |  |

| 68      | SA9                                                                   | l   | System Address 9  |  |  |

| 69      | SA10                                                                  | 1   | System Address 10 |  |  |

| 77      | SA11                                                                  | 1   | System Address 11 |  |  |

| 78      | SA12                                                                  | 1   | System Address 12 |  |  |

| 79      | SA13                                                                  | I   | System Address 13 |  |  |

| 80      | SA14                                                                  | 1   | System Address 14 |  |  |

| 81      | SA15                                                                  | 1   | System Address 15 |  |  |

| 82      | SA16                                                                  | ı   | System Address 16 |  |  |

|         |                                                                       |     |                   |  |  |

LA19-LA17 are additional latchable system address signals. LA19 is the MSB of the 20 bit below-1-megabyte memory address bus in ISA bus and Micro Channel bus architectures, formed by using LA19-LA17 and SA16-SA0. The WD90C26 uses the resulting memory address, along with either the BLW1M signal or decodes of LA23-LA20, for accesses to its video memory buffer DRAM. In certain other modes, the WD90C26 uses the address formed by LA19-SA0, along with a 1MB block decode from LA23-LA20, to access the WD90C26's DRAM video buffer as above-1-megabyte memory.

In ISA bus mode CONF(2)=1), LA19-LA17 are inputs to a transparent latch internal to the WD90C26 that allows LA19-LA17 to propagate in, while BALE is active high. LA19-LA17 are then captured when BALE goes inactive low.

In Micro Channel Mode CONF(2)=0), LA19-LA17 are also address inputs.

### **TABLE 4-4. SYSTEM INTERFACE ADDRESS SIGNALS**

ADVANCED INFORMATION 11/25/91

16-25

| PIN | MNEMONIC   | I/O     | DESCRIPTION                                                                                                                                                                    |

|-----|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83  | LA17       | 1       | Latchable System Address 17                                                                                                                                                    |

| 84  | LA18       | 1       | Latchable System Address 18                                                                                                                                                    |

| 85  | LA19       | 1       | Latchable System Address 19                                                                                                                                                    |

| 87  | LA20/B3    | I/O     | Latchable System Address Bit 20                                                                                                                                                |

|     |            |         | LA20 if pull-up on MD 7 (Full Decode Mode).<br>Blue MSB for 12-bit panel interface.<br>B3 if pull-down on MD7 and in 12-bit panel mode.                                        |

| 88  | LA21/G3    | 1/0     | Latchable System Address Bit 21                                                                                                                                                |

|     |            |         | LA21 if pull-up on MD 7 (Full Decode Mode).<br>Green MSB for 12-bit panel interface.<br>G3 if pull-down on MD7 and in 12-bit panel mode.                                       |

| 89  | LA22/R3    | 1/0     | Latchable System Address Bit 22                                                                                                                                                |

|     |            |         | LA22 if CONF(7)=1 (Full Decode Mode). Red MSB for 12-bit panel interface. R3 if pull-down on MD7 and in 12-bit panel mode.                                                     |

| 90  | LA23/BLW1M | 1       | Latchable System Address Bit 23                                                                                                                                                |

|     |            | T V V V | LA23 if MSB of the 24-bit system address formed by LA(23:17) and SA(16:0).                                                                                                     |

|     |            |         | Below 1 megabyte Address Decode                                                                                                                                                |

|     |            |         | BLWIM if CONF(7)=1 (12-bit I/F mode). Active low input from external decode indicating that the system address is in the below-1-megabyte address range of 000000h to FFFFFFh. |

TABLE 4-4. SYSTEM INTERFACE ADDRESS SIGNALS (Continued)

# 4.3 DISPLAY BUFFER MEMORY INTERFACE PINS

The display memory interface is designed for connection of up to four 256K by 4 or one 256K by 16 fast-page-mode DRAMs. This section is divided into the following subsections, which provide tables describing the data signals below:

- · Bank A Video Memory Data Bus Signals

- · Bank B Video Memory Data Bus Signals

### 4.3.1 Bank A Video Memory Signals

| PIN    | MNEMONIC                                     | I/O      | DESCRIPTION                                                                                                                                                                                                              |  |  |

|--------|----------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        |                                              | BANK     | A VIDEO MEMORY DATA BITS                                                                                                                                                                                                 |  |  |

| 110    | AMD7                                         | I/O      | Bank A Memory Data Bit 7                                                                                                                                                                                                 |  |  |

| 111    | AMD6                                         | 1/0      | Bank A Memory Data Bit 6                                                                                                                                                                                                 |  |  |

| 112    | AMD5                                         | 1/0      | Bank A Memory Data Bit 5                                                                                                                                                                                                 |  |  |

| 113    | AMD4                                         | I/O      | Bank A Memory Data Bit 4                                                                                                                                                                                                 |  |  |

| 115    | AMD3                                         | 1/0      | Bank A Memory Data Bit 3                                                                                                                                                                                                 |  |  |

| 116    | AMD2                                         | 1/0      | Bank A Memory Data Bit 2                                                                                                                                                                                                 |  |  |

| 117    | AMD1                                         | 1/0      | Bank A Memory Data Bit 1                                                                                                                                                                                                 |  |  |

| 118    | AMD0                                         | 1/0      | Bank A Memory Data Bit 0                                                                                                                                                                                                 |  |  |

|        |                                              | BANK A   | /IDEO MEMORY ADDRESS BITS                                                                                                                                                                                                |  |  |

| 130    | AMA8                                         | 0        | Bank A Memory Address Bit 8                                                                                                                                                                                              |  |  |

| 131    | AMA7                                         | 0        | Bank A Memory Address Bit 7                                                                                                                                                                                              |  |  |

| 133    | AMA6                                         | 0        | Bank A Memory Address Bit 6                                                                                                                                                                                              |  |  |

| 134    | AMA5                                         | 0        | Bank A Memory Address Bit 5                                                                                                                                                                                              |  |  |

| 135    | AMA4                                         | 0        | Bank A Memory Address Bit 4                                                                                                                                                                                              |  |  |

| 136    | AMA3                                         | 0        | Bank A Memory Address Bit 3                                                                                                                                                                                              |  |  |

| 137    | AMA2                                         | 0        | Bank A Memory Address Bit 2                                                                                                                                                                                              |  |  |

| 138    | AMA1                                         | 0        | Bank A Memory Address Bit 1                                                                                                                                                                                              |  |  |

| 138    | AMA0                                         | 0        | Bank A Memory Address Bit 0                                                                                                                                                                                              |  |  |

|        | Primary 9-bit video buffer DRAM address bus. |          |                                                                                                                                                                                                                          |  |  |

| AMA8 i | s the MSB and AMA                            | the LSB. |                                                                                                                                                                                                                          |  |  |

| 128    | ACAS                                         | 0        | CAS Bank A                                                                                                                                                                                                               |  |  |

|        |                                              |          | Column address strobe for video memory buffer DRAM bank A, consisting of 256K by 4 DRAMs #1 and #2. When 256K by 16 DRAM is used, this is the lower CAS strobe output and the BCAS signal is the upper CAS strobe input. |  |  |

| 129    | AOE                                          | 0        | Output Enable Bank A                                                                                                                                                                                                     |  |  |

|        |                                              |          | Output Enable control for video memory buffer DRAM bank A. When 256K by 16 DRAM is used, this is the DRAM output enable strobe.                                                                                          |  |  |

**TABLE 4-5. BANK A VIDEO MEMORY SIGNALS**

16-27

| PIN | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                           |

|-----|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 140 | ARAS     | 0   | RAS Bank A                                                                                                                                                            |

|     |          |     | Row address strobe for video memory buffer DRAM banks A, consisting of 256K by 4 DRAMs #1 and #2. When a 256K by 16 DRAM is used, this is the DRAM RAS strobe output. |

| 141 | AWE      | 0   | Write Enable Bank A                                                                                                                                                   |

|     |          |     | Write Enable control for video memory buffer DRAM bank A. When a 256K by 16 DRAM is used this is the DRAM write enable output.                                        |

TABLE 4-5. BANK A VIDEO MEMORY SIGNALS (Continued)

WD90C26

# 4.3.2 Bank B Video Memory Signals

| PIN | MNEMONIC                      | I/O  | DESCRIPTION                                                                                                                  |  |  |

|-----|-------------------------------|------|------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | BANK B VIDEO MEMORY DATA BITS |      |                                                                                                                              |  |  |

| 119 | BMD                           | 1/0  | Bank B Memory Data Bit 7                                                                                                     |  |  |

| 120 | BMD                           | 1/0  | Bank B Memory Data Bit 6                                                                                                     |  |  |

| 121 | BMD                           | 1/0  | Bank B Memory Data Bit 5                                                                                                     |  |  |

| 122 | BMD                           | 1/0  | Bank B Memory Data Bit 4                                                                                                     |  |  |

| 124 | BMD                           | 10   | Bank B Memory Data Bit 3                                                                                                     |  |  |

| 125 | BMD                           | 1/0  | Bank B Memory Data Bit 2                                                                                                     |  |  |

| 126 | BMD                           | 10   | Bank B Memory Data Bit 1                                                                                                     |  |  |

| 127 | BMD                           | 1/0  | Bank B Memory Data Bit 0                                                                                                     |  |  |

|     |                               | BANK | B VIDEO MEMORY ADDRESS BITS                                                                                                  |  |  |

| 1   | ВМА                           | 0    | Bank B Memory Address Bit 8                                                                                                  |  |  |