# United States Patent [19]

### Pease et al.

### [54] INTERFACE AND CONTROL CIRCUIT FOR REGULATING DATA FLOW IN A SCSI INITIATOR WITH MULTIPLE HOST BUS INTERFACE SELECTION

- [75] Inventors: Allan F. Pease, San Jose; Richard Moore, Irvine, both of Calif.

- [73] Assignee: Future Domain Corporation, Incorporated, Irvine, Calif.

- [21] Appl. No.: 29,910

- [22] Filed: Mar. 11, 1993

### **Related U.S. Application Data**

- [63] Continuation-in-part of Ser. No. 667,754, Mar. 11, 1991, abandoned.

### [56] **References Cited**

### **U.S. PATENT DOCUMENTS**

| 4,062,059 | 12/1977 | Suzuki et al 3  | 95/250  |

|-----------|---------|-----------------|---------|

| 4,384,327 | 5/1983  | Conway et al 3  | 95/308  |

| 4,635,194 | 1/1987  | Burger et al 3  | 95/375  |

| 4,716,525 | 12/1987 | Gilanyi et al 3 | 95/250  |

| 4,785,415 | 11/1988 | Karlquist 3     | 395/550 |

| 4,843,544 | 6/1989  | DuLac et al 3   | 395/250 |

| 4,965,801 | 10/1990 | DuLac et al 3   | 71/40.1 |

| 4,975,829 | 12/1990 | Clarey et al 3  | 95/500  |

# [11] **Patent Number:** 5,544,326

## [45] Date of Patent: Aug. 6, 1996

| 5,101,498 | 3/1992  | Ehlig et al       | 395/800 |

|-----------|---------|-------------------|---------|

| 5,185,876 | 2/1993  | Nguyen et al      | 395/841 |

| 5,237,660 | 8/1993  | Weber et al       | 395/250 |

| 5,241,630 | 8/1993  | Lattin, Jr. et al | 395/250 |

| 5,276,807 | 1/1994  | Kodama et al      | 395/309 |

| 5,287,460 | 2/1994  | Olsen et al       | 395/883 |

| 5,289,580 | 2/1994  | Latif et al.      | 395/883 |

| 5,299,315 | 3/1994  | Chin et al        | 395/250 |

| 5,371,861 | 12/1994 | Keener et al.     | 395/309 |

#### FOREIGN PATENT DOCUMENTS

| 287301A2 | 10/1988 | European | Pat. | Off. |  |

|----------|---------|----------|------|------|--|

| 451516A1 | 10/1991 | European | Pat. | Off. |  |

### OTHER PUBLICATIONS

National Semiconductor, Advanced Peripherals Mass Storage Handbook, Section 6, SCSI Bus Interface Circuits, pp. 6–3–6–22.

Primary Examiner-Krisna Lim

Assistant Examiner-Viet Vu

Attorney, Agent, or Firm—Skjerven, Morrill, MacPherson, Franklin & Friel

### [57] ABSTRACT

A single chip SCSI controller circuit has a pair of input and output first in, first out (FIFO) buffers as well as a main buffer. The circuit supports synchronous and asynchronous data transfers which are fully compatible with the SCSI-II specification. A mode select pin may be selectively actuated by the user or by attached interface circuitry to configure the chip for either microchannel architecture (MCA) or industry standard architecture (ISA) compatibility.

### 14 Claims, 48 Drawing Sheets

**U.S.** Patent

5,544,326

FIG. 9B

U.S. Patent

240

.

FIG. 31

| OE<7:0>                      |                                                                                                                                                              |                                                                            |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| OD<7:0>                      | 4                                                                                                                                                            |                                                                            |

| OCK12<br>OCO12               | 0<br>1<br>2<br>3<br>3<br>4<br>4<br>5<br>6<br>6<br>7<br>8<br>0<br>8<br>7<br>8<br>0<br>8<br>0<br>5<br>0<br>5<br>0<br>5<br>0<br>5<br>0<br>5<br>0<br>5<br>0<br>5 | 1Q 0<br>2Q 1<br>3Q 2<br>3Q 3<br>4Q 4<br>5Q 5<br>6Q 6<br>7Q 6<br>7Q 7<br>8Q |

| <u>OCK13</u><br><u>OCO13</u> | 0<br>1<br>2<br>3<br>4<br>4<br>5<br>6<br>7<br>8<br>0<br>5<br>6<br>7<br>8<br>0<br>5<br>6<br>7<br>0<br>5<br>6<br>7<br>0<br>5<br>6<br>7<br>0<br>5<br>0<br>5      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                     |

| OCK14<br>OCO14               | 0 1D<br>1 2D<br>3 3D<br>4 5D<br>5 6D<br>7 8D<br>7 8D<br>0E                                                                                                   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                     |

| OCK15<br>OC015               | 0 1D<br>1 2D<br>2 3D<br>3 4D<br>4 5D<br>6 6D<br>7 8D<br>CLI<br>0E                                                                                            | 1Q 0<br>2Q 1<br>3Q 2<br>3Q 3<br>4Q 4<br>5Q 5<br>6Q 6<br>7Q 7<br>8Q 7       |

10

### INTERFACE AND CONTROL CIRCUIT FOR **REGULATING DATA FLOW IN A SCSI INITIATOR WITH MULTIPLE HOST BUS INTERFACE SELECTION**

#### RELATED APPLICATION

This is a continuation-in-part application of our pending application Ser. No. 07/667,754, filed on Mar. 11, 1991, entitled SCSI CONTROLLER, now abandoned.

## BACKGROUND AND SUMMARY OF THE **INVENTION**

The invention relates generally to computer bus interface circuitry. More particularly, the invention relates to an 15 interface circuit, for connecting one of a selected plurality of different computer buses to the Small Computer System Interface (SCSI) bus. The circuit is well suited for single chip implementation. Dual first in, first out (FIFO) buffers are used to provide a circuit which supports both asynchro-20 nous and synchronous modes.

The Small Computer System Interface (SCSI) is a parallel input/output bus often used to connect disc drives. CD-ROMs, tape drives and other peripherals to a computer bus. 25 The SCSI bus is a bidirectional, multimaster bus which can accommodate peer to peer communications among multiple CPUs and multiple peripherals. Because of this versatility, the SCSI bus is becoming increasingly important in the microcomputer field.

30 There are several popular microcomputer architectures in use today, and for the most part, these architectures are not compatible with one another. For example, the IBM PC XT and AT computer, and the so-called compatibles, use a computer bus which is now popularly called the industry standard architecture (ISA). Some of the more recent IBM microcomputers of the PS/2 family use a different bus known as microchannel architecture (MCA). The microchannel architecture is generally not plug compatible with the earlier industry standard architecture. This has caused 40 some problems in the computer peripheral industry, since manufacturers who want to support both product lines must design different circuits for both architectures. This adds considerably to the cost of developing and supporting peripheral products. 45

For the engineer wishing to design a SCSI interface into a product to be used across the IBM microcomputer family, there has traditionally been no easy solution. The industry standard architecture and microchannel architecture are sufficiently different that it is not heretofore been possible to 50 design one product for use on both. A great deal of engineering time goes into developing hardware products, and this engineering time is reflected in the product cost. What is needed but has heretofore been unavailable, is a simple, easy to use and cost-effective SCSI controller which may be 55readily configured to work with either the industry standard architecture or the microchannel architecture.

The present invention implements a complete multifunctional SCSI chip for use with either the ISA architecture or the MCA architecture. The principles may also be used to 60 extend the SCSI circuit to additional architectures such as the Extended Industry Standard Architecture (EISA). In its presently preferred embodiment, the only external requirements are for address decoding at the high order memory address bits, a suitable oscillator and an external static 65 RAM. The static RAM is preferably an 8K×8 static RAM used to implement the SCSI controller's main FIFO. Using

presently available technology, the external main FIFO is more economically manufactured as a separate component, as opposed to integral with the remainder of the SCSI chip. However, with improvements in chip fabrication technology and with appropriate economies of scale, the entire SCSI chip including main FIFO could be fabricated as a single chip.

The SCSI controller of the invention supports asynchronous and synchronous protocols conforming to the SCSI specification known as the SCSI-II specification proposed by the American National Standards Institute (ANSI) and further described in the X3.131-198x; X3 Project 503-D prepared by the Technical Committee X3T9 of the I/O interface accredited Standards Committee, X3-Information Processing Systems.

The circuit includes logic circuitry for handling SCSI bus arbitration,-automatic generation of acknowledge handshakes, interrupt on SCSI control/data signal, interrupt on SCSI select signal, interrupt on arbitration complete signal and interrupt on SCSI reset signal. The circuit provides first in first out (FIFO) buffering of data-with interrupt generation based on FIFO fullness levels.

The circuit includes an address generator and timing controls for the 8K×8 external static RAM used to implement the main FIFO which supports high speed synchronous and asynchronous SCSI device operations. The FIFO data path is I/O mapped to the 16 bit data bus of the host computer. This allows high speed data transfers between the computer bus and the main FIFO. SCSI command information, chip status, setup parameters and data paths are I/O mapped.

The presently preferred chip implementation supports a ROM BIOS space of 7936 (decimal), 1F00 (hex) bytes. The onboard chip logic includes an EPROM enable capability as well as data buffering and latching. An internal memory of 256×8 bytes of memory mapped static RAM is provided for use by the ROM BIOS software for variable storage, scratch pad registers and the like.

In one aspect the invention comprises a computer system interface for connection between an input/output SCSI bus and a selected one of at least two different types of host computer bus architectures. The computer system interface of the invention is thus useful in interconnecting a host computer to a peripheral device. The apparatus comprises an internal data bus, a first interface means for coupling the SCSI bus to the internal data bus and a second interface means for coupling the host computer bus to the internal data bus. Control logic gating means are provided for causing data communicated between the SCSI bus and the first interface means to communicate with the internal data bus. The control logic gating means further causes data communicated between the-computer bus and the second interface means to communicate with the internal data bus.

Control signal generation logic means are provided for coupling to the host computer bus. The control signal generation logic means have a first portion adapted for generating control signals of a first type, corresponding to a host computer of a first type. The control signal generation logic means further includes a second portion adapted for generating control signals of a second type, corresponding to a host computer of a second type. User-settable means is provided for selectively enabling one and disabling the other of the first and second portions of the control signal generation logic.

Preferably, the user-settable means defines at least a first state and a second state, each corresponding to different host

computer bus architecture types. The user-settable means may be selectively placed in one or the other of the two states by predefined hardware configuration. In the presently preferred embodiment an external conductive lead or terminal is provided for this purpose. Placing this terminal at a 5 first logic state configures the SCSI controller chip as an ISA compatible device, while placing the terminal at a second logical state configures the chip as an MCA compatible device.

In another aspect the invention comprises a computer 10 system interface for connection between a predefined host computer bus and an input/output SCSI bus, for interconnecting a computer to a peripheral device. The apparatus comprises an internal data bus with a main FIFO buffer coupled to it. A first interface means is provided for coupling  $^{\ \ 15}$ the SCSI bus to the internal data bus and a second interface means is provided for coupling the host computer bus to the internal data bus. Control logic gating means are provided for causing data communicated between the SCSI bus and the first interface means to flow onto the internal data bus 20 and to further flow from the internal data bus into the main FIFO buffer. Monitoring means are provided for monitoring the quantity of data in the main FIFO buffer and for generating information for placement on the host computer bus as an indication of fullness of the main FIFO buffer. 25

The monitoring means preferably generates count data which indicates the quantity of data stored in the main FIFO buffer and may also include means for generating an interrupt signal for placement on the host computer bus in the event the quantity of data stored in the main FIFO buffer <sup>30</sup> reaches a predefined level. In this way, software operating on the host computer can access the count data to determine the correct data block size to send or receive. The interrupt signal can serve as an-automatic sentinel to alert the host computer when certain predefined fullness (or emptiness) <sup>35</sup> main FIFO conditions exist.

In the presently preferred embodiment, the first interface comprises an input/output FIFO buffer which may include its own means for monitoring fullness. Depending on the user-selected mode of operation, data communication between host computer bus and SCSI bus may invoke both the main FIFO buffer and the input/output FIFO buffer, the main FIFO buffer only, or neither buffer.

The SCSI controller of the invention is thus very flexible 45 and well adapted for use in a wide variety of SCSI applications. The user-settable computer architecture selection mechanism greatly simplifies SCSI interface circuit design, since the engineer may now design both ISA and MCA peripherals using the same multifunction SCSI chip. Hard-50 ware design is facilitated because the engineer is able to apply familiarity gained in developing an ISA SCSI interface to an MCA SCSI interface, and vice-versa. Software design is also facilitated since the multifunction SCSI chip provides a relatively transparent hardware/software interface. The software engineers' task is thus greatly facilitated, since the operating system software can be written with minimal concern about which computer architecture is in place.

For a more complete understanding of the invention and 60 its many objects and advantages, reference may be had to the following detailed specification and to the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

65

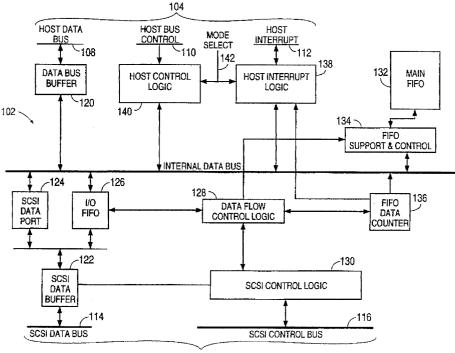

FIG. 1 is a block diagram of the invention giving a general system overview;

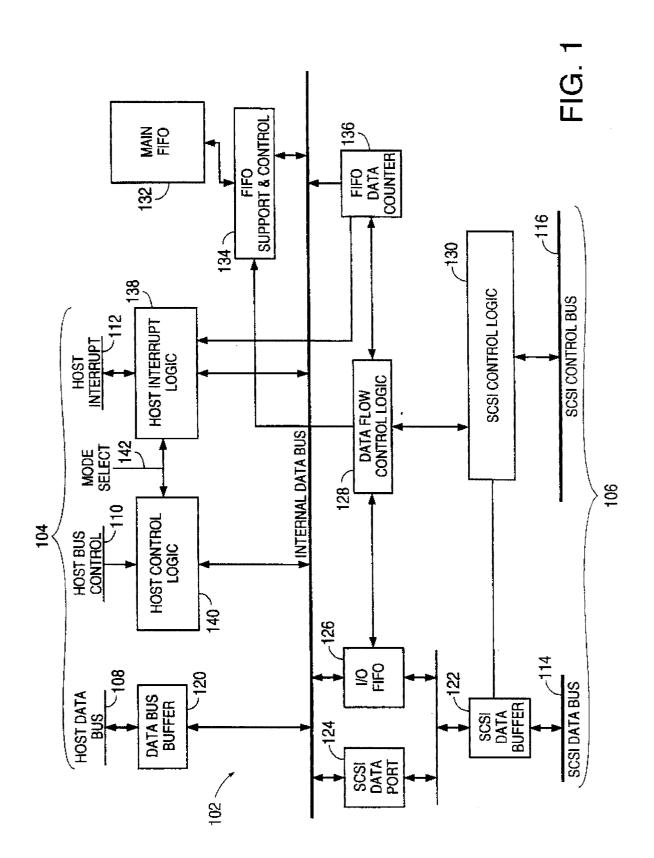

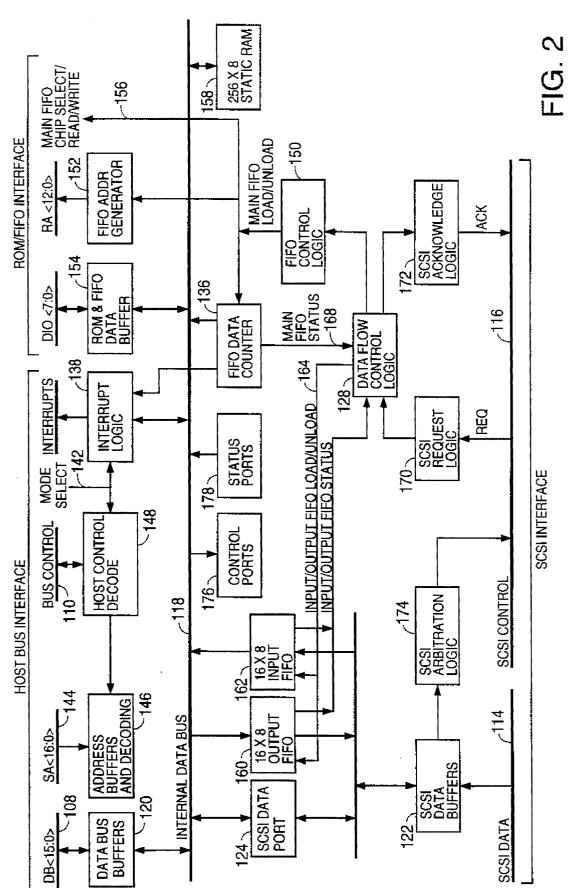

FIG. 2 is a more detailed block diagram of the invention; FIG. 3 depicts a single chip embodiment, showing pin designations;

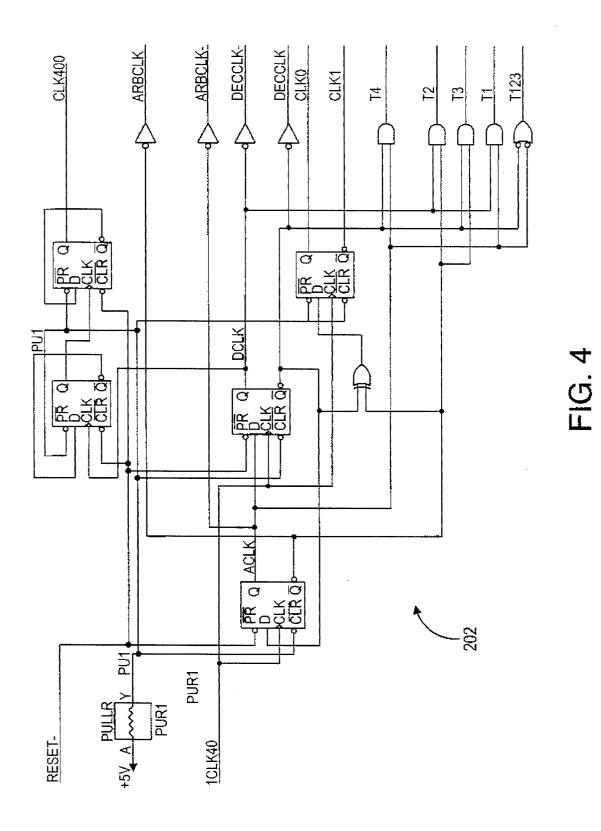

FIG. 4 is a schematic diagram of the 40 MHz clock divider circuit;

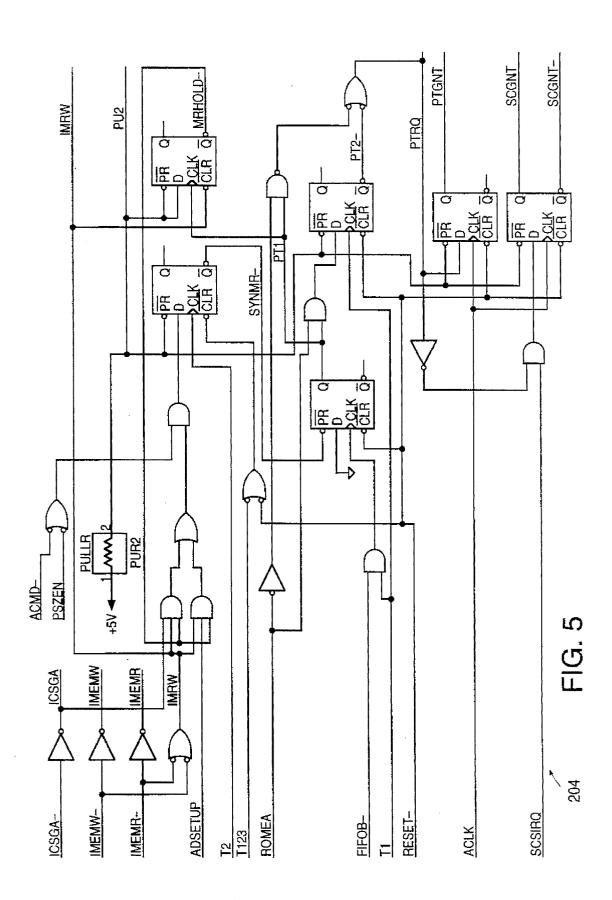

FIG. **5** is a schematic diagram of the internal arbitration logic;

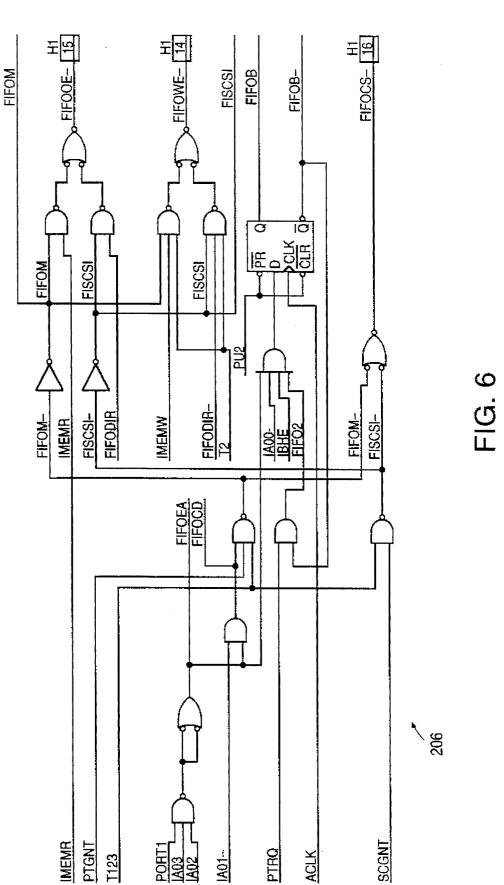

FIG. 6 is a schematic diagram of the basic address decoding logic;

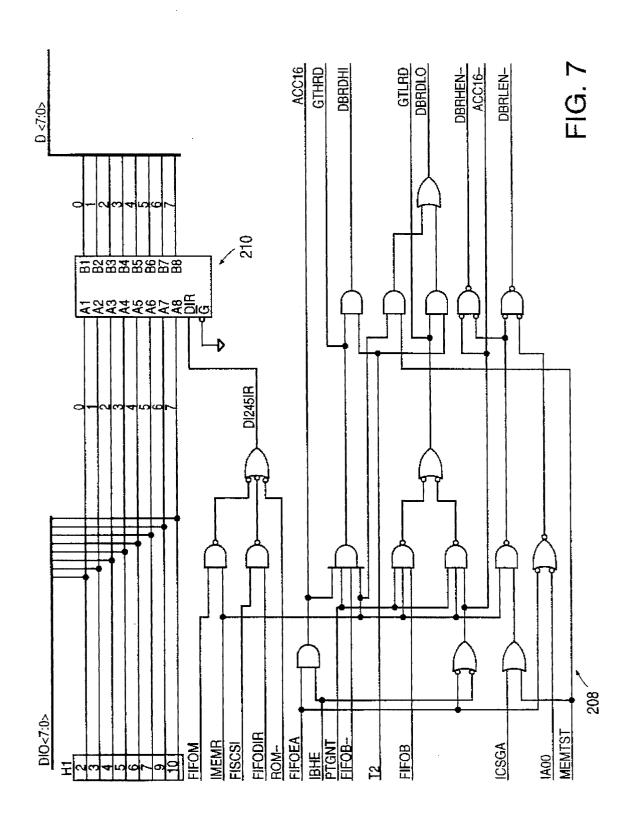

FIG. 7 is a schematic diagram of the DIO buffer/read data gating;

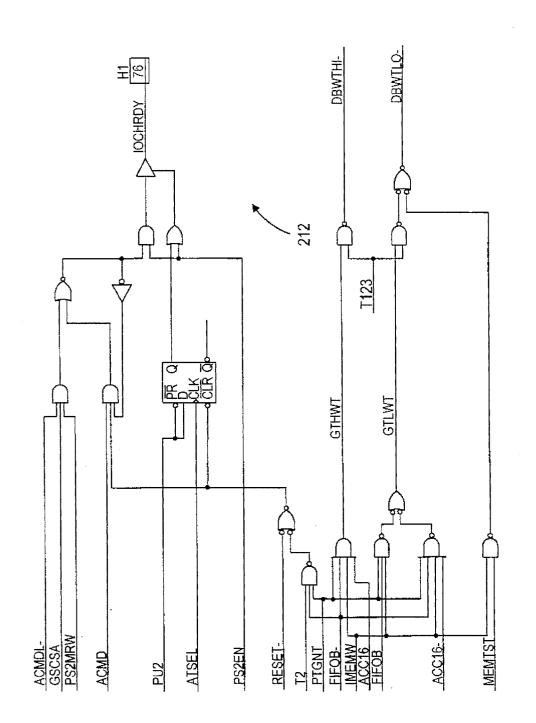

FIG. 8 is a schematic diagram of the CHRDY logic/write data gating;

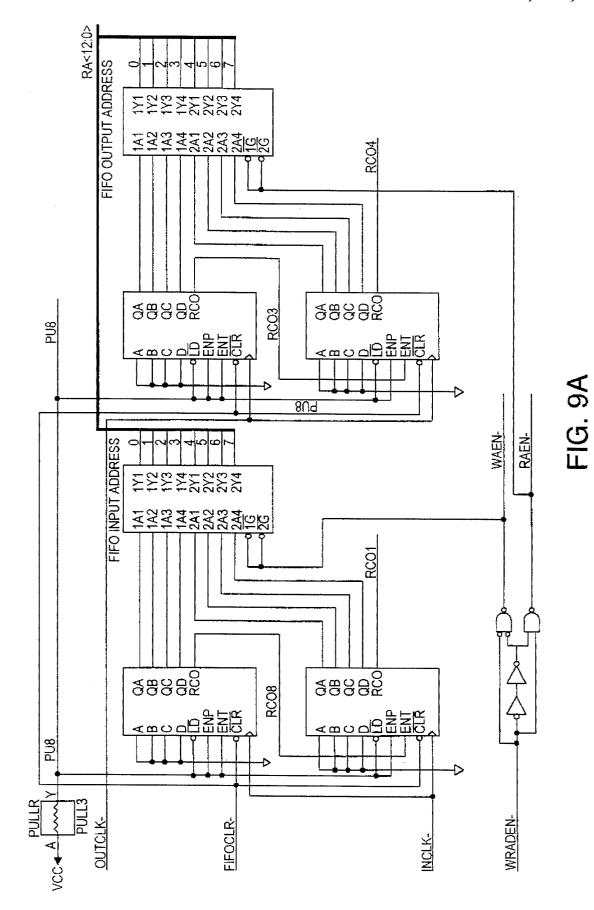

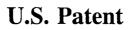

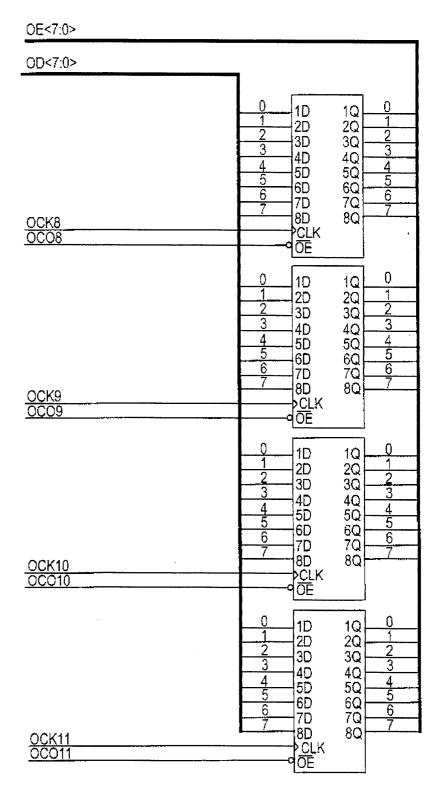

FIG. 9A is a schematic diagram of the FIFO-address generation A;

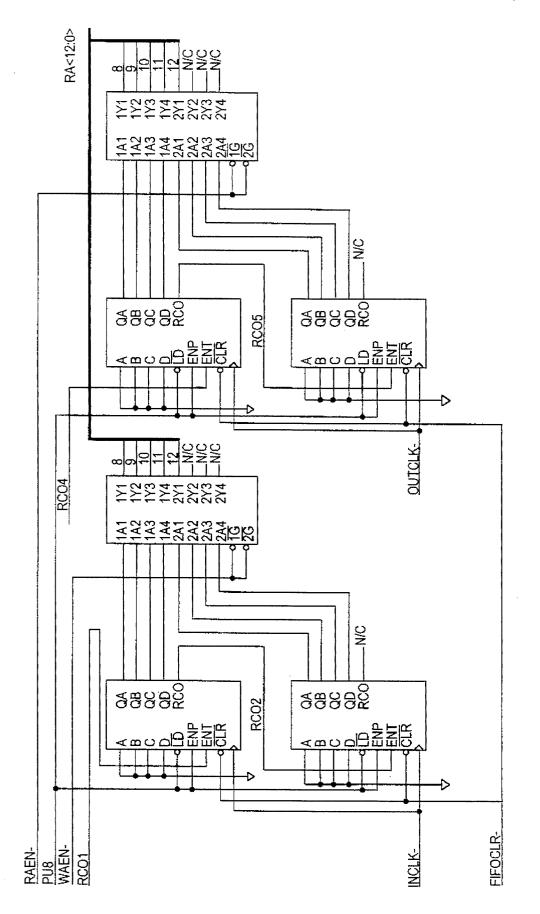

FIG. **9B** is a schematic diagram of the FIFO address generation B;

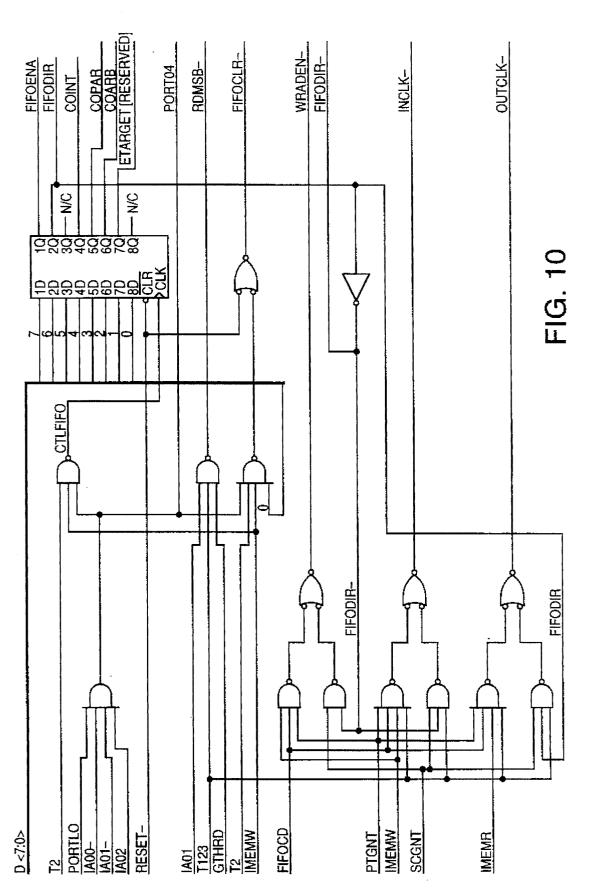

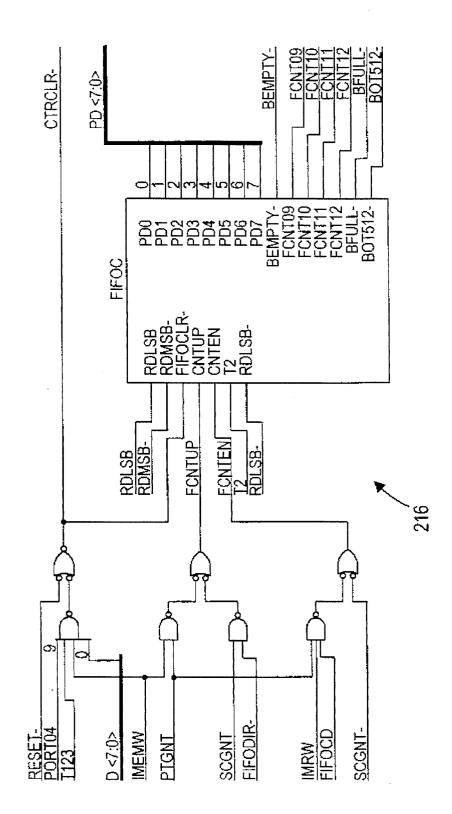

FIG. **10** is a schematic diagram of the FIFO control register and FIFO clocks;

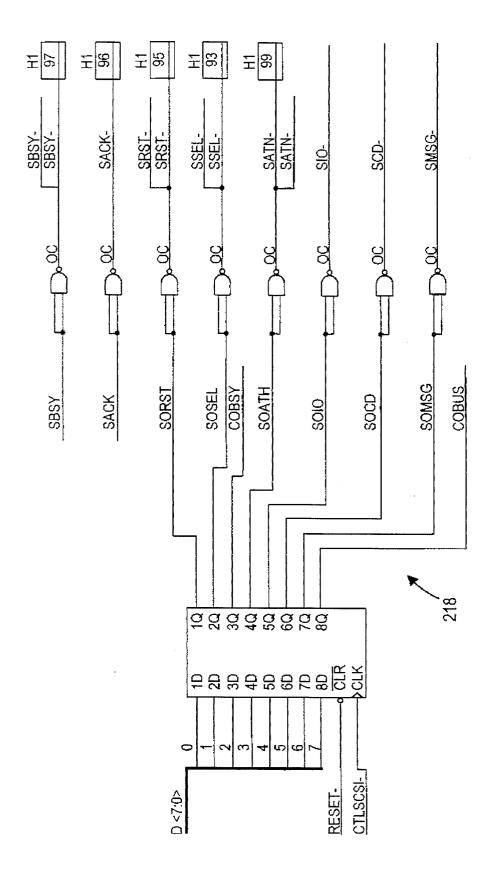

FIG. 11 is a schematic diagram of the FIFO data counter; FIG. 12 is a schematic diagram of the SCSI control outputs;

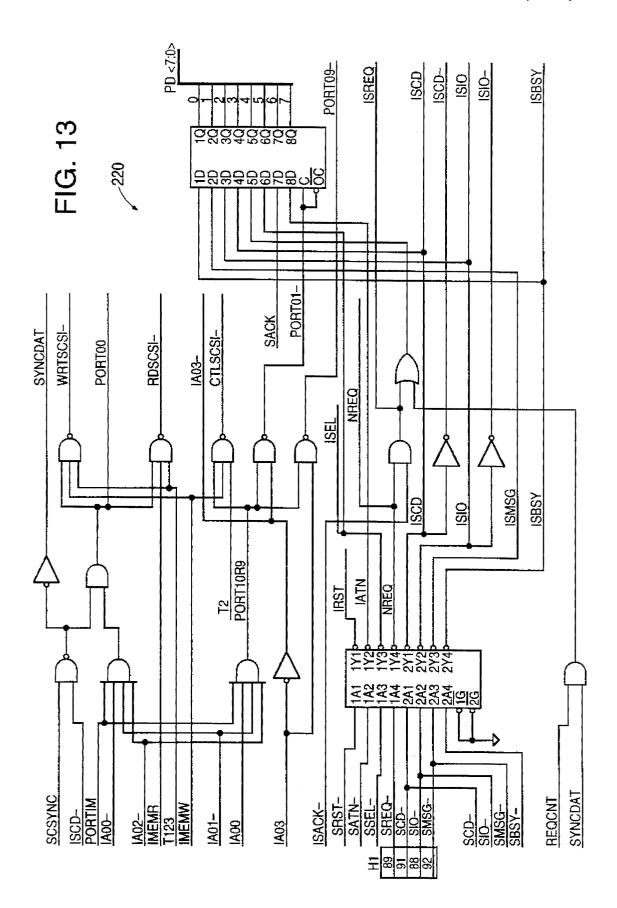

FIG. 13 is a schematic diagram of the SCSI control register and port address decode;

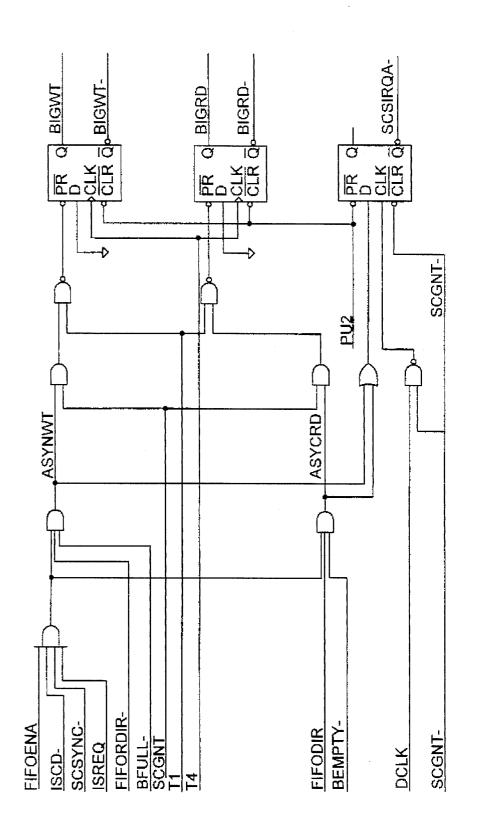

FIG. 14 is a schematic diagram of the asynchronous SCSI flow control;

FIG. 15 is a schematic diagram of the ID register (high byte) and extension buffer;

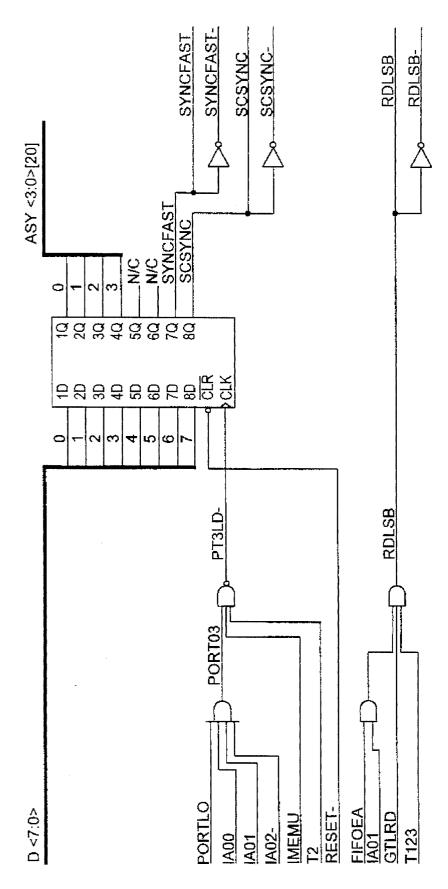

FIG. **16** is a schematic diagram of the synchronous SCSI data path and parity checker;

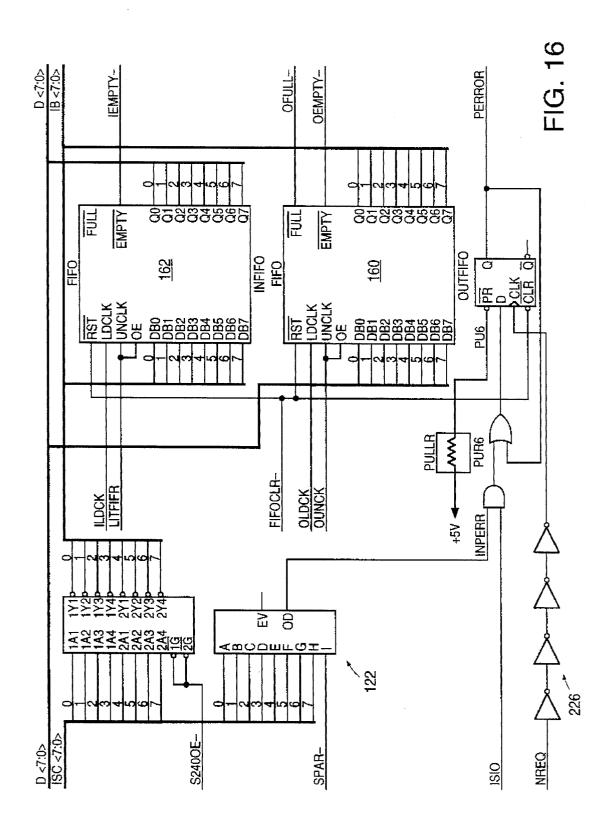

FIG. 17 is a schematic diagram of the asynchronous SCSI data path, arbitration, and parity generator;

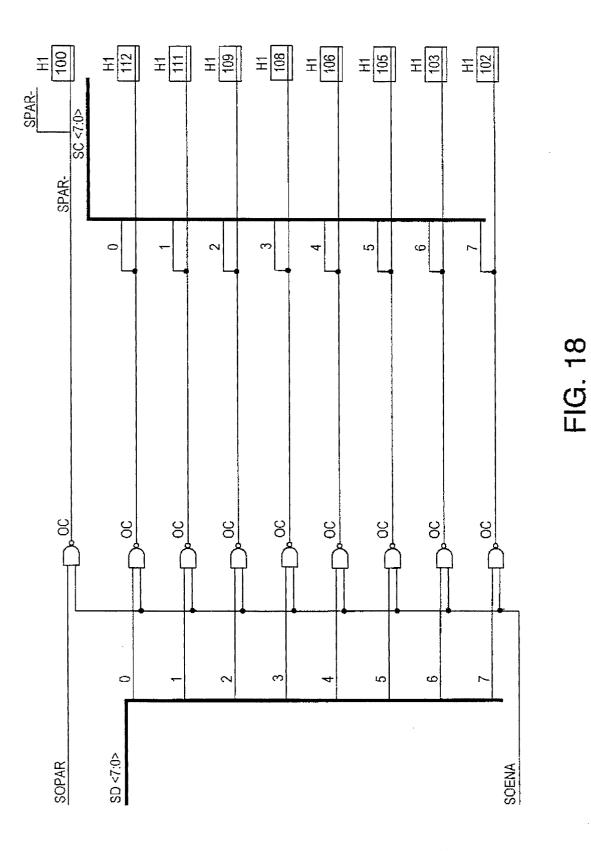

FIG. 18 is a schematic diagram of the SCSI data output drivers;

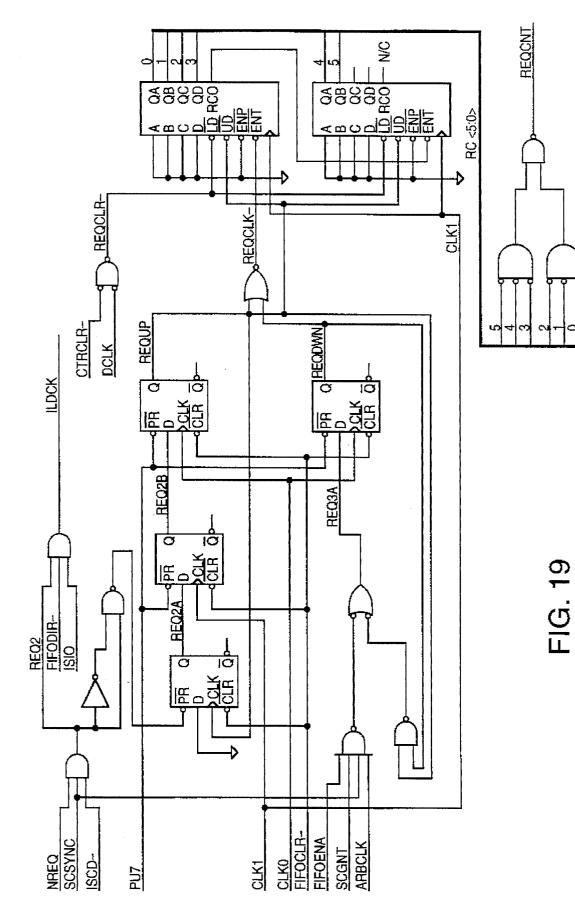

FIG. **19** is a schematic diagram of the synchronous request counter;

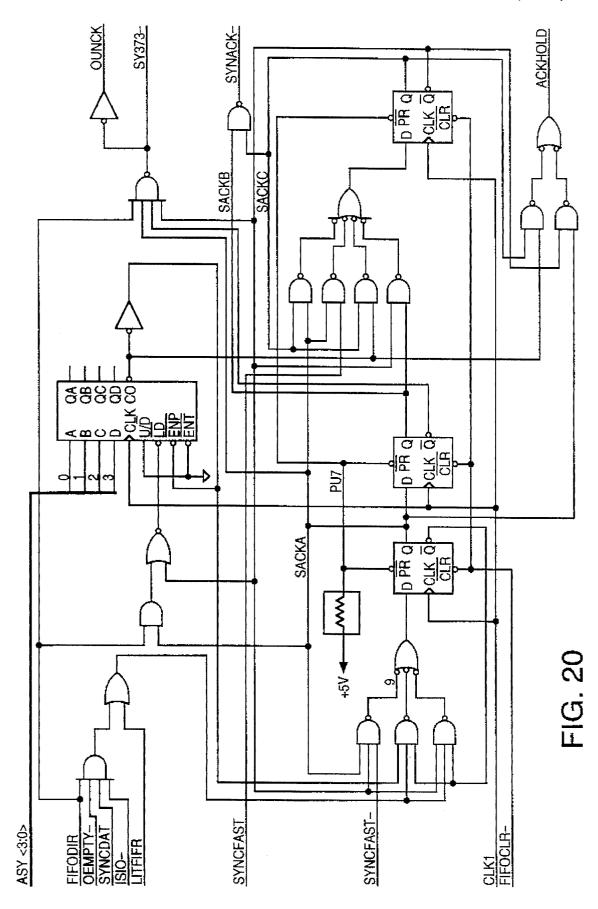

FIG. **20** is a schematic diagram of the synchronous SCSI acknowledge;

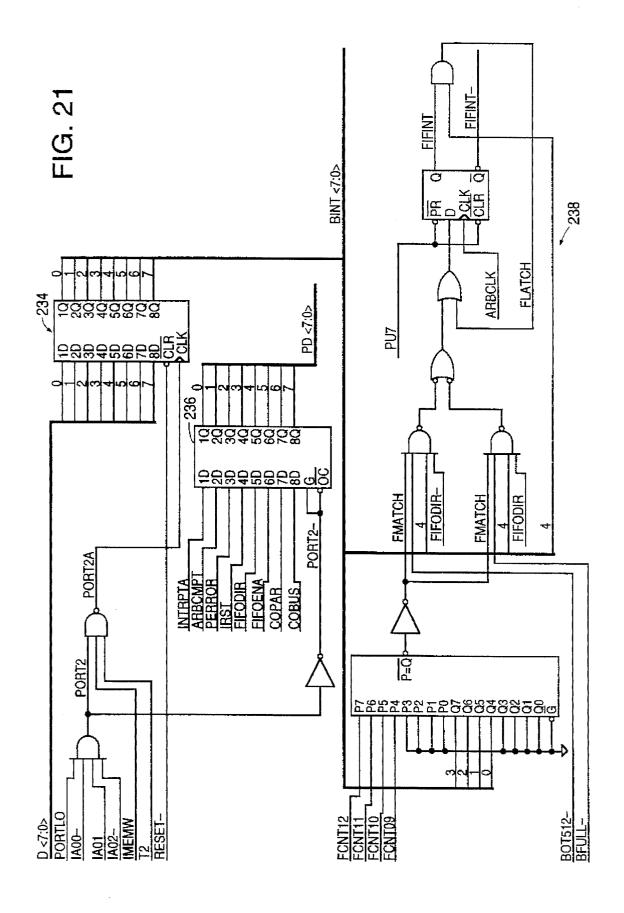

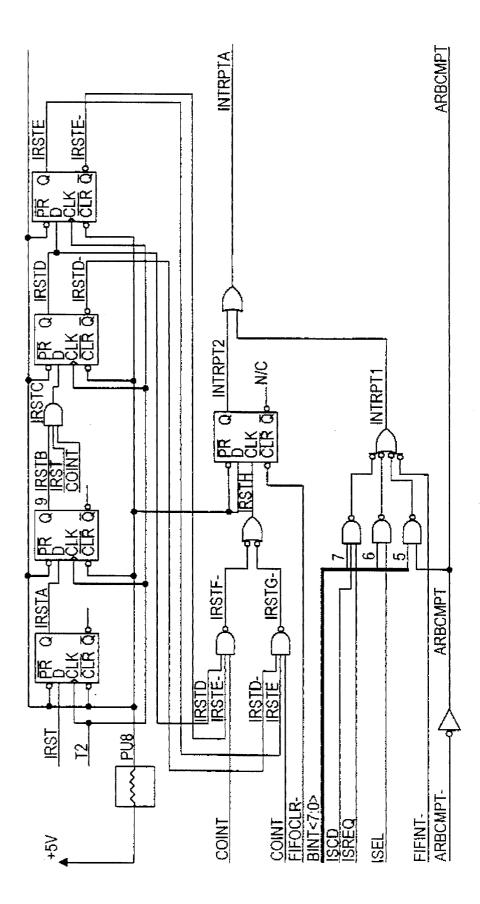

FIG. **21** is a schematic diagram of the FIFO interrupt and interrupt control register;

FIG. 22 is a schematic diagram of the interrupts;

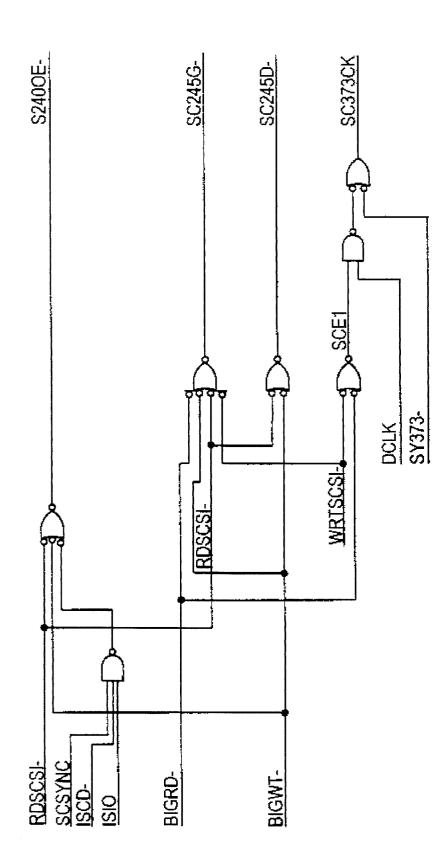

FIG. 23 is a schematic diagram of the SCSI data gating;

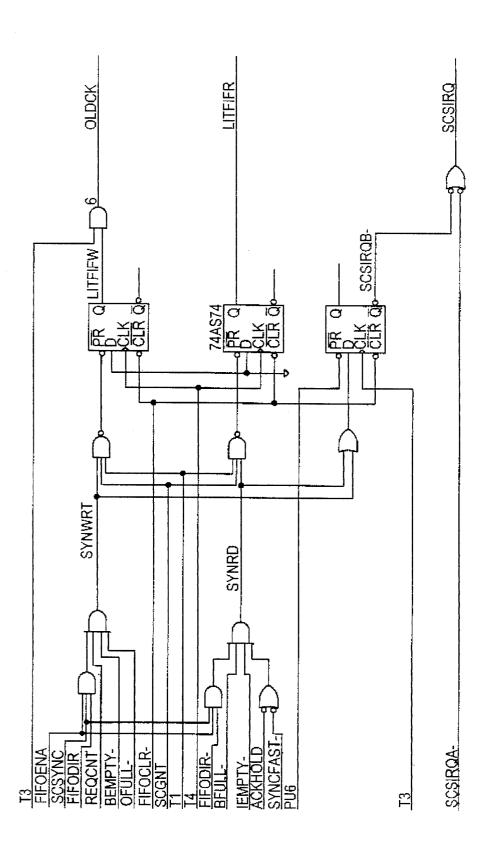

FIG. 24 is a schematic diagram of the synchronous SCSI flow control;

FIG. 25 is a schematic diagram of the SCSI acknowledge;

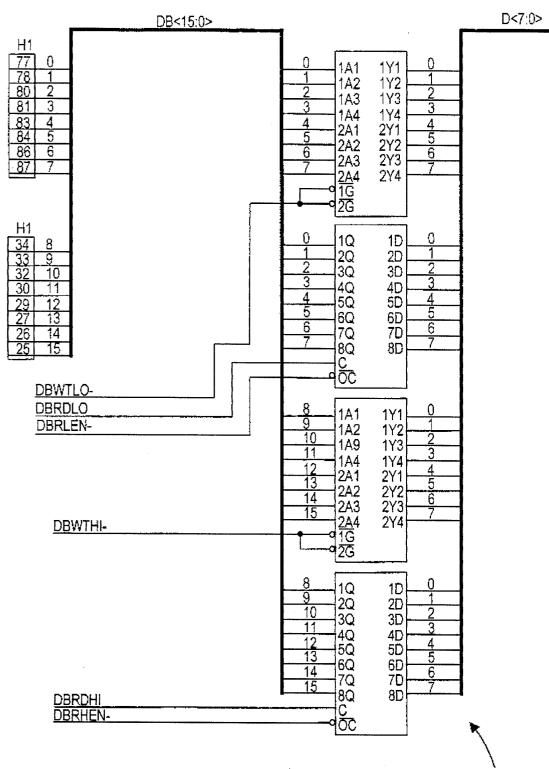

FIG. 26 is a schematic diagram of the data bus buffers;

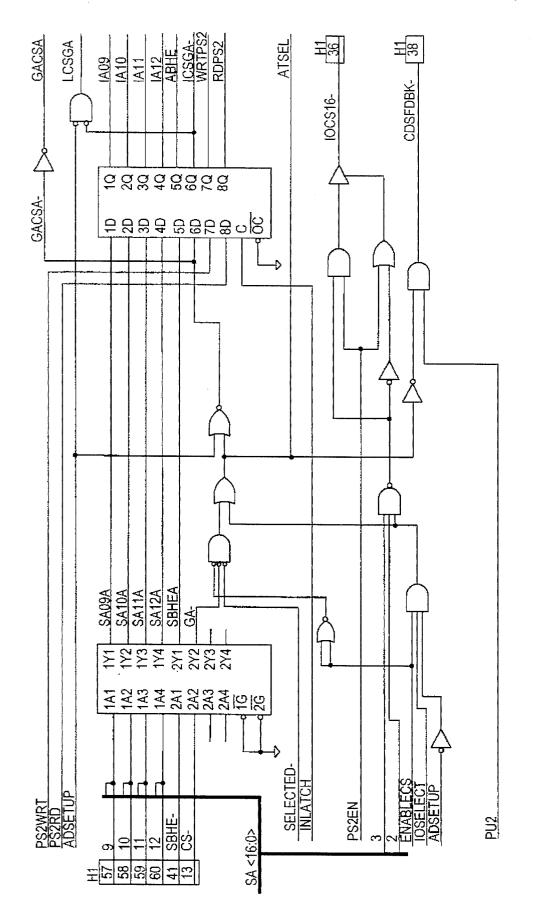

FIG. 27 is a schematic diagram of the address and control interface;

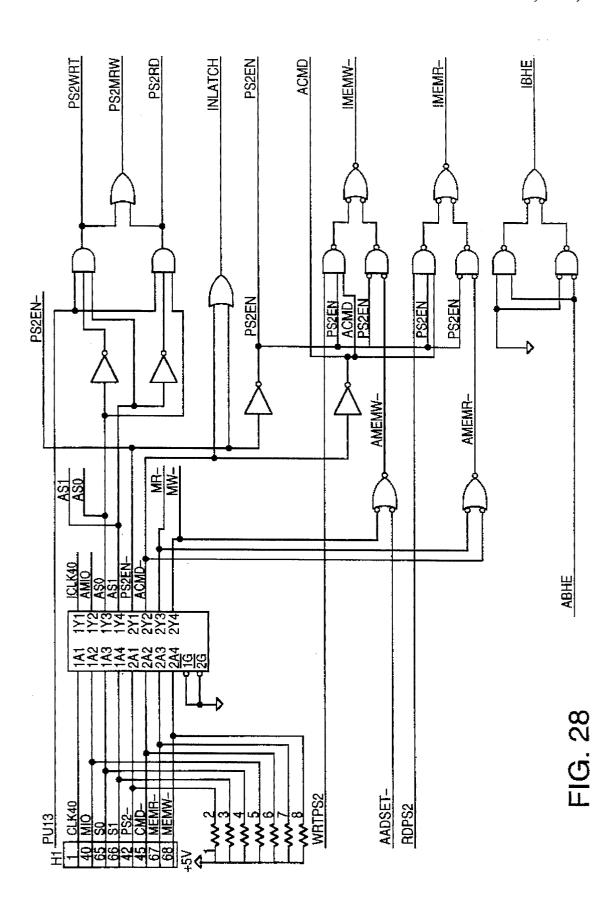

FIG. 28 is a schematic diagram of the PS2/AT decode;

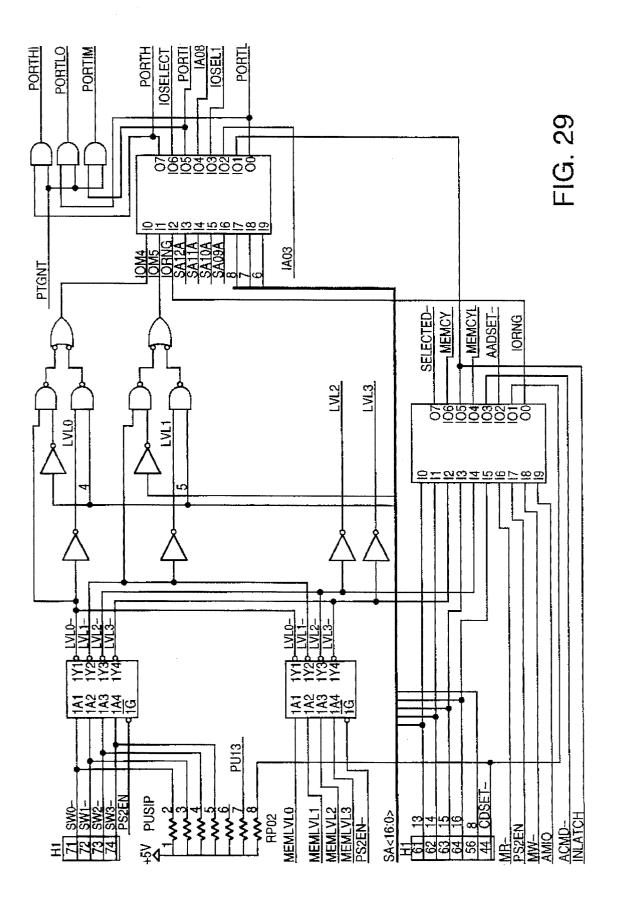

FIG. 29 is a schematic diagram of the chip select decod- $_{55}$  ing;

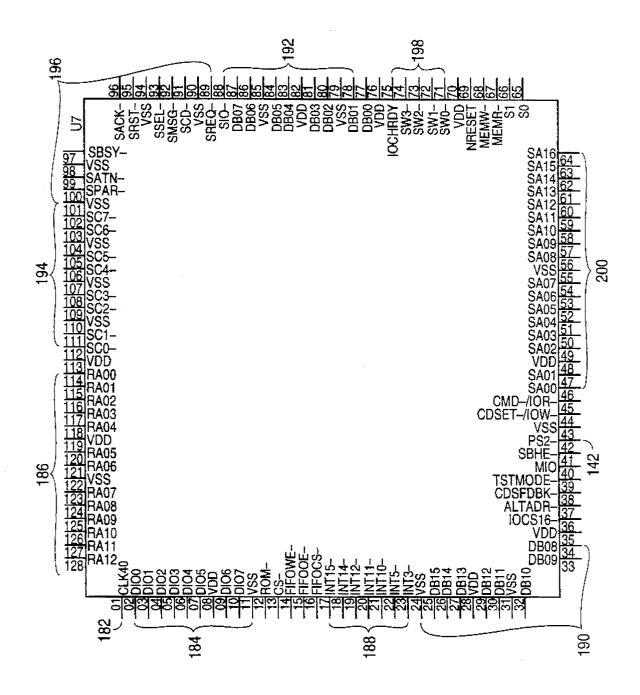

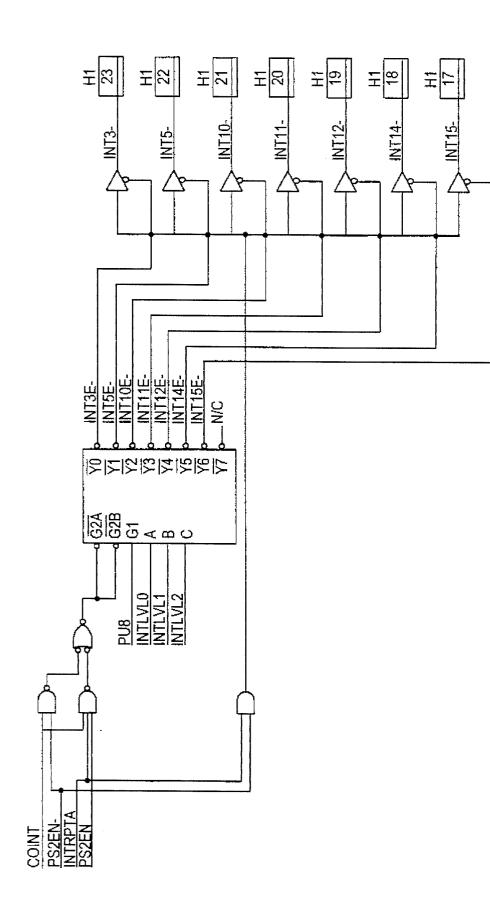

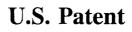

FIG. 30 is a schematic diagram of the interrupt selection; FIG. 31 is a schematic diagram of the Port 9 interrupt

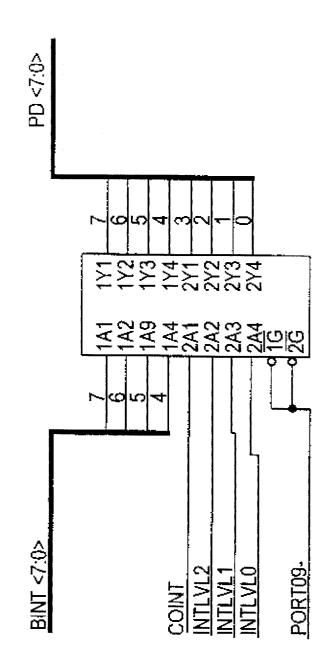

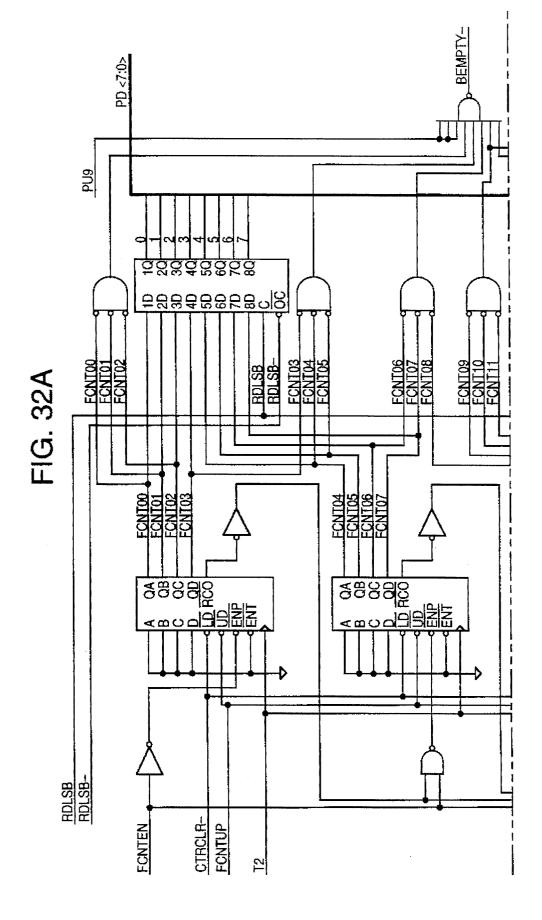

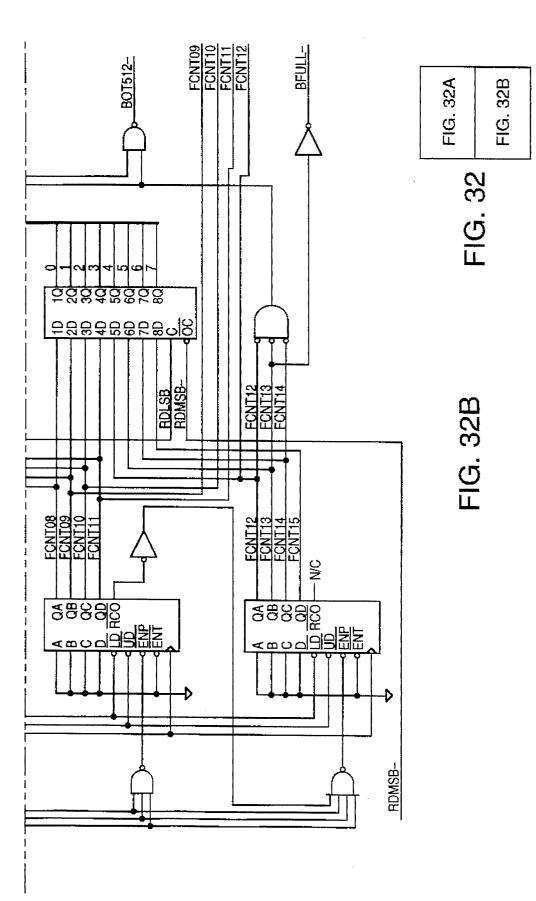

mask register; FIG. 32 is a key to FIGS. 32A and 32B, which are a schematic diagram of the FIFO data counter;

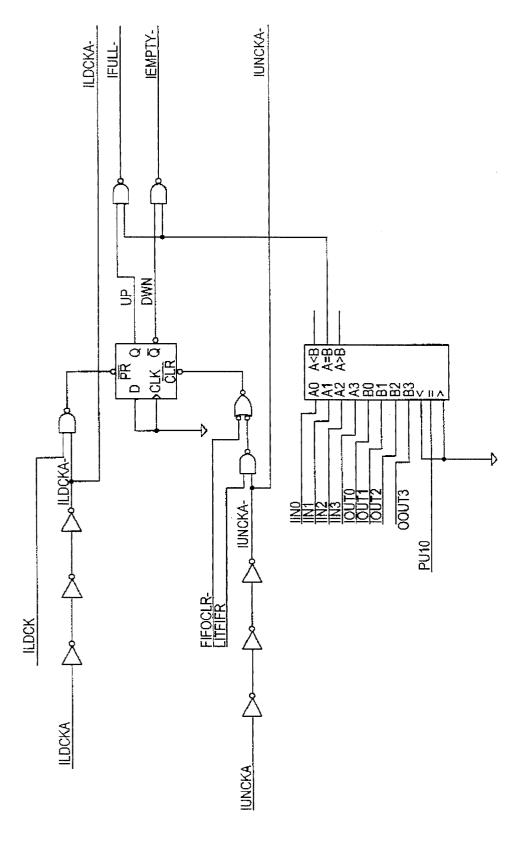

FIG. **33** is a schematic diagram of the input FIFO status flags;

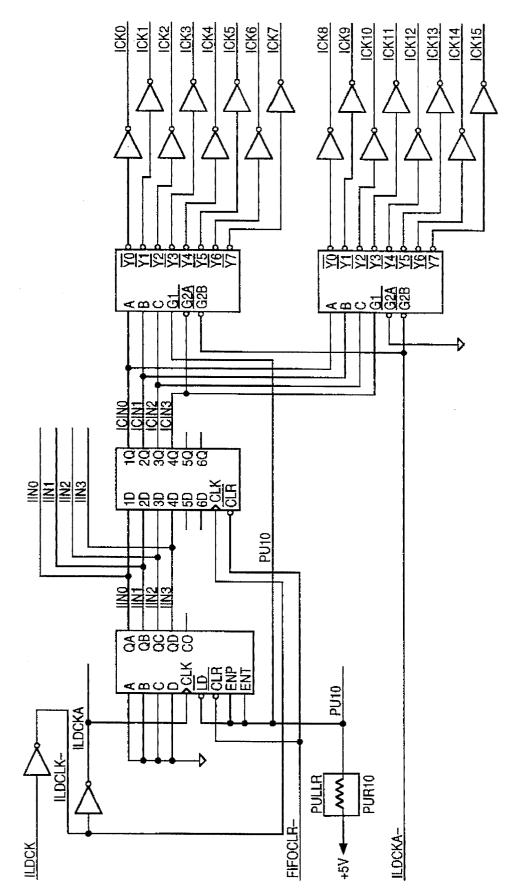

FIG. **34** is a key to FIGS. **34A** and **34B**, which are a schematic diagram of the input FIFO load sequencer;

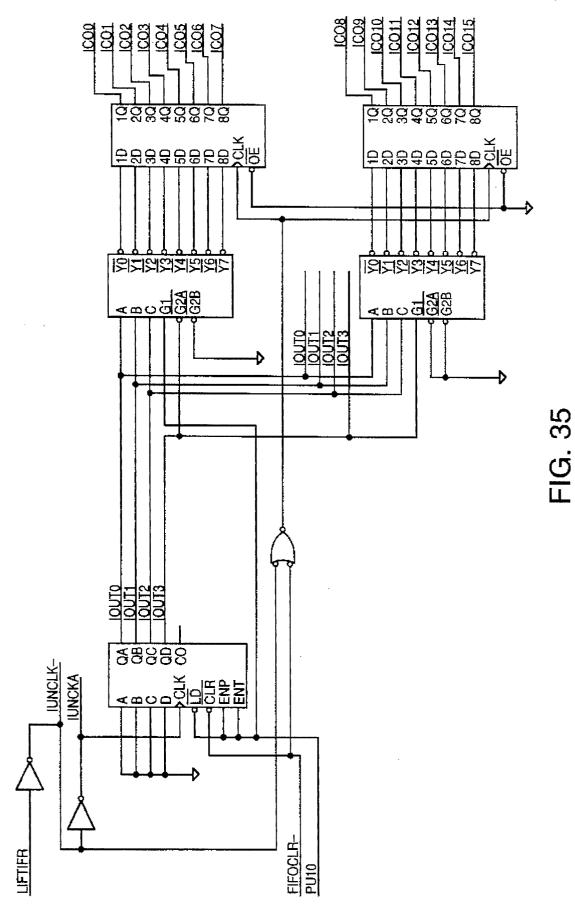

FIG. **35** is a schematic diagram of the input FIFO unload sequencer;

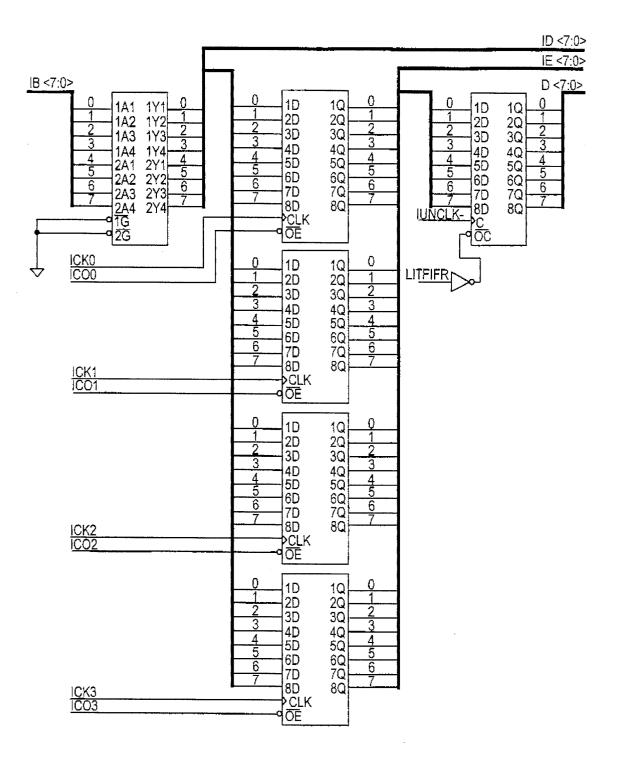

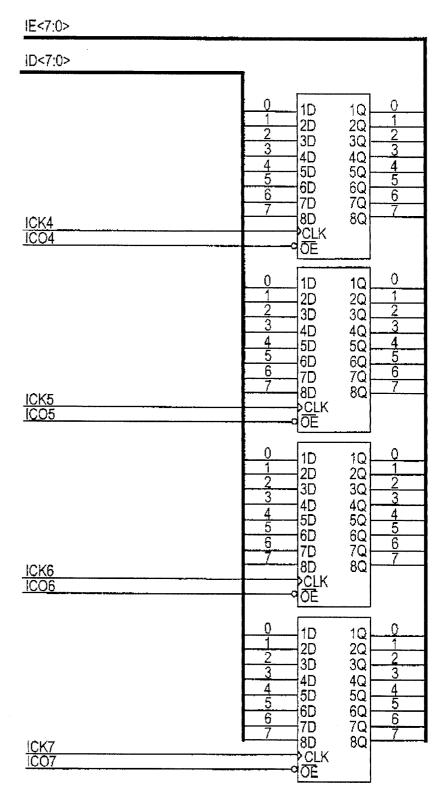

FIG. **36** is a schematic diagram of the input FIFO registers **0–3**;

FIG. **37** is a schematic diagram of the input FIFO registers **4–7**;

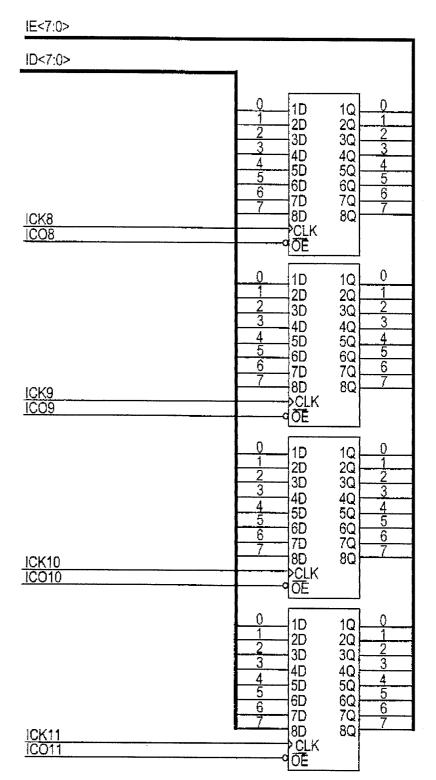

FIG. **38** is a schematic diagram of the input FIFO registers **8–11**;

FIG. **39** is a schematic diagram of the input FIFO registers **12–15**;

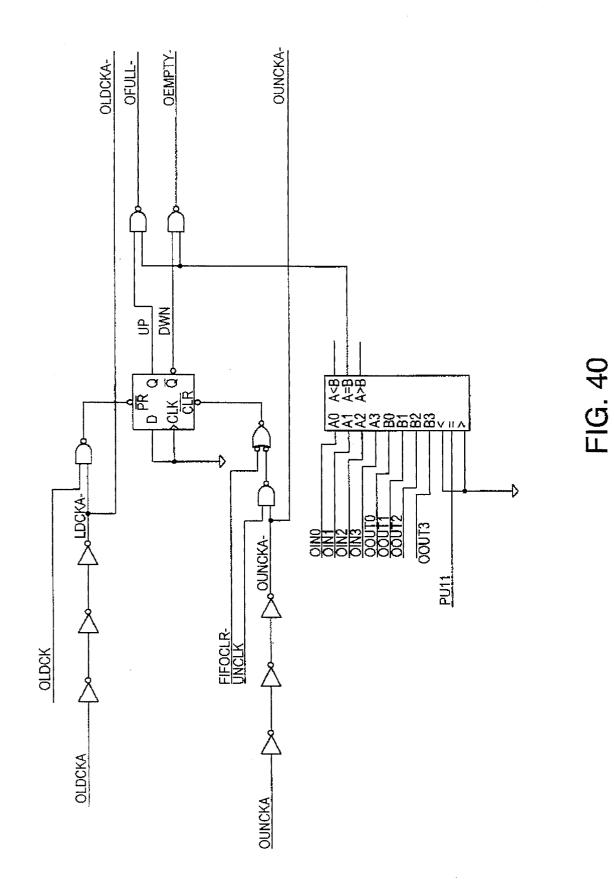

FIG. 40 is a schematic diagram of the output FIFO status  $_{10}$  flags;

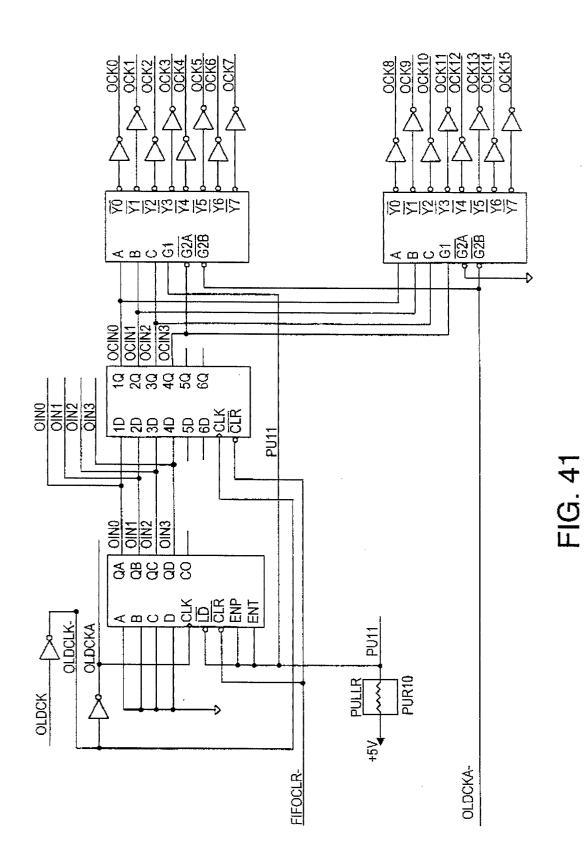

FIG. 41 is a schematic diagram of the output FIFO load sequencer;

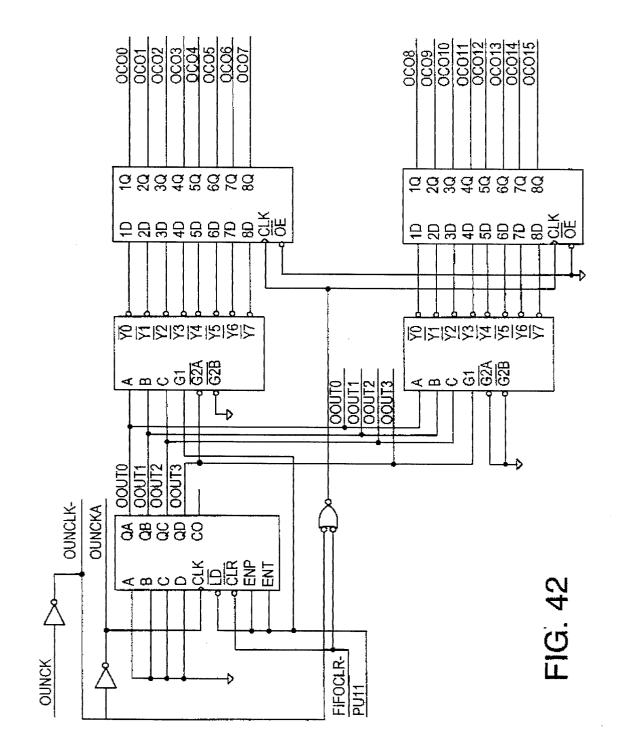

FIG. **42** is a schematic diagram of the output FIFO unload sequencer; 15

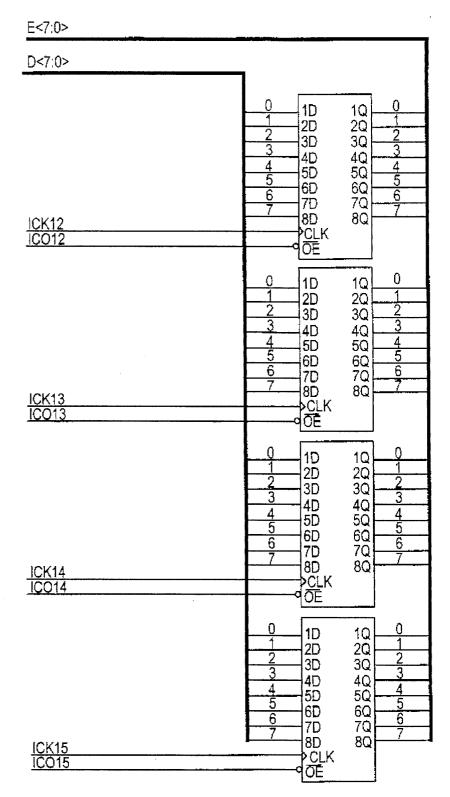

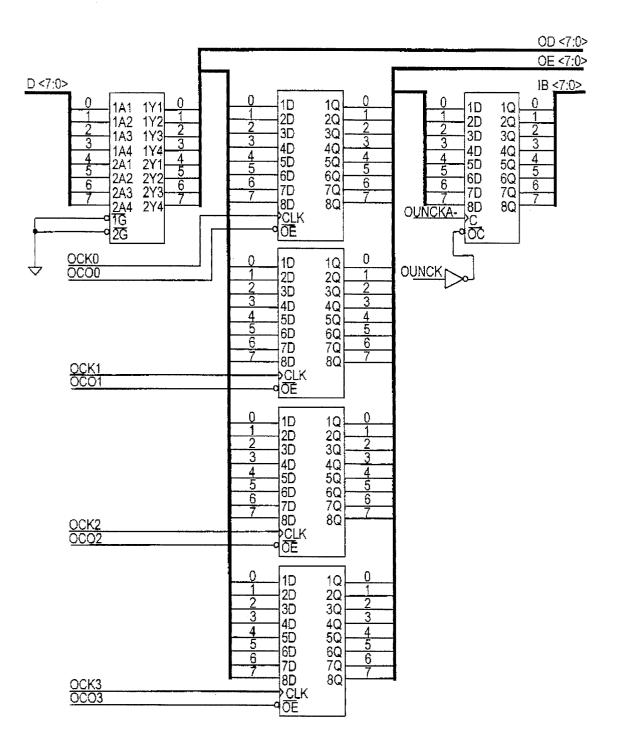

FIG. 43 is a schematic diagram of the output FIFO registers 0-3;

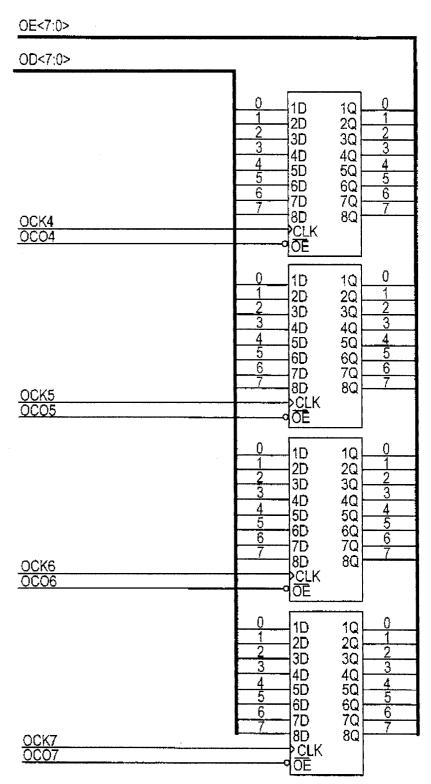

FIG. 44 is a schematic diagram of the output FIFO registers 4–7;

FIG. 45 is a schematic diagram of the output FIFO registers 8-11; and

FIG. 46 is a schematic diagram of the output FIFO registers 12–15.

### DESCRIPTION OF THE PREFERRED EMBODIMENT

General System Overview

Referring to FIG. 1, the SCSI controller is depicted by a 30 functional block diagram which will be useful in understanding the more detailed schematic diagrams which follow. The SCSI controller circuit, shown generally at **102** is adapted for interconnection between the host computer bus, shown generally at **104**, and the SCSI bus, shown generally 35 at **106**. For convenience, the host computer bus has been broken into the following components: host data bus **108**, host bus control **110** and host interrupt **112**. Similarly, the SCSI bus is illustrating comprising: SCSI data bus **114** and SCSI control bus **116**. The SCSI controller circuit **102** 40 includes an internal data bus **118**.

The host data bus 108 is connected to the internal data bus 118 through a data bus buffer 120. The SCSI data bus 114 is likewise provided with a SCSI data buffer 122. The SCSI data bus buffer is coupled to the internal data bus 118 45 through two alternate paths, a SCSI data port 124 and an input/output first in first out buffer or I/O FIFO 126. The I/O FIFO is controlled by data flow control logic 128. The data flow control logic is in turn controlled by SCSI control logic 130, which is responsive to signals on the SCSI control bus 50 116. In the presently preferred embodiment I/O FIFO 126 is a 16 byte FIFO for handling the offset or latency which can occur during synchronous data transfers. In the synchronous mode, there is a negotiation which takes place prior to data transmission during which time the rate of transfer and offset 55 are established. The offset of 16 allows up to 16 data requests to be queued up without the need to acknowledge. The size of I/O FIFO 126 must be sufficient to accommodate the maximum permissible offset. Although a 16 byte I/O FIFO is employed in the present embodiment, different 60 FIFO sizes are also possible and contemplated by the invention.

The SCSI controller circuit also includes a main FIFO **132**, which is coupled to the internal data bus through FIFO support and control circuitry **134**. In the presently preferred 65 embodiment the main FIFO is an 8K×8 bit FIFO which may be implemented using static random access memory. As will

be further illustrated, the bulk of the SCSI controller circuit of the invention may be fabricated as a single microchip. In its presently preferred form, the main FIFO **13**Z is packaged separately from the remainder of the microchip circuitry to reduce cost. 8K×8 bit random access memory chips are readily available and presently more economical than fabricating a single SCSI controller circuit with sufficient onboard RAM to accommodate the main FIFO. Of course, improvements in chip fabrication technology or economies of scale could make it desirable to include the main FIFO with the remaining circuitry in a single chip package. Further, while an 8K×8 bit main FIFO is presently employed, different storage sizes and data widths (e.g., 16 bit or larger) may be employed to meet future circuit requirements.

The circuit includes a FIFO data counter **136** which is coupled to the data flow control logic **128** and also to the internal data bus **118**. The FIFO data counter monitors the fullness of main FIFO **132** and provides a numeric value indicative of fullness which the host computer can access to determine the appropriate block size for data transfers. The FIFO data counter is coupled to interrupt logic **138** and is thereby able to send an interrupt to the host computer on its host interrupt bus.

The interrupt logic is capable of supporting both MCA and ISA interrupt protocols. This capability is depicted diagrammatically by reference numerals 138a and 138b. The circuit also includes control logic 140, coupled to the internal data bus and also to the host bus control lines 110. The control logic is also configured with a portion 140a for interfacing with MCA architecture and a second portion 140b for interfacing with ISA architecture.

A mode select pin on the single chip embodiment provides a user-settable means for configuring the chip as either an MCA or an ISA device. The mode select pin, designated **142** in FIG. **1**, is coupled to both interrupt logic **138** and control logic **140**.

The multifunction SCSI chip of the presently preferred embodiment communicates with SCSI targets using the small computer system interface (SCSI) protocol, implementing arbitration, disconnect/reselection and asynchronous, synchronous and fast synchronous data protocols. The following memory and I/O functions may be performed by the chip:

Read ROM

Read/Write Internal System Ram Input/Output Main FIFO Input/Output SCSI Data Port (8 Bit) Output SCSI Control Information (8 Bit) Output Interrupt Information (8 Bit) Output SCSI Synchronous Control (8 Bit) Output Adaptor Control (8 Bit) Input/Output Loopback Register (8 Bit) Input/Output Loopback Register (8 Bit) Input SCSI Bus Status (8 Bit) Input SCSI Bus Status (8 Bit) Input Main FIFO Count (16 Bit) Input Adaptor ID, LSB (8 Bit) Input Adaptor ID, MSB (8 Bit) Input Interrupt Mask (8 Bit) Input Option Select (8 Bit).

To provide a great deal of flexibility, the presently preferred single chip embodiment may be user-configured to reside at different I/O and memory base addresses. Four pins designated SW0–SW3 on FIG. 3 are provided to select the I/O and memory base addresses. In a microchannel imple-

mentation these four pins correspond to the microchannel POS bits 4-7. The I/O base address is given by Table I below and the memory base address is given by Table II below. A 1 in the Tables below corresponds to a grounded SW0-SW3 pin and a 0 corresponds to an open or pulled-up pin. Address 5 bits 17 and higher are decoded by logic external to the multifunction SCSI chip.

TABLE I

| SW1/POS5 | SW0/POS4 | Starting Address | 10 |

|----------|----------|------------------|----|

| 0        | 0        | 0140             |    |

| 0        | 1        | 0150             |    |

| 1        | 0        | 0160             |    |

| 1        | 1        | 0170             | 15 |

TABLE II

| SW3/POS7 | SW2/POS6 | Memory Base Address (Hex) |

|----------|----------|---------------------------|

| 0        | 0        | 0C8000                    |

| 0        | 1        | 0CA000                    |

| 1        | 0        | 0CE000                    |

| 1        | 1        | 0DE000                    |

The 7936 bytes (1F00 h) bytes of ROM BIOS or EPROM are mapped to the host computer bus starting at the base memory address selected in accordance with the above settings. This memory space may be read through the 8 bit computer bus connector and will support memory mapped 30 EPROM operations. The SCSI chip further includes 256×8 of static RAM which is shown and will be further identified in the discussion of FIG. 2 to follow. This RAM is used for system variable storage and scratch pad operations. It is mapped at offset 1F00 h from the memory base address. 35 Aside from ROM BIOS read operations and the 256×8 RAM read/write operations (which are memory mapped) the remaining functions of the present embodiment are I/O mapped.

Main FIFO 132, the 8K×8 external static RAM used for  $_{40}$ buffering data to and from the SCSI data port, is read from or written to using either an 8 bit or a 16 bit I/O operation. The main FIFO is located at offset 0Ch from the I/O base address. Thus the host computer can access the main FIFO buffer by performing an I/O operation to the I/O port located 45 0Ch from the selected I/O base address.

The invention provides a plurality of 8 bit status and control registers which include various control signals, status signals and the SCSI data ports. Like the main FIFO, these registers are mapped at offsets from the I/O base 50 address. Some of the registers provide both read and write functions, other registers only read functions and still other registers only write functions. For convenience, Table III below lists each status and control register, giving the assigned offset from the I/O base address. The main FIFO 55 port at offset 0Ch is also given in the Table. Beneath the Table there follows a brief description of each function which is invoked when the given I/O offset is addressed by the host computer during the appropriate read and/or write cycle. 60

TABLE III

| Off-<br>set | Read                    | Off-<br>set | Write     |        |

|-------------|-------------------------|-------------|-----------|--------|

| E<br>C      | FIFO Count<br>Main FIFO | E<br>C      | Main FIFO | <br>65 |

TABLE III-continued

| Off-<br>set | Read                                    | Off-<br>set | Write                                   |

|-------------|-----------------------------------------|-------------|-----------------------------------------|

| A           | POS Option Select                       | Α           |                                         |

| 9           | Interrupt Mask                          | 9           |                                         |

| 8           | SCSI Data Port                          | 8           | SCSI Data Port                          |

|             | (No ACK Generation)                     |             | (No ACK Generation)                     |

| 7           | Echo Register                           | 7           | Echo Register                           |

| 6           | ID Code (MSB)                           | 6           | U                                       |

| 5           | ID Code (LSB)                           | 5           |                                         |

| 4           |                                         | 4           | FIFO Control                            |

| 3           |                                         | 3           | SCSI Synchronous<br>Control             |

| 2           | Adapter Status                          | 2           | Interrupt Control                       |

| 1           | SCSI Bus Status                         | 1           | SCSI Control                            |

| 0           | SCSI Data Port<br>(With ACK Generation) | 0           | SCSI Data Port<br>(With ACK Generation) |

Offset 0, Read/Write. SCSI data port

This is a direct read of or write to the 8 bit SCSI data port. If the SCSI Request is asserted, an automatic SCSI Acknowledge is generated. Only asynchronous transfers are supported with this port.

Offset 1 Read. SCSI bus status

This is a direct read of the current levels of the SCSI control signals. Signals are read as 1 for asserted or 0 for 25 negated.

Bit 0-SCSI Busy

Bit 1—SCSI Message

- Bit 2-SCSI Input/Output

- Bit 3-SCSI Command/Data

- Bit 4-SCSI Request and Not Acknowledge

- Bit 5-SCSI Select

- Bit 6—SCSI Acknowledge

- Bit 7—SCSI Attention Offset 1, Write. SCSI control actions

Bits 0-6 drive the SCSI control signals. Writing a 1 to the bit asserts the signal, while a 0 releases it

- Bit 0-SCSI Bus Reset

- Bit 1—SCSI Select

- Bit 2-SCSI Busy

- Bit 3-SCSI Attention

- Bit 4—SCSI Input/Output

- Bit 5—SCSI Command/Data

- Bit 6-SCSI Message

- Bit 7—Enable SCSI Bus

Bit 7 must be set whenever the adapter is used to drive the

SCSI bus (except arbitration phase)

Offset 2, Read. Adapter Status.

Bit 0 indicates whether any enabled interrupt source is active, regardless of whether the Enable Interrupt bit in write register 4 is set. Bit 1 indicates that the adapter has won control of the SCSI bus. It is cleared by setting Initiate Bus Arbitration in write register 4 to 0. Bit 2 indicates that a parity error has occurred on data read from the SCSI bus. It is cleared by writing a 1 to write register 4 bit 0. Bit 3 indicates the current level of the SCSI Reset signal (1 for asserted, 0 for negated).

- Bit 0-Interrupt

- Bit 1—Arbitration Complete

Bit 2-SCSI Bus Parity Error

Bit 3—SCSI Reset

- Bit 4—FIFO Direction (Write Register 4 bit 6)

- Bit 5—Enable FIFO (Write Register 4 bit 7)

Bit 6—Enable SCSI Parity (Write Register 4 bit 3)

Bit 7—Enable SCSI Bus (Write Register 1 bit 7)

Offset 2, Write. Interrupt Control

Bits 4–7 enable the corresponding interrupt sources when set to 1. In bits 0-3 when the FIFO reaches this value  $\times 512$ , an interrupt is generated. The value 0 is interpreted as a full FIFO if data is being read from the SCSI device and empty if data is being written to the SCSI device, whereas 1 is for 512 bytes, 2 for 1024, etc.

Bits 0-3-FIFO Interrupt Count

Bit 4-Interrupt on FIFO Count

Bit 5—Interrupt on Arbitration Complete

Bit 6—Interrupt on SCSI Select

Bit 7-Interrupt on SCSI C/D and Request

Offset 3, Write. SCSI Synchronous Control

The rate of Acknowledge pulses can be controlled for synchronous operation. The control period for the adapter is 50 nanoseconds. The base period is 200 nanoseconds, i.e., with this field set to 0. If the field is set to one, the period 20 goes up to 250 nanoseconds, if set to two, 300 nanoseconds, and so on, up to 950 nanoseconds. The period will either be the value stated, or higher, which may be the case if synchronization with the FIFO is required. The Acknowledge is always asserted for 100 nanoseconds, with the remaining time made up in the deasserted state. The fast synchronous mode is enabled by setting bit 6 to 1. This mode ignores the Acknowledge period above and always uses a 100 nanosecond cycle with the Acknowledge asserted for 50 nanoseconds and deasserted for 50 nanoseconds. Bit 6 must be enabled along with the enable synchronous bit. Bit 7  $^{30}$ enables synchronous mode when set to 1.

Bits 0-3-Acknowledge Period

Bit 4-Reserved, Should Always Be Written As Zero

Bit 5—Reserved, Should Always Be Written As Zero

Bit 6-Enable Fast Synchronous

Bit 7—Enable Synchronous

offset 4, write. FIFO Control

Writing a 1 to bit 0 clears all data from the FIFO, resets the SCSI Parity Error Flag, and clears the SCSI Reset Interrupt. This is a momentary pulse and this data is not saved. Bit 2 initiates a SCSI bus arbitration (see Section 4.7). Bit 3 enables SCSI data parity generation. Bit 4 enables external driver for interrupts and the SCSI Reset interrupt latch. In bit 60 equals Read and 1 equals Write. Read is from the SCSI target to the host bus and Write is from the host bus to the SCSI target. Bit 7 enables the FIFO for data phase operations. The mode of operation, asynchronous, synchronous or fast synchronous is determined by the Synchronous 50 Control Register. If the FIFO is not enabled, the data may be read a single byte at a time from the SCSI port using PIO.

Bit 0-Clear FIFO and SCSI Parity Error Status

Bit 1-Reserved, Should Always Be Written As Zero

Bit 2-Initiate Bus Arbitration

Bit 3-Enable SCSI Parity

Bit 4—Enable Interrupts

Bit 5-Reserved, Should Always Be Written As Zero

Bit 6—FIFO Direction

Bit 7-Enable FIFO

It is important to note that the SCSI Reset line can also cause an interrupt if interrupts are enabled. An interrupt is generated on each transition of the SCSI Reset line. When the SCSI Reset line is asserted, an interrupt is generated, and 65 when the SCSI Reset line is deasserted, an interrupt is generated. This can be used by the software to detect any

change in the state of the SCSI interrupt line. This feature is only required in the target mode of operation. Offset 5, Read ID code (LSB)

The lower 8 bits of the ID code are read. This is the microchannel ID that would be assigned. This ID is read in whether the chip is in AT mode or microchannel mode. If the ALTADR pin is open, the ID returned is 60E9, and if it is at ground, the ID is 6127. This allows identification of two separate controllers if it is desired to have two separate adapters installed. This register is intended for use to help in finding the card in a memory mapped system, or for iden-

tifying the fact that the primary or secondary adapter has been located.

Offset 6, Read. ID code (MSB),

The upper 8 bits of the ID code are read.

Offset 7, Read and Write. Echo register

This is a read and write register. It can be used for setting semaphores, or for some other type of communication between multiple users or drivers for the adapter. What is written into the port is read back from the same port. Offset 8, Read and Write

This offset is the same as Offset 0, except that a SCSI Acknowledge is not generated. This allows a message input byte to be examined without an Acknowledge, so that it can be rejected. If the message is not rejected, a subsequent read at Offset 0 will generate the Acknowledge.

Offset 9, Read. Interrupt Mask

Bits 2-0—Reserved

Bit 3—Interrupt Enable (Write Register 4 bit 4)

Bits 7-4—Interrupt Mask (Write Register 2 bits 7-4) offset A, Read. Option Select

This is a direct read back of the microchannel POS option select register. The field are as given in Section 4.2. Note that, at AT mode, the address and interrupt fields are determined by the input jumpers as described in Sections 4.3 and 4.4. The card enable field is also read here, but is not relevant since access to this register implies that the card is enabled (in AT mode, the card is always enabled).

Offset E, Read. FIFO Count

This 16 bit register contains the count of the number of bytes currently in the FIFO.

A more detailed overview of the invention is shown in FIG. 2. Where applicable, individual blocks in FIG. 2 have been assigned the reference numerals corresponding to those blocks in FIG. 1. FIG. 2 illustrates the host computer address bus 144 which is coupled to the address buffers and decoding circuitry **146**. It will be recalled that the circuit decodes address bits 0-16, leaving address bits 17 and higher to be decoded by external logic.

In order to be compatible with MCA architecture, the circuit includes a microchannel programmable option select (POS) circuit 148. The programmable option select feature is not found in the ISA architecture. It provides software configurable switches in lieu of mechanically actuated switches for setting hardware options such as the I/O and 55 memory base addresses.

The FIFO support and control block 134 of FIG. 1 is shown in more detail in FIG. 2, comprising FIFO control logic 150, FIFO address generator 152, and FIFO data bus buffer 154. The address generator and data buffer communicate with the address bus and data bus, respectively, of the main FIFO buffer 132 (not shown). FIFO control logic 150 provides the main FIFO chip select and read/write signals on lead 156. The FIFO data buffer 154 communicates with the internal data bus 118, as illustrated. Also communicating with the internal data bus is the 256×8 static RAM 158. This static RAM is used for variable storage and scratch pad

registers. The host computer can access the status RAM 158 via the host data bus, data bus buffer 120 and internal data bus

The I/O FIFO 126 is shown in more detail in FIG. 2 as comprising a 16×8 output FIFO 160 and a 16×8 input FIFO 5 Both of these FIFOs are coupled to the internal data bus for data communication in the directions shown. Data flow control logic 128 controls both FIFOs 160 and 162 over the input/output FIFO load/unload lead 164. The status of both FIFOs is provided to the data flow control logic via the input/output FIFO status lead 166. Main FIFO status is provided to the data flow control logic via the main FIFO status lead 168.

The data flow control logic is responsible for coordinating incoming SCSI requests with outgoing SCSI acknowledge signals. The SCSI request logic block 170 receives request (REQ) signals from the SCSI control bus 116 and provides an indication thereof to the data flow control logic 128. Depending on the mode of communication selected, the data 20 flow control logic can command the SCSI acknowledge logic 172 to place an acknowledge (ACK) on the SCSI control bus 116. In order to handle the condition in which more than one SCSI device simultaneously attempts to gain access to the bus, the circuit includes SCSI arbitration logic 25 174. The arbitration logic is responsive to the condition of the SCSI data buffers 122. Further details of the foregoing logic blocks will be provided below.

Being an I/O mapped implementation, the circuit of the invention provides a plurality of control ports and status ports which the host computer may access for performing desired functions and gaining certain information. Table III outlined the control ports and status ports of the presently preferred embodiment. In FIG. 2, the control ports are designated generally by reference numeral 176 and the status ports by reference numeral 178.

The pinout layout of the presently preferred single chip embodiment of the invention is shown in FIG. 3. Specifically, FIG. 3 illustrates the single chip embodiment 180 having pins or leads carrying the various signals identified. 40 A listing of these signals and some other internal signals is provided in Table IV below. For convenience, some of the signals on the leads illustrated in FIG. 3 have been grouped together under common reference numerals. Accordingly, lead 182 is the clock input lead on which a 40 MHz external clock is applied. Leads 184 form the DI0–7 data leads of the  $^{45}$ ROM/main FIFO interface. Leads 186 comprise the RA address leads for bits 0-12 of the ROM/main FIFO interface. Leads 188 comprise the interrupt leads for connection to the host interrupt bus, while leads 190 and 192 connect to the 50 DB data bus of the host computer. The SCSI data bus connects to leads 194, while the SCSI control leads are connected at 196.

TABLE IV

| Signal  | Meaning                 |  |

|---------|-------------------------|--|

| RESET-  | Reset signal (low true) |  |

| ICLK40  | 40 MHz clock input      |  |

| CLK0    | Internal 20 MHz clock   |  |

| CLK1    | Internal 20 MHz clock   |  |

| T1      | Clock phase 1           |  |

| T2      | Clock phase 2           |  |

| Т3      | Clock phase 3           |  |

| T4      | Clock phase 4           |  |

| T123    | Clock phases 1-3        |  |

| DECCLK  | Clock phases 1-2        |  |

| ARBCLK- | Clock phases 2-3        |  |

| DECCLK- | Clock phases 3-4        |  |

TABLE IV-continued

|    |                      | TABLE IV-continued                                                                         |

|----|----------------------|--------------------------------------------------------------------------------------------|

|    | Signal               | Meaning                                                                                    |

|    |                      |                                                                                            |

| 5  | ARBCLK               | Clock phases 4-1                                                                           |

|    | IAxx                 | Internal buffered address lines                                                            |

|    | IBHE                 | Internal bus high byte enable                                                              |

|    | GACSA,<br>ICSGA,     | Internal decode of chip select                                                             |

|    | LCSGA                |                                                                                            |

| 10 | MEMCY,               | Internal decode of memory cycle                                                            |

| 10 | MEMCYL               |                                                                                            |

|    | IOSELECT,            | Internal decode of I/O cycle                                                               |

|    | PORTI,               |                                                                                            |

|    | PORTIM<br>PORTL,     | Internal decode of I/O cycle (ports 0-7)                                                   |

|    | PORTLO               | internal decode of 1/0 cycle (poins 0-7)                                                   |

| 15 | PORTH,               | Internal decode of I/O cycle (ports 8-15)                                                  |

|    | PORTHI               |                                                                                            |

|    | IMEMW                | Internal decode of host write cycle                                                        |

|    | IMEMR                | Internal decode of host read cycle                                                         |

|    | IMRW                 | Internal decode of host read or write cycle                                                |

| 20 | ACMD<br>FIFOB        | MCA command phase<br>First byte of 16 bit FIFO access cycle                                |

|    | PTRQ                 | Request for data cycle for host bus                                                        |

|    | PTGNT                | Host bus cycle grant                                                                       |

|    | SCSIRQ               | Request for data cycle for SCSI path                                                       |

|    | SCGNT                | SCSI cycle grant                                                                           |

| 25 | FIFOCLR-,            | FIFO and counter reset signals (low true)                                                  |

| 25 | CTRCLR-<br>FIFOENA   | Enable main FIFO transfers to/from SCSI                                                    |

|    | FIFODIR              | FIFO direction is to SCSI output                                                           |

|    | FIFODIR-             | FIFO direction is from SCSI input                                                          |

|    | SCSYNC               | Synchronous SCSI data mode                                                                 |

|    | SYNCFAST             | Fast synchronous SCSI data mode                                                            |

| 30 | ASY<3:0>             | Synchronous SCSI Ackowledge period                                                         |

|    | BOT512-<br>FCNT12,   | FIFO contains less than 512 bytes (low true)<br>FIFO data count most significant four bits |

|    | · · · · ,            | The data count most significant rout bits                                                  |

|    | FCNT09               |                                                                                            |

|    | FIFINT-              | FIFO interrupt (low true)                                                                  |

| 35 | BEMPTY-              | Main FIFO empty (low true)                                                                 |

|    | BFULL-               | Main FIFO full (low true)                                                                  |

|    | IEMPTY-<br>OFULL-    | Input FIFO empty (low true)<br>Output FIFO full (low true)                                 |

|    | OEMPTY-              | Output FIFO empty (low true)                                                               |

|    | ISREQ                | SCSI Request and not SCSI Acknowledge                                                      |

| 40 | REQCNT               | Positive count of unserviced synchronous                                                   |

| 40 | 51014 <i>01</i> 7    | SCSI Requests                                                                              |

|    | SYNACK-              | Synchronous SCSI Acknowledge (low true)                                                    |

|    | SACK<br>BIGWT        | SCSI Acknowledge<br>Write asynchronous SCSI data to main FIFO                              |

|    | BIGRD                | Read main FIFO data to asynchronous SCSI                                                   |

|    | SCSIRQA-             | Asynchronous SCSI data request                                                             |

| 45 | ACKHOLD              | Holdoff of SCSI input cycle during                                                         |

|    |                      | synchronous Acknowledge                                                                    |

|    | OLDCK                | Output FIFO load clock                                                                     |

|    | OUNCK<br>LITFIFR     | Output FIFO unload clock<br>Input FIFO read cycle                                          |

|    | S240OE-              | Enable ISC bus onto IB bus                                                                 |

| 50 | SC245G-              | Enable D bus/IB bus bidirectional buffer                                                   |

| 50 | SC245D-              | Direction of D bus/IB bus buffer (low for                                                  |

|    |                      | IB to D)                                                                                   |

|    | SY373-               | Latch SCSI output data (synchronous mode)                                                  |

|    | SC373CK              | Latch SCSI output data                                                                     |

|    | DB<15:0><br>D<7:0>   | Host data bus<br>Internal data bus                                                         |

| 55 | PD<7:0>              | Internal data bus extension for I/O read ports                                             |

|    | IB<7:0>              | Intermediate data bus for SCSI data path                                                   |

|    | ISC<7:0>             | SCSI inut data path (low true)                                                             |

|    | SD<7:0>              | SCSI output data path                                                                      |

|    | SC<7:0>-             | SCSI data bus (low true)                                                                   |

| 60 | DIO<7:0><br>RA<12:0> | Data I/O bus for ROM and main FIFO RAM<br>Address for main FIFO RAM                        |

| 20 | NAS12.0>             |                                                                                            |

The switches SW0-3, used to configure the I/O and memory base address are depicted at 198. The host computer address bus connects to leads 200 in addition to electrical power VDD and VSS, the remaining leads provide other control functions and bear the conventional MCA and/or

10

ISA pin designations. One notable addition is pin 142 which comprises the user-settable means for selectively enabling either the MCA or the ISA architecture configurations. This pin is also designated PS2, the PS2 designation being another nomenclature for MCA architecture.

Detailed System Description

The remaining FIGS. 4 to 46 may now be referred to for the detailed description of the presently preferred embodiment which follows.

Referring first to FIG. 4, the 40 MHz clock divider circuit is illustrated generally at 202. The clock signal CLK40 which was input on lead 182 is divided by circuit 202 into a four phase, 10 MHz clock. The clock signals so generated are used throughout the remainder of the circuit and are instrumental in establishing the data flow control logic 128 15 of FIG. 2.

In FIG. 5, the internal arbitration logic circuit depicted generally at 204. This circuitry decides whether the internal data bus 118 is shared and which operation is given access to the internal data bus as between host bus operations and SCSI transfers. The internal arbitration logic may also be 20 considered part of the data flow control logic **128** of FIG. 2.

At the 10 MHz basic clock rate, each cycle of 100 nanoseconds is devoted to either a host processor phase or a SCSI phase. The internal arbitration logic circuit provides two outputs, one designated PT GNT and one designated SC  $\,$  25  $\,$ GNT. The former serves as the processor grant signal and the latter as the SCSI grant signal. The signals are mutually exclusive so that only one of these two functions may have access to the internal data bus at a time. The terminal designated SCSI RQ is the request from the SCSI logic for 30 access to the bus, while the signal designated PT RQ is the request from the processor for cycle. Priority is given to the processor cycle.

The internal arbitration logic circuit includes an edge detection circuit so that it may detect processor requests for 35 cycle. The circuit includes generation of timing states, depending on whether an 8 bit or a 16 bit cycle is invoked. The edge detector circuit includes a flipflop which provides a hold signal that prevents a double trigger of the edge detector. The circuit also provides a PT2- which extends the 40 bus cycle for ROM transfers, because ROMs are typically slower devices and need the extended bus cycle time.

FIG. 6 depicts the basic address decode circuitry 206. This circuit breaks down general address ranges and detects whether the host is accessing ROM, the main FIFO, or the 45 internal static RAM 158. To do this it decodes some of the upper address bits.

Main FIFO access is not a straight address decode operation, since certain other conditions must be met before the processor can access the main FIFO. Specifically, to access 50 the main FIFO the FIFO chip select signal must be asserted as well as the FIFO output enable or write enable signal. If the bus is on a SCSI cycle, a similar operation is required, although there is no need for address decoding.

Circuit **206** provides FIFO B and FIFO B- signals which 55 are used to implement a 16 bit cycle notwithstanding that the internal data bus is 8 bits wide. The FIFO B signal is used to split a 16 bit cycle into two 8 bit cycles on the internal data bus, with the FIFO B signal indicating that it is the first of those two cycles. The FIFO B signal ensures that the next 60 cycle will be used to access the second 8 bit half of a 16 bit access.

FIG. 7 comprises some additional address decoding logic shown generally at 208 as well as the ROM and FIFO data buffer shown generally at 210. The circuitry of FIG. 7 65 controls the read cycles and latching of data into the data bus buffers.

FIG. 8 comprises similar circuitry dedicated to the control of write cycles and latching of data in the write buffers. The circuitry of FIGS. 7 and 8 may be considered part of the address buffers and decoding block 146 of FIG. 2. Data is maintained on the internal data bus for approximately 50 nanoseconds, making it necessary to latch the data during read cycles. The address decode logic circuit 208 of FIG. 7 generates latch control signals DBRDHI and DBRDLO, as well as the Boolean NOT versions of those signals. The circuit of FIG. 8 includes a portion designated generally at 212 which generates the IOCHRDY signal which is used by the MCA and ISA control decode logic block 140 of FIG. 2. This signal is a standard signal in the MSA and ISA architectures. It is used to insert a wait state.

Turning now to FIG. 9, the FIFO address generator circuit is shown generally at 214. A more detailed representation of the FIFO address generator are shown in FIGS. 37 and 38. The FIFO address generator circuit generates either a read address or a write address. It employs two counters which it multiplexes, depending on whether the operation is a read or a write. Each time a read operation occurs the read counter is incremented and each time a write operation is incurred the write counter is incremented. In effect, the FIFO address generator circuit 214 makes the main FIFO behave as a circular buffer with first in, first out behavior. Reading occurs in the same sequence as writing.

It will be recalled that the main FIFO appears as a single port device to the host computer. The FIFO address generator circuitry is required because the host computer cannot directly generate addresses for accessing the main FIFO.

FIG. 10 depicts the control register for the main FIFO. The circuitry in FIG. 10 also generates some clock signals which are used as control signals for the FIFO address generator circuit 214. These clock signals are designated INCLK- and OUTCLK-. The circuitry also provides the select signal for read or write addressing, designated WRADEN-. The FIFO control register comprises one of the control ports which may be accessed by the host computer. In the presently preferred embodiment, this port resides at offset 04h. As described above, control port 4 is a write register comprising one of the control ports 176 of FIG. 2. The FIFO control register provides internal control signals which control the incrementing and decrementing of the FIFO address generator.

By virtue of the circuit construction, the host computer can always access the main FIFO during the appropriate cycle. Devices on the SCSI side will only access the main FIFO if the FIFO is enabled. The circuit is capable of several different kinds of transfers, unbuffered asynchronous transfers, buffered asynchronous transfers and buffered synchronous transfers. Enabling the main FIFO allows one of the buffered transfers to take place. Disabling the main FIFO allows the unbuffered asynchronous transfer to take place. Synchronous transfers are always buffered.

The circuit of FIG. 10 provides a FIFO clear signal designated FIFOCLR-, which resets all counters on the entire interface chip 180.

FIG. 11 depicts the data counter circuitry shown generally at 216. The data counter circuitry is used to keep track of the fullness within the main FIFO. A more complete representation of the FIFO data counter is found in FIG. 39.

Turning now to FIG. 12, the SCSI control port circuitry is depicted at **218**. With reference to above Table III, the SCSI control port resides at offset 01h, valid for write operations. SCSI control leads 196 include several control signals generated by circuitry 218. For example, if a SCSI reset signal is desired, the reset signal SRST is asserted by writing

to port 1 with the appropriate bit set corresponding to the reset signal. Each bit of port 1 is mapped to a selected one of the SCSI control signals. Some of the control signals such as SBSY and SACK have other control signals gated with them and are thus generated in a different way.

FIG. 13 provides the circuitry, shown generally at 220, required to read the status of the SCSI bus. The circuitry allows the control lines to be read to determine what the bus status is. For example, it is possible to determine if there is an active request or if there is a message phase or a data 10 phase in effect. The bus phase, as well as other asynchronous bus conditions can be decoded using circuitry 220. The SCSI bus status port resides at offset 01h for read operations.

FIG. 14 depicts the asynchronous SCSI flow control circuitry 222. This portion of the data flow control logic 15 determines when the circuit is performing a FIFO read or FIFO write from the main FIFO directly onto the SCSI data port. Since this is an asynchronous operation, the I/O FIFOs are not involved. Circuitry 222 also generates a SCSI request and generates the actual cycle signal for causing a main 20 FIFO read or write. These signals are designated BIGWT and BIGRD, for the write and read signals, respectively. Boolean NOT signals of both read and write signals are also provided.

FIGS. 15 and 16 illustrate the circuitry which provides the 25 chip ID byte used by the MCA architecture. This ID byte is also readable by the host computer if ISA architecture is selected. Specifically, the portion of the circuit illustrated in FIG. 15 generates the high byte or most significant portion of the ID. Referring to Table III, these ID codes are read 30 from ports 5 and 6 (offsets 5 and 6).

Another control register can be used for SCSI mode control and loopback operation. This control register is specifically for selecting whether synchronous or asynchronous transfers are to be performed, and to select the syn- 35 chronous data rate for synchronous transfers. The circuit includes an echo register which forms part of the control and status port blocks 176 and 178 of FIG. 2. The echo register is a single port which can be read from or written to. When a given value is written to the echo register it is echoed back 40 or repeated for reading. The echo register is thus useful for system integrity self-testing or as a flag port to convey software flags or the like. In Table III the echo register resides at offset 7.

FIG. 16 depicts the synchronous SCSI data path and 45 parity checking circuitry. A more detailed circuit description is given in FIGS. 33-39. Referring to FIG. 16, the input FIFO 162 and the output FIFI 160 are illustrated. Also illustrated generally at 122 are the SCSI data buffers shown also in FIG. 2. The circuitry includes a parity checker circuit 50 used to determine if there is a parity error PERROR condition. The parity checker circuitry is shown generally at 226. The input and output FIFOs are both only 8 bits wide. The 9th parity bit normally found on the data bus is not carried past the input buffers. Hence the separate parity checking 55 circuitry is provided.

Turning now to FIG. 17, the asynchronous SCSI data path circuitry is illustrated. This circuitry includes arbitration logic which is implemented using two programmable array logic circuits (PALS), designated at 228 and 230. The 60 equations for the PALS are provided in the attached Appendix. To the left of PALS 228 and 230 there is a priority encoder circuit 232 which determines which SCSI device will win during the SCSI arbitration phase. Each SCSI device has an ID assigned to it. When the device wishes to 65 arbitrate for the bus, it pulls the bit on the SCSI data bus corresponding to its ID during the arbitration phase of the

cycle. If more than one device has similarly done so during this arbitration phase, the one with the highest assigned priority will get access to the bus. The priority encoder compares its assigned ID with all others requesting access to the bus. The priority encoder simply selects the highest priority of all IDs presently on the bus and provides that information to PAL 228. PAL 228 then makes the determination whether it or some other device has won the arbitration priority contest.

The SCSI data buffers 122 (FIG. 2) are shown in more detail in FIG. 18. As illustrated, these circuits provide the data output drivers for the SCSI side of the circuit. Open collector driver switches are used to conform to the SCSI specification.

FIG. 19 depicts the synchronous request counter. In synchronous mode it is necessary to keep a count of the number of requests that come in. When those requests are serviced, the count is decremented. The circuitry of FIG. 19 keeps this synchronous request count. The output REQCNT indicates that there is a nonzero count. This signal is used as part of the data flow control logic to indicate that a transfer of data is necessary due to active requests.

The synchronous acknowledge logic is illustrated in FIG. 20. This circuitry is part of the synchronous acknowledge logic circuitry 172 of FIG. 2. It provides a timing circuit for generating acknowledge signals which depend on the status of the data transfer and the actual length of the synchronous cycle. The ASY bus provides bits which are used to signify the actual length of the synchronous cycle as provided by the synchronous control register. The data rate is set to match what was negotiated at the beginning of the synchronous transfer cycle. This rate determines how far apart the acknowledge signals ACK are spaced. Acknowledges are sent on a per byte basis. The target asserts a request for a byte and the circuit then asserts an acknowledge ACK for each request so that there is a one to one correspondence between bytes transferred and requests asserted by the target and acknowledges asserted by the circuit of the invention. The difference between synchronous and asynchronous transfer is that with synchronous transfer there is an offset between requests coming in and acknowledges going out. In asynchronous mode the requests are interleaved with acknowledges so that a direct one to one interlocked operation occurs. In the synchronous mode requests can be buffered and then acknowledged some time later. The presently preferred embodiment provides a latency of 16 so that a target can send up to 16 requests before and acknowledgement must be made. The circuitry of FIG. 20 keeps track of this information concerning the number of requests received and whether an acknowledge has been sent. Acknowledges do not occur until the data is offloaded into the main FIFO from the input FIFO. In the other flow direction, acknowledges of output data do not occur until the data actually goes out onto the bus, which can account for some time delay.

The circuit supports the necessary interrupt logic needed to operate on either MCA or ISA architectures. The interrupt logic circuitry is shown in FIGS. 21 and 22. Included in the circuit of FIG. 21 is an interrupt control register 234 which contains 4 bits which the main FIFO count is compared to. When the count of the main FIFO reaches the number stored in interrupt control register 234, an interrupt is sent to the host computer. The interrupt control register also contains 4 mask bits which are used to mask out individual interrupt conditions.

The circuit also includes an interrupt status register 236 which can be interrogated by the host computer to determine the nature of various interrupt conditions that may have

occurred. While primarily used for interrupt status, this register can also be used to store other status conditions which can then be read through the interrupt status register port. In Table III the interrupt status is read by accessing port **02**h. The interrupt mask comprising a portion of interrupt  $_5$  control register **234** is located at port **09**h.

There are five interrupt conditions which the present embodiment will respond to. One is the main FIFO fullness interrupt. The comparators and logic for determining main FIFO fullness is shown generally at **238**. The other interrupt conditions include the SCSI reset interrupt, a command request interrupt (for designating that the target is requesting a command byte from the host), the SCSI select phase interrupt (used by the device that won arbitration in selecting the device it wishes communication with) and the arbitration phase completion interrupt (asserted by the winner of the 15 arbitration phase).

FIG. 23 depicts the SCSI data gating circuitry which is part of the data flow control logic. This circuitry enables the different buffers in the SCSI data path to ensure data flow in the proper direction.

FIG. 24 depicts synchronous SCSI flow control logic for controlling the synchronous SCSI data flow. This circuit enables the transfer of data between the main FIFO and the I/O FIFO, taking into account the status of the I/O FIFO.

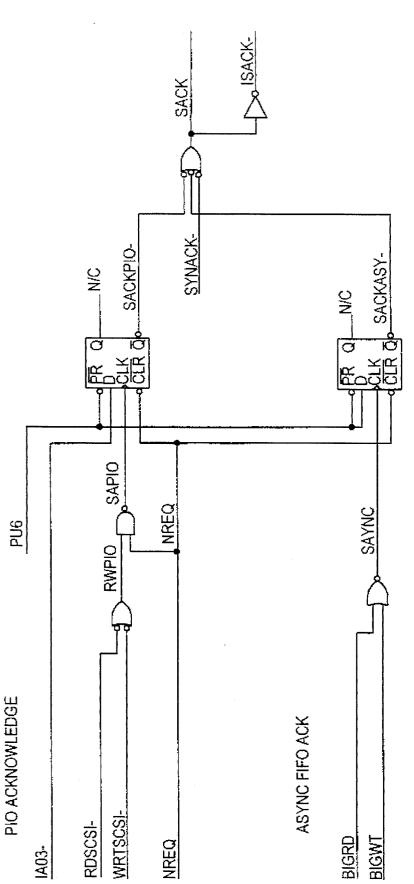

The SCSI acknowledge logic is shown in FIG. 25. The 25 circuitry is related to the synchronous SCSI acknowledge circuitry of FIG. 20, but also includes the asynchronous acknowledges which are generated either in unbuffered transfers by reading and writing port 0 add in buffered transfers which are reading and writing to and from the main 30 FIFO. By reading through port 0 the circuit automatically generates an acknowledge feature is disabled to allow the host computer to inspect a message byte, determine if the message byte is to be handled and then to take action or not. In 35 other words, the circuit provides two SCSI data ports, port 0 which provides automatic acknowledge generation and port 8 which does not. Address bit 3 (IA03) is used to designate port 8 or port 0.

The system includes address buffers coming from the host 40 bus. These buffers comprise inverters which convert the logical polarity of the signals.

FIG. 26 illustrates a data bus buffers at 240 and the internal RAM 258. The circuit further includes an internal RAM and a latch for latching the address when configured 45 in the MCA mode. This latch is necessary because the address on the bus is not latched in the MCA architecture.

FIG. 27 illustrates another address latch for some additional address bits. The circuitry on FIG. 27 also includes decoding circuitry used to decode the MCA and ISA control signals. In general, this circuitry detects what kind of bus cycle is desired, decodes those signals and asserts the appropriate memory read or write signals for the internal controls of the chip.

FIG. **28** illustrates further control signal decoding circuits 55 for the same purposes.

With reference to FIG. 29, the chip select decoding circuitry is illustrated. In order to determine whether the chip (i.e., chip 180) has been selected, this circuitry decodes the most significant bits of the address coming in to the chip. 60 The circuit also detects whether the circuits of FIGS. 27 and 28 have decoded an input/output or a memory cycle. Based on whether an input/output (I/O) or a memory cycle has been decoded, the circuit of FIG. 32 decodes the address range differently. The address decode circuitry of FIG. 29 thus 65 allows selective access to either the I/O ports or the memory space addressed by the chip.

FIG. 30 depicts the interrupt selection circuits which provide 7 interrupt outputs from the chip on leads (FIG. 3). Ordinarily only one of the interrupts will be enabled for a given hardware implementation. For an MCA application the programmable option select (POS) setting may be used to determine what interrupt level and hence what lead will be active when an interrupt occurs. In an ISA implementation switches S0–S1 (see FIG. 3) are appropriately set to select the desired interrupt level. Ordinarily jumpers or dual inline pin (DIP) switches are used for this purpose and may be attached to the S0 and S1 leads of the chip.

In accordance with the microchannel architecture specification, the chip of the invention is capable of being software configured. When an MCA computer is poweredup a software configuration program runs which searches the disk file for one that matches the ID register on each option device plugged into the mother board. A SCSI controller card is an example of such a device. Using the chip of the invention to implement a SCSI controller card, the ID register on the chip would be read at power-up time, if not previously installed in the system. Next, the user is given an opportunity through the software configuration program to select the desired configuration parameters such as base address and interrupt level. The configuration program sets these values and stores them in nonvolatile memory which is part of the computer system. Thus when the computer system is powered-down and next powered-up, the nonvolatile memory retains the configuration parameters which are then used to set up or configure the SCSI chip.

FIG. **31** is the interrupt mask register for implementing the port **9** interrupt mask. This interrupt mask is also referred to in Table III. This circuit is an input port to allow the user to program which interrupts are to be enabled and disabled. The register serves as a status port from which the selected interrupt configuration can be read.

Software Considerations

There are primarily three ways that the host computer can talk to the chip of the presently preferred embodiment through software. One is using the system BIOS, two is through a loadable device driver and three is through executable routines which may be provided as a tool kit of different functions which the software engineer can select from. Port 8 is provided to allow direct access to the SCSI data bus without generating an acknowledge. This port is thus useful in reading from the target during the Message In phase. This will allow the processor to decide whether the message is to be accepted or rejected. If the message is to be accepted, reading port 0 will generate the acknowledge. Port 8 should also be used in place of port. 0 when setting up the ID prior to arbitration or target selection. This is important on multiinitiator systems, since spurious acknowledges could disrupt the operation of another initiator. Finally, port 8 should be used instead of port 0 when reading the ID during reselection.

When disconnecting after a Data Out phase, it is necessary to read the FIFO counter, adjust the current SCSI data pointer by this amount and clear the FIFO. When disconnecting following a Data In phase, the contents of the FIFO should be read out completely before another data transfer is begun. The FIFO counter only indicates the volume of data present in the main FIFO. In synchronous mode the input and output FIFOs contain data which has been requested and not acknowledged. The software assumes that a disconnect will normally occur only after all requests have been acknowledged.

The following is an example of suitable **80286** code which may be used to control the chip of the presently preferred embodiment.

5,544,326

19

; TMC-1800 SCSI HOST ADAPTER CODE EXAMPLE - ARBITRATION ROUTINE - SELECTION ROUTINE - DATA IN ROUTINE - DATA OUT ROUTINE

.286c

; EXTERNAL PROCEDURE DELCARATIONS

| EXTRN START_TIMER:NEAR      | ; STARTS TIMER                   |

|-----------------------------|----------------------------------|

| EXTRN CHECK_TIMER:NEAR      | ; CHECKS TIMER FOR TIMEOUT       |

| EXTRN TMC1800_ERROR:NEAR    | ; ERROR HANDLER                  |

| EXTRN READ_PTR_UPDATE:NEAR  | ; READ POINTER AND FLOW CONTROL  |

| EXTRN WRITE_PTR_UPDATE:NEAR | ; WRITE POINTER AND FLOW CONTROL |

; TMC-1800 PORT ADDRESS DEFINITIONS (I/O BASE ADDRESS = 140H ASSUMED)

| SCSI_ACK                         | = 140H ;                         | READ/WRITE PORT 0 SCSI DATA WITH<br>ACKNOWLEDGE                                            |

|----------------------------------|----------------------------------|--------------------------------------------------------------------------------------------|

| SCSI_STAT<br>SCSI_CTL<br>AD_STAT | = 141H ;<br>= 141H ;             | READ PORT 1 SCSI STATUS<br>WRITE PORT 1 SCSI CONTROL                                       |

| FIFO_CTL<br>SCSI_NO_ACK          | = 142H ;<br>= 144H ;<br>= 148H ; | READ PORT 2 ADAPTER STATUS<br>WRITE PORT 4 FIFO CONTROL<br>READ/WRITE PORT 8 SCSI DATA W/O |

| FIFO                             | = 14CH ;                         | ACKNOWLEDGE<br>READ/WRITE PORT C FIFO                                                      |

; TMC-1800 SCSI STATUS PORT BIT DEFINITIONS

BSY = 01H ; SCSI BUSY

; TMC-1800 SCSI CONTROL PORT CONTROL CODE DEFINITIONS

ENABLE\_CODE = 80H ; ENABLE SCSI BUS SELATN\_CODE = 8AH ; ENABLE SCSI BUS AND ASSERT SEL AND ATN ATN\_EN\_CODE = 88H ; ENABLE SCSI BUS AND ASSERT ATN ; TMC-1800 ADAPTER STATUS PORT BIT DEFINITIONS

ARB\_DONE = 02H ; ARBITRATION COMPLETE

.

; TMC-1800 FIFO CONTROL PORT BIT DEFINITIONS

| ARB      | = 04H ; | INITIATE ARBITRATION           |

|----------|---------|--------------------------------|

| FIFO_DIR | = 40H ; | FIFO DIRECTION (SET FOR WRITE) |

| FIFO_EN  | = 80H ; | ENABLE FIFO FOR SCSI DATA      |

# ; MISCELLANEOUS DEFINITIONS

| HALF_SECOND<br>THREE_SECONDS |  | ; TIMER TICKS FOR 1/2 SECO<br>; TIMER TICKS FOR 3 SECOND | ND |

|------------------------------|--|----------------------------------------------------------|----|

|------------------------------|--|----------------------------------------------------------|----|

\_TEXT

| SEGMENT<br>ASSUME | PUBLIC<br>TEXT   | 'CODE' |

|-------------------|------------------|--------|

| ASSUME<br>ASSUME  | <br>TEXT<br>TEXT |        |

; PROGRAM VARIABLES (INCLUDED IN TEXT SEGMENT; ASSUMES CODE IS RAM-BASED)

| DATA POINTER D<br>OUR ID D | )B<br>)B<br>)B | <pre>? ; SCSI TARGET ADDRESS<br/>? ; BUFFER ADDRESS<br/>? ; TMC-1800 SCSI ID BIT SET<br/>1,2,4,8,16,32,64,128</pre> |

|----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|

|----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|

| Ŧ          |                                                            |

|------------|------------------------------------------------------------|

| ÷.         | TMC1800_ARB                                                |

| 7          | INITIATE A SCSI CONNECTION THROUGH ARBITRATION.            |

| ;          | MAX WAIT FOR SUCCESSFUL COMPLETION IS 3 SECONDS.           |

| ;          | THIS ROUTINE MAY BE CALLED FREELY AS LONG AS NO            |

| 7          | ACTIVE SCAL CONNECTION EXTERNO DEPUTY                      |

| ż          | ACTIVE SCSI CONNECTION EXISTS BETWEEN THE TMC-1800         |

| - <u>-</u> | AND ANY TARGET; BUS FREE PHASE IS DETECTED BY<br>HARDWARE. |

|            | INTO MARE .                                                |

|            |                                                            |

|            | ENTRY PARAMETERS:                                          |

| 7          | OUR ID = TMC-1800 SCSI ID BIT (ONE BIT SET)                |

| 7          | REGISTERS PRESERVED: CX, DX                                |

| 1          | REGISTERS CHANGED: AX                                      |

| ;          | EXIT PARAMETERS:                                           |

|            | CARRY SET IF TIMEOUT                                       |

|            | WHEN USI IF ITEBUUT                                        |

| ſ          |                                                            |

TMC1800 ARB

| PROC | NEAR            |   |                      |

|------|-----------------|---|----------------------|

| PUSH | CX              |   |                      |

| PUSH | DX              |   | SAVE REGISTERS       |

| XOR  | AX, AX          | , | DAVE REGISTERS       |

| MOV  | DX, SCSI CTL    |   |                      |

| OUT  | DX, AL          |   | DICADIR DAGA DRAMA   |

| MOV  | AL, OUR ID      |   | DISABLE DATA DRIVERS |

| MOV  | DX, SCSI NO ACK |   |                      |

# APPENDIX

NAME PAL 01 ; DEVICE p16r8 3 /\* INPUT PIN DEFINITIONS \*/ /\* CLOCK DERIVED FROM BUS OSC \*/

/\* ARBITRATION PENDING - REQ FROM CPU \*/

/\* SCSI BUSY LINE \*/

/\* SCSI SELECT LINE \*/

/\* HIGHER ADDRESS ARBITRATING \*/

/\* CHIP RESET \*/