Issue 4, 1989

SPECIAL MICRO CHANNEL™ ISSUE

IBM Personal Systems Technical Journal

IBM

IBM Personal Systems Technical Journal is published by the U.S. Marketing and Services Group, International Business Machines Corporation, Roanoke, Texas, U.S.A.

Editor Libby Boyd

Consulting Editor Mike Engleberg

Technical Consultant

Production Coordinator

Automation Consultant

Illustrator Bill Carr

Manager Gene Barlow

To correspond with the *IBM Personal Systems Technical Journal*, please write to the Editor at

IBM Corporation Internal Zip 40-C2-02 One East Kirkwood Blvd. Roanoke, TX 76299-0015

To subscribe to this publication, use an IBM System Library Subscription Service (SLSS) form, available at IBM branches, and specify form number GBOF-1229.

Permission to republish information from this publication is granted to publications that are produced for non-commercial use and do not charge a fee. When republishing, please include the names and companies of authors, and please add the words "Reprinted by permission of the *IBM Personal Systems Technical Journal.*"

Titles and abstracts, but no other portions, of information in this publication may be copied and distributed by computer-based and other information-service systems. Permission to republish information from this publication in any other publication or computer-based information system must be obtained from the Editor.

IBM believes the statements contained herein are accurate as of the date of publication of this document. However, IBM hereby disclaims all warranties as to materials and workmanship, either expressed or implied, including without limitation any implied warranty of merchantability or fitness for a particular purpose. In no event will IBM be liable to you for any damages, including any lost profits, lost savings or other incidental or consequential damage arising out of the use or inability to use any information provided through this service even if IBM has been advised of the possibility of such damages, or for any claim by any other party.

Some states do not allow the limitation or exclusion of liability for incidental or consequential damages so the above limitation or exclusion may not apply to you.

This publication could contain technical inaccuracies or typographical errors. Also, illustrations contained herein may show prototype equipment. Your system configuration may differ slightly. IBM has tested the programs contained in this publication. However, IBM does not guarantee that the programs contain no errors.

This information is not intended to be a statement of direction or an assertion of future action. IBM expressly reserves the right to change or withdraw current products that may or may not have the same characteristics or codes listed in this publication. Should IBM modify its products in a way that may affect the information contained in this publication, IBM assumes no obligation whatever to inform any user of the modifications.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such products, programming or services in your country.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever.

All specifications are subject to change without notice.

Copyright © 1989 by International Business Machines Corporation

## THANK YOU

Thanks to Bob Lohman, Manager, Special Marketing Programs, who supported our efforts and whose staff contributed to this Micro Channel issue.

My special thanks to Joel Cohen, who provided technical direction and coordination for this issue and who was committed to producing information that will be of value to our readers.

Joel J. Cohen is in Special Marketing Programs in IBM's Entry Systems Division at the Boca Raton Laboratory. His responsibilities include the development and coordination of PS/2 demonstrations at business shows. His experience in the computer field extends from centralized batch-oriented to online data processing to personal systems. In a period of over 30 years he has held a variety of staff and management positions involving the design, development, marketing, assurance, usability, and marketplace evaluation of computers. Joel joined IBM in 1964. He holds a bachelor of science degree in electrical engineering from the University of City College in New York and a master of science degree in electrical engineering from Northeastern University in Boston.

Editor

|     | Hardware                                            |

|-----|-----------------------------------------------------|

|     | Micro Channel Architecture                          |

| 1   | Executive Comments                                  |

| 3   | Requirements for Advanced Bus Architecture          |

| 23  | Micro Channel System Configuration Considerations   |

| 43  | Features and Benefits                               |

| 48  | Bus Masters and Applications                        |

|     | Extended Features                                   |

| 53  | Overview of Extended Micro Channel Functions        |

| 61  | New Micro Channel Features                          |

| 66  | SCB - An Architecture for Micro Channel Bus Masters |

|     | Bus Master Design and Applications                  |

| 83  | Design Alternatives with Micro Channel Systems      |

| 86  | IBM PS/2® Micro Channel SCSI Adapters               |

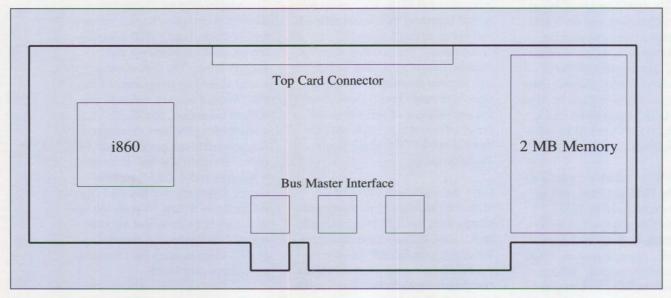

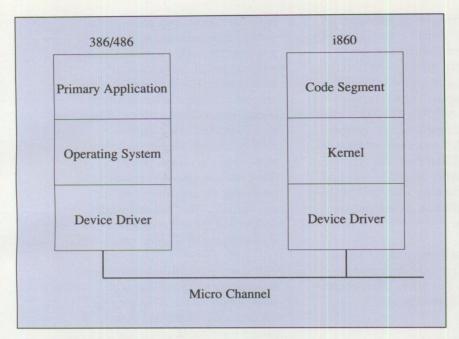

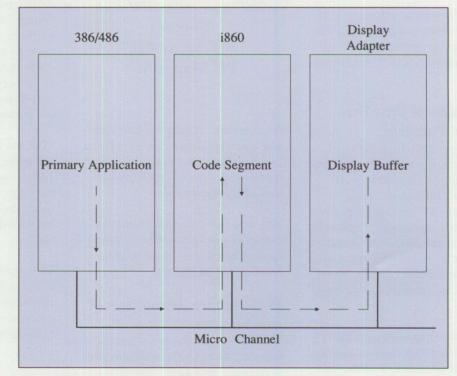

| 93  | PS/2 Wizard Adapter                                 |

| 96  | Experience in Bus Master Design                     |

| 99  | Bus Master Adapters from Independent Option Vendors |

|     | Software                                            |

| 104 | Bus Masters and OS/2 ®                              |

| 112 | Micro Channel Issues in AIX <sup>TM</sup> PS/2      |

|     | Random Data                                         |

| 119 | Information for Developers                          |

| 124 | Book Report                                         |

| 125 | New Products                                        |

|     |                                                     |

## **Executive Comments**

Dr. Robert L. Carberry IBM Corporation Somers, New York

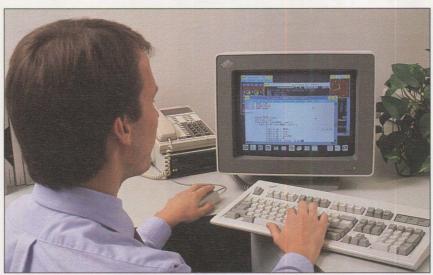

This special issue of the *IBM* Personal Systems Technical Journal highlights IBM's technical leadership and innovation in the definition, design, development and use of Micro Channel architecture.

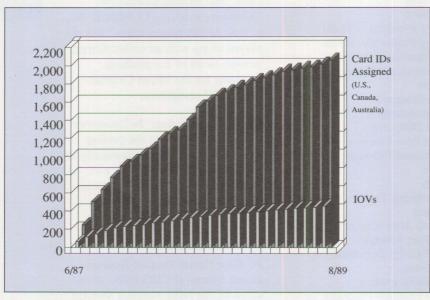

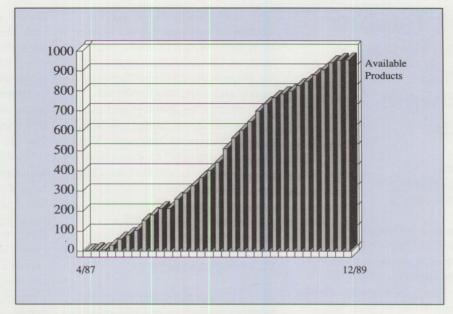

Micro Channel architecture has rapidly established itself as the new industry standard. More than half of the IBM Personal System/2® computers being shipped today are Micro Channel-based, a trend that is continuing to accelerate. As of August 1989, there were over 1000 Micro Channel card products from over 300 independent developers. There were already 27 advancedfunction bus master cards available. And, 197 Micro Channel card IDs have been issued to 93 companies for additional bus master cards - an indicator of much more to follow. Twenty-two other companies have acknowledged the significance of Micro Channel architecture by announcing Micro Channel-compatible systems.

In September of this year, IBM released additional information about Micro Channel architecture, which expands performance, improves system integrity and enhances programmability. The basic I/O data transfer capability of the Micro Channel on the Personal System/2

is up to 20 million bytes per second today. This information describes two additional modes that permit data transfers of up to 40 million bytes per second and 80 million bytes per second, with extendability to 160 million bytes per second. Additional fault detection and isolation capability is provided with data parity, address parity and synchronous channel-check features. Pro-

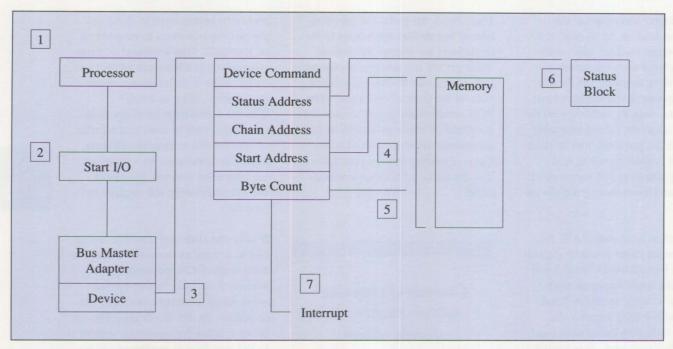

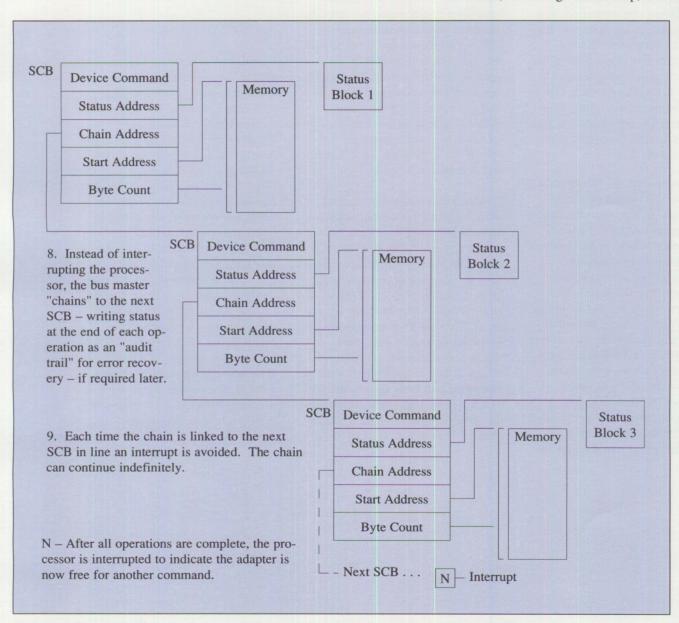

grammability is expected to be enhanced by the introduction of Subsystem Control Block architecture, a standard for communications between bus masters.

In making this announcement, we have demonstrated our continuing commitment to an architecture that provides a sophisticated and a broad platform for multiple families of

products, while allowing significant growth for current product families.

In view of this momentum, it seems appropriate and timely that we dedicate this issue to Micro Channel architecture for the purpose of promoting a better understanding, not only of the architecture itself, but of applications of the architecture with a specific focus on bus masters. In this issue individual authors have the opportunity to describe advantages and functions in their own words.

Our objectives are to:

- Broaden understanding of Micro Channel architecture – including trends and future direction

- Demonstrate its capabilities through applications of the architecture to advanced hardware and software product development

- Demonstrate IBM's intent to increase productivity of independent developers of Micro

Channel products through the availability of interface hardware and consistent software protocol

- Demonstrate IBM's intent to support independent developers of Micro Channel products through the availability of detailed documentation design seminars and the IBM Developer Assistance Program

- Recognize technical contributions of IBM and of independent developers

We hope that developers, dealers and users will all find value in the articles in this issue in terms of gaining a better understanding of the power and depth of Micro Channel architecture as a platform for growth today and in the future.

## ABOUT THE AUTHOR

Dr. Robert L. Carberry is Vice President of Systems for IBM's Entry Systems Division. He joined IBM in 1964. In the Federal Systems Division he held various management positions, including manager of Systems Architecture and manager of Processor Development. In 1979, he became assistant to the President of that division. Dr. Carberry next joined the Data Systems Division as manager of Processor Development and was subsequently appointed to the position of Director of Engineering and Scientific Processor Programs. In 1982, he was named Director of the Data Systems Division, Kingston Laboratory, responsible for various hardware, operating system, and language development activities. In 1984, Dr. Carberry was named Vice President of Systems Architecture and Technology for the Entry Systems Division. In January 1985, he became Vice President, Product Development and Technology and then in August of that year, he became Vice President of Product Line Management and Operations. In December 1986, he joined the Corporate Development Staff as the IBM Director of Systems Product and Technology. In June 1988, he assumed his present position.

## Requirements for Advanced Bus Architecture

Chet Heath IBM Corporation Boca Raton, Florida

The structured channel architecture for microsystems has evolved in the same spirit as the structured channel architecture for System/360 mainframe systems. Like the System/360 channel architecture, Micro Channel architecture has become a standard, an accepted architecture for advanced microsystems. Micro Channel architecture is fully compatible with applications and operating systems for the IBM Personal Computer, and it supports a new family of adapter cards as well as new capabilities.

## **IBM Heritage**

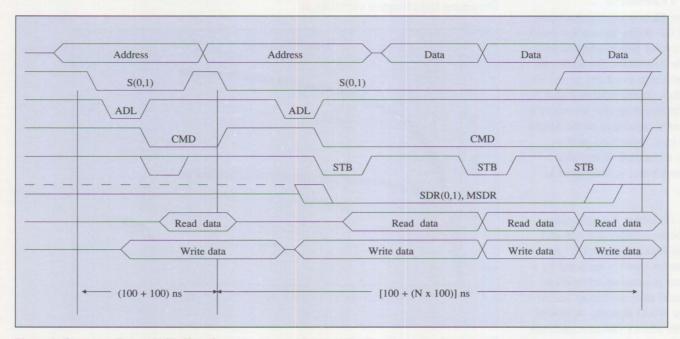

The personal computer owes its heritage to a period in 1973 when IBM introduced the 5100 series of products. The 5100 machine was a desktop computer that could execute about 30,000 instructions per second. It had a 5-inch screen and a keyboard that could not be detached. In its time, it was useful for simple, single-task, single-thread applications, typically written in BASIC or APL.

The IBM 5100 machine later advanced to the 5110, the 5120, the 5130, and the System/23 Datamaster. The Datamaster, based on Intel® 8085 processor architecture, differed principally in its channel architecture from the PC by only four lines. The PC featured additional addressing of up to one million bytes.

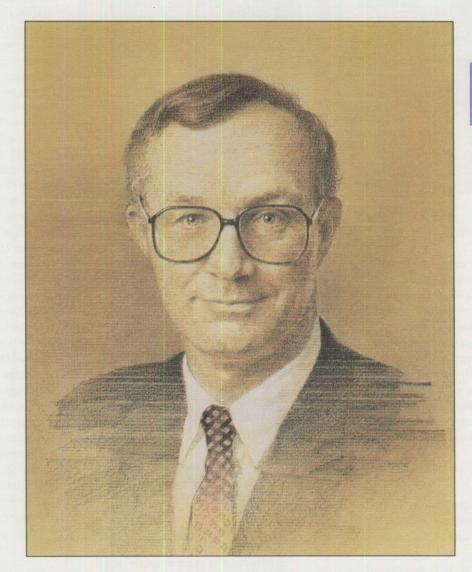

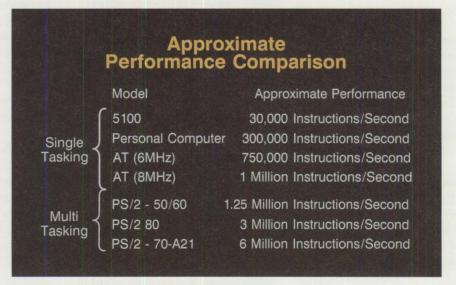

The PC evolved into the Personal Computer XT™ with the addition of a fixed disk. The Personal Computer AT®, initially operating at 6 MHz, produced a theoretical 750,000 instructions per second. That was later upgraded to one million instructions per second with an 8 MHz AT® implementation. For comparison, the theoretical calculations for several machines are shown in Figure 1.

All these implementations were meant to be compatible with previous products, but they lacked a general architecture or direction. It became obvious with the AT computer that a general structured architecture for advanced microsystems would be needed to move to the multitasking, multiuser environment with concurrency, typified by PS/2 Models 50 and higher.

## **Previous Evolutions**

A similar architecture evolution occurred in 1964 when the 1401 series of machines evolved to the IBM System/360. That transition was from single-task, single-thread operations to multitasking, multiuser op-

erations for which the System/360, its channel architecture, and its entire system design were intended.

Another evolution occurred in 1973 in the minicomputer arena between the IBM System/3, which was a single-task, single-thread environment, and the multitasking System/3X series of machines. A transition was provided at this time – the System/32 was provided to continue the single-task applications in equipment designed for the multitasking environment.

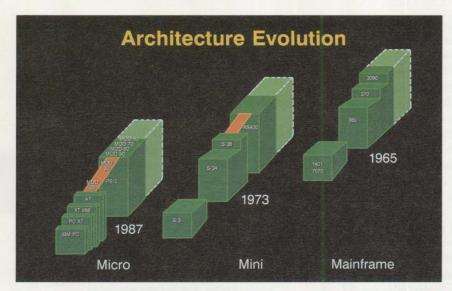

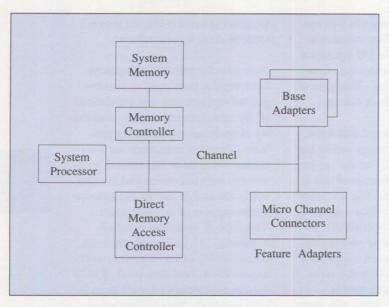

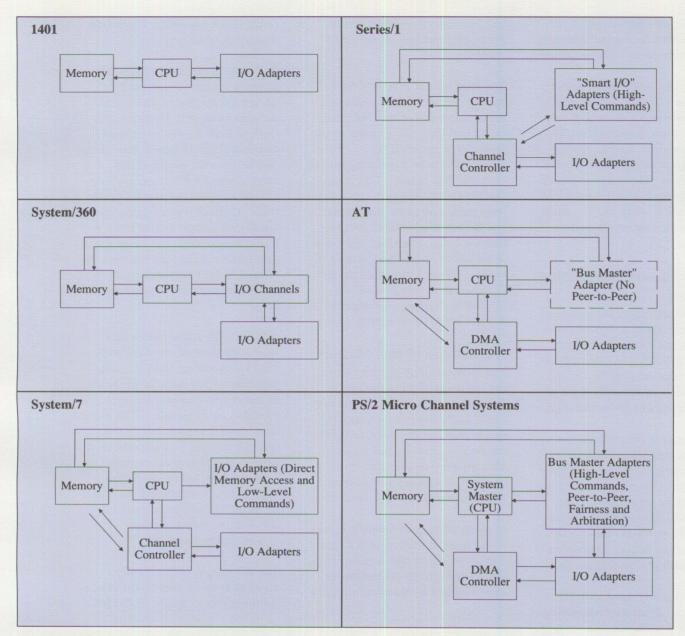

In 1987, IBM accomplished another evolution by making the transition from the single-task, single-thread environment of the AT computer multitasking PS/2 system with Micro Channel architecture, while also providing a compatible environment for single-thread applications in the Models 25, 30, and 30 286 (Figure 2).

Each time, the needs of the future could not be met by modifications of the past, and a new generation of systems was defined.

Figure 1. Approximate Performance Comparison

Figure 2. Architecture Evolution

## Single-Tasking Versus Multitasking

In a single-task system, each operation occurs in sequence. Much the way a person can assemble a bicycle in sequential steps (first the handlebars, then the wheels, and finally the seat), so can tasks in a computer be manually performed, in sequence, by one user. The time to complete the entire sequence of operations is the sum of the times required for each task.

In the single-tasking environment, operations to the disk require a delay in processing. This is because accessing the disk, talking to the I/O, or operating the processor are each sequential operations. During the seek latency period of the file, the processor is unused.

The command to operate the disk and the time to process the data are typically short compared to the time required for the disk to respond. All other tasks wait for the first to complete, and delays accumulate from all tasks. For this reason, the latency of the disk file in a single-

tasking machine is a significant factor in the performance of the system as a whole.

Single-tasking has the advantage of simplicity in system design, yielding low-cost systems. But it is not the way most of us work or think – most of us multitask in both our work and our thinking.

In a factory, for example, multiple tasks would be performed concurrently to maximize productivity. Operations would be done simultaneously whenever possible. The time to complete the entire operation is then little more than the time required to complete the longest task.

The difference between single-tasking and multitasking involves this concept of concurrency, which means that, in multitasking, I/O operations can occur at the same time rather than sequentially.

When the system is shared among a number of users or a number of tasks, it becomes much more viable economically, and the organization that it supports becomes more productive.

## **Technology Trends**

Looking at the trend of technological advances from 1981 until today (Figure 3), we see a 5-to-1 improvement in the clock rate of the processor. The efficiency of the execution unit for real-mode instructions has improved by a factor of 4-to-1. We have seen about a 20-to-1 improvement in the processing power of the system. I/O devices that depend on the processor to support data movement have increased their data transfer requirement (called throughput) a great deal more. Displays have moved from 128,000 picture elements to more than 6 million. Direct-access storage devices moved from the 50,000 bytes-per-second transfer rate of diskette media to the enhanced small device interface (ESDI) in excess of 1.25 million bytes per second, and most recently to the small computer system interface (SCSI), transferring data at approximately 5 million bytes-per-second.

Communications has undergone the most dramatic transition in performance. Going from 300-baud modems, which were a luxury in 1981, to 16-million-bit-per-second local area networks has produced a 53,000-to-1 improvement. I/O devices are now moving data much more quickly.

## The Need for Change

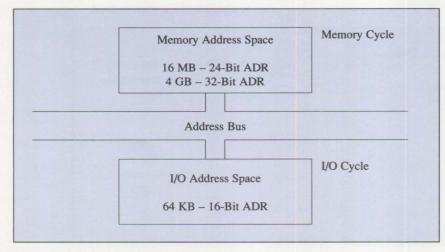

The objectives for the IBM Personal Computer were to provide an address space of 1 million bytes and a path for the transfer of one character at a time. These machines could do only single transfers of data, which typically depended on the processor for every transfer. The AT was extended to allow a 16-

megabyte address space defined by a 24-bit address bus and a 16-bit data path. The AT computer also introduced the "string mov" operation capability of the 286 processor that allowed the rapid movement of blocks of data to and from file devices.

Single-tasking machines operate their I/O interfaces one at a time, so the requirement for the bus throughput is no greater than the fastest I/O device. But in multitasking, where tasks and I/O devices operate at the same time, throughput requirements are higher.

IBM did not consider the AT bus to be a suitable base upon which to define a family of multitasking and multiuser systems. When taken together, the limitations of the AT's interface to I/O implied a number of concerns about the design of any system that supported compatibility with the cards designed for the PC, PC XTTM, and AT computers. In 1984 these limitations may have been viewed as advantages for the single-task, single-thread environment; indeed, the AT is still a qualified bus for those operations. But in the multitasking environment, there were limitations in several areas:

Addressing – 24 bits: The AT implemented only 24 address lines for memory, so only 16 MB of storage can be addressed on the bus.

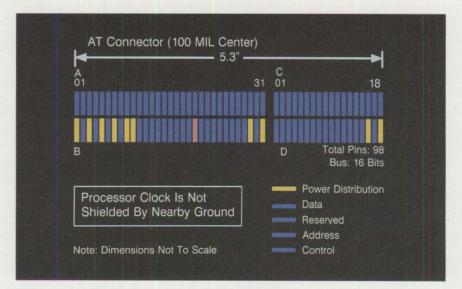

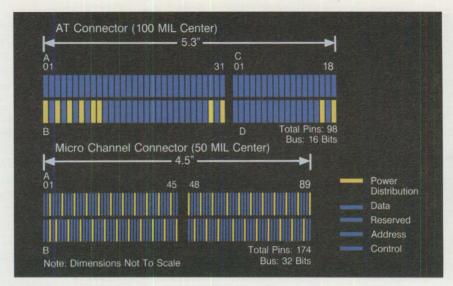

Data Bus – 16 bits: The AT data bus is only 16 bits wide, limiting the throughput, when existing cards are installed, to 5.3 MB instantaneously and about 3.5 MB continuously.

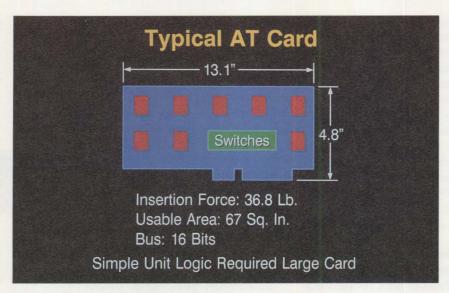

Connector Design and Insertion Force: The PC and AT connector design is a legacy from the mid1970s' design of the IBM 5140, with insertion and removal forces approaching 40 pounds. Good design practice would keep the insertion and removal forces below 40 pounds for assembly and service operations by humans or robots. Extending the AT connector to have sufficient pins for a 32-bit interface would yield forces closer to 65 pounds during either insertion or removal. This would expose the system board to excessive stress during assembly and service operations.

Direct Memory Access (DMA)

Utilization: The DMA channels,

used as alternate paths between I/O

and memory, were permanently assigned to devices early in the development of PC and PC XT

machines. The AT design added

more channels at a wider width, but

DOS cannot use them. As a result,

the DMA controller is assigned to

I/O that is slow by today's standards. The processor does all the work to move data between memory and I/O.

**Electromagnetic Compatibility** (EMC): The radiation of electromagnetic energy outside the system and susceptibility to external interference are not just problems to be solved by the manufacturer, but issues of data quality and validity for the user. When energy is radiated from a data signal, the data levels are reduced, and may oscillate below valid levels. The signals then become vulnerable to outside interference. Shielding the cabinet is expensive, and only contains the energy within the cabinet. It does not limit the electromagnetic incompatibilities between cards or devices within the cabinet. EMC problems increase, as the square of the data rates increases, on the I/O bus.

|                                                      | 1981            | Today           | Ratio*   |  |  |

|------------------------------------------------------|-----------------|-----------------|----------|--|--|

| Processors                                           | 8088            | 80386           | 4:1      |  |  |

| Instruction Unit Efficiency<br>Clock MHz             | 4.8             | 25              | 5:1      |  |  |

| Maximum Memory Size                                  | 2 <sup>20</sup> | 2 <sup>32</sup> | 4000:1   |  |  |

| Data Bus                                             | 8               | 32              | 4:1      |  |  |

| Performance                                          | 300 KIPS        | 6 MIPS          | 20:1     |  |  |

| Display (Mbits/screen)                               | 0.128           | 6.291           | 50:1     |  |  |

| DASD (MBytes/sec transfer rate)                      | 0.050           | 1.250           | 25:1     |  |  |

| Printer (Bytes/sec)                                  | 80              | 5000            | 63:1     |  |  |

| Communications (Bits/sec)                            | 300             | 16,000,000      | 53,000:1 |  |  |

| * Approximate performance ratios for comparison only |                 |                 |          |  |  |

Figure 3. Technology Trends

Figure 4. Typical AT Card

Faster I/O demands a solution to this problem.

Configuration Conflicts: Because the system resources required to operate a card are either fixed in the design, or very limited in selectability by switches, and because most PC, PC XT and AT designs decode only 10 of the 16 I/O address lines, many conflicting situations exist with the configuration of systems that use these cards. For example, because PC, XT, and AT interrupts cannot be shared between two device adapters, and because compatible software typically recognizes only two communications interrupts, a maximum of two cards that drive the interrupt request lines can be installed. If a user wishes to install a binary synchronous adapter, one asynchronous card must be removed. If a synchronous data link control (SDLC) adapter is installed, the binary synchronous card must be removed. This limits the number of solutions that the user can define.

**Logic-ground Isolation:** Personal computer cards have only three ground pins to connect the logic

ground on the card to the system board ground. If a card pulls sufficient current from the system, the logic-ground reference on the card can rise as high as one-half volt above the system ground. Data transfer between the cards and the system can then yield misinterpretations in data level, and invalid transfers can occur. Therefore, if a branch address is sought at the instant that a noise spike or static discharge pulse from elsewhere in a network is added to the DC offset. and if the branch is taken, the system can lose its place in memory and execute variables or instructions out of order. The user is locked out of the keyboard. This places a requirement on any new architecture to solve this problem.

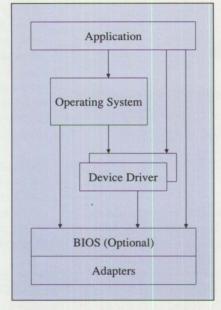

Processor Workload: Affecting performance the most, however, is the loading of a great deal of the I/O-to-memory transfer burden onto the processor by simple PC adapter cards that implement little hardware and use the processor to perform much of the interface logic through the basic input/output system (BIOS) or application drivers. This

practice may be permissible in a single-tasking machine because the processor is not used elsewhere in a single-tasking system. But in a multitasking machine, such I/O designs can decrease performance because they tie up the processor when it could be dedicated to tasks and the operating system.

The limitations that compatibility to PC, XT, and AT cards would impose on a system outweigh the relatively infrequent need to propagate old cards from an old system to a new system.

## **Getting Technical**

### **Mechanical Considerations:**

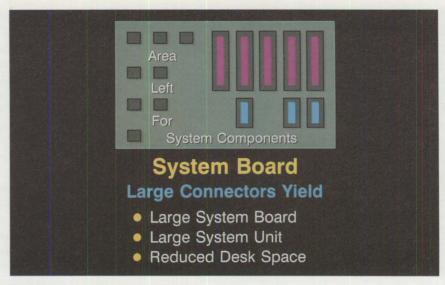

Taking a closer look at the system design limitations just outlined, consider the typical AT card (Figure 4). When populated with early 1980svintage unit logic components and switches, a large card was required to perform even the simplest I/O adapter function. The personal computer 8-bit card connector consumed approximately 3 inches, or one-fourth the width of the PC system board. The AT extended the connector to slightly less than half the width of the AT system board, and tightened the mechanical reference and tolerance control in the placement of the copper tabs on the cards and in the spring contacts in the system unit connector. The force to insert or remove the card grew close to the 40-pound maximum recommended force. Large connectors consumed a large fraction of the limited system board area, yielding a large system board when the processor, memory and I/O adapter logic were added to the layout (Figure 5). This caused the system unit to consume more area and a larger fraction of the already crowded desk. And, from a manufacturing point of view, the larger

AT cards may yield unusable waste when they are cut from the standard 12-inch by 24-inch raw stock.

It became obvious that a smaller system overall, with smaller components that consumed less desk space, would be an advantage to the customer.

While this requirement may imply more development expense and time for adapter card designers to implement in a smaller space, that expense is typically amortized over tens of thousands of cards. Indeed, the techniques typically employed to implement in a small space — large-scale integration, surface-mount technology, automated manufacturing systems and computer-aided design — yield card designs that are often less expensive to duplicate and more reliable.

The developer's challenge is not the customer's problem. To the customer, small cards are better, if a smaller footprint is needed.

## **Electromagnetic Compatibility:**

Let's unfold a card to visualize the EMC design problems of AT cards and the systems that they support. Looking specifically at both sides of the connector interface at once (Figure 6), and highlighting the radio frequency ground signals, one can see that most of the signals do not have the close proximity of a radio frequency shield. In fact, the processor clock was placed midway between two radio frequency grounds. This was acceptable when the card format was designed in 1978 for the 5140 machine, from which the PC was derived. That system had a slow clock by today's standards.

Today, however, clock rates are much faster, data transfers are much faster, and I/O devices move much

Figure 5. System Board Layout

more data in a shorter time. The result is electromagnetic incompatibility with other nearby equipment and internal interference between elements within the system cabinet. The security of the data moving through the machine can even be compromised by others.

To prolong the life of the PC bus and allow extension to the 16-bit AT interface, IBM introduced "single-point ground" power systems, conductive plating of the power supply, frames and covers, and internal ground planes in PC XT and later machines. But those measures become much more costly and less effective as the speed of the systems increase. To understand why, let's go back to basic electricity.

Many of us, in our youth, built electromagnets by winding turns of wire

Figure 6. AT Connector

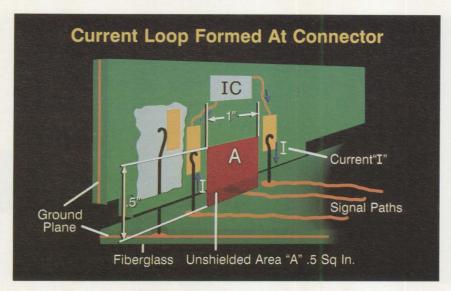

Figure 7. Current Loop Formed at Connector

around an iron nail or spike. We found that as we increased the area inside of loops by creating more turns or accumulating area, the magnetism increased. Also, when we increased the current by adding more batteries, we increased the magnetism.

This is true for a fixed distance from the radiating element. The electrostatic portion of the radio wave is proportional to the area inside of a loop times the current that flows through that loop, and if it is an alternating current or radio frequency, times the square of that frequency.

The data transitions on the computer bus are currents that alternate at very high frequencies and thus have the potential to transmit energy (or receive energy) as interference with other equipment either inside or outside the box.

Look at the card connector in three dimensions (Figure 7). An unshielded area is formed where the current flows on spring tabs to a card, through the card, and then returns over spring tabs back to the system. Everywhere else in the system – on the cards and on the system board – there is ground shielding, except at this one point.

Using a radio frequency quiet room, IBM engineers found that the card connector on the system board was the principal source of radiation from the I/O bus when the interface between I/O and the system was active. This unshielded area was considerably larger in the PC, PC XT and AT implementations – about one-half square inch. In all these implementations, the ground system on the cards is connected to the ground system or shield on the outside of the case.

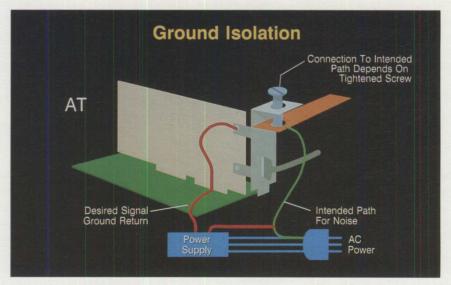

However, this meant that when the limited number of grounds in the AT was inadequate to sink a current back to the power supply – for example, if the card bracket retaining screw was not tightened firmly – the currents could flow back through the metal system frame (Figure 8), which is the intended path for containing noise in the PC, PC XT, or AT system. Current re-

turning to the power supply could actually flow out over the shields of cables and back through the AC power mains, forming a gigantic loop called a "ground loop." Even with a small current flowing, this would create a large loop area and very large radio signal. This is called "conducted electromagnetic interference."

The ground mechanism used in the PC, PC XT, and AT also makes the system susceptible to noise from outside the system. Energy from equipment connected to the system could be coupled through the shield system. If the retaining screw was not tightened, the current could sink through the card and through the system rather than safely returning to the AC mains. Typically, this would manifest itself as a data error when static discharges, perhaps from someone touching adjacent equipment in a low-humidity environment. This data error would not necessarily occur in the equipment that the person touched. In extreme cases, a lightning strike could actually destroy local area network (LAN) cards or communications cards where the screw is not tightened.

## **Requests for Processor Attention:**

The AT system unit typically had a few devices connected to it, enough for one user and a few applications. It was designed to support simple file serving and very limited multitasking configurations for only one user. Yet, increasingly, we are using desktop systems as small mainframes. With multiple users often attached through networks, and multiple tasks per user, these systems often perform the same duties as the mainframe machine in a raised floor environment.

In a mainframe environment, each user or each task may have a favorite piece of I/O that it operates. For example, if two tasks were to talk to the same printer at the same time, the text would be mixed between the two, and we would see gibberish printed on the paper. Obviously, BIOS or an operating system would prohibit this error by sequentially scheduling access to the printer - but this would result in one task delaying another. Still another task might require a special printer or plotter for output. This is one of the reasons that the total amount of I/O and types of I/O attached to a system can grow when multitasking and multiuser operating systems are introduced.

To receive requests for attention for I/O devices, the AT has 11 interrupt request lines. These signals on the AT card interface cannot be shared between device adapters. This means only 11 different interrupting devices can be configured in an AT system.

In a multitasking system such as the Personal System/2 Model 80, where there are eight connectors and six adapters on every system board, we are talking about 14 functions. Here, eleven interrupts would be insufficient. A redefinition in the AT interface with at least 14 interrupts would be required to solve this problem alone.

Why can't interrupt requests from PC or AT cards be shared? There are two reasons. First, let's understand how the edge-triggered interrupt request mechanism works in systems that support personal computer cards. A transition from low to high on a PC bus interrupt request line is interpreted by the system as a request for attention by an I/O adapter. To create this transi-

tion, the request line is first driven low, then high. The drivers on adapter cards may be inactive at other times, but they, too must drive low, then high to get the transition.

A driver with a pull-down transistor and a pull-up transistor is required to drive the interrupt request line quickly from one state to the other. A bipolar or a tri-state type of driver may be used, as long as the high state immediately follows the low state. First the bottom transistor becomes active, "on" like a switch. Then it turns off as the top transistor becomes active, causing the transition.

Assume two such drivers on separate adapter cards are connected to the same interrupt request line. Eventually one adapter will make a transition. While the first adapter is still driving the line high, a second adapter drives the line low as it begins to present an interrupt. This type of situation is much more likely when multiple I/O adapters are operated simultaneously by concurrent tasks in a multitasking or multiuser situation.

During the overlap of the two simultaneous requests, a temporary short circuit across the power supply is created. This situation would also occur if one of the drivers were an open collector driver, as used in level-sensitive interrupt systems. This may cause either one or both of two problems:

- 1) The interrupt-request line may not achieve a valid level as the two transistors fight to pull it both low and high at the same time. The interrupt may thus be lost to the system. A lost interrupt can be a catastrophe in a multitasking operating system and may require a reset and restart of the system hardware, to regain synchronism between the I/O and the system.

- 2) With time, perhaps milliseconds, or perhaps much longer, the drivers may be damaged and the lifetime of the components would be shortened, requiring the replacement of a card or a system board that contains the driver.

A resistor between the card and the bus could limit the current, but

Figure 8. Ground Isolation

would then decrease the noise margin for the logic and aggravate the noise problems in the system.

Schemes have been devised to inhibit one card driver, if an edge is detected from another interrupt driver on the same request line. They may work when two interrupts are unlikely at the same instant in time, but they are also sensitive to noise spikes on the interrupt-request lines. The noise spikes may be detected by many or all such circuits, inhibiting some or all adapters. No interrupt is present, none will be serviced, and the system can hang.

In the opinion of IBM engineers, mixing the drivers on existing PC, PC XT, and AT cards, or mixing existing interrupt drivers with new cards that employ only open-collector drivers, could be detrimental to both data and system integrity, as well as to the reliability of the system. Consequently, we concluded that any system that mixed levelsensitive and edge-triggered interrupts on the same request line may be unreliable for users and very difficult and potentially expensive to support under warranty and service agreements. Even if all the possible warnings are given, normal human errors would still result in unreliable configurations.

A satisfactory design point could be achieved only if all existing PC, PC XT, and AT cards were excluded from an interrupt-sharing mechanism and were defined with an all open-collector, level-sensitive interrupt sharing system. One of the greatest advantages of such a system would be that it does not support existing PC, PC XT, and AT cards. Given that all new cards would have to be designed, and a new system would have to be designed to support them, the best

technical solution could be chosen without compromise for PC, PC XT, and AT card support.

## Requirements of the Multitasking Environment

Many other limitations imposed by support of PC, PC XT, and AT card designs could be fixed as well.

The Single-Tasking Environment: One limitation is the excessive dependency of most I/O devices on the processor for data movement and control. The displays, all the files, most communications, most local area networks, and printers are

The best technical solution could be chosen without compromise.

dependent upon the AT processor to move data. An 80386™ processor, with all of its complexity and sophistication, is reduced, for many of the operations in the machine, to simply moving data and operating I/O devices. In a single-tasking environment, it may be acceptable to operate each I/O device in sequence and to dedicate the processor to support that device. Such a system may even look very favorable in single-tasking benchmarks. The I/O adapters can be relatively simple and inexpensive to build.

## The Multitasking Environment: However, in a multitasking environ-

ment, all of the interrupt-driven I/O adapters tax the system performance before the applications and operating system instructions can be exe-

cuted. Before PS/2 systems with Micro Channel architecture were developed, the solution to supporting fast, processor-dependent I/O was typically to build faster processors and faster memory systems – a very cost-ineffective solution.

For example, let's look at what happened with printers. In 1981, an 80character-per-second printer was considered cost-effective and adequate for a personal computer environment. Today, we have moved to laser printers that can transfer 5,000 bytes per second in graphics mode for desktop publishing. In a DOS environment, this original load of 80 bytes per second on the processor was rather modest. DOS applications consume about 200 instructions to service the interrupt, and to move a byte to the printer. These instructions save the state of the machine, do the housekeeping required to figure where the next print character will come from, operate the interface, and resume processing at the place that it was prior to the interrupt. This requires one interrupt per character in the existing printer adapter. The asynchronous and binary communications adapters, and many other adapters for the personal computer, are of this same basic design, with one character transfer per interrupt. This means a load, under DOS, of 16,000 instructions per second. This is a modest load, because there are 300,000 instructions per second available in the PC.

The same function today for a single interrupt is a load of 5,000 characters per second, times 200 instructions per character, or 1 million instructions per second – about all of the capability of a 80286<sup>TM</sup> processor, running at 10 MHz.

Under a multitasking operating system, however, the environment is much much larger and more complex; it can take 1,000 instructions to service the interrupt. This means a 5,000 character-per-second printer will use 5 million instructions per second. That is approximately all of the capability of a 25 MHz, zerowait-state 80386-based system. So a \$10,000 computer is tied up 100 percent of the time when the printer is operating.

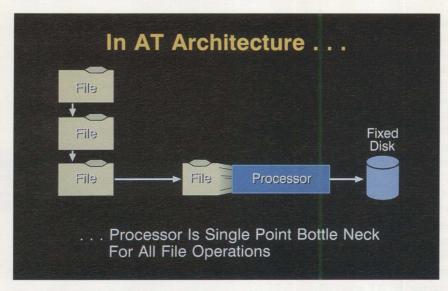

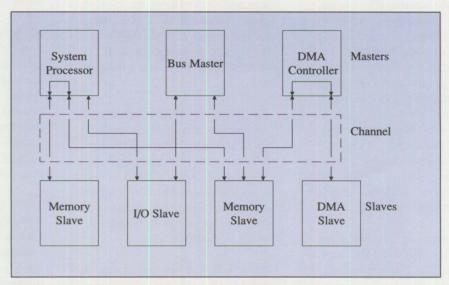

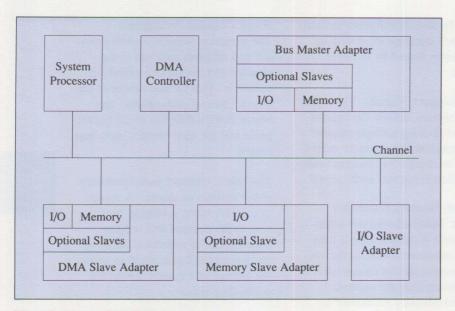

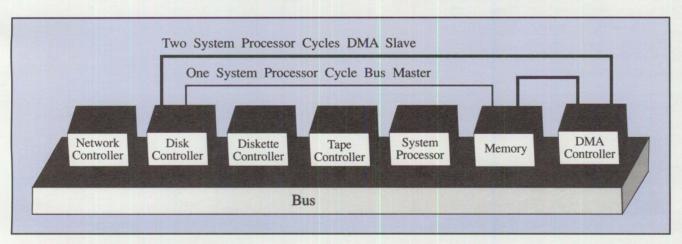

Processor Bottleneck: A requirement of concurrency is that multiple devices can operate at the same time. If each device depends 100 percent on the processor, then two devices cannot operate at the same time at full performance. One solution to the burden on the processor is to offload that burden to a direct memory access (DMA) controller. Then multiple channels of the DMA controller can each simultaneously support an I/O adapter while the tasks and operating system get maximum access to the processor. This would be the ideal solution. Unfortunately, it is not possible with the AT bus and may be severely limited in a system that supports AT cards.

When the personal computer evolved in 1981 from the original mid-1970s Datamaster product, it implemented a DMA control function. In 1981, that was considered an advantage over competitive designs. The diskette moving data at 50,000 transfers per second was the fastest I/O device. It was assigned to DMA channel 2.

Cards using the DMA controller used the same drivers as interrupt request drivers and consequently could not share a DMA request line.

The connection to the DMA request and acknowledge signals on the PC

bus was also hardwired on the card, to assigned DMA channels. The result was that each new DMA adapter design would require that a new DMA channel be defined. Otherwise, an installer would need to understand which card designs, which DMA channels, and which configurations to avoid, to protect the drivers.

The SDLC adapter was similarly assigned to DMA channel 1. Dummyread transfers from memory using DMA channel 0 did the refresh operations. This left only DMA channel 3 available for further implementations. When the PC XT was intro-

Multiple devices can operate at the same time.

duced, DMA channel 3 became the interface for the fixed disk. The PC Network was defined to allow the cost-effective sharing of fixed-disk storage.

It may seem as though a rule has been violated here, where the PC Network and fixed disk share a DMA request line. To avoid problems, the PC Network BIOS turned off the fixed disk when the network was active, preventing two drivers from simultaneous activity on the same line. The DMA request was sequentially shared, and file and network activity became mutually exclusive. This was permissible. Remember that the PC XT was a single-tasking design, like its prede-

cessors, and did not support application concurrency.

When the AT computer was introduced, it could offer concurrency between the fixed disk and PC

Network by moving the fixed disk adapter to the processor and using the "string mov" capability of the 80286 processor. The display controller, asynchronous communications, printers, and bisynchronous communications were getting faster and were an increasing burden, but the overhead to support them was still within the capability of the faster 80286 processor.

Networks evolved connections to other networks called "gateways" or "bridges." This implied two network functions in one system. The mechanism of having the PC Network BIOS turn off another device would not work when the other device was the PC Network itself. Either more DMA channels would have to be defined, or the network responsibility would have to be moved to the processor, where the attention could be moved between I/O adapters with interrupts, albeit with considerable software overhead.

The AT computer did both. It defined three new 16-bit DMA channels and moved networks to the processor along with second and third fixed-disk devices, using the power of the processor to support I/O. Yet the processor was now the single element that could move data for most I/O. As long as faster processors and memory systems were cost-effective, the operating system could schedule concurrent tasks as sequential tasks, and the speed of the processor would make up for the fact that all I/O would need to wait in line for the one processor (Figure 9). The AT also removed the memory refresh from DMA

Figure 9. In AT Architecture

channel 0. This left four DMA channels free for use by I/O devices. But for the large part, none of the new channels has been used. Why?

Originally intended to support only sector-oriented files, the new 16-bit channels were incompatible with DOS. The reason is that the DOS file system is byte oriented, and it can place a buffer of data anywhere on an 8-bit boundary in storage. It can create buffers that are even or odd, and they can end or start on even or odd boundaries.

The Intel 8237 DMA module was implemented to count words, not bytes, on the AT and would only allow DMA transfers from even boundaries. This is a characteristic problem of many systems, derived from the AT architecture, that implement the 16-bit DMA ports.

DMA channels 5, 6, and 7, if implemented in those systems, are incompatible with DOS because they cannot place a buffer on any given boundary as defined by the operating system. DMA channel 0, which

was freed up in the AT because refresh responsibilities went to dedicated logic, has not been used. Perhaps this is because card designs would have to be specific to the AT, and the AT only, and could not operate on personal computer designs.

To summarize these points, the AT system has three active, or usable, DMA ports for which there exists a business case to build cards that can also be used in the PC and PC XT implementations. This limitation on the ability to move data transfer responsibility from the processor is a major limiting factor in the concurrent environment of a multitasking operating system such as IBM Operating System/2<sup>TM</sup> (OS/2).

## **All Things Change**

The Complete System: In a concurrent environment, typically a number of applications are operating at the same time. This is the intent of a multitasking operating system – to do more than one thing at a time. It is what can make the Personal System/2 more productive,

as much as five times more productive, than previous machines.

We have accepted that a new operating system is required to run these multiple applications concurrently. We have accepted that new processors are required to do multitasking and multiuser operations. The 80286, 80386 and 80486™ processors allow the efficient switching of tasks because they have hardware dedicated for those functions.

Multiple tasks create simultaneous activity to a number of I/O devices. Each application may operate a unique device; the number of devices increases. More types of devices are connected, and the amount of data traffic, or throughput, to and from these devices expands. The number of requests per second for processor attention, interrupts from these devices, grows as well.

The path between I/O and memory, the channel, must be redesigned to reflect the change. Every element of the system – adapters, processor, operating system, applications and the channel – must be redesigned.

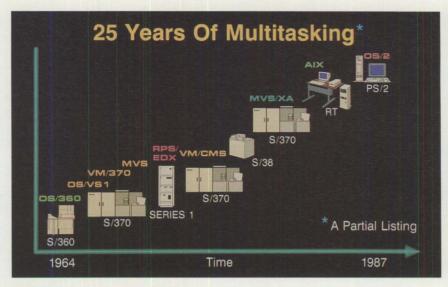

These characteristics of concurrent systems are not new. We have seen them in every multitasking and multiuser system that IBM has produced since 1964 (Figure 10).

OS/2 is not the first operating system that we have used for multitasking. In fact, multitasking is at least 25 years old. The problems that micro system designers are finding today are often similar to problems that minicomputer designers saw 15 years ago and mainframe designers saw a decade before that. What is new is that the rules have changed and innovative concepts have been applied. Logic can now be more complex; it is faster, less expensive,

and far more reliable. The processors are more powerful. Memory is far less expensive. We can be creative and use our experience as well.

Video Graphics: The reason that the change can occur now is technology. Figure 11 shows a comparison between an Enhanced Graphics Adapter (EGA) card that was designed around 1984, and a Video Graphics Array (VGA) chip that replaces that function. In fact, the chip package consumes almost 80 percent of the chip's area; only 20 percent of that component is the actual VGA silicon chip. The VGA chip has almost twice the function of the EGA card.

The display function is one of the most frequently upgraded features in a system. Unfortunately, another limitation of systems designed for AT cards is that the investment in the display adapter will probably be discarded within a few years. Why?

When the EGA card was installed, the monochrome and color cards were removed. The original investment was lost as the new EGA function made the old cards obsolete. The user paid again for the monochrome and color functions because half of the EGA logic was dedicated to reproducing the old display modes. AT users upgraded to VGA and paid again for the EGA display function. Each time, approximately one-half of the investment in the new card was to replace the function just removed. Micro Channel architecture puts an end to this loss of investment, as we will see later.

File Servers: A file server is a potential single point of failure for what is, in effect, a multiuser system. It operates I/O concurrently, and is an example of the type of sys-

Figure 10. 25 Years of Multitasking

tem that needs Micro Channel architecture today.

The server will probably grow in its throughput and configuration as more I/O devices and users are connected to the LAN. The desktop will use Micro Channel architecture to run multiple tasks at the user station and to allow network asset management or control of the network configuration. Network asset man-

agement allows an electronic census of installed options, prior to distribution of applications, that may be I/O device-dependent. Additionally, the network manager can cycle adapter functions in the LAN stations on and off to accommodate application I/O needs and remote diagnostics. These functions can be supported by specialized software applications in all the stations and the network

Figure 11. Video Graphics Technology

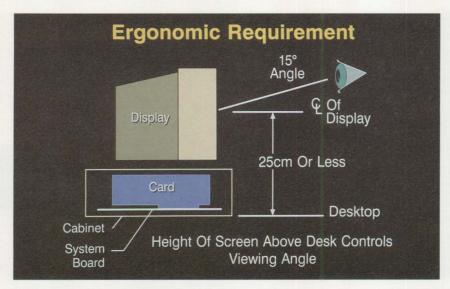

Figure 12. Ergonomic Requirement

manager or by the operating system itself.

## **A New Foundation**

An architecture for the 1990s has 32 bits for both I/O and memory, can be expanded to wider data bus widths, allows higher throughput, and still supports the 80286 and 80386SX<sup>TM</sup> and other processors with 16-bit interfaces. It is independent of both the processor and operating system. Specifically, IBM's intention was to create a foundation for a broad range of machines, with an architecture that could support single or multiple bus system architectures (for example, the PS/2 Model 70-A21).

# EMC and Signal Quality Characteristics at Higher Speeds: The channel would be expandable to wider data paths and faster throughput. It would allow advanced error detection, recovery and diagnostics.

To support the faster data transfer, the data quality must be predictable

and not lose integrity through radiation.

## **Automatic Configurability:**

Complex multitasking and multiuser systems would need automatic setup to support conflict-free configuration of multiple I/O interfaces. If IBM had kept switches, resolution of conflicts in configuration would have been very complex indeed. Assume that a system had eight sockets; then one could install as many as eight cards of the same design. That would mean eight I/O address ranges for the adapter control registers. Three switches are needed to select one of eight options.

To provide enough DMA ports to move processor-dependent I/O off the processor, four switches would be required to select one of 15 DMA ports. There are 16 address locations, for "on-card ROM," used for power-on self-test (POST) and BIOS extension – another four switches. Without interrupt sharing, three switches would duplicate the seven "PC" interrupts, but four would be needed to select one of all

11 non-shared AT interrupts. This is a total of 15 switches for each adapter:

- 3 I/O addresses

- 4 DMA channels

- 4 On-card ROM/RAM addresses

3 or 4 1 of 11 interrupts

15 Switches

Designing for the worst case, with six adapters defined on the system board and four adapters per combo card in each socket, as many as 570 switches would be required for foolproof, switchless set-up on the AT computer:

(6 x 15) System board

4 x 15 Each card (combo)

x 8 Cards

570 Switches

This is beyond the average person's clerical ability and patience, but well within the capability of the computer. Programmable Option Select (POS) can replace 32 equivalent switches (expandable to 256,000 switches) and turns what would have been an ordeal for a human into a minor task for the computer.

## **Smaller Footprint for Desktop:**

The smaller card can yield a smaller system, and also can assist in the usability of the system. In several countries, industry regulations and public laws define certain ergonomic characteristics of data entry terminals and personal systems. One part of these requirements is the placement of the centerline of the display no more than 25 centimeters above the desktop to reduce glare and neck-muscle fatigue (Figure 12). With the common practice of pancake-like stacking of the display

and system unit to conserve desk space, the designer has a choice of a smaller screen or a smaller card.

Micro Channel cards are 3.5 inches high, the same height as the connectors to peripherals on the rear bracket of PC, PC XT, and AT cards. PS/2 systems, therefore, maintain connection to most AT peripherals while permitting larger-size displays to be installed where ergonomics is a consideration.

However, Micro Channel architecture does not restrict the card height to 3.5 inches. While this is a specification for existing PS/2 computers, systems with capability for larger cards are feasible.

Increased Flexibility for Interrupt Structure: The AT interrupt structure had to be improved. Micro Channel systems support up to 256 adapters to share a common interrupt-request line. With 11 compatible interrupt-request lines, this allows more than 2,800 device adapters to be installed in a system:

256 x 11 = 2816 Interrupting adapters

Certainly this is enough for an advanced microsystem; it is also enough for minicomputers and mainframes as well.

The I/O device's request for attention is interlocked with the system's response to the request. Lost or spurious interrupts can be detected, and diagnostics can locate defective adapters and/or interrupt routines more easily.

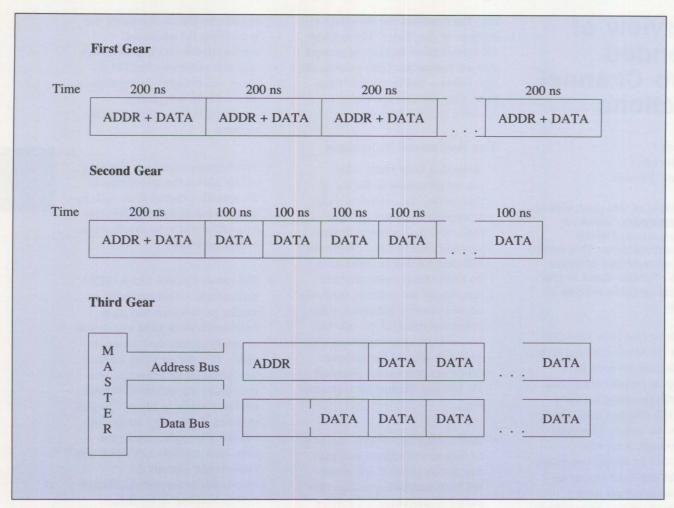

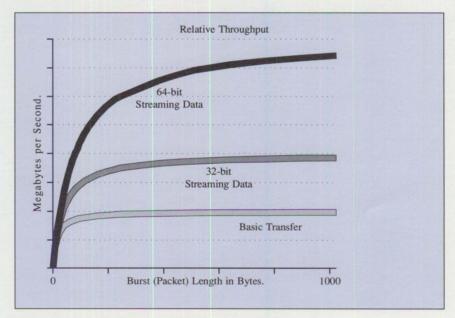

**Increased Data Rates:** The Micro Channel interface supports a base burst speed, in its initial definition, of 20 million byte transfers per sec-

ond. Even other microcomputer manufacturers specify the AT bus at no greater than 3.5 million byte transfers per second. There have been implementations of the Micro Channel standard that move data at a rate of approximately 17 million byte transfers per second, or on the order of four times the capability of the AT bus.

IBM has defined all the timing, loading, capacitance, and electromagnetic characteristics of the system so that designers building cards, systems, and applications to the Micro Channel specification can define equipment that can be integrated properly.

The performance of the Micro Channel bus can be extended well beyond its present level. We have preserved the ability to extend Micro Channel functionality, in a compatible fashion, so that cards developed today to Micro Channel specifications can run on Micro Channel systems tomorrow.

Expanded DMA and Bus Masters for Concurrency: We have expanded the DMA and bus master capability so that a number of devices can be intelligent and no longer be dependent upon the processor. Up to 15 devices can be supported independently of the processor.

## **Building In the Future**

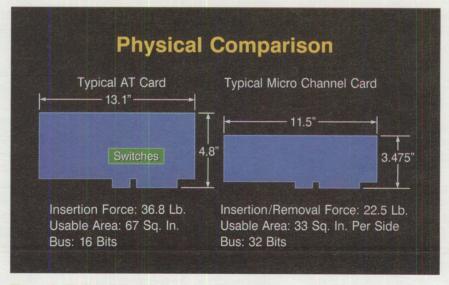

To see how this has been done, look at a physical comparison of an AT card and a Micro Channel card (Figure 13). On initial inspection, the Micro Channel card is physically smaller. This allows for a smaller system. However, the card format is optimized for surface-mount technology (SMT). The connector dimensions match the tab spacing on SMT components, facilitating wiring of the card.

SMT allows an increase in the vertical and horizontal densities, each by a factor of 2-to-1, for an overall aerial density improvement of 4-to-1. Surface mounting also allows the implementation of components on both sides of the board for a total

Figure 13. Physical Comparison

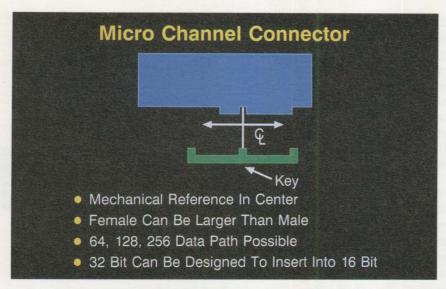

Figure 14. Micro Channel Connector

improvement of 8-to-1 in component density.

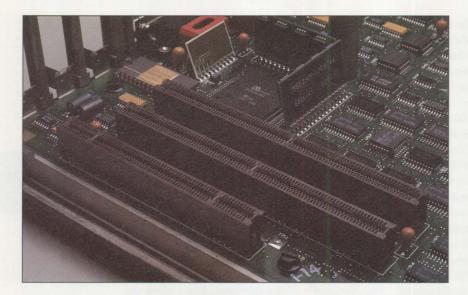

The Micro Channel connector uniquely references mechanical alignment from a keyway centered in the connector, allowing tighter control of mechanical tolerances (Figure 14). When inserted in a 32bit socket, neither end of a 16-bit male connector is in contact with the end of the female socket. Likewise, a 16- or 32-bit card could be inserted into a 64-bit or larger socket and align perfectly. A 32-bit card has been designed that leaves clearance at the end bulkhead position for a 16-bit connector. Therefore, this 32-bit design can be used in 16- or 32-bit or larger systems. A single design can be made for all systems and still be capable of 32bit throughput.

The spacings on the connector have been cut to one-half of the spacings used on the AT connector. A Micro Channel 16-bit socket is approximately the same size as a PC 8-bit socket. The Micro Channel 32-bit connector is actually smaller than the AT 16-bit connector. This fol-

lows the trend of other components in the system, such as processors that have grown in power from the 8-bit interface of the 8088 processor to the 16-bit 80286 and the 32-bit 80386 without growing significantly in physical size.

The number of signals in the connector has been doubled, and the insertion and removal forces have been cut almost in half. This is extremely important because in manufacturing and service situations, had the length of the connector increased or more tabs been defined, either the insertion force or removal force would have exceeded 40 pounds.

We have designed out the electromagnetic compatibility problems of the AT connector. One can see by the pattern in the lower half of Figure 15 that each signal in the Micro Channel bus is situated between a ground, across from a ground, or adjacent to a ground signal. There is a radio frequency shield on every fourth pin. On the opposite side of the connector, the pattern is identical but offset by two pin spacings. The area between the closest shield and a signal is thereby diminished significantly.

The loop area of the Micro Channel bus is one-twenty-eighth of that for the AT bus. The signal transitions can then increase in frequency, by a factor of the square root of 28, or approximately five times (Figure 16). This has been experimentally verified outside of IBM – studies of the Micro Channel bus have shown a cutoff frequency above 80 MHz. Studies of the AT bus have shown a cut-off frequency of approximately 16 MHz, or again the same factor of 5-to-1.

Micro Channel cards now make positive ground contact with an intended path for ground return in the AC power lines. This occurs when fingers attached to the shield bracket on the back of the connector make direct contact on insertion.

The card itself is isolated electrically, so that currents on the card cannot escape that card through the shield system and must return directly to the ground of the power supply. External static discharge currents will be returned through the intended path to the AC power system, not through the card itself.

More DMA: Remember the problems with DMA utilization on AT cards? Only one channel on the AT was usable. The DMA channels that were added to the AT were not compatible with DOS. Micro Channel architecture has solved these problems. Instead of three usable DMA channels supporting just three permanently assigned devices, we can support up to 15 devices with no fixed assignments.

All channels are compatible with DOS. Micro Channel DMA control-

lers can handle the even transfers (as does the AT) as well as all data formats involving odd transfers (those beginning or ending on even and odd boundaries). The DMA controller automatically adjusts the address boundaries upon transfer.

Processor-dependent I/O can now move to DMA because usable DMA channels are available; no assignments are fixed. Data can move faster. Single-transfer operations are employed for compatibility with the AT operations, but we also defined a burst capability in the Micro Channel interface that allows 312 transfers to occur with the same arbitration overhead that normally would have allowed only one data transfer in the AT.

More Designs: Existing designs for the AT system can be migrated to the Micro Channel standard because all of the AT signals can be derived from the Micro Channel interface. However, new functions not possible in the AT can also be defined.

Potentially, more Micro Channel adapter designs are possible. Recall that, on the majority of the cards designed for PC, PC XT, and AT systems, only 10 of the 16 I/O address lines defined by the processor are decoded. This means that only 1,024 registers can be selected by the processor instead of the 65,536 defined by the full 16-bit I/O address.

Even the most rudimentary adapter will define three registers – one for commands to the attached device, another to transmit data to or from the device, and one last register to read status. If these registers are only 8 bits wide, then a maximum of 341 unique designs could be defined for a system that could install

Figure 15. Card Connectors

PC, PC XT, and AT cards with 10-bit decodes.

However, all cards complying with the Micro Channel specification fully decode the 16-bit address, so that theoretically about 22,000 unique designs are possible for Micro Channel systems.

Faster DMA: Micro Channel architecture also defines a serial DMA

capability, much like the "string mov" operation in some Intel processors. Separate read and write operations allow memory-to-memory operations, I/O caching, and inline processing to be defined in the DMA controller. Yet, on first inspection, serial DMA might appear to be slower than the parallel DMA, defined for PC, PC XT, and AT im-

Figure 16. Radiated Electromagnetic Field Strength

Figure 17. PC/XT/AT Parallel DMA

plementations, that moves data with just one operation.

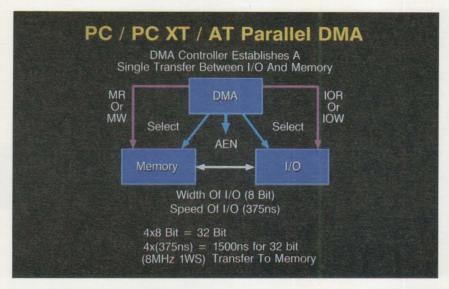

First, let's understand the way the PC, PC XT, and AT handle a DMA transfer (Figure 17). The PC DMA controller does not actually transfer data. It is a third party that arranges a transfer out from a source (for example, memory) and into a destination (in this example, an I/O adapter). The transfers occur as one operation, in parallel, hence the name "parallel DMA."

The parallel transfer begins when the DMA controller selects the memory by address, selects the I/O adapter by a signal called "DMA acknowledge," and asserts a signal called "AEN." AEN says to all the non-DMA adapters in the system, "I will drive two data strobes at once," in this case, memory write and I/O read. Only the parties in the DMA transfer respond, and data moves out of memory, across the data bus, and into the I/O adapter, all as one operation.

If everything occurs as one operation, then the width of the transfer

must be the width of the narrowest party. That is, an 8-bit I/O device could not receive 32 bits of data from a 32-bit memory in one operation; it would take four operations, each 8 bits wide, to move the 32-bit value. The most common I/O width is 8 bits, and today most systems are being defined for 32-bit memory width, so this is a realistic example. Likewise, the duration of the transfer must be the length of the slowest party. Here again, it is the I/O adapter on the AT bus that moves data at the default speed of the AT bus – 375 nanoseconds (ns), or 375 billionths of a second. It will take four 375 ns, 8-bit-wide transfers to move a 32-bit quantity of data from memory to I/O, or 1500 ns. The memory and the I/O are both delayed 1500 ns to complete the four operations.

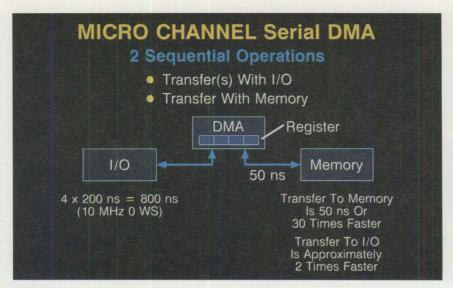

Now let's understand serial DMA as it is used in the "string mov" operation of the 80286, 80386, and 80486 processors and by Micro Channel DMA as well (Figure 18). In a Micro Channel DMA controller, a register is directly involved in the transfer. Data is read into the

register in one or more operations and written to a destination with one or more operations. The transfers occur sequentially, hence the name "serial DMA."

Here again, four 8-bit transfers would be required to move a 32-bit value from an 8-bit I/O adapter to the DMA controller, and at least one more to read the data out.

There are still more operations than with PC-, PC XT-, and AT-style parallel DMA, but they occur much faster on the Micro Channel interface. The four 8-bit transfers can occur at the default speed of the Micro Channel interface, 200 ns each. The total time is 800 ns.

The transfer with the I/O adapter was at its optimal speed, and the transfer with memory can be at the optimal speed of a 32-bit cached storage (as used in the Model 70-A21). Assume an average duration of 50 ns. If the operations occur on one bus, the total duration is 850 ns, or faster by just slightly over half the time of the AT bus. If the memory is on a separate bus, the I/O transfers do not impede its operation, and the serial DMA transfer with memory will occur 30 times faster than the AT-style parallel mode.

## **Greater Latitude for System**

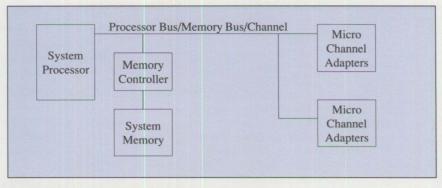

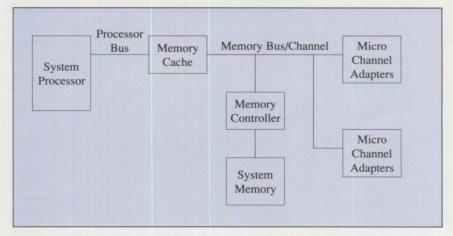

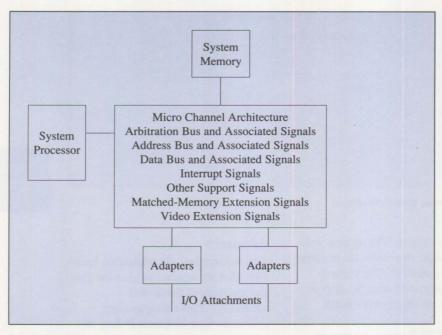

Design: Whether a computer is designed with one bus or more than one bus is a function of the system organization, but not of the channel architecture. Cost-effective Micro Channel systems can be defined with all the memory and I/O on one bus, as in the PS/2 Models 50 and 60. In addition, systems with the memory on one bus and the I/O on another, such as the PS/2 Model 70-A21, can also be defined with the same Micro Channel specification. It is important that high-function, ad-

vanced architecture does not imply higher complexity and cost – and it does not with Micro Channel architecture. The business case for card development is built on the large number of sockets installed for a wide range of products and not on the limited number of sockets for high-end systems alone.

One thing that allows this flexibility is that each of the parties in the system moves data at its individual optimal rate rather than in lock step with a system processor. Asynchronous transfer allows the straightforward Micro Channel implementation of processors of different types and speeds than the one that may have been soldered to the system board at the time of purchase.

Full Specifications: A full specification of all channel timings, current and capacitance loadings, mechanical and electrical considerations, and full definition of the functions are available in the *IBM Personal System/2 Hardware Interface Technical Reference* manual for the PS/2 Models 50, 60, 70386 and 80386 computers.

*Note:* IBM regularly holds education sessions and offers design assistance to adapter card developers.

Micro Channel Reliability: The Micro Channel interface has significantly improved the reliability, availability and serviceability of the system unit as well. Micro Channel design assists in the implementation of integrated circuits (ICs). IC designers most often run out of pins in the package before the silicon circuitry inside is completely used. More information is packed into fewer signals with the Micro Channel interface, and fewer pins are required to define the same function

Figure 18. Micro Channel Serial DMA

in an IC. A larger portion of the circuity in a system can be included inside the more reliable silicon chip, and the reliability of the entire system increases.

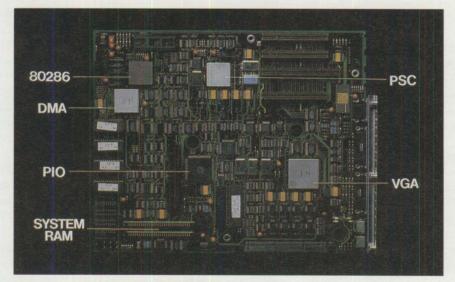

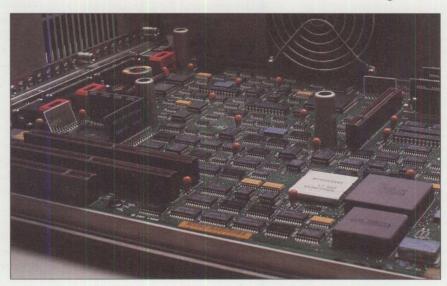

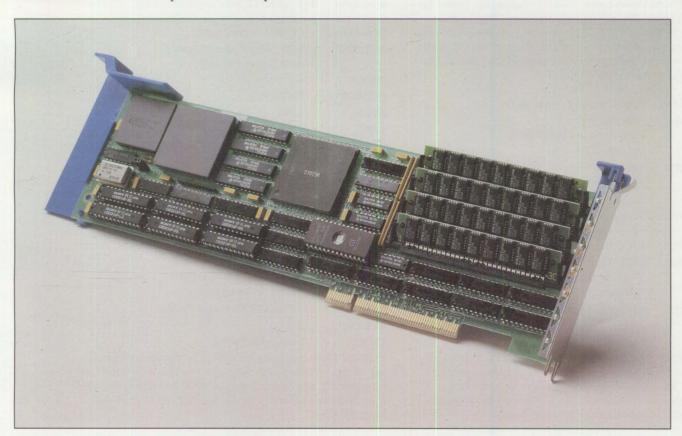

Because the Personal System/2 Model 50 (Figure 19) uses integrated circuits, it has one-eighth of the board area of the AT 339 that it replaces, is 25 percent faster, and includes six I/O adapters on the planar. It has a mean time between

Figure 19. PS/2 Model 50 System Board 80286: Intel 80286 Processor VGA: Video Graphics Array DMA: Direct Memory Access Chip PSC: Processor Support Chip PIO: Planar (System Board) I/O Chip

Figure 20. Card Compatibility

failure (an index of reliability) that is two to three times better than that of the AT 339 system, and has a service cost that is approximately one-third that of the AT 339. It also consumes only 94 watts, or half the power of most AT-based systems. These are all advantages to the customer.

Micro Channel architecture was planned from the ground up to support tomorrow's applications. It has the data integrity and reliability required of a system that multiple users may depend on.

Apples and Oranges: We often see comparisons between what Micro Channel architecture was in its first 16-bit implementation, and the maximum configuration of what implementation of another architecture might offer in the future. The AT computer might be extendable, just as the Micro Channel computer will be expanded. While we will not describe what extensions will be made to Micro Channel architecture here, one comparison between today's implementations is often not recognized: the DMA transfer rate

for 16-bit operations on the Micro Channel bus is often 10 times the DMA transfer rate of AT systems that employ 5 MHz Intel 8237-compatible DMA controllers.

Compare the what-might-be cases for example, what if the AT and Micro Channel DMA controllers each were implemented as bus masters. In both cases, the maximum burst rate of the Micro Channel bus would be nearly four times that of the AT bus - with both buses operating at default rates. This is because a system that exchanges data with existing AT cards could move two bytes in 375 ns. The Micro Channel interface defines 4-byte transfers between master and slave in 200 ns. The 32-bit SCSI interface bus master has been implemented and demonstrated with 4-byte transfers every 240 ns, or nearly 17 million bytes per second. This approximates the calculated continuous rate of 18.7 MB. That is approximately five times the rated speed of the AT bus as given in other manufacturers' specifications.

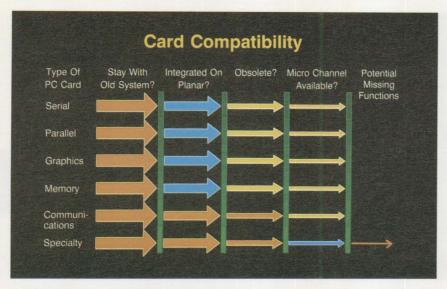

As for claims that lack of AT card compatibility limits a system designer's options, many of the cards in systems today must stay right where they are because the diskette, fixed disk, display, and memory cards are matched to the data width, speed, and peripheral interfaces of those systems (Figure 20). If the cards are removed, the system peripherals will not work.

Most of these interfaces have been upgraded. Where they are implemented on the PS/2 system board, no card need be purchased at all. Furthermore, many of the communications and other functions, purchased for the old system when it was new, are now obsolete, and more current designs are now available for the PS/2 Micro Channel computers. It is important to remember that all Micro Channel cards are current – with none made before April 1987.

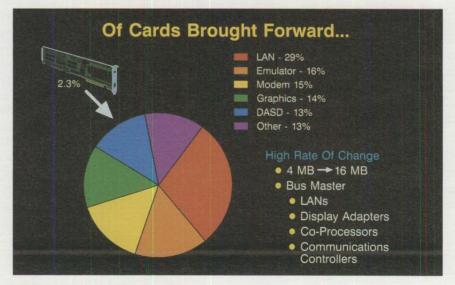

Card Portability: Studies have shown that it is indeed rare for a user to "cannibalize" a system to recover even a few cards for installation in a new system. Businesses need the most current and productive systems to be competitive. In the workplace, the old system is typically given to a new user whose needs are met by the capability of the old system. Almost 98 percent of the time, all the cards in a system remain in that system. Little more than 2 percent of the cards are brought forward (Figure 21).

LAN cards are the cards most frequently drafted into new duty. It is important to note that this data was obtained before Ethernet® LAN adapters were widely available for Micro Channel systems. Today there are several Micro Channel Ethernet bus master cards, and as many slave adapters, available.

There is a similar situation for 3278 emulation boards. Token-Ring LAN has recently gone through a generational change from 4-megabit to 16-megabit interface as well.

Today there are over 1,000 Micro Channel adapter cards available. IBM has issued more than 2,700 design IDs worldwide, indicating that as many as 1,700 more cards are under development. More than 650 vendors have the Micro Channel standard in their plans today. Of the 1,000 cards, 27 are advanced bus master cards; 197 bus master IDs have been assigned. Indeed, this is a better story for Micro Channel advanced I/O card designs than for AT cards.

## **Dollars and Common Sense**

It's easy to get excited about advanced technology, but dollars and common sense are what influence most business decisions. The reason to buy Micro Channel architecture is that it comes for free, in the highest-quality personal systems available today - the PS/2 Models 50 and above. They are also among the least expensive to own!

Assume you intend to own your new system for five years. Let's analyze the cost of ownership. We'll use the AT 339 system for comparison, but data for any other AT-bus machine can be used instead.

During the first year, both systems are under warranty, so the service cost is identical – zero. Based on IBM's annual onsite maintenance charges as of July 1, 1989, years 2 through 5 show that the Micro Channel system has a much lower IBM service cost. This is a reflection of higher reliability and more efficient diagnostics, as well as a reduction

in "no trouble found" service calls due to mis-set switches.

Diagnostics in Micro Channel systems can help prevent costly and unnecessary replacement of functional components due to a greater ability to accurately isolate and replace only the failed components; this can further reduce the service cost.

When you upgrade the system display, you do not need to pay a second time for the VGA function as you would have to in an AT system. This is because both the input and output of the display controller are connected to the Micro Channel interface. Cards that extend the display capabilities do not need to discard the existing controller or replace the function on the extension card. This can save the original VGA investment that need not be added to cost of the extension display adapter. This amounts to a savings of several hundred dollars.

PS/2 system users also won't have to spend as much on electric power. Check the name plate power rating on the back of most AT-based systems. The AT 339 is 192 watts, and, fully configured, it can cost you \$650 to run it five years for 24 hours per day, 292 days per year, at 10 cents per kilowatt hour. Adjust this number if you use the machine more or less, or if your local power costs more or less.

While some may say that the lower power allotted to adapter designs in Micro Channel systems makes the designer's job more challenging, those challenges can be overcome by large scale integration (LSI) and computer-aided design techniques that reduce size and power consumption and make the design less expensive to reproduce and more reliable in operation. The reduced power in PS/2 Micro Channel systems is an advantage to the customer. The name plate rating for a maximally configured PS/2 Model 50 Z is 94 watts, about one half that of the AT system it replaced. The result: you'll save about \$325 in electric bills. (The display also uses electricity but is not included in this system unit comparison.)

Figure 21. Cards Brought Forward

Add up all the savings you can demonstrate, and then consider comparative depreciation in the resale value of the system, and the value of increased productivity from a system that is more available and needs less maintenance time. You'll find you save a sizable fraction of the purchase price. Your calculations would look something like this:

On-Site Maintenance:

| Year      | AT 339 | PS/2 50 Z | You Save |

|-----------|--------|-----------|----------|

| 1         | 0      | 0         | 0        |

| 2         | 442    | 192       | 250      |

| 3         | 442    | 192       | 250      |

| 4         | 442    | 192       | 250      |

| 5         | 442    | 192       | 250      |

| Display   |        |           |          |

| Upgrad    | de 400 | 0         | 400      |

| Electrici | ty 650 | 325       | 325      |

| Total     |        |           | \$1,725  |

In fact, if you keep the system a few more years, it will have been free – the savings in ownership will have paid for the original purchase.

The moral is to look past the cost of purchase to the real cost of ownership before you decide which system offers the lowest overall cost. This is why Micro Channel architecture also stands for "Maintain the Customer's Assets" – maintain the asset in the system unit by building the future in and "designing in" quality, and maintain the asset in the feature cards by assisting in the portability of those functions across a broad range of machines.

## Evolution Follows Revolution

The future will see the Micro Channel standard grow and evolve gracefully. New functions are already defined for advanced systems. They will include further improvement in the ability of the system to detect, in some cases to recover from, and perhaps even to correct, errors.

Although implementations of the Micro Channel interface have already defined data transfers at 32 megabytes per second, the demands of multitasking and multiuser systems will further increase throughput requirements. By adjustments in the efficiency of transfer protocols and wider-width data transfers, we are confident that the throughput can be significantly increased over time.