|

Introduction

Module Types

Module Pinout

Documentation

Introduction

The 485Turbocache (aka "485 Turbocache" or "TurboCache") is Intel's

all-in-one Level 2 cache solution designed specifically for 486-class systems.

The modules integrate not only the cache SRAM chips but also the cache

controller logic (similar to the 128-pin Cache

Modules). Different sizes are available (64 or 128 KB). All known modules

use the Write-Through policy. The standard interface lacks the WB/WT pin and

other signals necessary to implement the WB mode.

The modules are used by the following Micro Channel systems and planar

upgrades:

And also by some non-MCA systems:

- Digital Equipment DECpc 433

- Digital Equipment DECpc 452ST (processor card)

- Diversified Technology (DTI) MBC2000 motherboard

- Epson ExpressStation 486

- Hauppauge 4860 motherboard (info)

- Intel L486 Series Professional Workstation (manual)

- Morse Technologies KP 486EDX

- Multibest Industrial MB4861DX

- Packard Bell 22/23 motherboard

- Zenith ZDS

- Zeos 486/33

- Honeywell Measurex MX64+ Processor Board

(The list above is based on info from VCF user "wault".)

Module Types

Known module types:

- Intel 82485MA (-25/-33) (64 KB, WT, 2-Way Associative, 0 WS @ 25/33 MHz)

- Intel 82485MB (-25/-33) (128 KB, WT, 2-Way Associative, 0 WS @ 25/33 MHz)

- IDT7MB6091 (128 KB, WT, Direct-mapped, 0 WS @ 33 MHz)

- IDT7MB6098/A/SA33K (128 KB, WT, Direct-mapped, 0 WS @ 33 MHz)

- "ECM-256" (unknown mfg.) (256 KB?)

- "ECN03" (unknown mfg.) (64 KB, 33 MHz)

Intel 82485Mx Rev. B

![Angle [P]](/other/img/photo.gif)

![Angle (alt) [P]](/other/img/photo.gif) (photos from "Xhoba")

(photos from "Xhoba")

Intel 82485-33 Cache Controller

Micron MT56C2818-24 Dual 4Kx18, Single 8Kx18 Cache Data SRAM

(4 devices for 64 KB, 8 devices for 128 KB)

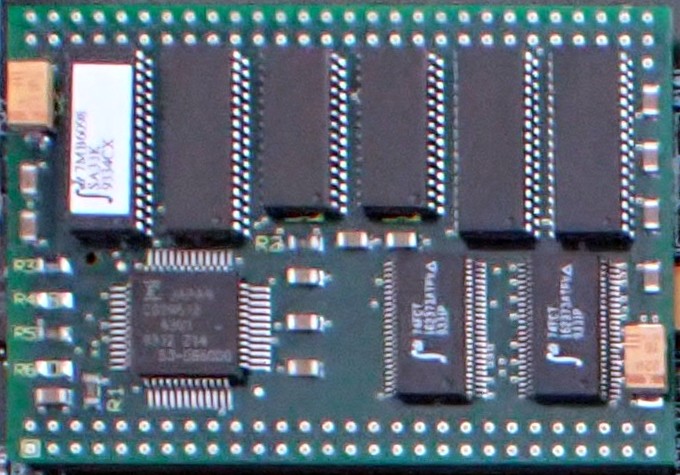

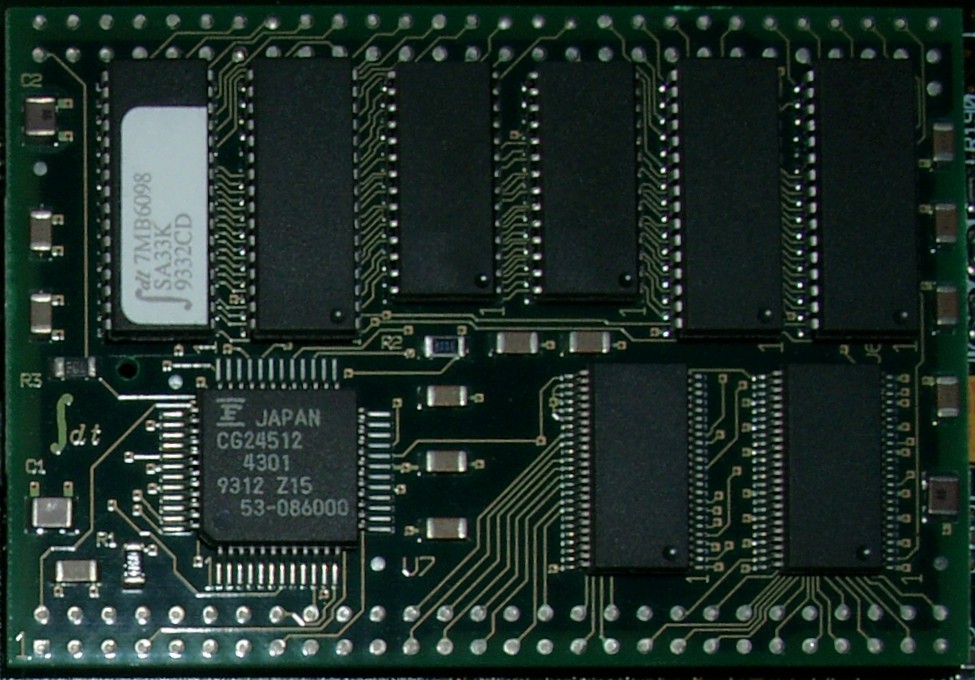

IDT7MB6098

![Old - Front [P]](/other/img/photo.gif)

![Old - Angle [P]](/other/img/photo.gif)

![Newer - Front [P]](/other/img/photo.gif)

![Newest - Front [P]](/other/img/photo.gif) (photos by MadMax, IBMMuseum and SuperVinx)

(photos by MadMax, IBMMuseum and SuperVinx)

Cache Controller implemented using PALs.

Cache Controller implemented using a gate array? Fairchild CG24512 4301 53-086000

Cache Controller implemented using a gate array? A slightly different PCB layout.

IDT74FCT162373 16-bit Latch

IDT71B74 8Kx8 Cache-TAG SRAM

IDT71589 32Kx9 Cache SRAM, Burst Mode 486

Equivalent of a 128-pin module 7MP6104.

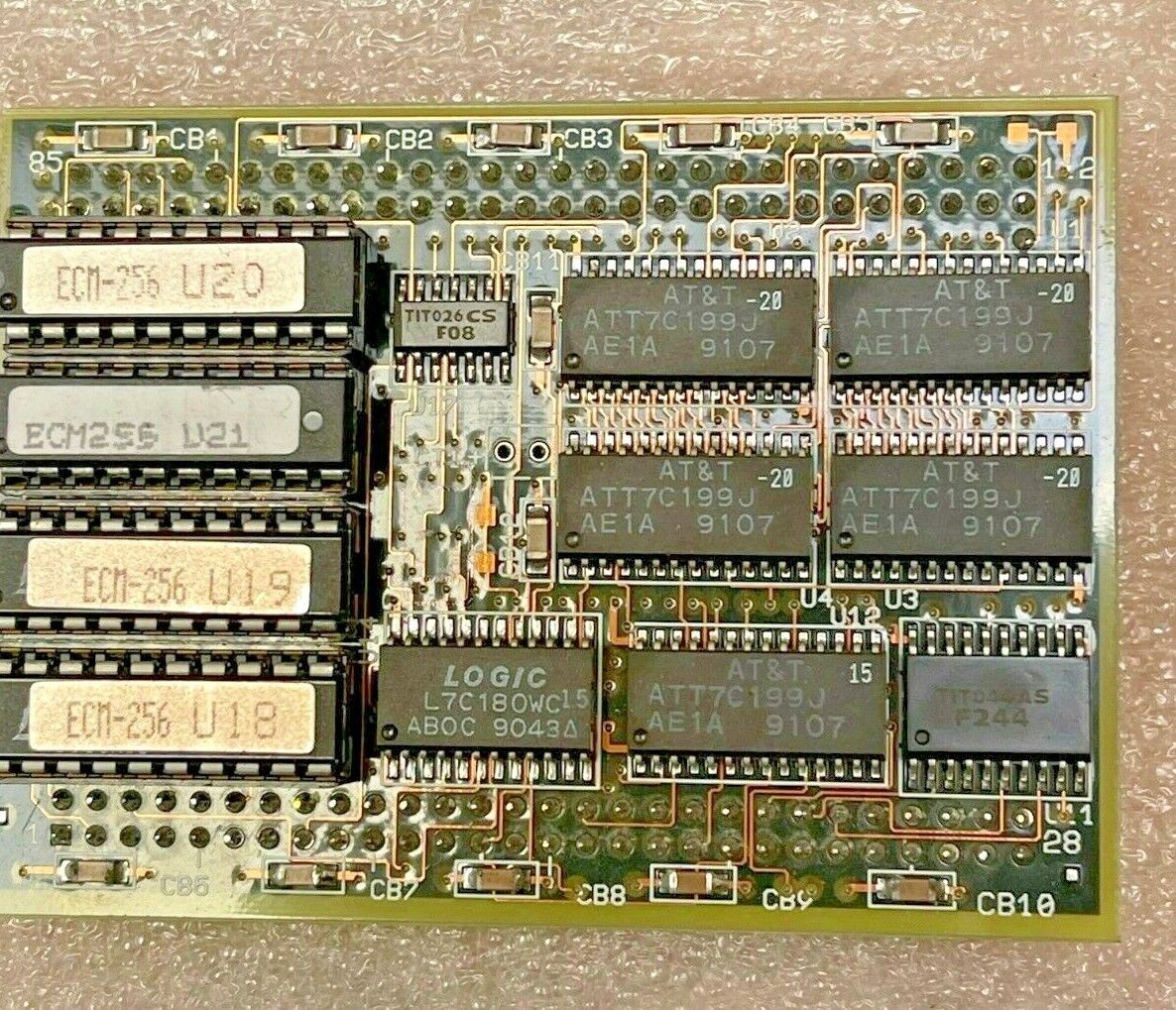

"ECM-256" (unknown mfg.)

![Front [P]](/other/img/photo.gif)

![Back [P]](/other/img/photo.gif) | |

![Front (alt) [P]](/other/img/photo.gif)

![Back (alt) [P]](/other/img/photo.gif)

U1-4 AT&T ATT7C199J-20 or Toshiba TC55328J-20 32Kx8 SRAM

U5-8 Toshiba TC55328J-20 32Kx8 SRAM

U12 AT&T ATT7C199J-15 or Logic L7C199WC 15 32Kx8 SRAM

U14 Logic L7C180WC 15 4Kx4 Cache-TAG SRAM

U? Pericom P74PCT521BS 8-Bit Identity Comparator

PALs and 74xx glue

"ECN03" (unknown mfg.)

![Front [P]](/other/img/photo.gif)

![Back [P]](/other/img/photo.gif)

![Both (orig) [P]](/other/img/photo.gif) (orig. photo from UMMR)

(orig. photo from UMMR)

U12-19 Motorola MCM6265NJ20? 8Kx9 SRAM

U?,? Motorola MCM6265NJ15? 8Kx9 SRAM (tag?)

DL1 Delay line

PALs and 74xx glue

Possibly a non-standard module. Notice the additional

J2 header - looks like it would conflict

with the socket base.

Module Pinout

The module comes in a 113-lead FR-4 QIP (Quad In-line Package). It connects

to the host system via two 2x28-pin headers + one additional key pin.

The following table shows the module's pinout - Top Side View.

Pin BB3 acts as a key and is grouped together with rows 4 and 5.

| 1 | 2 | 3 | 4 | 5 |

|---|

| A | GND | RESET | | -CS | GND |

| B | CLK | M/-IO | -CRDY | -CKEN |

| C | Reserved | -FLUSH | -CBRDY | -BRDYO |

| D | -BLAST | -EADS | Vcc | -SKEN |

| E | -BOFF | Vcc | WP | -START |

| F | -ADS | W/-R | D0 | GND |

| G | GND | -WPSTRP | D2 | D1 |

| H | -BE0 | -BE1 | GND | D3 |

| I | -BE2 | -BE3 | D5 | D4 |

| J | A2 | GND | D7 | D6 |

| K | Vcc | A3 | D8 | GND |

| L | A4 | A5 | D10 | D9 |

| M | A6 | A7 | Vcc | D11 |

| N | A9 | A8 | D13 | D12 |

| O | A10 | Vcc | D15 | D14 |

| P | GND | A11 | DP0 | GND |

| Q | A31 | A12 | D16 | DP1 |

| R | A14 | A13 | GND | D17 |

| S | A15 | GND | D19 | D18 |

| T | A17 | A16 | D21 | D20 |

| U | A19 | A18 | D22 | Vcc |

| V | Vcc | A20 | D24 | D23 |

| W | A22 | A21 | GND | D25 |

| X | A23 | Vcc | D27 | D26 |

| Y | A25 | A24 | D29 | D28 |

| Z | A27 | A26 | D30 | D31 |

| AA | A29 | A28 | DP2 | DP3 |

| BB | GND | A30 | -PRSN | Vcc | GND |

Note: Pin G2 is -WPSTRP on the original Intel

485Turbocache modules but is unused (N/C) on IDT modules.

For description of the individual signals see the

Intel 485Turbocache Module

datasheet.

Documentation

Manuals:

i486 Processor Hardware Reference Manual (1990)

1.2.3 485Turbocache Module (page 35 phys.)

6.7 Introduction to the 485Turbocache Module (page 226 phys.)

6.8 485Turbocache Module Hardware Interface (page 231 phys.)

6.9 Design Considerations (page 243 phys.)

6.10 Timing Diagrams (page 245 phys.)

Datasheets:

Intel 82485MA/MB - 485Turbocache Module Intel486 Microprocessor Cache Upgrade

IDT7MB6091 - 128KB Secondary Cache Module for the Intel i486

IDT7MB6098A - 128KB Secondary Cache Module for the Intel i486

Data books:

IDT High-Performance Static RAMs (1992)

IDT Specialized Memories and Modules (1994)

IDT7MB6098A - 128KB Secondary Cache Module for the Intel i486 (page 1015 phys.)

Micron SRAM Data Book (1991)

MT56C2818 - Dual 4Kx18, Single 8Kx18 Cache Data SRAM (page 344 phys.)

Technical Disclosure Bulletins:

486 L2 Write-through Cache Support in a Local Bus Multiprocessor System

|