# 80C186 and 80C188 Integrated 16-Bit Microprocessors

This document amends the 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book, order #16514D, and replaces the discontinued 80C186/80C188 CMOS High-Integration 16-Bit Microprocessors Amendment (specifications for the 20-MHz industrial operating range). This amendment consists of two parts:

- Clock generation information changes for the 80C186 and 80C188 microcontrollers. If the guidelines in this bulletin are not followed, you may experience problems with clock start-up.

- Industrial operating information at 20 MHz. This is the same information that was published in the discontinued 80C186/80C188 CMOS High-Integration 16-Bit Microprocessors Amendment.

## CLOCKING INFORMATION CHANGES Crystal-Driven Clock Source

The internal oscillator circuit of the microcontroller is designed to function with a parallel resonant fundamental or third-overtone crystal. The 80C186 and 80C188 microprocessors use a crystal frequency that is twice the processor frequency. AMD does not recommend that you replace a crystal with an LC or RC equivalent for any member of the Am186™ family.

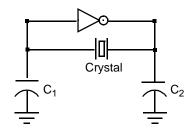

The X1 and X2 signals are connected to an internal inverting amplifier (oscillator) that provides, along with the external feedback loading, the necessary phase shift (Figure 1 on page 2). In such a positive feedback circuit, the inverting amplifier has an output signal (X2) 180 degrees out of phase of the input signal (X1). The external feedback network provides an additional 180 degree phase shift. In an ideal system, the input to X1 has 360 or zero degrees of phase shift.

The external feedback network is designed to be as close as possible to ideal. If the feedback network is not providing necessary phase shift, negative feedback dampens the output of the amplifier and negatively affects the operation of the clock generator. Values for the loading on X1 and X2 must be chosen to provide the necessary phase shift and crystal operation.

### Selecting a Crystal

When selecting a crystal, you should always specify the load capacitance ( $C_L$ ). This value can cause variance in the oscillation frequency from the desired specified value (resonance). The load capacitance and the loading of the feedback network have the following relationship:

$$C_L = ((C_1 \cdot C_2)/(C_1 + C_2)) + C_S$$

where  $C_S$  is the stray capacitance of the circuit. Placing the crystal and  $C_I$  in series across the inverting

amplifier and tuning these values  $(C_1, C_2)$  allows the crystal to oscillate at resonance. This relationship is true for both fundamental and third-overtone operation. Finally, there is a relationship between  $C_1$  and  $C_2$ . To enhance the oscillation of the inverting amplifier, these values must be offset with the larger load on the output (X2). Equal values of these loads tend to balance the poles of the inverting amplifier.

The characteristics of the inverting amplifier set limits on the following parameters for crystals:

| ESR (Equivalent Se          | eries Resistance) 40 12 Max      |

|-----------------------------|----------------------------------|

| Drive Level                 | 1 mW Max                         |

| The recommended as follows: | range of values for C1and C2 are |

| C <sub>1</sub>              | 15 pF ± 20%                      |

| C <sub>2</sub>              | 22 pF ± 20%                      |

You must determine the specific values for  $C_1$  and  $C_2$ . The values are dependent on the characteristics of the chosen crystal and board design. The  $C_1$  and  $C_2$  values include the stray capacitances of the design.

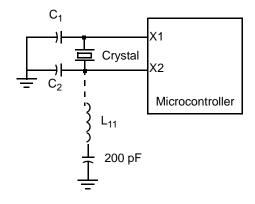

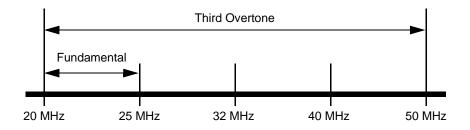

Figure 1 on page 2 shows the correct connection of the oscillator configurations. Figure 1a shows the inverting amplifier configuration. This is the equivalent circuitry with the inverter integrated into the microcontroller. Figure 1b shows the crystal configuration. The diagram shows the correct connection for third-overtone crystals. The fundamental mode crystals do not require the  $L_1$  or the 200-pF capacitor. Figure 1c shows the recommended crystal mode based on the crystal frequency. The 80C186 and 80C188 microprocessors use a crystal twice the CPU frequency and can use either fundamental or third-overtone mode crystals, depending on the CPU frequency.

a. Inverting Amplifier Configuration

#### b. Crystal Configuration

#### Notes:

1. Use for third overtone mode crystals. Fundamental mode crystals do not use L1 or the 200-pF capacitor.

| XTAL Frequency | L1 Value (Max              |

|----------------|----------------------------|

| 20 MHz         | 12 μH ±20%                 |

| 25 MHz         | 8.2 μH ±20%                |

| 32 MHz         | $4.7 \mu\text{H} \pm 20\%$ |

| 40 MHz         | 3.0 µH±20%                 |

| 50 MHz         | 2.2 uH±20%                 |

c. Recommended Crystal Mode

Figure 1. Oscillator Configurations and Recommended Crystal Modes

#### SWITCHING CHARACTERISTICS OVER INDUSTRIAL OPERATING RANGE AT 20 MHZ

This section includes the following timings and timing waveforms at 20 MHz:

- "Read-Cycle Timings" on page 4

- "Read-Cycle Waveforms" on page 5

- "Write-Cycle Timings" on page 6

- "Write-Cycle Waveforms" on page 7

- "Interrupt Acknowledge Cycle Timings" on page 8

- "Interrupt Acknowledge Cycle Waveforms" on page 9

- "Software Halt Cycle Timings" on page 10

- "Software Halt Cycle Waveforms" on page 11

- "Clock Timings" on page 12

- "Clock Waveforms" on page 13

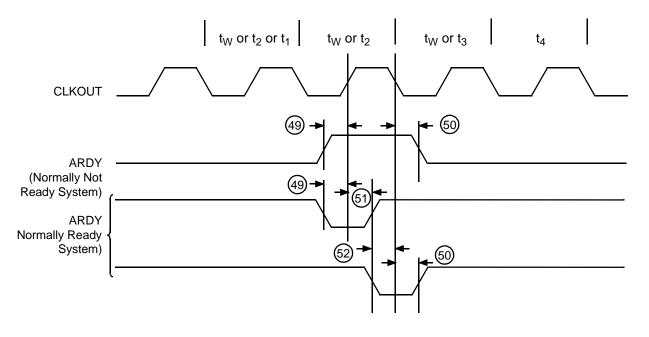

- "Ready, Peripheral, and Queue Status Timings" on page 14

- "Synchronous Read (SRDY) Waveforms" on page 14

- "Asynchronous Ready (ARDY) Waveforms" on page 15

- "Peripheral and Queue Status Waveforms" on page 15

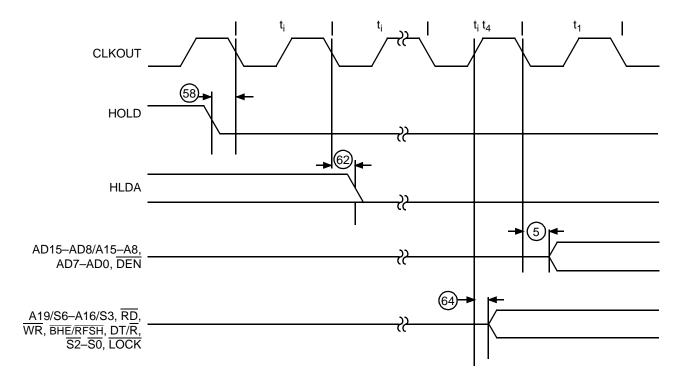

- "RESET and HOLD/HLDA Timings" on page 16

- "RESET Waveforms" on page 16

- "HOLD/HLDA Waveforms (Entering HOLD)" on page 17

- "HOLD/HLDA Waveforms (Leaving HOLD)" on page 17

## Read-Cycle Timings<sup>1</sup>

$T_{A\text{-IND}}$ =-40°C to +85°C,  $V_{CC}$ =5 V ±10%

|     |                    |                                                     | Preliminary                 |     |      |

|-----|--------------------|-----------------------------------------------------|-----------------------------|-----|------|

|     |                    | Parameter                                           | 20 MHz                      |     | 1    |

| #   | Symbol             | Description                                         | Min                         | Max | Unit |

| Gen | eral Timin         | g Requirements (listed more than once)              | ·                           |     |      |

| 1   | t <sub>DVCL</sub>  | Data in Setup (A/D)                                 | 10                          |     | ns   |

| 2   | t <sub>CLDX</sub>  | Data in Hold (A/D)                                  | 3                           |     | ns   |

| Gen | eral Timin         | g Responses (listed more than once)                 | •                           |     |      |

| 3   | t <sub>CHSV</sub>  | Status Active Delay                                 | 3                           | 29  | ns   |

| 4   | t <sub>CLSH</sub>  | Status Inactive Delay                               | 3                           | 29  | ns   |

| 5   | t <sub>CLAV</sub>  | Address Valid Delay                                 | 3                           | 25  | ns   |

| 6   | t <sub>CLAX</sub>  | Address Hold                                        | 0                           |     | ns   |

| 7   | t <sub>CLDV</sub>  | Data Valid Delay                                    | 3                           | 25  | ns   |

| 8   | t <sub>CHDX</sub>  | Status Hold Time                                    | 10                          |     | ns   |

| 9   | t <sub>CHLH</sub>  | ALE Active Delay                                    |                             | 20  | ns   |

| 10  | t <sub>LHLL</sub>  | ALE Width                                           | t <sub>CLCL</sub> -15 = 35  |     | ns   |

| 11  | t <sub>CHLL</sub>  | ALE Inactive Delay                                  |                             | 20  | ns   |

| 12  | t <sub>AVLL</sub>  | Address Valid to ALE Low <sup>2</sup>               | $t_{CLCH} - 10 = 10$        |     | ns   |

| 13  | t <sub>LLAX</sub>  | Address Hold from ALE Inactive <sup>2</sup>         | t <sub>CHCL</sub> -10 = 10  |     | ns   |

| 14  | t <sub>AVCH</sub>  | Address Valid to Clock High                         | 0                           |     | ns   |

| 15  | t <sub>CLAZ</sub>  | Address Float Delay                                 | $t_{CLAX} = 0$              | 17  | ns   |

| 16  | t <sub>CLCSV</sub> | Chip-Select Active Delay                            | 3                           | 25  | ns   |

| 17  | t <sub>CXCSX</sub> | Chip-Select Hold from Command Inactive <sup>2</sup> | t <sub>CLCH</sub> -10 = 10  |     | ns   |

| 18  | t <sub>CHCSX</sub> | Chip-Select Inactive Delay                          | 3                           | 20  | ns   |

| 19  | t <sub>DXDL</sub>  | DEN Inactive to DT/R Low                            | 0                           |     | ns   |

| 20  | t <sub>CVCTV</sub> | Control Active Delay 1 <sup>3</sup>                 | 3                           | 22  | ns   |

| 21  | t <sub>CVDEX</sub> | DEN Inactive Delay                                  | 3                           | 22  | ns   |

| 22  | t <sub>CHCTV</sub> | Control Active Delay 2 <sup>3</sup>                 | 3                           | 22  | ns   |

| 23  | t <sub>CLLV</sub>  | LOCK Valid/Invalid Delay                            | 3                           | 22  | ns   |

|     |                    | nses (Read Cycle)                                   |                             |     |      |

| 24  | t <sub>AZRL</sub>  | Address Float to RD Active                          | 0                           |     | ns   |

| 25  | t <sub>CLRL</sub>  | RD Active Delay                                     | 3                           | 27  | ns   |

| 26  | t <sub>RLRH</sub>  | RD Pulse Width                                      | 2t <sub>CLCL</sub> -20 = 80 |     | ns   |

| 27  | t <sub>CLRH</sub>  | RD Inactive Delay                                   | 3                           | 25  | ns   |

| 28  | t <sub>RHLH</sub>  | RD Inactive to ALE High <sup>2</sup>                | t <sub>CLCH</sub> -10 = 10  |     | ns   |

| 29  | t <sub>RHAV</sub>  | RD Inactive to Address Active <sup>2</sup>          | t <sub>CLCL</sub> -15 = 35  |     | ns   |

<sup>1.</sup> All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50-100$  pF (10–20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup> Equal loading.

<sup>3.</sup> DEN, INTA, WR.

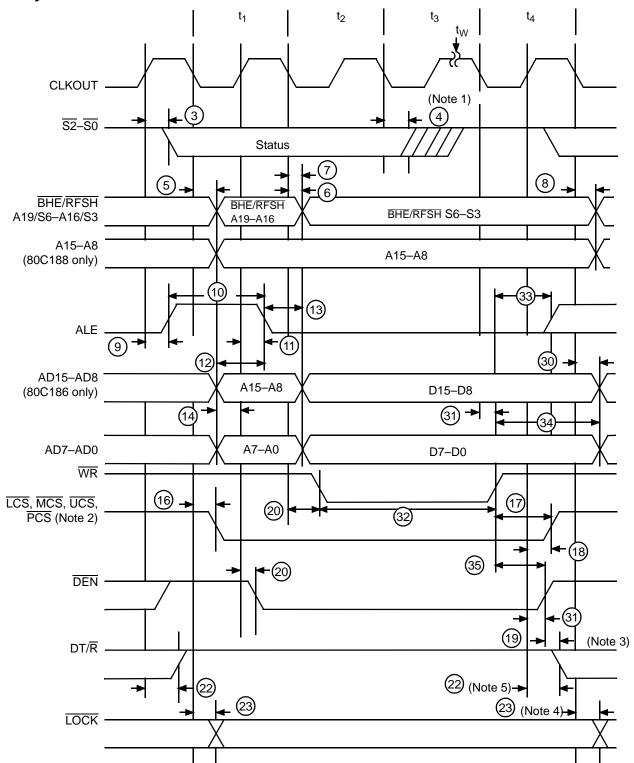

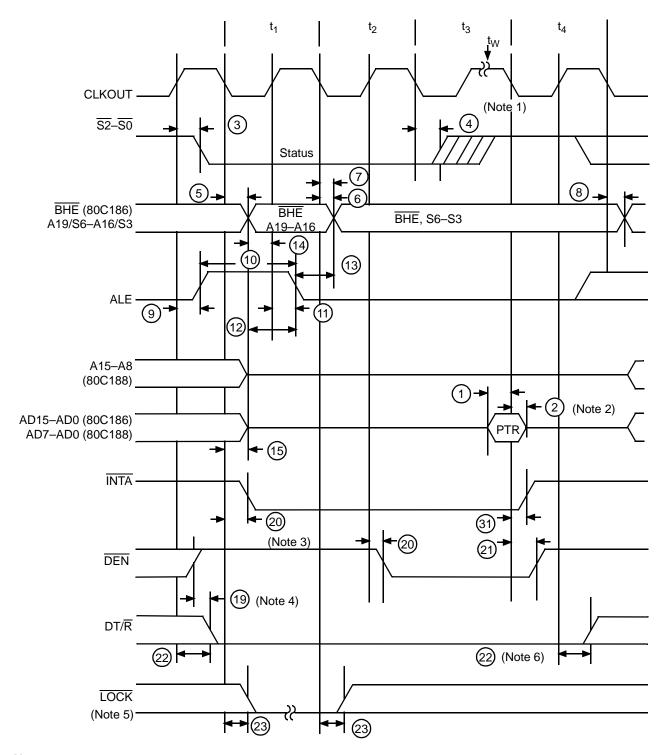

## **Read-Cycle Waveforms**

- 1. Status inactive in state preceding t<sub>4</sub>.

- 2. If latched, A1 and A2 are selected instead of  $\overline{PCS5}$  and  $\overline{PCS6}$ ; only  $t_{CLCSV}$  is applicable.

- 3. For write cycle followed by read cycle.

- 4. t<sub>1</sub> of next bus cycle.

- 5. Changes in t-state preceding next bus cycle if followed by write.

## Write-Cycle Timings<sup>1</sup>

$T_{A\text{-IND}} = -40^{\circ} C$  to + 85°C,  $V_{CC} = 5~\text{V} \pm 10\%$

|     |                    |                                                     | Preliminary                 |     |      |

|-----|--------------------|-----------------------------------------------------|-----------------------------|-----|------|

|     |                    | Parameter                                           | 20 MHz                      |     |      |

| #   | Symbol             | Description                                         | Min                         | Max | Unit |

| Gen | eral Timin         | g Responses (listed more than once)                 |                             |     |      |

| 3   | t <sub>CHSV</sub>  | Status Active Delay                                 | 3                           | 29  | ns   |

| 4   | t <sub>CLSH</sub>  | Status Inactive Delay                               | 3                           | 29  | ns   |

| 5   | t <sub>CLAV</sub>  | Address Valid Delay                                 | 3                           | 25  | ns   |

| 6   | t <sub>CLAX</sub>  | Address Hold                                        | 0                           |     | ns   |

| 7   | t <sub>CLDV</sub>  | Data Valid Delay                                    | 3                           | 25  | ns   |

| 8   | t <sub>CHDX</sub>  | Status Hold Time                                    | 10                          |     | ns   |

| 9   | t <sub>CHLH</sub>  | ALE Active Delay                                    |                             | 20  | ns   |

| 10  | t <sub>LHLL</sub>  | ALE Width                                           | t <sub>CLCL</sub> -15 = 35  |     | ns   |

| 11  | t <sub>CHLL</sub>  | ALE Inactive Delay                                  |                             | 20  | ns   |

| 12  | t <sub>AVLL</sub>  | Address Valid to ALE Low <sup>2</sup>               | t <sub>CLCH</sub> -10 = 10  |     | ns   |

| 13  | t <sub>LLAX</sub>  | Address Hold from ALE Inactive <sup>2</sup>         | t <sub>CHCL</sub> -10 = 10  |     | ns   |

| 14  | t <sub>AVCH</sub>  | Address Valid to Clock High                         | 0                           |     | ns   |

| 16  | t <sub>CLCSV</sub> | Chip-Select Active Delay                            | 3                           | 25  | ns   |

| 17  | t <sub>CXCSX</sub> | Chip-Select Hold from Command Inactive <sup>2</sup> | t <sub>CLCH</sub> -10 = 10  |     | ns   |

| 18  | t <sub>CHCSX</sub> | Chip-Select Inactive Delay                          | 3                           | 20  | ns   |

| 19  | t <sub>DXDL</sub>  | DEN Inactive to DT/R Low                            | 0                           |     | ns   |

| 20  | t <sub>CVCTV</sub> | Control Active Delay 1 <sup>3</sup>                 | 3                           | 22  | ns   |

| 23  | t <sub>CLLV</sub>  | LOCK Valid/Invalid Delay                            | 3                           | 22  | ns   |

| Tim | ing Respo          | nses (Write Cycle)                                  |                             |     |      |

| 30  | t <sub>CLDOX</sub> | Data Hold Time                                      | 3                           |     | ns   |

| 31  | t <sub>CVCTX</sub> | Control Inactive Delay <sup>3</sup>                 | 3                           | 22  | ns   |

| 32  | t <sub>WLWH</sub>  | WR Pulse Width                                      | 2t <sub>CLCL</sub> -20 = 80 |     | ns   |

| 33  | t <sub>WHLH</sub>  | WR Inactive to ALE High <sup>2</sup>                | t <sub>CLCH</sub> -14 = 6   |     | ns   |

| 34  | t <sub>WHDX</sub>  | Data Hold after WR <sup>2</sup>                     | t <sub>CLCL</sub> -15 = 35  |     | ns   |

| 35  | t <sub>WHDEX</sub> | WR Inactive to DEN Inactive <sup>2</sup>            | t <sub>CLCH</sub> -10 = 10  |     | ns   |

<sup>1.</sup> All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50-100$  pF (10–20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup> Equal loading.

<sup>3.</sup> DEN, INTA, WR.

## **Write-Cycle Waveforms**

- 1. Status inactive in state preceding t<sub>4</sub>.

- 2. If latched, A1 and A2 are selected instead of  $\overline{PCS5}$  and  $\overline{PCS6}$ ; only  $t_{CLCSV}$  is applicable.

- 3. For write cycle followed by read cycle.

- 4.  $t_1$  of next bus cycle.

- 5. Changes in t-state preceding next bus cycle if followed by read, INTA, or halt.

## Interrupt Acknowledge Cycle Timings<sup>1</sup>

$T_A = -40^{\circ}C$  to +85°C,  $V_{CC} = 5 \text{ V} \pm 10\%$

|     |                    |                                                | Preliminary                |     |      |

|-----|--------------------|------------------------------------------------|----------------------------|-----|------|

|     |                    | Parameter                                      | 20 MHz                     |     | 1    |

| #   | Symbol             | Description                                    | Min                        | Max | Unit |

| 80C | 186 Gener          | al Timing Requirements (listed more than once) | <u>.</u>                   |     |      |

| 1   | t <sub>DVCL</sub>  | Data in Setup (A/D)                            | 10                         |     | ns   |

| 2   | t <sub>CLDX</sub>  | Data in Hold (A/D)                             | 3                          |     | ns   |

| 80C | 186 Gener          | al Timing Responses (listed more than once)    |                            |     | •    |

| 3   | t <sub>CHSV</sub>  | Status Active Delay                            | 3                          | 29  | ns   |

| 4   | t <sub>CLSH</sub>  | Status Inactive Delay                          | 3                          | 29  | ns   |

| 5   | t <sub>CLAV</sub>  | Address Valid Delay                            | 3                          | 25  | ns   |

| 6   | t <sub>CLAX</sub>  | Address Hold                                   | 0                          |     | ns   |

| 7   | t <sub>CLDV</sub>  | Data Valid Delay                               | 3                          | 25  | ns   |

| 8   | t <sub>CHDX</sub>  | Status Hold Time                               | 10                         |     | ns   |

| 9   | t <sub>CHLH</sub>  | ALE Active Delay                               |                            | 20  | ns   |

| 10  | t <sub>LHLL</sub>  | ALE Width                                      | $t_{CLCL}-15=35$           |     | ns   |

| 11  | t <sub>CHLL</sub>  | ALE Inactive Delay                             |                            | 20  | ns   |

| 12  | t <sub>AVLL</sub>  | Address Valid to ALE Low <sup>2</sup>          | t <sub>CLCH</sub> -10 = 10 |     | ns   |

| 13  | t <sub>LLAX</sub>  | Address Hold from ALE Inactive <sup>2</sup>    | t <sub>CHCL</sub> -10 = 10 |     | ns   |

| 14  | t <sub>AVCH</sub>  | Address Valid to Clock High                    | 0                          |     | ns   |

| 15  | t <sub>CLAZ</sub>  | Address Float Delay                            | $t_{CLAX} = 0$             | 17  | ns   |

| 19  | t <sub>DXDL</sub>  | DEN Inactive to DT/R Low <sup>2</sup>          | 0                          |     | ns   |

| 20  | t <sub>CVCTV</sub> | Control Active Delay 1 <sup>3</sup>            | 3                          | 22  | ns   |

| 21  | t <sub>CVDEX</sub> | DEN Inactive Delay (Non-Write Cycles)          | 3                          | 22  | ns   |

| 22  | t <sub>CHCTV</sub> | Control Active Delay 2 <sup>3</sup>            | 3                          | 22  | ns   |

| 23  | t <sub>CLLV</sub>  | LOCK Valid/Invalid Delay                       | 3                          | 22  | ns   |

| 31  | t <sub>CVCTX</sub> | Control Inactive Delay <sup>3</sup>            | 3                          | 22  | ns   |

<sup>1.</sup> All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50-200$  pF (10 MHz) and  $C_L = 50-100$  pF (12.5-20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup> Equal loading.

<sup>3.</sup> DEN, INTA, WR.

## **Interrupt Acknowledge Cycle Waveforms**

- 1. Status inactive in state preceding t<sub>4</sub>.

- 2. The data hold time lasts only until  $\overline{INTA}$  goes inactive, even if the  $\overline{INTA}$  transition occurs prior to  $t_{CLDX}$  (min).

- 3. INTA occurs one clock later in Slave mode.

- 4. For write cycle followed by interrupt acknowledge cycle.

- 5. LOCK is active upon t<sub>1</sub> of the first interrupt acknowledge cycle and inactive upon t<sub>2</sub> of the second interrupt acknowledge cycle.

- 6. Changes in t-state preceding next bus cycle if followed by write.

## Software Halt Cycle Timings<sup>1</sup>

$T_A = -40^{\circ} C$  to 85°C,  $V_{CC} = 5~V \pm 10\%$

|     |                    |                                             | Preliminary                |     |      |

|-----|--------------------|---------------------------------------------|----------------------------|-----|------|

|     | Parameter          |                                             | 20 MHz                     |     |      |

| #   | Symbol             | Description                                 | Min                        | Max | Unit |

| 80C | 186 Gener          | al Timing Responses (listed more than once) |                            | -   |      |

| 3   | t <sub>CHSV</sub>  | Status Active Delay                         | 3                          | 29  | ns   |

| 4   | t <sub>CLSH</sub>  | Status Inactive Delay                       | 3                          | 29  | ns   |

| 5   | t <sub>CLAV</sub>  | Address Valid Delay                         | 3                          | 25  | ns   |

| 9   | t <sub>CHLH</sub>  | ALE Active Delay                            |                            | 20  | ns   |

| 10  | t <sub>LHLL</sub>  | ALE Width                                   | t <sub>CLCL</sub> -15 = 35 |     | ns   |

| 11  | t <sub>CHLL</sub>  | ALE Inactive Delay                          |                            | 20  | ns   |

| 19  | t <sub>DXDL</sub>  | DEN Inactive to DT/R Low <sup>2</sup>       | 0                          |     | ns   |

| 22  | t <sub>CHCTV</sub> | Control Active Delay 2 <sup>3</sup>         | 3                          | 22  | ns   |

<sup>1.</sup> All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50-200$  pF (10 MHz) and  $C_L = 50-100$  pF (12.5–20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup> Equal loading.

<sup>3.</sup> DEN, INTA, WR.

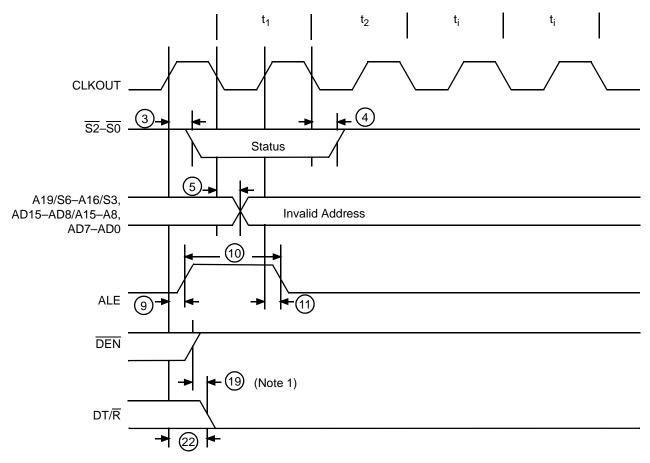

## **Software Halt Cycle Waveforms**

#### Notes:

1. For write cycle followed by halt cycle.

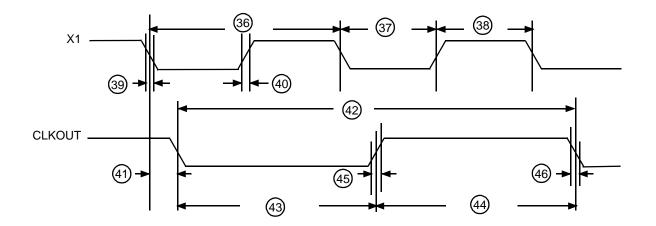

## Clock Timings<sup>1</sup>

$T_{A-IND} = -40^{\circ}C$  to +85°C,  $V_{CC} = 5 \text{ V} \pm 10\%$

|     |                                |                                                              | Preliminary                   |      |      |

|-----|--------------------------------|--------------------------------------------------------------|-------------------------------|------|------|

|     |                                | Parameter                                                    | 20 MHz                        |      |      |

| #   | Symbol                         | Description                                                  | Min                           | Max  | Unit |

| CLK | IN Require                     | ements—measurements taken with external clock input to X1 an | d X2 not connected (fl        | oat) |      |

| 36  | t <sub>CKIN</sub>              | CLKIN Period                                                 | 25                            |      | ns   |

| 37  | t <sub>CLCK</sub> <sup>2</sup> | CLKIN Low Time 1.5 V <sup>3</sup>                            | 7                             |      | ns   |

| 38  | t <sub>CHCK</sub> <sup>2</sup> | CLKIN High Time 1.5 V <sup>3</sup>                           | 8                             |      | ns   |

| 39  | t <sub>CKHL</sub>              | CLKIN Fall Time 3.5 – 1.0 V                                  |                               | 5    | ns   |

| 40  | t <sub>CKLH</sub>              | CLKIN Rise Time 1.0 – 3.5 V                                  |                               | 5    | ns   |

| CLK | OUT Timi                       | ng                                                           |                               | •    |      |

| 41  | t <sub>CICO</sub>              | CLKIN to CLKOUT Skew                                         |                               | 17   | ns   |

| 42  | t <sub>CLCL</sub>              | CLKOUT Period                                                | 50                            |      | ns   |

| 43  | t <sub>CLCH</sub>              | CLKOUT Low Time $C_L = 50 \text{ pF}^4$                      | $0.5 t_{CLCL} - 5 = 20$       |      | ns   |

|     |                                | $C_L = 100 \text{ pF}^3$                                     | 0.5 t <sub>CLCL</sub> -7 = 18 |      |      |

| 44  | t <sub>CHCL</sub>              | CLKOUT High Time $C_L = 50 \text{ pF}^4$                     | $0.5 t_{CLCL} - 5 = 20$       |      | ns   |

|     |                                | $C_L = 100 \text{ pF}^5$                                     | 0.5 t <sub>CLCL</sub> -7 = 18 |      |      |

| 45  | t <sub>CH1CH2</sub>            | CLKOUT Rise Time<br>1.0-3.5 V                                |                               | 8    | ns   |

| 46  | t <sub>CL2CL1</sub>            | CLKOUT Fall Time<br>3.5 – 1.0 V                              |                               | 8    | ns   |

<sup>1.</sup> All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50-100$  pF (10–20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup>  $t_{CLCK}$  and  $t_{CHCK}$  (CLKIN Low and High times) should not have a duration less than 40% of  $t_{CKIN}$ .

<sup>3.</sup> Tested under worst case conditions:  $V_{CC}$  = 5.5 V @ 20 MHz,  $T_A$  = 70° C.

<sup>4.</sup> Not tested.

<sup>5.</sup> Tested under worst case conditions:  $V_{CC}$  = 4.5 V @ 20 MHz,  $T_A$  = 0° C.

## **Clock Waveforms**

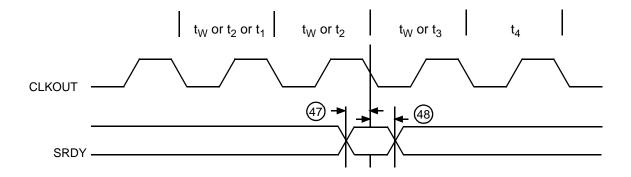

## Ready, Peripheral, and Queue Status Timings<sup>1</sup>

$T_{A\text{-IND}} = -40^{\circ} C$  to +85°C,  $V_{CC} = 5 \text{ V} \pm 10\%$

|      |                     |                                                              | Preliminary |     |      |

|------|---------------------|--------------------------------------------------------------|-------------|-----|------|

|      |                     | Parameter                                                    | 20 MHz      |     | 1    |

| #    | Symbol              | Description                                                  | Min         | Max | Unit |

| Rea  | dy and Pe           | ripheral Timing Requirements                                 |             | •   |      |

| 47   | t <sub>SRYCL</sub>  | SRDY Transition Setup Time <sup>2</sup>                      | 15          |     | ns   |

| 48   | t <sub>CLSRY</sub>  | SRDY Transition Hold Time <sup>2</sup>                       | 10          |     | ns   |

| 49   | t <sub>ARYCH</sub>  | ARDY Res. Transition Setup Time <sup>3</sup>                 | 10          |     | ns   |

| 50   | t <sub>CLARX</sub>  | ARDY Active Hold Time <sup>2</sup>                           | 10          |     | ns   |

| 51   | t <sub>ARYCHL</sub> | ARDY Inactive Holding Time                                   | 10          |     | ns   |

| 52   | t <sub>ARYLCL</sub> | ARDY Setup Time <sup>2</sup>                                 | 20          |     | ns   |

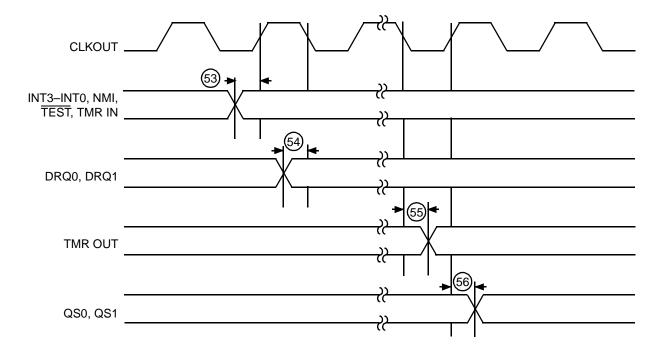

| 53   | t <sub>INVCH</sub>  | Peripheral Setup <sup>3</sup> : INTx, NMI, TMR IN, TEST/BUSY | 15          |     | ns   |

| 54   | t <sub>INVCL</sub>  | DRQ0, DRQ1 Setup Time <sup>3</sup>                           | 15          |     | ns   |

| Peri | pheral and          | d Queue Status Timing Responses                              |             |     |      |

| 55   | t <sub>CLTMV</sub>  | Timer Output Delay                                           |             | 22  | ns   |

| 56   | t <sub>CHQSV</sub>  | Queue Status Delay                                           |             | 23  | ns   |

#### Notes:

## Synchronous Read (SRDY) Waveforms

<sup>1.</sup> All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50-100$  pF (10–20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup> To guarantee proper operation.

<sup>3.</sup> To guarantee recognition at clock edge.

## Asynchronous Ready (ARDY) Waveforms

## **Peripheral and Queue Status Waveforms**

## RESET and HOLD/HLDA Timings<sup>1</sup>

$T_{A\text{-IND}} = -40^{\circ} C$  to +85°C,  $V_{CC} = 5 \text{ V} \pm 10\%$

|     |                    |                                         | Preliminary |     |      |

|-----|--------------------|-----------------------------------------|-------------|-----|------|

|     |                    | Parameter                               | 20 MHz      |     |      |

| #   | Symbol             | Description                             | Min         | Max | Unit |

| RES | ET and H           | OLD/HLDA Timing Requirements            |             |     |      |

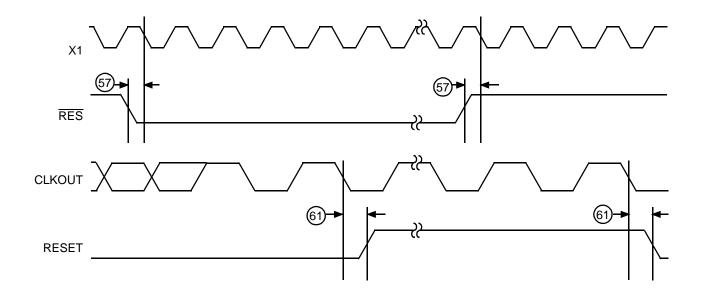

| 57  | t <sub>RESIN</sub> | RES Setup                               | 10          |     | ns   |

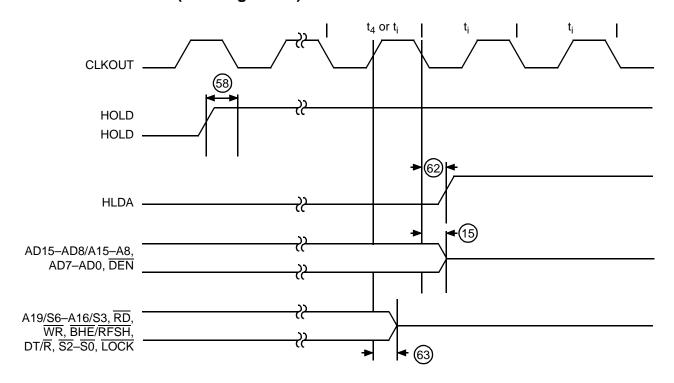

| 58  | t <sub>HVCL</sub>  | HOLD Setup <sup>2</sup>                 | 10          |     | ns   |

| 15  | t <sub>CLAZ</sub>  | Address Float Delay                     | 0           | 17  | ns   |

| 5   | t <sub>CLAV</sub>  | Address Valid Delay                     | 3           | 25  | ns   |

| RES | ET and H           | OLD/HLDA Timing Requirements            |             |     | •    |

| 61  | t <sub>CLRO</sub>  | Reset Delay                             |             | 22  | ns   |

| 62  | t <sub>CLHAV</sub> | HLDA Valid Delay                        | 3           | 22  | ns   |

| 63  | t <sub>CHCZ</sub>  | Command Lines Float Delay               |             | 25  | ns   |

| 64  | t <sub>CHCV</sub>  | Command Lines Valid Delay (after Float) |             | 25  | ns   |

#### Notes:

#### **RESET Waveforms**

<sup>1.</sup> All timings are measured at 1.5 V and 100 pF loading on CLKOUT unless otherwise noted. All output test conditions are with  $C_L = 50$ –100 pF (10–20 MHz). For AC tests, input  $V_{IL} = 0.45$  V and  $V_{IH} = 2.4$  V, except at X1 where  $V_{IH} = V_{CC} - 0.5$  V.

<sup>2.</sup> To guarantee recognition at next clock.

## **HOLD/HLDA Waveforms (Entering HOLD)**

## **HOLD/HLDA Waveforms (Leaving HOLD)**

#### **Trademarks**

© 1998 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am186, Am188, and E86 are trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.