## Am186ER/Am188ER AMD continues 16-bit innovation

Systems in Silicon

AMDLA Am186 ER

AMDA

Am186"ER

#### **386-Class Performance, Enhanced System** Integration, *and* Built-in SRAM

#### Am186ER and Am188ER

Systems in Silicon

AMD

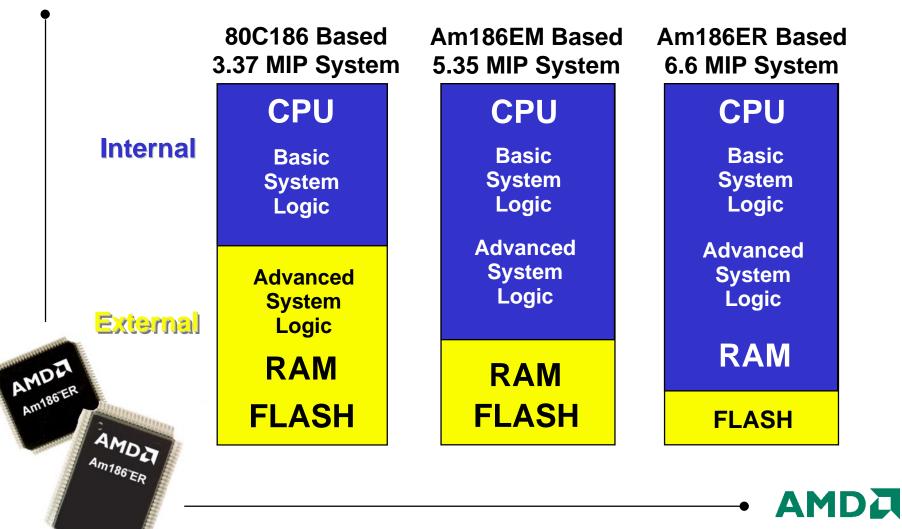

#### **Am186 System Evolution**

Systems in Silicon

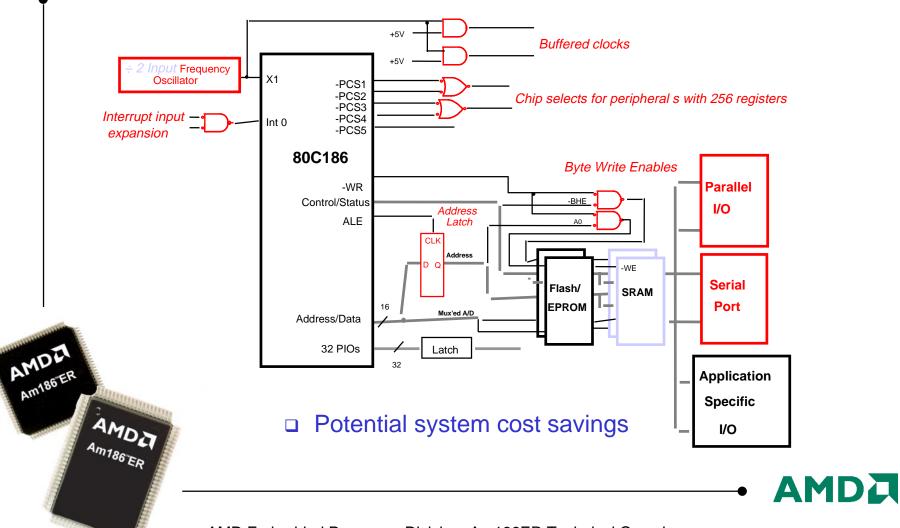

## **Typical 80C186 Design**

Systems in Silicon

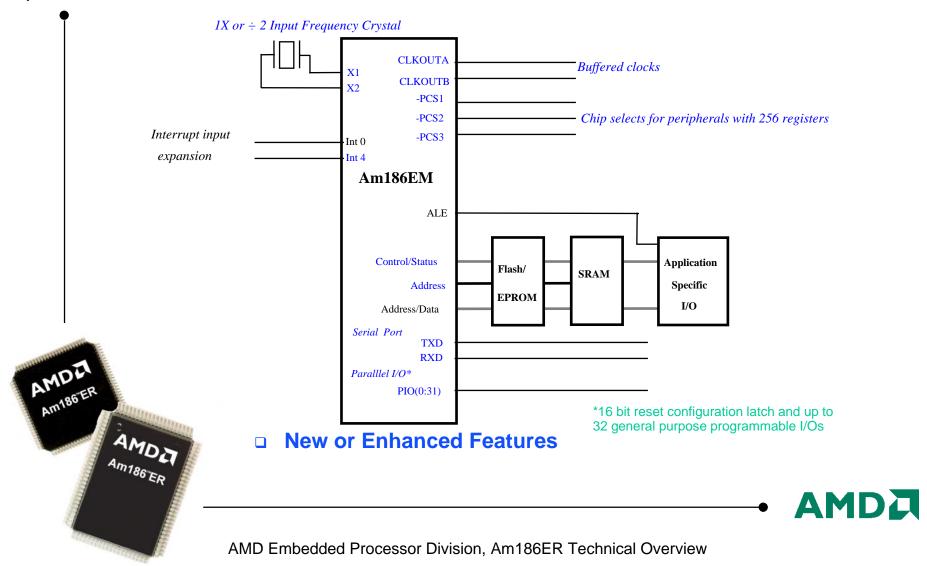

#### Typical 80C186EM Design (Glueless System Bus)

Systems in Silicon

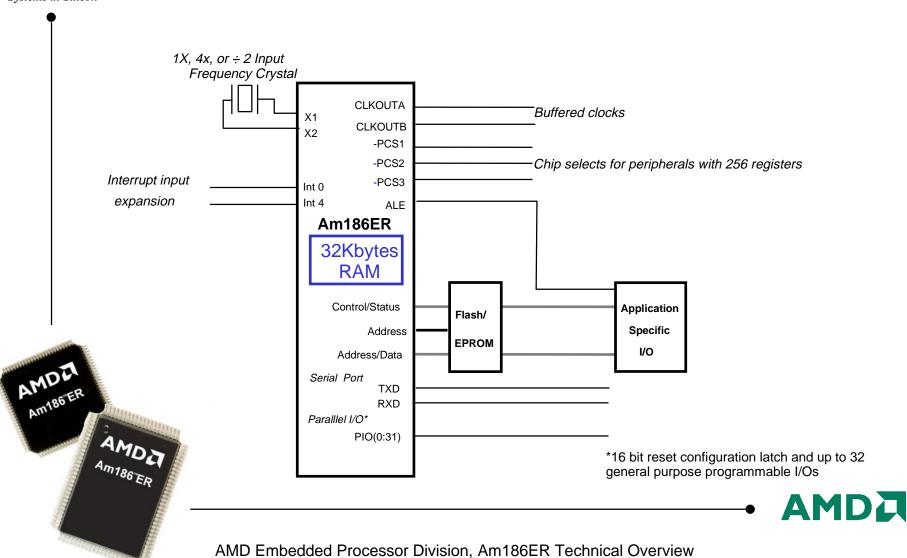

#### **Typical Am186ER Design** (Glueless System Bus & Integrated RAM)

Systems in Silicon

MD

m186"ER

## Am186/188ER vs. 80C186/188

- Software compatible with 80C186/188

- 25 to 50MHz

- Higher performance options

- Glueless connection to memory

- Lower system cost

- Demultiplexed address bus

- Zero wait state using commodity memories

- Use Am188ER to replace low frequency 80C186

- 25 MHz Am188ER equals12 MHz 80C186 performance

- Save on routing and space while using cheaper x8 components

m186"ER

## Am186/188EM vs. Am186/188ER

- No wait state internal RAM

- 16Kx16 for Am186ER, and 32Kx8 for Am188ER

- Visible for debugging

- Low Power

- 3.3v Vcc with 5V tolerant IO

- TTL compatible

- Integration of RAM reduces system power

- Multiple clocking modes

- $-\frac{1}{2}x$ , 1x, and 4x system frequency vs. input frequency

- Use a 12.5 MHz crystal for 50MHz system

- Same 100 pin TQFP and PQFP package/pinout

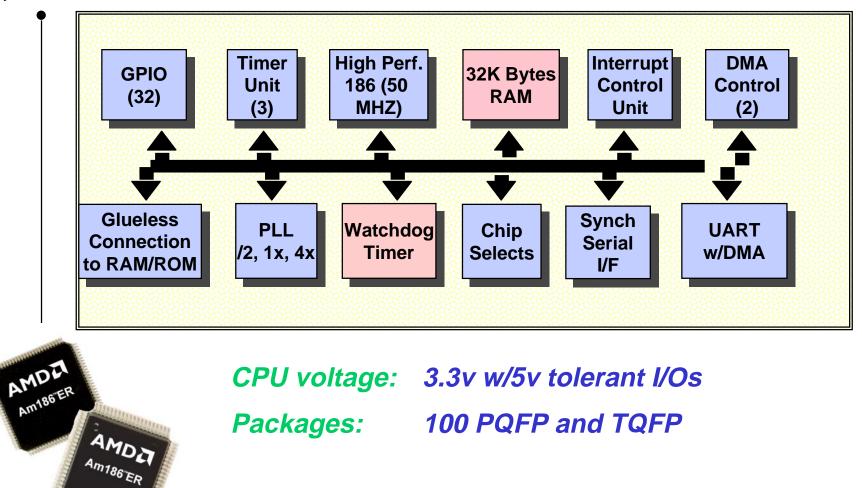

## **Am186ER Block Diagram**

Systems in Silicon

Systems in Silicon

#### **Am186ER and Am188ER Features**

## Am186/188ER New Features w/ Revision B

• Increased Performance - 50 MHZ - 6.6 MIPs

- DMA to/from asynchronous serial port

- Hardware Watchdog Timer

- Generates NMI or reset

m186"ER

## Am186/188ER Rev B Enhanced Features Con't

- Am186/188ER 40MHz max at Industrial Temp now available in both PQFP and TQFP

- PQFP 25, 33 & 40MHz at Industrial Temp available

- TQFP 25, 33 & 40MHz at Industrial Temp available

- If you are currently using an EM/EMLV or ES/ESLV and need to upgrade to a higher frequency industrial grade device (3.3V), consider the ER

Systems in Silicon

m186"ER

# Am186ER/188ER Feature Set

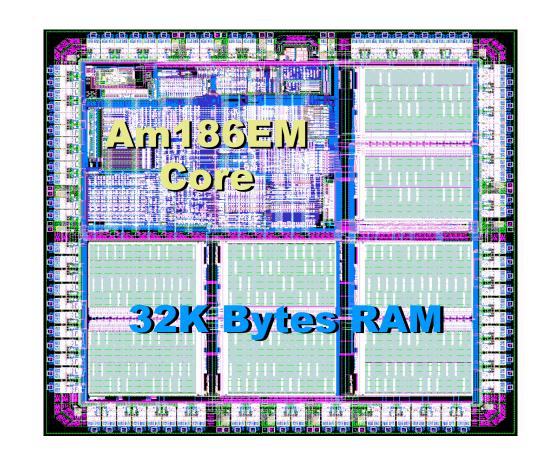

- 32K Bytes of integrated RAM

- Asynchronous and synchronous serial ports

- Glueless interface to ROM, SRAM, PSRAM and FLASH

- 32 programmable I/Os

- Interrupt controller with 13 interrupt sources

- 3 timers (with pulse width modulation)

- 2 DMA channels and 13 chip selects

- Integrated PLL

- two clockouts

- system frequency is /2, 1x, and 4x the input frequency

- Am188ER gives 60% of the performance of Am186ER

m186"ER

## **On-Board RAM**

16Kx16 for Am186ER and 32Kx8 for Am188ER

- Same performance as no-wait state external RAM

- Locatable on any 32 Kbytes Boundary

- Show reads on the address bus for easier debugging

- Externally displays data from internal RAM reads

- Show reads enabled in hardware or software

- Internal memory disable

- Disable with hardware or software

AMDE

Am186"ER

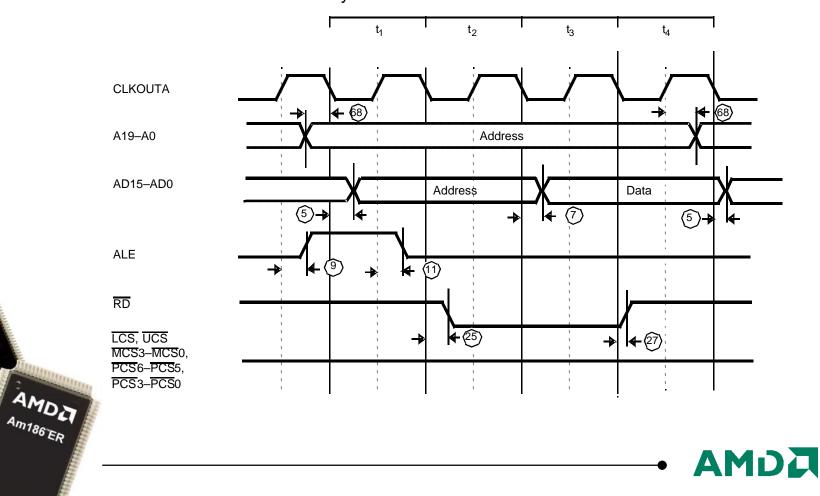

#### **Diagram of the Show Reads**

Internal RAM Show Read Cycle Waveform

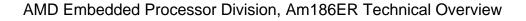

## **5V Tolerant I/Os**

Vcc on the Am186ER and Am188ER is 3.3V

- Inputs are 5V tolerant

- up to 2.6V over Vcc on inputs

- Outputs drive TTL Logic

- logic one to 2.4V

- Allows mixed voltage system

- Supports legacy 5V components

m186"ER

## **Clock and Power Management Unit**

• Up to 50 MHz speeds

- Clock options

- /2 for systems running lower than 20MHz

- 1x for systems running between 16 and 40MHz

- 4x for systems running between 16 and 50MHz

- 2 CLKOUT pins program options:

- Normal operating frequency

- Power save frequency

- Can be disabled

- Power save mode

## **PRL Register**

Systems in Silicon

- Used for code to identify product and revision

- Indicates the current release level of the processor

- Specifies either the 8 bit or 16 bit controller

- Revision B

- Am186ER = 28h

- Am188ER = 29h

Systems in Silicon

## **ER and EM Family: Common Features**

AMD

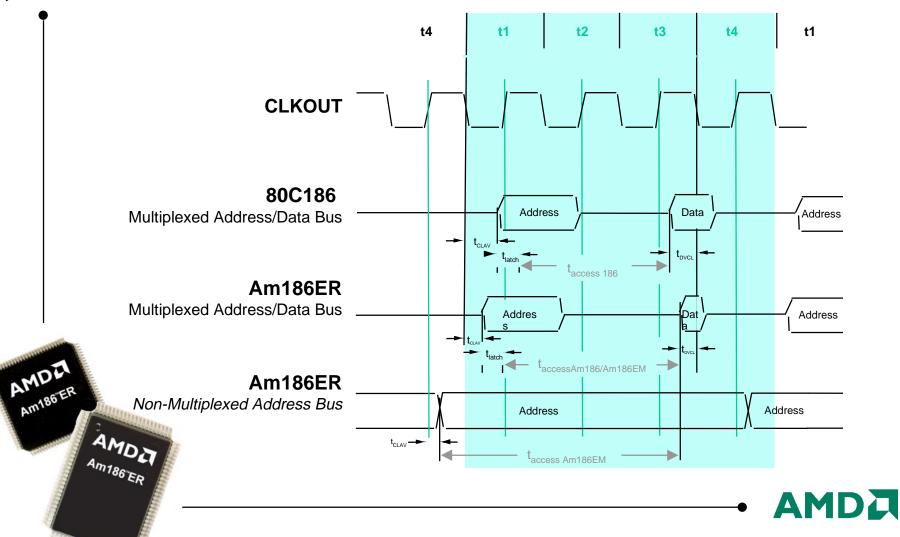

## **Demultiplexed Bus**

Systems in Silicon

AMD

m186"ER

- Am186ER demultiplexed address & data bus yields:

- Higher performance

- Address available time increased

- No ALE required

- Data setup time decreased

- Lower system cost

- Eliminates glue logic needed to latch memory address

- Using commodity memory reduces cost

- Multiplexed bus still supported for peripherals

#### **Demultiplexed Bus Interface**

Systems in Silicon

Am186"ER

## **Asynchronous Serial Port**

• Asynchronous protocol

- Full duplex, 7 or 8 bit

- Odd/even/no parity, 1 or 2 stop bits

- Interrupts

- Tx, Rx, Break

- Framing, parity, & overrun errors

- Baud rate generator

- div = (CLK Freq) / (32 \* Baud rate) 1

m186"ER

## **Synchronous Serial Interface**

- High speed serial transfers

- Up to 25 Mbits/s at 50MHz

- Half-duplex bi-directional

- ASIC or Mach<sup>™</sup> control

- Master with up to 2 slaves directly supported with enables

- more than 2 slaves supported with PIOs

- Operates in polled mode only

- SCLK at 1/2, 1/4, 1/8 and 1/16 CPU clock

m186"ER

## 32 Programmable I/O Pins

- Up to 32 PIO pins are available for I/O if their alternate functions are unused

- Input

- Input with weak internal pull-up/pull-down

- polarity depends on original pin

- Output

- Open-drain output

- Multiplexed with other signals

- Default depends on pin

- Read or written through the peripheral control block

## **16-Bit Reset Configuration Register**

Systems in Silicon

The reset configuration register function is to store data from the AD bus at reset. The illustration below demonstrates this.

systems in Suiton

# 80C186, EM, and ER Family: Common Features

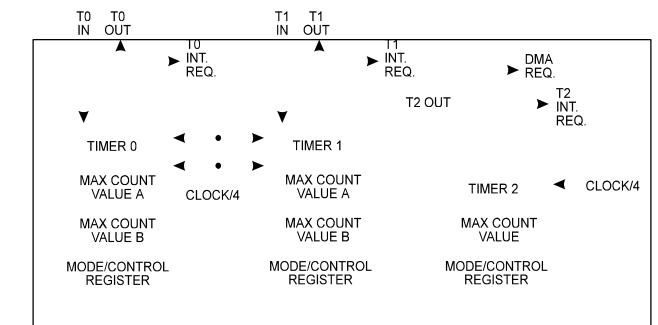

## **Three 16-bit Timers**

Systems in Silicon

m186"ER

- Same as the 80C186

- Watchdog timer functionality added to timer 1

- Supports pulse width modulation

- Can re-trigger on external events

- Continuous or one-shot count

- Can generate interrupt on terminal count

- Chainable interrupts

## **Three 16-bit Timers(cont.)**

Systems in Silicon

#### § Inside the line indicates I/Os internal to the timers

**Am186EM Features**

m186"ER

## **Chip Selects**

- 6 chip-selects (PCS) with a range of 256 bytes for use with peripheral devices

- Mapped to memory or I/O space

- 4 chip-selects (MCS) with a range of 2K to 128Kbytes

- 2 chip select outputs (UCS and LCS) for use in the top and bottom of memory map

- Good for system code and external RAM

- UCS is initial chip select after reset

## **Two DMA Channels**

Systems in Silicon

AMD

m186"ER

- Same as 80C186

- DMA options

- Mem-mem, mem-I/O, I/O-I/O

- byte or word

- 2 Bus cycles per transfer (read followed by a write)

- Interrupt after last transfer

- DMA channel priority

- DMA pointer increment/decrement/static

- Synchronization source/destination/none

## **DRAM Refresh Control**

Systems in Silicon

- Simplifies DRAM control logic

- Options

- Refresh request rate

- Enable/Disable refresh

- PSRAM refresh handled with separate pin

## **PIC - Peripheral Interrupt Controller**

Total of 13 interrupts

- 7 internal interrupts

- 3 timer interrupts

- 2 DMA interrupts

- asynchronous serial port interrupt

- watchdog timer interrupt

- 6 external interrupts

- 5 maskable interrupt pins

- 1 nonmaskable interrupt pin

- Edge or level sensitive

- Masked or slave mode options

## Hardware Watchdog Timer

Systems in Silicon

- Recover from software hangs

- Generates NMI or system reset

- 1.34 ns timeout at 50 MHz

AMD

## **PCB - Peripheral Control Block**

Systems in Silicon

- 128 contiguous 16-bit register

- Provides access to all internal peripherals

- Mapped anywhere in memory or I/O space

## ONCE Mode "On Circuit Emulation"

- Can be used for board testing

- Useful in debugging

- Tri-states all pins

- Activated by tying UCS & LCS low at reset

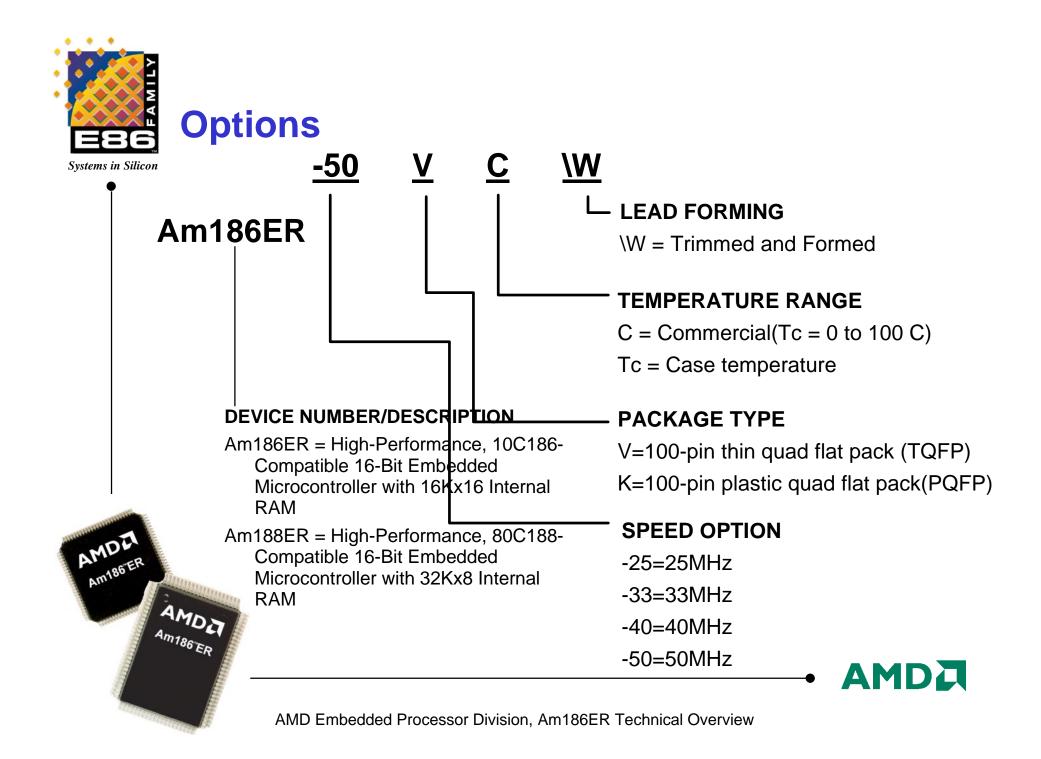

## Options and Timeline for the Am186ER and Am188ER Revision B

Schedule Am186/188 (Rev B)

- Announcement:

- Data Sheet (printed) :

- User's manual (printed):

- General Samples Available:

- Demo Boards Available:

- Production Starts:

March 31, 1998 March 31, 1998 March 31, 1998 May 1998 May 1998 3Q98

m186"ER

## Am186/Am188ER Notes

• The existing Am186/188ER is in full production.

- Rev B yields higher performance and more features.

- Design-ins should occur with Rev B silicon.

- Rev B is backward compatible with Rev A with only 1 exception.

- In external clocking configuration for an oscillator, X2 pin should float instead of being grounded as in Rev A. For a crystal configuration, no changes are required.

- This change was required to improve the oscillator.