## Cyrix<sup>®</sup> M II<sup>™</sup> Processor

# **Technical Brief**

## Architectural Overview

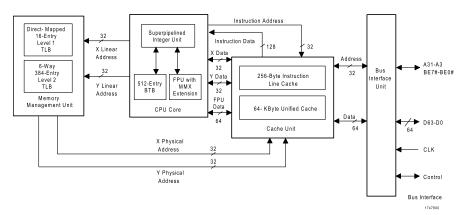

The M II<sup>™</sup> processor operates at higher frequencies than the previous 6x86MX™ processor. Based on the proven 6x86<sup>™</sup> processor core, the M II<sup>™</sup> CPU is superscalar in that it contains two separate pipelines that allow multiple instructions to be processed at the same time. It features a 64-KByte internal cache, a two-level TLB and a 512-entry BTB. The M II<sup>™</sup> processor also contains a scratchpad RAM feature, supports performance monitoring and allows caching of both SMI code and SMI data. It delivers optimum 16-bit and 32-bit performance while running Windows<sup>®</sup> 95, Windows NT,

OS/2<sup>®</sup>, DOS, UNIX<sup>®</sup> and other operating systems.

The M II<sup>™</sup> processor features a superpipelined architecture that increases the number of pipeline stages to reduce timing constraints and increase frequency scalability. Advanced architectural techniques include register renaming, out-oforder completion, data dependency removal, branch prediction and speculative execution. These design innovations eliminate many data dependencies and resource conflicts to achieve higher performance when executing both 16-bit and 32-bit software.

Dontium®

| Architectural Features           | Cyrix<br>M II <sup>™</sup><br>Processor | Pentium II<br>Processor | Pentium <sup>®</sup><br>Processor<br>with MMX <sup>™</sup><br>Technology |

|----------------------------------|-----------------------------------------|-------------------------|--------------------------------------------------------------------------|

| MMX Instruction Set              | X                                       | X                       | Х                                                                        |

| Superscalar                      | X                                       | X                       | Х                                                                        |

| Superpipelined                   | X                                       | X                       |                                                                          |

| Register Renaming                | X                                       | X                       |                                                                          |

| Data Dependency Removal          | X                                       | X                       |                                                                          |

| Multi-Branch Prediction          | X                                       | X                       |                                                                          |

| Speculative Execution            | X                                       | X                       |                                                                          |

| Out-of-Order Completion          | X                                       | X                       |                                                                          |

| 80-Bit Floating Point Unit       | X                                       | X                       | Х                                                                        |

| Primary Cache (Data+Instruction) | 64K (unified)                           | 16K+16K                 | 16K+16K                                                                  |

The M II<sup>™</sup> processor is a high performance CPU offering advanced processing on Windows<sup>®</sup> 95 and other operating systems. The M II<sup>™</sup> processor is compatible with MMX<sup>™</sup> technology to run the latest MMX games and multimedia software.

With its enhanced memory management unit, a 64-KByte internal cache, and other advanced architectural features, the M II<sup>™</sup> processor achieves high performance and offers better value than competitive processors.

# Cyrix<sup>®</sup> M II<sup>™</sup> Processor Technical Brief

# **Technical Specifications**

| Clocking                | 2x, 2.5x, 3x, 3.5x flexible core/bus clock ratios                                                                                                                                                    |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L1 Cache                | 64-KByte; write-back; 4-way associative;<br>unified instruction and data; dual port<br>address                                                                                                       |  |

| Bus                     | 64-bit external data bus; 32-bit pipelined address bus                                                                                                                                               |  |

| Pin/Socket              | Socket 7 pinout compatible (P55C)                                                                                                                                                                    |  |

| Compatibility           | Compatible with MMX <sup>™</sup> technology<br>and x86 operating systems including<br>Windows <sup>®</sup> 95, Windows NT, Windows,<br>OS/2, <sup>®</sup> DOS, Solaris, UNIX <sup>®</sup> and others |  |

| Floating Point Unit     | 80-bit with 64-bit interface; parallel<br>execution; uses x87 instruction set;<br>IEEE-754 compatible                                                                                                |  |

| Voltage                 | 2.9V core with 3.3V I/O                                                                                                                                                                              |  |

| Power Management System | Management Mode (SMM);<br>hardware suspend; FPU auto-idle                                                                                                                                            |  |

| Burst Order             | 1-plus-4 or linear burst                                                                                                                                                                             |  |

#### Bringing information to people — anytime, anywhere

www.cyrix.com Cyrix Corporation, 2703 North Central Expressway, Richardson, TX 75080 Tel 800 462 9749 94405-00 © May 1998 Cyrix Corporation. Cyrix is a registered trademark and M II, 6x86MX and 6x86 are trademarks of Cyrix Corporation, a subsidiary of National Semiconductor Corporation. MMX is a trademark of Intel Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders.

#### Cyrix U.S. Product Information

General Sales and Technical Support 800 462 9749 Sales and Technical Support Email: tech\_support@cyrix.com Web: www.cyrix.com/support

#### Channel Sales and Technical Support

Cyrix Direct Connect (U.S. Channel Program) 800 215 6823 Sales and Literature Orders 800 340 0953 Technical Support Email: direct\_connect@cyrix.com Web: www.cyrix.com/channel

### **Cyrix International Offices** Europe

European Cyrix Response Centre 44 (0) 1756 702815 Tel

Hong Kong National Semiconductor 852 2737 1800 Tel

France 0800 90 84 98 Tel

**Germany** 0130 813 839 Tel

United Kingdom 0800 137 305 Tel

Japan National Semiconductor Japan Ltd. 81 3 5639 7375 Tel

Korea National Semiconductor (Far East) Ltd. 82 2 3771 6900 Tel

China National Semiconductor Ltd. 86 10 6804 2453 Tel

**Singapore** National Semiconductor Asia Pacific Pte Ltd. 65 252 5077 Tel

**Taiwan** Cyrix International, Inc. 886 2 718 4118 Tel

South & Central America National Semicondutores da América do Sul 55 11 3043 7450 Tel