## Intel, Cyrix Reach P200 Level

Pentium Ships First But 6x86 Has Slight Performance Edge

by Linley Gwennap

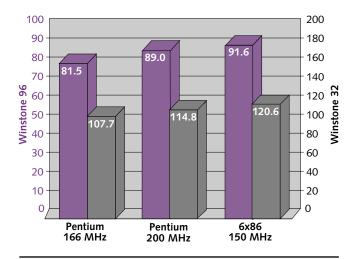

Underscoring the tight performance race between the two vendors, Intel and Cyrix extended the performance of their mainstream processors to the P200 level at nearly the same time. Intel's 200-MHz Pentium processor is available in volume immediately, offering a 7–9% performance boost over the Pentium-166, as Figure 1 shows. Cyrix's 150-MHz 6x86, which the company sells as the 6x86-P200+, will ship in limited quantities later this month, with volume production slated for August. Testing at MDR Labs revealed the Cyrix chip outperforms the newest Pentium by 3–5% on Ziff-Davis's Winstone 96 and Winstone 32 benchmarks.

Intel, of course, has been shipping 200-MHz Pentium Pro processors for several months, but given PPro's problems with 16-bit code, the new chips outperform PPro on the Winstone 96 benchmark, which includes popular 16-bit applications running under Windows 95. Although PPro is still the fastest processor on 32-bit applications, the Cyrix 6x86 delivers the most performance within the popular P54C pinout, giving PC makers an easy upgrade for their current systems.

#### Intel Takes P54C to the Limit

The 200-MHz speed grade represents the end of the line for the two-year-old P54C design, which recently surpassed Intel's 486DX2 as the best-selling PC processor of all time. Starting with the original 0.5-micron BiCMOS versions at 90 and 100 MHz, the company pushed the clock speed higher and higher over time through circuit tuning and a shrink to 0.35-micron BiCMOS, producing a version known as P54CS.

Getting the part to yield at 200 MHz was no small task. While a CMOS design will yield a small number of parts well above the center point of the clock-speed curve, BiCMOS parts have a narrower yield curve. Most of Intel's parts have been yielding at 150 to 166 MHz.

To reach 200 MHz, Intel has taken several steps. First, a combination of a few circuit changes to speed critical paths with some process improvements to reduce the effective gate

length moved the speed curve slightly higher. To further improve the operating frequency, Intel revived the VRE voltage specification for the Pentium-200, which requires a 3.45-V supply. This specification was used to improve the yield of early Pentium-100 chips. Increasing the voltage by 5% provides a similar improvement in clock speed.

A new plastic PGA package also helps the clock frequency. Instead of using the traditional ceramic substrate, the PPGA mounts the die on a standard PCB. The heat sink attaches to a heat slug mounted directly on the die, providing better thermal characteristics than a typical CPGA package, which has a layer of ceramic between the heat sink and die. With this arrangement, the die can operate at a higher temperature and thus tolerate a higher clock speed. Because it uses copper traces on FR4 rather than tungsten through ceramic, the PPGA has better electrical characteristics as well. Thus, the chip can run slightly faster. We believe the new package also reduces Intel's manufacturing costs.

Continued on page 6

**Figure 1.** On two PC benchmarks, the new 200-MHz Pentium outscores the Pentium-166 by 7–9%. Cyrix's new 150-MHz chip, dubbed the 6x86-P200+, is 3–5% faster than the Pentium-200. See article text for configurations. (Source: MDR Labs)

Inside: K5-PR100 AGP Spec PowerPC 401 Network Computers

#### AT A GLANCE

| Intel's Pentium and Cyrix's 6x86 are neck and neck, with both chips reaching 200-MHz performance levels this summer. The Pentium-200 boosts PC performance by just 7–9% over the 166-MHz version, reflecting the limits imposed by the 66-MHz Pentium bus. The 6x86 chip's more advanced microarchitecture and faster external bus help it to edge out Pentium's 200-MHz performance by a few percent while running at just 150 MHz. Cyrix's 75-MHz bus raises issues of compatibility with existing chip sets and motherboards, even as the company investigates pushing bus speeds higher. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Editorial: Intel's Competitors Stuck in Third Tier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Most Significant Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 401GF Is Coolest, Cheapest PowerPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AGP Speeds 3D Graphics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vendors Clash on Low-Cost Computers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Literature Watch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Recent IC Announcements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Patent Watch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chart Watch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

The next issue of Microprocessor Report will be delivered in four weeks, on July 15, due to a scheduled editorial shutdown.

#### **Publisher and Editorial Director**

Michael Slater E-mail: mslater@mdr.zd.com

#### **Editor in Chief**

Linley Gwennap E-mail: linley@mdr.zd.com

#### Senior Editor

Jim Turley E-mail: jturley@mdr.zd.com

#### Senior Analyst

Yong Yao E-mail: yyao@mdr.zd.com

#### Senior Analyst

Peter N. Glaskowsky E-mail: png@mdr.zd.com

Editorial Assistant: Suzanne Gifford

#### **Editorial Board**

Dennis Allison Rich Belgard Jeff Deutsch Brian Case Dave Epstein Don Gaubatz Bernard Peuto John Novitsky Nick Tredennick John F. Wakerly

#### **Editorial Office**

480 San Antonio Rd., Suite 210 Mountain View, CA 94040 Phone: 415.917.3050 Fax: 415.917.3093

Microprocessor Report is published every three weeks, 17 issues per year. Rates are: N. America: \$495 per year, \$895 for two years. Europe: £375 per year, £645 for two years. Elsewhere: \$595 per year, \$1,095 for two years. Additional copies in the same envelope: \$175 per year in North America, \$225 elsewhere. Back issues are available.

## Published by

President: Peter Christy E-mail: pchristy@mdr.zd.com

#### **Business Office**

874 Gravenstein Hwy. So., Suite 14 Sebastopol, CA 95472 Phone: 707.824.4004 Fax: 707.823.0504

**Subscriptions:** 707.824.4001

E-mail: cs@mdr.zd.com

World Wide Web: www.chipanalyst.com

Copyright ©1996, MicroDesign Resources. All rights reserved. No part of this newsletter may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without prior written permission.

Winner, Computer Press Award, 1993, 1994

Printed on recycled paper with soy ink.

## Intel's Competitors Stuck in Third Tier

### Taking On Intel's Design and Manufacturing Is Only the Start

Ever since the debut of the IBM PC 15 years ago, Intel has been the dominant force in microprocessors for personal computers. During this time, competitors have tried a variety of strategies to capture some of Intel's market share, with limited success. Today, Intel's position appears stronger than ever, and its challengers—whether x86 or RISC—are increasingly being forced to seek customers among third-tier PC makers to survive.

The challenges in competing with Intel are many. Intel's vast capital resources, the fruit of many years of highly profitable, high-volume microprocessor sales, have given the company a big lead both in the size and number of its design teams and the scale and sophistication of its manufacturing capability. Even if the formidable design and manufacturing hurdles can be overcome, however, Intel's competitors face another challenge: Intel's dominant position has given the company enormous clout that it can—and apparently does—use to engender grave doubts in the mind of any PC executive flirting with the idea of using competitive chips.

Consider the difficulty Cyrix and IBM have getting design wins for the 6x86. This chip delivers better performance than the fastest Pentiums on typical Windows applications, giving Cyrix—along with its foundry and marketing partners, IBM and SGS-Thomson—a strong product offering (see page 1). Yet Acer is Cyrix's only design win among leading PC makers.

There are some technical reasons that have contributed to Cyrix's difficulty in signing up big-name customers. The 6x86 is power-hungry, requiring substantially more cooling than Intel's Pentium, and its performance on floating-point code falls short. But the biggest challenge Cyrix and its partners face is Intel's clout with its customers—and the fear these customers have about how Intel may respond.

We have heard no first-hand accounts of Intel's conversations with its large customers. But sources at several of Intel's competitors describe a consistent pattern. When a PC maker shows serious interest in a non-Intel processor, the competitors say, a visit from Intel's top executives soon follows. They explain that using a non-Intel processor could affect the relationship between Intel and the PC maker, perhaps making Intel more cautious about revealing future product roadmaps or providing early silicon samples. The message that many PC makers seem to get—although it is presumably never stated—is the availability of leading-edge Intel processors might also be affected.

Intel is well aware, of course, of its dominant position and the obligations that accompany this position if the company is to stay clear of antitrust-law violations. Intel surely has top-notch legal advice and would not carelessly endanger its position with strong-arm tactics. But the irony is there is no need for Intel to use such tactics—so many people in the industry assume that Intel would find ways to retaliate against companies using competitive processors that no threats are necessary.

Given the widely held fear that using a competitive processor could impact a PC maker's ability to get leading-edge processors from Intel, the competitors' lack of a full product line limits the prospects for the chips they do have. Cyrix—and some day AMD—might offer a good desktop solution, but what about the portable line, where power consumption is key? What about servers, where Pentium Pro with its multiprocessor-ready bus is needed? No competitor can match Intel's product spectrum today. It is possible that AMD will have a good notebook processor in 1997, but it is unlikely that it will have chips with multiprocessor capabilities matching Intel's P6 family.

The view PC makers take of the alternatives varies, but they can be divided into three broad categories. The Intel Loyalists, such as Dell, Gateway, and Packard-Bell, are unlikely to seriously consider alternative processors anytime soon. The best long-term prospects for Intel's competitors are the Big Independents—companies such as Compaq, Acer, AST, and even HP, which are confident enough to risk Intel's ire and want to reduce Intel's influence over their product directions. These companies also seek to use their R&D efforts to differentiate their products from those of the Intel Loyalists; one approach is to use some non-Intel processors. So far, these companies have used non-Intel processors mostly in low-end products, but once high-speed 6x86 chips are available in high volume, this could change. Compaq has retreated from alternative processors for now, but this change appears to have been driven more by the lack of volume availability than by any newfound love for Intel.

In the meantime, most of the volume for Intel's competitors will come from the Countless Unknowns—the great masses of PC makers whose names are largely unknown but which collectively ship a significant fraction of the industry's computers. While unglamorous, this market is big enough for the alternative processor makers to succeed on a modest scale while they continue preparing for future assaults on the top tier.

MilalSato

#### Sun Signs Four Java Chip Makers

Sun Microelectronics has announced the first four intended licensees for Java microprocessors. LG Semicon, Mitsubishi, NEC, and Samsung are expected to begin manufacturing Java chips for both commercial use and internal consumption in 1997.

None of the four companies is yet a licensee; each has signed a "memorandum of understanding" avowing interest in the Java chips, but the details of each license agreement are still being negotiated. Assuming all goes well, each vendor will receive from Sun a design package including RTL models, simulation tools, test vectors, and other deliverables.

All four potential licensees have several characteristics in common: large manufacturing capacity, a brand name in consumer electronics, a major market presence and distribution channel, and commitments to use Java chips for internal consumption. This strategy was deliberate, and Sun expects to increase the ranks of Java-chip manufacturers within a few months, adding vendors from the U.S., Europe, Taiwan, and Japan. We believe Philips, Motorola, Toshiba, and Hitachi may be among the second-round candidates.

Part of the licensee selection criteria involved commitments for substantial internal consumption. None of the four companies has said publicly what they intend to do with their Java chips, apart from some musings regarding cellular telephones, intelligent home appliances, and network computers.

Currently, Sun is licensing only the PicoJava core, not the peripheral logic or bus interface used on MicroJava (see MPR 2/12/96, p. 4). Each licensee will develop its own application-specific implementations, possibly competing head-on with Sun's own versions of MicroJava. At this stage, Sun is more interested in seeding the market with Java processors (and collecting royalties therefrom) than in dominating the market with its own implementations.

Each of the licensees already has at least one embedded microprocessor line, although each emphasized that the Java core was not intended to replace any current product line. Mitsubishi, for one, recently launched its new embedded CPU/DRAM family with the M32R/D (see MPR 5/27/96, p. 10). Since all four vendors are major memory producers, future chips that merge a PicoJava core with substantial amounts of on-chip DRAM might not be far off.

Separately, Sun announced the first customer for Java chips: Northern Telecom. The telecommunications giant plans to embed Java processors in future telephones for home and business use. These telephones would be able to access the Internet in addition to their standard functions, so the Java chips would be useful in executing downloaded content. The Java phones are expected to begin appearing next year. Given the interest level of four major chip makers, more customers must be in the pipeline.

#### ■ AMD Boosts K5 to 100 MHz

As both Intel and Cyrix announced parts with Pentium-200 performance (see cover story), AMD has just reached the 100-MHz level with its K5 processor. The company reaches this milestone a bit ahead of schedule; when it announced its 90-MHz K5 (see MPR 3/25/96, p. 1), AMD expected volume shipments of the 100-MHz version in 3Q96.

The company has changed its nomenclature for the device. Originally code-named the K5, the part was first announced as the 5K86. Now the company has backtracked, using K5 as the official product name. AMD continues to compare its parts to Intel's using the P-rating system, but it now uses the suffix PR instead of merely P. (Cyrix continues to use the P suffix.) Thus, AMD's new chip is known as the K5-PR100, with performance similar to that of a 100-MHz Pentium processor.

The PR100, now shipping in volume, is priced at \$84 in quantities of 1,000, a whopping 37% below Intel's list price for the Pentium-100. AMD is committed to delivering its K5 chips for at least 25% less than Intel's prices. The company has cut the price of its K5-PR90 to \$67 and the K5-PR75 to \$55. These prices mirror the relatively small gaps between Intel's Pentium pricing at 75, 90, and 100 MHz.

Moving to the Pentium-100 level ahead of schedule helps AMD, but the gain is not enough to propel it above the \$100 price point. In fact, the price of AMD's best K5 chips has dropped from \$99 to \$84 in less than three months, despite the clock-speed boost. At these prices, profitability for AMD's chips is poor, and the company is restricted to the lowest-price portion of the market, preventing it from gaining significant share.

The next step for the K5 is a new version that AMD expects to boost per-clock performance by 20%. The company plans to ship this enhanced K5 by September. With Intel moving the low-end market to the Pentium-120 by the end of the year, AMD needs this version to keep pace and perhaps even get prices into three digits again.

#### First PA-8000 Workstations Appear

After a three-year hiatus, HP is again shipping the industry's fastest workstations. The HP9000 Model C180-XP, using a 180-MHz PA-8000 processor with 1M of instruction cache and 1M of data cache, delivers 10.8 SPECint95 and 17.2 SPECfp95 (base), surpassing the fastest Alpha workstations from Digital. The HP system has an entry price of \$49,850 in a configuration with 32M of memory, a 2G disk, and a 17" color monitor. The company also offers a 160-MHz system, appropriately called the Model C160, that has an entry price of \$22,520.

These systems are the first workstations from HP to include PCI expansion slots. HP sells PCI-based personal computers and can now use the same PCI cards in both

product lines. IBM and Digital, which both also have PC and workstation lines, also offer RISC workstations with PCI slots. The HP workstations do not, however, take advantage of any PCI-based devices on the motherboard. In the future, HP may be able to lower its build costs by using standard PC chips for basic I/O and networking functions.

The company also formally announced K-class servers using the PA-8000, which it has been shipping since April (see MPR 4/15/96, p. 4). The HP9000 K260 and K460 support up to four 180-MHz processors and come standard with 128M of memory. Prices start at \$62,245. Because these systems are designed with many banks of memory, SPECfp95 performance is slightly better than on the C180; the K460, with 32way interleaved memory, rates at 18.3 SPECfp95 (base). The SPECint95 score, which mainly focuses on CPU-cache interaction, is unaffected by this change to main memory.

The photo at right shows the PA-8000 chip mounted to a daughterboard with dual external 1M caches. To support the two 128-bit data paths to the caches plus tag bits, control signals, and the 64-bit system bus, more than 1,000 connections are required between the die and board. Many of these connections carry power; the PA-8000 consumes well over 40 W peak. (The company would not provide more precise figures.) Instead of using an extremely expensive PGA package, HP mounts the die to the board using flip-chip attachment, completely eliminating the package.

The new announcements are a huge step forward for HP, raising the SPECint95 performance of its high-end workstations by more than 2.5× in one fell swoop. The company gained prominence in the workstation industry in the early 1990s by grabbing the performance lead with its original PA-RISC systems, but HP lost the workstation performance lead to Digital in 1993. The PA-8000 overcomes the disappointment of the PA-7200 and thrusts HP back into the spotlight. It may be difficult to stay there, however; Digital continues to aggressively push the clock speed of its Alpha chips and is likely to surpass HP's performance soon.

#### ■ TI Promotes 0.25-Micron Effort

In a widely publicized nonannouncement, Texas Instruments hyped its forthcoming 0.25-micron CMOS process. The company believes this process, which it refers to by its effective gate length of 0.18 microns, will eventually enable chips with as many as 125 million transistors. Even with such an advanced process, such a design would be quite large,  $19 \times 19$  mm, and expensive to build. Furthermore, the only way to reach such high transistor counts would be to devote most of the transistors to memory. Intel, for example, today builds a 30-million-transistor cache chip for the Pentium Pro in 0.35-micron CMOS.

The new process is a future derivative of TI's EPIC-4 process (see MPR 7/10/95, p. 16). The company is currently sampling UltraSparc-2 processors built in a 0.29-micron version of EPIC-4 and expects these parts to reach production in 3Q96. The first products in the 0.25-micron process are

#### Few Newsletters Misprinted

A few subscribers have noted that their copies of Microprocessor Report arrived recently with missing or duplicated pages. We are working with our bindery to solve this problem and do not expect any such errors in the future. If you have received any newsletters with printing errors, please contact our customer service department (see page 2); we will be happy to send you a corrected copy. Thanks for your support.

scheduled to sample late this year, with volume production in 1H97. The company did not disclose specific product plans, but the first devices are likely to be versions of Ultra-Sparc-2 and TI's multiprocessor MVP DSP. Neither of these chips is likely to approach 125 million transistors.

Of course, many other vendors are also developing quarter-micron processes. If TI can stick to its schedule, it may be one of the first to reach this milestone; Intel, for example, does not expect to ship 0.25-micron parts until 2H97. These advanced fabrication processes will certainly give chip designers a significant increase in transistor count to play with. But don't expect a 100-million-transistor CPU chip in the next few years.

#### Sigma Launches MPEG-1 for Video CD

Sigma Designs (Fremont, Calif.), formerly a graphics-board vendor, has recently redirected its business to become a multimedia component supplier. The RealMagic EM8000 is the first product released under this new guise.

The EM8000 is the first chip to integrate MPEG-1 audio and video decoding plus X-Y scaling in a single device. Based on horizontal and vertical bilinear interpolation, the Sigma chip's proprietary video-scaling scheme permits the display of a clear video image in sizes ranging from a postage stamp to a full screen.

This chip is well designed for video CD players. These devices are popular in Asia, where they are used as karaoke machines and movie players, but they have seen little action in other geographical areas. Within one or two years, these systems will be obsoleted by DVD players.

The chip also has a glueless interface to the ISA bus, enabling EM8000 PC add-in cards. These would be most useful in older PCs, as most recent Pentium systems can perform MPEG-1 decoding in software.

Sigma offers a reference design to OEMs with a complete turnkey manufacturing kit. The EM8000 is sampling now, with full production expected in 3Q96. The unit price is \$41 in 1,000-piece quantities. This price is a bit expensive, even for the level of integration offered; MPEG-1 video decoders sell for \$25 or less, and audio is easily handled by the host CPU. The EM8000 will be more useful in a standalone video system than a PC.

### P200

Continued from page 1

The PPGA package fits into the same socket as the CPGA Pentium and uses similar heat sinks, so board makers should be able to interchange the two parts. One proviso: the board must be designed to deliver the VRE voltage level, which is tolerable to non-VRE Pentiums as well. Intel will offer the 200-MHz Pentium only in the PPGA package; the Pentium-166 will be offered in the PPGA as well as the standard CPGA. Intel is likely to use the new package for other high-speed parts in the future.

The 200-MHz clock speed pushes power dissipation to 15.5 W (maximum) at 3.45 V. The faster clock also improves performance to 5.5 SPECint95 and 2.9 SPECfp95 (base). This integer score is slightly better than that of the 200-MHz 603e (see MPR 5/27/96, p. 13), but the FP score lags the PowerPC chip's.

#### **Bandwidth Problem Looms**

Achieving even higher clock speeds from the current Pentium design will not be possible. Intel's next process shrink is to a 0.28-micron process (see MPR 7/10/95, p. 16), but this process eliminates bipolar devices, requiring a pure CMOS design. Intel is working on a new design, the P55C, that utilizes the 0.28-micron CMOS process, but it is not expected to ship until late this year. It isn't clear whether even the P55C will exceed 200 MHz, as the missing bipolar transistors may offset the gain from the gate shrink and the new process makes no improvements to the critical metal layers.

The P55C addresses one key problem with the P54C design: the current chip has run out of bus bandwidth. The 200-MHz Pentium runs at three times the clock speed of the original Pentium yet uses the same 66-MHz bus. This bottleneck has been exacerbated over the past few years by the increased size and complexity of typical application software. As a result, the Pentium-200 scores just 9% better than a Pentium-166 on Winstone 96 despite a 20% faster clock. A 180-MHz Pentium, with just a 60-MHz bus, would do worse than a Pentium-166, which is why Intel skipped that speed grade.

The P55C doubles the size of the on-chip caches, to 16K for instruction and 16K for data, reducing the number of external cache accesses. This change, combined with minor improvements over the P54C pipeline, will give the P55C-200 about 15% better performance than the Pentium-200, according to Intel. The performance improvement at lower clock speeds may be less.

#### Short Lifespan for Pentium-200

Intel is selling the Pentium-200 for \$599 in quantities of 1,000, a 20% premium over the Pentium-166 despite the relatively modest increase in performance. We expect this price to drop to about \$450 by the end of the year. Once the P55C is available, the Pentium-200 will disappear fairly quickly, perhaps as soon as mid-1997.

We expect Intel to offer aggressive pricing on the P55C, phasing out the Pentium-200, for two reasons. First, the P55C includes Intel's new MMX multimedia instructions (see MPR 3/5/96, p. 1), which the company wishes to move into the PC mainstream as quickly as possible. Second, we do not believe the speed yields on the P54C design at 200 MHz are adequate to support the volumes required to move that device into the sub-\$300 portion of the market. Thus, the Pentium-200 is simply a bridge product filling the gap between the Pentium-166 introduction in January and P55C production late this year.

#### Cyrix Improves Bandwidth with 75-MHz Bus

Due to its more efficient microarchitecture, Cyrix's new part exceeds the performance of the Pentium-200 while operating at just 150 MHz. To achieve this performance, Cyrix has pushed the bus speed of its part to 75 MHz; Pentium, in contrast, is limited to 66 MHz. This change improves the bandwidth to the rest of the system by 14%, easing the bottleneck seen by the 200-MHz Pentium.

Cranking up the bus speed, however, can make life more difficult for the motherboard designer. Cyrix is working closely with chip-set and motherboard vendors to enable the 75-MHz bus speed. VLSI Technology announced that its Lynx chip set, available today, will support the 75-MHz bus. This chip set operates the PCI bus asynchronously, allowing it to remain at 33 MHz. The faster bus speed, however, requires more expensive cache SRAMs.

Cyrix expects Opti, SiS, and VIA to add 75-MHz system-bus support to their Pentium chip sets in the near future; none of these vendors has committed to this plan. Motherboards supporting the 75-MHz bus are available from Diamond Flower, Inc. (DFI), with First International Computer (FIC) expected to become a second source.

The 150-MHz 6x86 does not support the  $2.5\times$  clocking mode found in Pentium, which would have allowed a 60-MHz bus. It does support a  $3\times$  clocking mode, but Cyrix is discouraging its use, as this configuration would not match a Pentium-200 in performance. Thus, potential 6x86-P200+customers are limited to a single chip set and a single mother-board vendor today, with the possibility of a small number of vendors in the future.

The company is investigating pushing the bus speed even further, to 83 MHz. This increase would support a 166-MHz 6x86 that could be deployed in 4Q96, maintaining the 2× ratio. Without the faster bus speed, however, the 166-MHz version would offer no better performance than the 150-MHz part, so there would be little point in offering it. An 83-MHz system bus is challenging but possible.

#### Cyrix Reaches 0.44 Microns

To achieve 150 MHz operation, Cyrix, along with fab partner IBM, developed a 0.44-micron version of the 6x86 built in a variant of IBM's CMOS-5S process called CMOS-5S2. This device is a 10% optical shrink of the 0.5-micron version

Cyrix plans to move most of its production to the shrunk part, which also improves yield at the lower frequencies while reducing cost. The 6x86 remains far more expensive to produce than Pentium, which we estimate costs just \$40 to manufacture. By focusing its efforts on products that sell for \$300 and up, however, Cyrix makes this cost difference acceptable.

Cyrix has priced its 6x86-P200+ at \$499 in quantities of 1,000. IBM is also selling the P200+ under its own label, at a 1,000-piece list price of \$479. These prices are 20% or more below Intel's Pentium-200 price, but this gap is not really meaningful. Intel is scheduled to reduce its prices on July 29, about the time the P200+ reaches volume production; we expect the Pentium-200 will be much closer to Cyrix's \$499 price by the time most vendors can buy the 6x86.

Cyrix is also working with its second foundry partner, SGS-Thomson, which has not yet been able to ship any 6x86 parts in volume. SGS-Thomson's Phoenix (Ariz.) fab is now producing samples of the 6x86, and the vendor expects to put these parts into production in 2H96.

As part of its system effort (see MPR 4/15/96, p. 4), Cyrix is selling 6x86-P200+ PCs, promising shipments by the end of this month. The base price for these systems is \$2,699 in a configuration that includes a 256K pipelineburst cache, 16M of EDO memory, a Matrox Millennium graphics card with 2M of WRAM, 2.5G hard drive, 8× CD-ROM, 15-inch monitor, speakers, and Windows 95.

Cyrix measured a high-end configuration, which included a 4G SCSI-2 disk with 64M of cache, at 100.5 on the Winstone 96 benchmark. This score is the highest ever published on that metric, including ratings for Pentium and Pentium Pro systems, although Pentium Pro might do better if tested with such a disk controller. Cyrix's record-breaking configuration is on the price list at \$4,999.

#### Cyrix M2 to Duel Klamath

In early 1997, Cyrix plans to debut its next design, codenamed M2. This device will retain the proven 6x86 processor core but quadruple the size of that chip's unified L1 cache to 64K, twice as much on-chip cache as the P55C. The greatly expanded cache will help overcome the bandwidth limitations of the Pentium bus.

Combined with the greater efficiency of the 6x86 CPU core, the new cache should help the M2 achieve better performance than the P55C. Sticking with the current pinout provides PC makers the option of extending the lifetime of their Pentium-based motherboards by moving to the M2.

The M2 will debut in IBM's 0.35-micron CMOS-5X process, which should allow clock frequencies of 180 and 200 MHz. We expect a subsequent shrink to the 0.27-micron CMOS-6S process in 2H97, boosting M2 speeds to 225 and

#### Price & Availability

Intel's 200-MHz Pentium is available now at a 1,000-piece list price of \$599. For more information, contact your local Intel sales office or check the World Wide Web at www.intel.com. For specific information on the plastic PGA package, request document 243103-001 from the Intel Literature Center at 800.548.4725.

The 6x86-P200+ is available in limited quantities now, with volume production slated for early August from both Cyrix and IBM. Cyrix's list price is \$499 in quantities of 1,000. IBM's price is \$479 in the same quantities.

Contact Cyrix (Richardson, Texas) at 214.968.8388; fax 214.699.9857 or check the Web at www.cyrix.com. Contact IBM Microelectronics through its fax-back service at 415.855.4121 or via the Web at www.chips.ibm.com.

250 MHz; these parts would use a 75- and 83-MHz bus, respectively, for best performance. If Cyrix can deliver parts on this timetable, the M2 should be comparable in 16- and 32-bit integer performance to Intel's Klamath, a P6-family part expected to roll out early next year.

We believe the performance of the 6x86 core will begin to suffer at speeds above 200 MHz, even with the larger cache, due to the limited bus bandwidth. Cyrix, within the Pentium pinout, will find it difficult to match the performance of Intel's 300-MHz P6 (code-named Deschutes), expected to ship by the end of 1997. The 6x86 core might deliver better performance by moving to a new pinout, perhaps retaining the Pentium bus interface but adding a new L2 cache bus. Cyrix, however, does not expect to adopt a new pinout until its M3 processor, due in 1998.

#### Cyrix Adopts MMX

A key enhancement of Klamath over Pentium Pro is the addition of MMX support. To match Klamath, Cyrix has added MMX to the M2 as well. The company had initially developed its own set of multimedia instructions for M2, but when both Intel and AMD adopted MMX, Cyrix realized it had no choice but to offer compatible instructions. The company says converting to MMX added only 30–60 days to the M2 schedule, a small price to pay for compatibility.

Unlike AMD, Cyrix has not licensed MMX from Intel. From a legal standpoint, Cyrix's ability to implement these instructions should be no different from its current implementation of other x86 instructions. Presumably, its use of Intel-licensed foundries—IBM and SGS-Thomson—should protect its MMX designs.

Cyrix based its MMX implementation on public information about the new instructions. It remains to be seen whether this implementation will be fully compatible with Intel's. When Cyrix delivered its first Intel-compatible processor, the x86 instruction set had been relatively well

|             | Intel P            | entium | P200        | 6x86       | 6x86        |  |

|-------------|--------------------|--------|-------------|------------|-------------|--|

|             | 166 200<br>MHz MHz |        | vs.<br>P166 | 150<br>MHz | vs.<br>P200 |  |

| Winstone 96 | 81.5               | 89.0   | 9.2%        | 91.6       | 2.9%        |  |

| Graphics    | 8.0                | 8.6    | 7.5%        | 8.7        | 1.2%        |  |

| Database    | 9.3                | 10.2   | 9.7%        | 10.5       | 3.6%        |  |

| Spreadsheet | 7.5                | 8.2    | 9.3%        | 8.5        | 3.7%        |  |

| Word Proc.  | 8.2                | 9.0    | 9.8%        | 9.3        | 3.0%        |  |

| Winstone 32 | 107.7              | 114.8  | 6.6%        | 120.6      | 5.1%        |  |

| Graphics    | 9.3                | 9.7    | 4.3%        | 9.9        | 1.7%        |  |

| Database    | 13.5               | 14.7   | 8.9%        | 15.4       | 4.3%        |  |

| WP/SS       | 10.6               | 11.4   | 7.5%        | 12.2       | 6.4%        |  |

**Table 1.** Cyrix's 6x86-P200+, which runs at 150 MHz, slightly outperforms Intel's Pentium-200 on PC application benchmarks. See article text for configuration details. (Source: MDR Labs)

documented for years. The startup discovered several "holes" in this documentation only through extensive testing of Intel's own processors, and since then the Cyrix designs have had no significant compatibility issues.

Bringing out its MMX processors just a few months after Intel's raises the level of risk. Cyrix will have little, if any, opportunity to test Intel's MMX processors before finalizing the M2. Without this testing, the possibility of a compatibility problem is greater. MMX is much simpler than the rest of the x86 architecture, however, minimizing this risk.

Another issue for Cyrix is that it will have no MMX-enabled part that matches well against the P55C. The M2 should exceed the performance of the P55C, positioning it against Klamath. That would leave the current 6x86 to take on the P55C. If the market demands MMX at the P55C price points, Cyrix may choose to offer low-speed versions of the M2 instead. By 2H97, however, P55C prices will fall below \$300, removing this problem from Cyrix's radar screen.

#### Cyrix Gains on 16-Bit and 32-Bit Applications

MDR Labs measured the performance of both the 200-MHz Pentium and 150-MHz 6x86 on two PC application suites: Ziff-Davis's Winstone 96 and new Winstone 32. Winstone 96 is a popular metric that consists of a variety of 16-bit PC applications that we ran under Windows 95. Winstone 32, which we also ran under Windows 95, contains only 32-bit (Win32) PC applications.

Because the two chips use different system bus speeds, it was impossible to run them in the same motherboard for the best comparison. We tested the 6x86 in a DFI board using the Lynx chip set, which is the only available chip set that supports a 75-MHz bus. Although this board can be configured at 66 MHz for the Pentium-200, we measured the Intel chip in a Tyan motherboard using Intel's 430HX (Triton II) chip set, which delivers better performance than Lynx for the Pentium processor. For comparison, we also tested a Pentium-166 in the same Tyan motherboard.

Other than these differences, the two test systems were as identical as possible. They both included 256K of pipeline-burst cache, 32M of EDO DRAM, a Seagate Barracuda 2G

disk connected through an Adaptec SCSI adapter, and a Matrox Millennium graphics card with 2M of WRAM. Measurements were taken with the graphics card set for  $1024 \times 768 \times 8$ -bit resolution.

The data in Table 1 shows the 150-MHz 6x86 outperforms the 200-MHz Pentium by 2.9% on Winstone 96 and 5.1% on Winstone 32. The Cyrix chip consistently outscores the Pentium, coming out ahead on every component of each metric. Except for the business-graphics component in both suites, the Cyrix chip wins by 3.0–6.4%. (A complete report is on the Web at *www.chipanalyst.com.*) None of these tests contains significant amounts of floating-point code, on which the 6x86 is slower than Pentium.

End users are unlikely to perceive such small differences in performance. But given the relatively small gap between the performance of the Pentium-200 and the Pentium-166, the 6x86's edge appears more significant, particularly on 32-bit code.

#### **Cyrix Strategy Raises Socket Issues**

Over the past few months, Cyrix has demonstrated that its 6x86 can match Intel's fastest Pentium on mainstream PC applications, and the company has responded well to Intel's first attempt to restore a performance gap. We expect Cyrix to continue to stay close to the PC application performance (except for 3D graphics) of Intel's top parts for at least the next year, moving to the M2 as Intel moves to Klamath.

A key difference between these two P6-class parts will be the pinout. Both Cyrix and AMD will try to extend the performance range, and thus the life, of the P55C socket with the M2 and K6, respectively. Staying with the P55C socket will help PC makers in the short term, but moving to the Klamath pinout will provide much more performance headroom in the long term. Intel's competitors were successful with the 486 pinout in 1995 but not 1996; we expect the P55C pinout to be successful in 1997 but less so in 1998.

Although matching Intel's fastest Pentium is a big PR boost for Cyrix, the most important effect of the new version of the 6x86 is increasing yield and reducing the cost of the P133+, P150+, and P166+ versions, which sell into segments of the market with higher volumes than the P200+. Even as the P200+ declines in price, we do not foresee significant sales, even by Cyrix standards. Although the P200+ is nominally pin-compatible with Pentium, its 75-MHz bus makes it incompatible with all current Pentium motherboards. We expect few vendors to redesign boards for the 6x86-P200+, limiting its adoption.

In contrast, the Pentium-200 offers an easy upgrade to existing motherboards. For the next several months, the new clock speed will be the high end for consumers and others who don't want Pentium Pro. In fact, Intel doesn't expect P55C systems to be in stores in time for Christmas, leaving the Pentium-200 as the premium model through the holiday buying season. Once P55C ships in volume, however, the Pentium-200 will be a quickly fading memory.

## 401GF Is Coolest, Cheapest PowerPC

### IBM's Low-Power Processor Delivers 650 MIPS/Watt with a \$13 Price Tag

by Jim Turley

For the first time, PowerPC chips can mount a credible assault on the market for low-cost battery-operated devices. Fulfilling a year-old promise, IBM Microelectronics rolled out its PowerPC 401 core, providing a new low end to the PowerPC family. The small new design maintains software compatibility with the range of PowerPC processors from IBM and Motorola but drops prices below \$15.

At 25 MHz, the part merely sips power, consuming just 40 mW (typical) from a 2.5-V supply—one-fifth the power of previous embedded PowerPC chips and well into the target range for portable devices.

The 401 core is available both as a macrocell for ASIC development and as a packaged part, the 401GF. At \$13 in quantity, the 401GF is the least expensive PowerPC chip made, yet it delivers 52.5 Dhrystone MIPS at 50 MHz. The 25-MHz and 50-MHz versions of the 401GF will begin sampling in a few weeks; 75- and 100-MHz versions will follow before the end of 1996, according to IBM.

#### Stripped to the Core

The 401GF achieves its remarkably low power consumption through a combination of design tradeoffs, circuit-design techniques, and fabrication process. As IBM's entry-level PowerPC, the 401 core includes only the features absolutely necessary for PowerPC compatibility. For example, the 401GF does not include the serial ports, MMU, DRAM controller, or DMA logic of the earlier 403-series parts (see MPR 5/9/94, p. 1). As Table 1 shows, the 401GF includes little more than a 401 core, dual caches, and a multiplexed bus interface.

By its nature as a PowerPC implementation, the 401GF has a somewhat richer feature set than most minimal embedded CPUs. For example, the chip supports simple static branch prediction, handles unaligned loads and stores, offers

| Processor        | 401GF   | 403GA    | 403GB    | 403GC    |

|------------------|---------|----------|----------|----------|

| Max freq         | 50 MHz  | 33 MHz   | 28 MHz   | 33 MHz   |

| I/D cache        | 2K/1K   | 2K/1K    | 2K/1K    | 2K/1K    |

| Dhry MIPS        | 52 MIPS | 41 MIPS  | 35 MIPS  | 41 MIPS  |

| Voltage          | 3.3 V   | 3.3 V    | 3.3 V    | 3.3 V    |

| Power (typ)      | 140 mW  | 265 mW   | 200 mW   | 200 mW   |

| Package          | TQFP-80 | PQFP-160 | TQFP-128 | PQFP-160 |

| MMU?             | No      | No       | No       | Yes      |

| DRAM ctrl?       | No      | Yes      | Yes      | Yes      |

| DMA chan         | None    | 4        | 2        | 4        |

| Serial chan None |         | 1        | 1        | 1        |

| Availability     | 2Q96    | Now      | Now      | Now      |

| Price (10K)      | \$13    | \$28     | \$25     | \$30     |

**Table 1.** The 401GF is similar to IBM's three 403-series parts in many respects, including the caches, but without the peripherals.

selectable byte ordering, includes a hardware multiply and divide unit, and has separate instruction and data caches. The 401's register file is triple ported, reducing pipeline stalls and contention for the internal buses.

The caches are more deluxe than usual for a low-cost chip. The data cache has a two-line write buffer, both caches can be locked on a line-by-line basis, and both forward the critical word first. In all, these features help the 401GF attain its 1.05 MIPS/MHz ratio. They also contribute to its relatively bulky die size.

#### **Optimized for ASICs**

The first two versions of the 401GF, at 25 and 50 MHz, are fabricated in IBM's 0.5-micron three-layer-metal CMOS-5S process. At 4.5 mm², the 401 core is hardly oversize, but the inherent complexity of the PowerPC architecture does tip the scales a bit. The notoriously small ARM7 core, for instance, measures just 3.8 mm² in a less aggressive 0.7-micron process. LSI Logic's CW4001 covers 3.5 mm² in a comparable 0.5-micron process, less one metal layer. In IBM's favor, though, neither of these cores offers any of the performance features mentioned above.

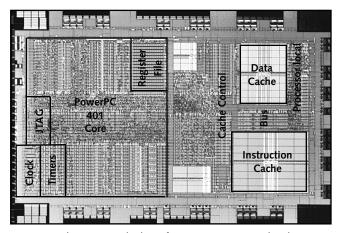

IBM's design method is tailored for ASICs, even on its standard parts. Although not immediately clear from the die photo in Figure 1, the 401GF has two internal buses—one for low-latency units close to the CPU core and another for relatively long latency peripherals—with a bus bridge between them. Since the 401GF has no on-chip peripherals, the secondary bus sits unused; on its 403-series brethren, it hosts the serial channels. IBM is studiously building its library of peripheral functions, hoping to attract PowerPC-based ASIC customers that Motorola cannot service.

**Figure 1.** The 401GF is laid out for convenient ASIC development, so less than 25% (4.5 mm²) of the chip's 22 mm² is dedicated to the PowerPC core in IBM's 0.5-micron three-layer-metal process.

#### Price & Availability

IBM's 401GF is sampling now in an 80-lead TQFP package; 75- and 100-MHz samples will be available near the end of 1996. In 10,000-piece quantities, the 401GF is priced at \$13. For more information, contact IBM Microelectronics (Research Triangle Park, NC) via fax at 415.855.4121, or visit IBM's embedded PowerPC page at www.chips.ibm.com/products/embedded/index.html.

#### Conditional Clocking Quiets 401's Logic

The 401's three-stage pipeline is the minimum necessary for a contemporary RISC design, yet it allows the chip to reach competitive performance levels: IBM expects to sample the 75-MHz version before the end of the year and, with a possible process shrink to 0.35 micron, a 100-MHz chip. The ARM7 core, in contrast, is currently limited to 40 MHz without expanding its three-stage pipeline into five stages.

The 401GF relies heavily on conditional clocking and clock-distribution tricks. Individual sections of the 401 core are clocked only as necessary, with registers, execute stages, and buffers idled when not in use. The 401GF also has four user-selectable power-down states, from wait mode, which stops fetching and cuts power in half, to deep sleep, which

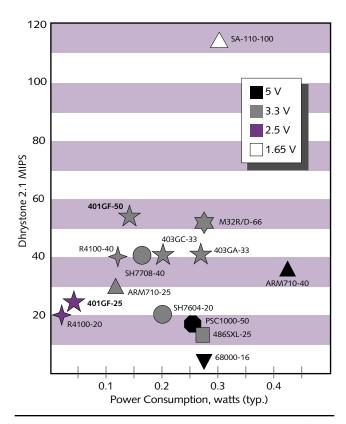

Figure 2. The 401GF's low power consumption compares favorably with that of a number of other recently announced embedded microprocessors. (Source: vendors)

halts all circuits while power consumption plummets to just 0.015 mW. Resuscitating the 401GF from deep sleep requires a hardware interrupt and a good 1.5 milliseconds, or 37,500 cycles at 25 MHz.

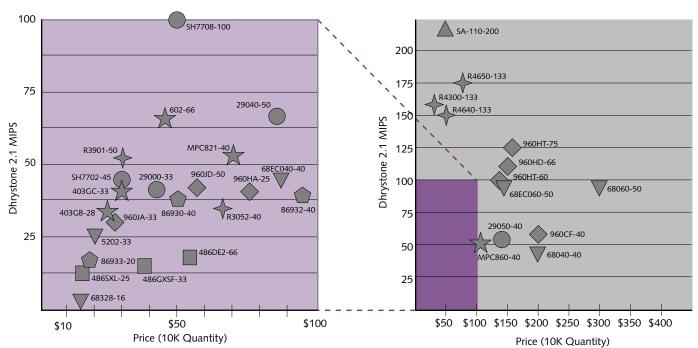

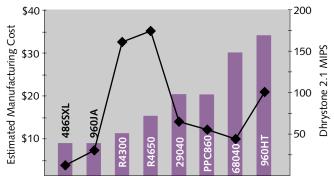

#### Good for Low Power

The chip's estimated power consumption is impressively low. At 25 MHz, the 401GF draws about 16 mA from its 2.5-V supply, for 40 mW of typical power consumption. At 656 MIPS/watt, the 401GF unseats even the impressive Strong-Arm-110 (see MPR 2/12/96, p. 1) in power/performance efficiency, though it comes nowhere near the Digital chip's highend performance. As Figure 2 shows, the 401GF comes in a close second behind NEC's 20-MHz R4100 (see MPR 3/27/95, p. 12), which, at just 27 mW and 20 MIPS, stands out with an amazing 815 MIPS/watt.

The 401GF can operate up to 25 MHz at 2.5 V; after that, a 3.3-V supply is required. The higher supply voltage has the side effect of giving the chip compatibility with conventional 5-V I/O levels.

Turning up the clock frequency on the puny PowerPC increases performance linearly, but its power consumption climbs even faster because of the jump to 3.3 V. At 50 MHz, the 401GF needs closer to 140 mW, dropping its MIPS/watt ratio to about 375-still an efficient part. At 100 MHz, the 401GF will give the 100-MHz SA-110 a run for its money, coming within a few percent of Digital's estimated integer performance and power consumption—and all from a 3.3-V supply, twice the voltage of the SA-110 core.

The economic ratios are just as good. IBM is pricing both the 25-MHz and the 50-MHz versions of its new chip at \$13 in 10,000-unit quantities. These prices are less than half that of the cheapest SA-110 and cheaper than the R4100's. The 401 challenges low-cost products like Hitachi's SH-3 family and NEC's V800 line. Unlike those architectures, PowerPC has a broad, clear upgrade path to higher performance and (at least in the midrange) an alternate vendor.

#### IBM Picking Up Speed in Embedded Market

IBM has come a long way since the company began its embedded PowerPC line two years ago. Although the chips in IBM's embedded line were sometimes hard to tell apart, the company is now beginning to grow into a full-line microprocessor supplier. For the next few years, IBM will continue to emphasize its core-based ASIC capabilities rather than its thin catalog of standard designs. The ASIC designs will fill the fabs and cover the time the company needs to assemble a credible array of standard peripherals.

For consumer-electronics and portable-communications-gear makers with the wherewithal for ASIC development and a taste for PowerPC, IBM is the obvious choice. But even without the "brand name" recognition of the world's best-selling desktop RISC processor, IBM has created a very competitive 32-bit embedded CPU that stacks up well against the best.

## **AGP Speeds 3D Graphics**

### Accelerated Graphics Port Enables New Generation of 3D Accelerators

by Yong Yao

Continuing to set new standards in PC system design, Intel unveiled the details of its proposed accelerated graphics port (AGP) architecture at the recent AGP conference. The new interconnect addresses latency and bandwidth limitations that arise when PCI is used for 3D graphics. AGP is an extension of the basic PCI architecture, but it adds a demultiplexed address bus, pipelined transfers, and a 133-MHz effective transfer rate to improve performance.

This increased performance enables 3D texture data, traditionally kept in the frame buffer, to move to main memory. This change makes memory usage more efficient and frees frame-buffer bandwidth for tasks such as screen refreshing and Z-buffering. Besides helping 3D performance, AGP will also boost 2D performance due to the lower arbitration overhead and the higher data rate among the graphics controller, CPU, and main memory.

To achieve the high transfer rate, AGP is defined as a point-to-point connection, not a bus. While this design simplifies the electrical environment, it implies that the graphics subsystem be connected directly to the system-logic chip set; no other devices in the system can use AGP. A system can include an AGP-based graphics controller on the mother-board, or it can include a single AGP slot for an add-in graphics-accelerator card.

As it did with PCI and USB, Intel is aggressively pushing AGP into the PC market. The company has already signed Microsoft as well as a slew of graphics vendors to back the new standard, which Intel is openly licensing. The first AGP chip sets and graphics cards are due to appear in 1H97; by the end of next year, AGP should be in many high-end systems, becoming widely used within two to three years.

High-performance 3D graphics will be one of the key areas driving PC performance over the next several years. Intel realized that the basic PC architecture of today must be modified to deliver optimal 3D performance and thus has offered AGP as a solution. The company is also leaping into the 3D chip market; its first such product, due next year, will be an AGP-based 3D accelerator.

| Resolution        | Screen<br>refresh<br>75 MHz | Color<br>plane<br>(R/W) | Z-buffer | Texture | Other | Total<br>bandwidth<br>required |

|-------------------|-----------------------------|-------------------------|----------|---------|-------|--------------------------------|

| 640 × 480         | 50                          | 100                     | 100      | 100     | 20    | 370                            |

| 800 × 600         | 100                         | 150                     | 150      | 150     | 30    | 580                            |

| $1024 \times 768$ | 150                         | 200                     | 200      | 250     | 40    | 840                            |

**Table 1.** 3D rendering bandwidth requirements in Mbytes/s. The numbers are based on 16-bit color, 30 frames per second, and average scene complexity (average amount of polygon overlap) equal to three.

#### **Texture Maps Overwhelm PCI**

Not long ago, PCI was created to resolve the data-bandwidth problem among peripherals, memory, and the host CPU. Ironically, the bandwidth of the PCI bus has now become the bottleneck in some advanced PC designs for 3D graphics. Rendering in 3D requires a large amount of bandwidth between the graphics accelerator and the frame buffer, as Table 1 shows. To meet these bandwidth requirements, many graphics subsystems use expensive high-performance memory chips, increasing the cost of the system.

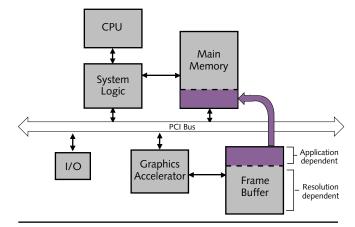

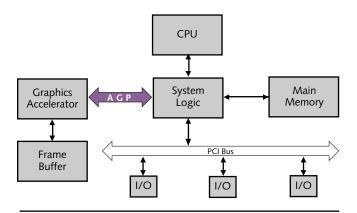

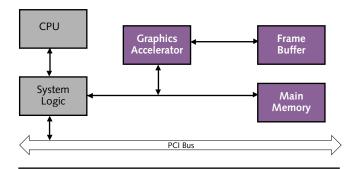

One way to ease this problem is to move texture data from the frame buffer to main memory, as Figure 1 shows. Texture data is a good candidate to make this move for several reasons. First, it is generally read only; moving it to main memory does not cause data-consistency problems. Second, texture data must pass through main memory when it is loaded from mass storage; leaving it in main memory actually reduces overhead. Finally, texture size will grow as 3D applications become more complex and deliver better image quality, so leaving textures in the frame buffer will continue to increase the graphics subsystem cost over time.

Moving texture data to main memory reduces the size, and thus the cost, of the frame buffer, but it requires a corresponding amount of storage in main memory. From a system perspective, however, it is better to increase the size of main memory than of the frame buffer, because main memory uses less expensive DRAMs. In addition, storing texture data in main memory improves memory utilization, because application-dependent textures can be returned to the free memory heap when the application completes.

Unfortunately, this move shifts the bandwidth pressure from the frame buffer to the PCI bus. As Table 1 shows, texture data alone will exceed today's PCI bandwidth limit of

**Figure 1.** Moving texture data from the frame buffer to main memory can reduce the cost of the graphics subsystem, but the texture data requires more bandwidth than PCI can deliver.

Figure 2. The proposed AGP system architecture adds a highbandwidth path between the graphics subsystem and the systemlogic chip set but has no impact on any other I/O subsystem.

100 Mbytes/s. Thus, a new method of connecting graphics to main memory is required.

#### AGP Extends PCI Standard

The primary goal of the AGP initiative is to contain the cost of implementing 3D in PCs while enabling performance improvements. Intel has made three major extensions to PCI for the AGP interface:

- Deeply pipelined memory read and write operations

- 133-MHz data-transfer rates

- Demultiplexing of address and data

These changes provide bandwidth and latency improvements well beyond that of the current 32-bit 33-MHz PCI bus and beyond even what the 66-MHz 64-bit PCI specification provides.

|             | I                                                                                    |

|-------------|--------------------------------------------------------------------------------------|

| Signal name | Function description                                                                 |

| IRDY#       | Indicates the master is ready to provide all write data for the current transaction. |

| TRDY#       | Indicates the target is ready to provide read data for a whole 32-byte block.        |

| GNT#        | Same meaning in AGP as in PCI, but additional information is associated with it.     |

| C/BE[3:0]   | Provides command information (different than PCI) when requests are being queued.    |

| PIPE#       | Used to queue pipelined request using the AD bus.                                    |

| SBA[7:0]    | Additional bus to queue pipelined requests.                                          |

| SBE         | Enables the SBA bus to be used.                                                      |

| ST[2:0]     | Indicates how the AD bus will be used next.                                          |

| AD_STB      | Indicates the AD bus has valid data (2× mode).                                       |

| SB_STB      | Indicates the SBA bus has a valid request (2× mode).                                 |

| DBF#        | Indicates if the master can accept normal-priority read data.                        |

Table 2. The first set of signals have a different meaning in AGP than in PCI; the second set are the 16 new AGP signals that are not part of the PCI specification. In the table, the master refers to an AGP-compliant graphics controller and the target refers to an AGP-compliant system-logic chip set.

Given these differences, Intel attempted to leverage as much of the PCI specification as possible. The three AGP performance enhancements are realized though the use of "sideband" signals, which are separate from the standard PCI signal set. AGP specifically avoids the use of any of the reserved fields, encodings, and pins in the PCI specification. AGP-defined protocols like pipelining are overlaid on PCI in such a manner that a standard PCI-compliant agent would view the bus as idle.

Despite these similarities, AGP and PCI devices cannot coexist. The key reason is that AGP is not a bus; it supports only a single device. Intel could have attempted to build AGP as a precise superset of PCI, putting AGP devices on that bus, but this decision would have either restricted AGP to 33 MHz or forced all PCI devices to support a 66-MHz clock, a needless cost burden for most PCI peripherals. In addition, AGP defines a different connector than PCI; the demultiplexed address signals would not fit in the current PCI connector. Thus, AGP devices need to be off of the PCI bus.

Leveraging the PCI definition allowed Intel to develop the AGP specification more quickly; the very concept of AGP did not exist until six months ago. The similarities to PCI will also ease the task of hardware designers. For the next few years, many graphics chips are likely to sport a dual AGP/PCI interface, allowing the system designer more flexibility. In fact, some the first "AGP" graphics chips may simply be slightly modified PCI chips that do not support many of the optional features of AGP.

#### AGP Boosts Memory Bandwidth

AGP is defined as a point-to-point connection based on a 3.3-V 66-MHz PCI bus. As Figure 2 shows, at one end of the connection is a device called the AGP-compliant target, which must always be the main-memory controller. The memory controller is part of the system logic in today's PCs.

| Cycle name         | CBE#<br>status | Cycle description                                                                                                                                                                                                                |

|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read               | 0000           | Read n sequential Q-words, where n=length_field+1*.                                                                                                                                                                              |

| Priority read      | 0001           | Same as Read, but the request is queued in the high priority queue.                                                                                                                                                              |

| Write              | 0010           | Write n sequential Q-words, where n=length_field+1*.                                                                                                                                                                             |

| Priority write     | 0011           | Same as Write, but indicates that the write data must<br>be transferred from the master within the maximum<br>latency window established for high-priority accesses.                                                             |

| Long read          | 1000           | Same as Read except for access size, in this case n=4* (length_field+1), allowing up to 256-byte transfers.                                                                                                                      |

| Priority long read | 1001           | Same as Priority read except for access size, in this case n=4* (length_field+1), allowing up to 256-byte transfers.                                                                                                             |

| Flush              | 1010           | Similar to read. This command drives all accesses ahead of it to the point that all the results are fully visible to all other system agents, and then returns a single Qwork of random data as an indication of its completion. |

| Fence              | 1100           | Creates a boundary in a single master's access stream, around which writes may not pass reads. This command does not occupy a slot in the AGP pipeline.                                                                          |

**Table 3** The CBE lines provide bus commands for AGP pipeline operations. \*The length\_field is specified by the SBA bus.

At the other end is the AGP-compliant master, which is a graphics accelerator. The point-to-point connection not only makes the double-edged clocking possible, it also improves data integrity, simplifies the AGP protocols, and eliminates PCI bus arbitration overhead.

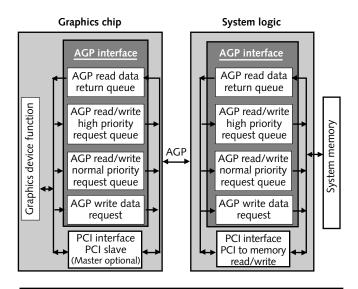

The AGP interface closely resembles that of the PCI bus. Most PCI signals are reused in AGP transactions, while others have slightly different semantics, as Table 2 shows. There are 16 new signals, also listed in Table 2, defined by the AGP specification. The PCI FRAME#, DEVSEL#, STOP#, and IDSEL signals are not used during AGP transactions. All AGP devices, however, are also required to respond to PCI transactions, so they must handle these signals as defined by the PCI specification.

#### **Pipelining Improves Read Operations**

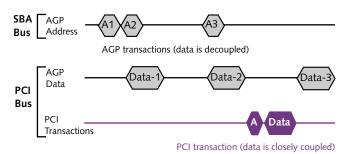

Pipelining is the major protocol enhancement provided by AGP. Only memory read and write operations targeted to main memory are affected by pipelining. All other bus operations, including reads and writes to the graphics controller, are executed as standard PCI transactions. The request portion of an AGP transaction is signaled differently than a PCI address phase. The information is still transferred on the AD and C/BE# signals of the bus, as is the case with PCI, but is identified with the new signal PIPE# instead of FRAME#.

The system logic can access the graphics chip only with PCI transactions. Only the graphics chip can use pipelined transactions while accessing main memory. Table 3 lists the AGP pipeline operations. Note that, unlike PCI transactions, AGP pipeline transactions are not cache coherent and cannot be retried or terminated after they start.

The pipelined transactions defined by AGP run in a split-transaction fashion. The graphics chip initiates a pipelined transaction with an access request. The system logic responds to the request by initiating the corresponding data transfer at a later time. The graphics chip can then issue its next pipelined transaction while waiting for the previous data to return. This overlap results in several requests (reads or writes) active in the target's request queue at any point in time. The AGP specification does not impose a limit on how many outstanding transactions are allowed; this limit is determined by individual implementations.

As Figure 3 shows, the request queue is divided into high-priority and normal-priority subqueues, each of which deals with respective accesses according to its own rules. Data within a given queue is always returned in order, but data from different queues may be returned out of order. Figure 4 shows a transaction example.

#### Double Clocking Allows 133-MHz Transfer Rate

Another significant change between AGP and PCI is the double-clocking technique used to achieve a 133-MHz data transfer rate. The AGP interface operates with a 66-MHz clock, but data can be transferred on both clock edges. Most of the AGP electrical interface specifications are based on 66-

Figure 3. To improve response time, AGP's access queuing model divides transactions into high and normal priorities.

MHz PCI, but AGP has two transfer modes:  $1 \times$  and  $2 \times$ . Because it is a point-to-point connection using 3.3-V signaling, the AGP specification for the 1× transfer mode actually relaxes some of the design specifications relative to 66-MHz PCI. The 2× transfer mode, referred to as AGP-133, requires additional interface timing strobes and different signal timings from the  $1 \times$  mode.

With a 133-MHz effective transfer rate, AGP reaches 533 Mbytes/s of peak bandwidth. In addition, its sustained bandwidth is significantly improved over PCI's by pipelining and demultiplexing.

#### Sideband Port Demultiplexes Address

To further increase the efficiency of the AGP interface, especially for random memory accesses, Intel added a sideband address (SBA) bus. This bus demultiplexes the address of an AGP transaction from the data. It is used exclusively to transmit AGP access requests. Therefore, it is always driven from

Figure 4. Sample AGP transactions show the PCI address phase and its corresponding data are always together. For a pipelined AGP transaction, the address phase and data phase are decoupled. In the figure, the PCI transaction is running out-of-order with the third AGP transaction. Note that pipelined transactions can also be performed without the optional SBA bus.

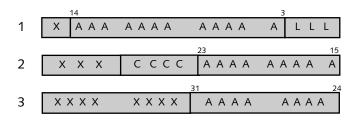

**Figure 5.** Address (A), command (C), and length (L) bits are transferred across the sideband address bus in three groups, as shown. Each group requires two 8-bit transfers.

the master to the target. Since use of the SBA bus indicates a pipelined transaction, there is no need for the PIPE# signal. Supporting SBA is optional for the master, but an AGP-compliant chip set is required to support this bus. If an AGP master uses the SBA bus, it will always issue demultiplexed transactions.

The sideband address bus (SBA[7:0]) is only 8 bits wide, reducing pin count. To use this bus, a complete AGP request is broken into three parts: low- order address bits and length, middle address bits and command, and high-order address bits, as Figure 5 shows. Each of these three parts takes two 8-bit transfers, or one cycle when double clocking. The latter two parts of the request need be transmitted only if they have changed since the previous request, which exploits potential locality among requests to minimize traffic over the SBA bus.

#### AGP Requires Address Remapping Table

Texture maps that are stored in main memory must be contiguous from the point of view of the application and the 3D controller. A typical  $256 \times 256$  pixel 16-bit texture map is 128K in size, but Windows cannot allocate that much contiguous physical memory. Intel's solution is to have Windows allocate space for texture maps in the application's virtual address space, then lock the pages into physical memory. This method results in each texture map occupying many 4K pages distributed throughout physical memory.

Intel's AGP chip set contains a graphics address remapping table (GART) that mimics this virtual-to-physical address translation. Accesses from the graphics controller to a

**Figure 6.** VESA has defined a version of its UMA design that places the graphics accelerator and its frame buffer on the main-memory bus.

special address range are translated by the GART into physical addresses, making the textures appear to be contiguous. The GART is potentially quite large. A 4M window requires a 1024-entry GART, with each entry occupying 4 bytes.

The AGP specification does not describe how the GART is to be implemented by a chip set vendor. Instead, the vendor must provide a chip set driver that manages the GART according to a GART Services API that will be defined in the AGP specification. This definition should allow vendors other than Intel to design AGP chip sets that are compatible with Intel's at the operating-system level. The detailed definition of the GART and the API is not yet available, and this may delay third-party chip-set designs slightly.

Intel will be the first to market with an AGP chip set. This chip set, known as the 440LX, is designed for P6 (primarily Klamath) systems. Intel says it will not develop AGP chip sets for Pentium (including P55C) systems, although the P55C will still be the major volume player when AGP debuts; this decision is apparently a ploy to motivate home users to move to Klamath. We expect other vendors to add AGP to their Pentium and P6 chip sets, although they may lag Intel to market by three to six months.

A well-designed system-logic chip set is critical to bring the AGP architecture into full play. The chip set must bring the graphics accelerator logically closer to the host CPU and handles concurrent operations among the CPU, the graphics accelerator, main memory, and PCI masters. Even when multiple AGP chip sets are available, they may be significant performance differences among them.

#### **UMA Offers Product Differentiation**

The Video Electronics Standards Association (VESA) had also foreseen the increase in bandwidth needed for efficient 3D performance. As part of its UMA standard, VESA defined an optional method of connecting the graphics controller, frame buffer, main-memory controller, and main memory all across a high-bandwidth memory bus, as Figure 6 shows. This design allows the graphics controller to freely access either the frame buffer or main memory without requiring any intervention from the system logic; a simple handshaking protocol controls access to the memory bus.

The VESA proposal has some technical advantages:

- It adds only a couple of control lines to the chip set and the graphics accelerator, reducing the cost of manufacturing the chip set.

- It provides a 64-bit connection to memory, twice the width of AGP's. The interface speed will grow with memory technologies. For instance, today's fast SDRAM can operate at 100 MHz or higher.

- The graphics accelerator can directly access main memory without a chip set in between.

AGP, however, has its own technical advantages:

- The AGP interface is independent of the memory technology used for main memory.

- The chip set sees every access to main memory and can

#### For More Information

For more information on AGP, contact the AGP Implementors Forum at 503.264.9222; fax 503.264.5959 or access the Web at www.teleport.com/~agfxport.

allocate valuable memory bandwidth most efficiently.

- AGP does not impart an additional load on the systemmemory interface.

- Unlike the VESA proposal, AGP can support both add-in graphics cards and motherboard implementations.

The VESA proposal illustrates a different technical approach to the bandwidth problem, but ultimately the important differences between the two proposals are the industry backers. The backing of Intel and Microsoft, along with a large number of graphics vendors, ensures AGP's success. Just as PCI outmuscled VESA's VL-bus, AGP will even more easily brush aside this alternative proposal.

#### AGP Headed for Rapid Acceptance

AGP is an open specification, in that it will be licensed to all interested parties under royalty-free reciprocal terms, similar to USB. Unlike USB, the definition of AGP is controlled by Intel alone. Because of this, the definition of AGP has been completed much more quickly than with USB or PCI. All major 3D graphics companies, such as 3Dfx, 3Dlabs, ATI, Cirrus Logic, Rendition, S3, and Trident, plan to support AGP. Intel expects to ship its first AGP system-logic chip set in 1H97. In the same time frame, some of the early adopters will launch their AGP-compliant graphics accelerators.