# **PC Processors for Model Year 2000** *A Comparison of Microarchitectures in Upcoming PC Processors*

# by Keith Diefendorff

There is no objective way to ascertain which is the "best" microprocessor for a PC. Which attributes are most important is unclear, and how best to measure their value is debatable. Benchmarks are valuable tools, but the results are often misused or misunderstood, and they can obscure important characteristics. Moreover, benchmarks are not available for processors that haven't yet reached the market. For chip suppliers this is a good thing; without the cover of confusion and uncertainty, many of them wouldn't survive.

With no illusion of picking a winner, but hoping to shed some light on the subject, we review the microarchitectures of the upcoming crop of PC processors, including Intel's Pentium III (Coppermine), AMD's Athlon, Cyrix's Mojave, Centaur's WinChip 4, Rise's mP6 II, and Motorola's G4. As background, in the previous issue (see MPR 7/12/99, p. 16) we presented a concise overview of the microarchitecture techniques used in modern PC processors.

# Intel, AMD Vie for Performance Lead

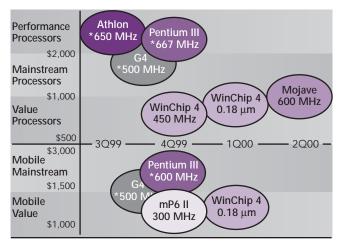

Intel will introduce its forthcoming Coppermine version of Pentium III at the high end of the market and, as it has done with many previous processors, drive it aggressively down the price curve until it becomes a low-end processor. We expect Coppermine, or simple derivatives of it, to enter the low-end market segments within about six months of introduction.

Coppermine is a 0.18-micron version of the 0.25micron Pentium III (Katmai). Pentium III, like Pentium II before it, is based on the P6 microarchitecture, which Intel first introduced in Pentium Pro in 1995. Coppermine takes advantage of Intel's new P858 process to boost frequency and bring 256K of L2 cache onto the chip. Intel says Coppermine will enter production this November. We expect it to begin life at up to 667 MHz, as Figure 1 shows.

Weary of competing against Intel with the K6, AMD has quietly begun sampling Athlon. Athlon is based on AMD's new K7 microarchitecture—the most powerful of any ever deployed in a PC processor. Unlike the K6, the K7 uses a long pipeline, designed to enable AMD to match Intel on the all-important clock-frequency parameter. We anticipate that AMD will introduce Athlon at up to 650 MHz in 0.25-micron CS44E this quarter. AMD says it will ship Athlon in 0.18-micron CS50 before the end of the year, not far behind Coppermine, boosting frequency substantially. Assuming AMD can avoid stubbing its toe on the manufacturing line again, Athlon will become the first processor to seriously challenge Intel for the performance high ground.

# Other x86 Competitors Target Low End

The status of Cyrix's x86 processors is still somewhat uncertain following National's decision to sell Cyrix to Via (see MPR 7/12/99, p. 5). We assume for purposes of this article, however, that Cyrix's roadmap remains intact and, as Cyrix expects, Via will proceed with Mojave.

At Microprocessor Forum last year, Cyrix described the M3—a highly integrated Jalapeno-based processor for which the company now seems to have lost enthusiasm. Mojave uses the same Jalapeno core as the M3, but in a more

Figure 1. On the basis of their microarchitectures and frequencies at introduction, we expect the new PC microprocessors to be best suited to the segments shown. (\*MDR estimates)

traditional configuration, with a 133-MHz version of Intel's Socket 370 interface. At the Forum, Cyrix claimed the M3 would ship at 600 MHz in National's 0.18-micron CMOS-9 process (see MPR 9/14/98, p. 1); we assume Mojave is targeted at the same speed. (National refers to CMOS-9 as a 0.18-micron process, although our analysis shows it to be more like a 0.21-micron process.)

Like the P6 and the K7, Jalapeno is a superscalar out-oforder design. But unlike those processors, both of which dispatch and decode up to three instructions per cycle, Jalapeno does only two. Its instruction reordering capability is also more limited than that of the P6 or the K7.

Like Mojave, Centaur's WinChip 4 faces an uncertain future, as IDT has decided to exit the x86 processor business and to sell Centaur (see MPR 8/2/99, p. 4). We assume, however, that a buyer will be found and that WinChip 4 will survive. WinChip 4 employs a simple in-order microarchitecture that, unlike previous WinChips, is deeply pipelined to more closely match Intel's frequencies.

Centaur's separation from IDT may be a blessing. The company has had to endure IDT's endless difficulties getting its 0.25-micron CMOS-10.5 process into production, a process Centaur was counting on for low cost while achieving 500-MHz operation. As a result of IDT's difficulties, Centaur has been forced to utilize IBM's 0.28-micron CMOS-6S2 process. This process will probably limit initial WinChip 4 parts to 400–450 MHz and increase costs. It would help Centaur greatly if the new owner has a good, inexpensive IC process.

The latest entrant in the PC processor game is Rise (see MPR 11/16/98, p. 1), a fabless semiconductor startup based in Silicon Valley. Like IDT, Rise has its sights set on the low-

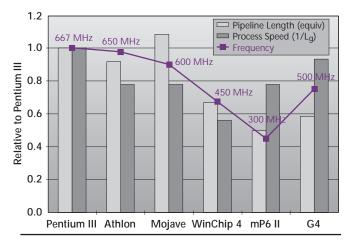

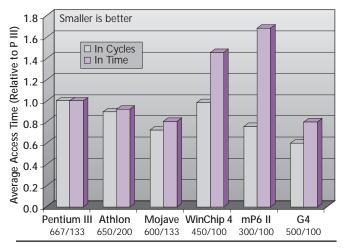

Figure 2. Clock frequency is generally well correlated to the load pipeline length in these processors. The frequency (purple) is our expectation of the maximum frequency of the part at introduction. All values were normalized to Pentium III at 667 MHz. Pipeline length was measured through availability of data from the D-cache. Pipeline length was adjusted by one stage for Athlon and G4 to account for predecode. The G4's pipeline was credited with another two stages to account for its RISC ISA. Process speed was estimated as the reciprocal of the gate length (L<sub>0</sub>). (Source: MDR)

end desktop and portable markets. Its current mP6 processor is a three-issue in-order design, which it will beef up with a 256K on-chip L2 cache in the mP6 II. Rise says the mP6 II will be rendered in an undisclosed 0.18-micron process. Our sources indicate that it may be UMC's L180 process.

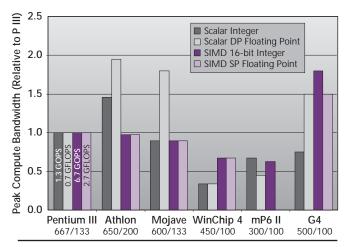

The only non-x86 processor family currently in the hunt for a slice of the PC market is PowerPC, which is at the heart of Apple's Macintosh. The next-generation PowerPC processor is Motorola's G4, which uses the same superscalar, out-of-order microarchitecture as the current PPC 750 (G3) but adds Motorola's new AltiVec SIMD architecture. The G4 also includes a fully pipelined scalar floating-point unit and boasts improved memory bandwidth. The chip will initially be implemented in Motorola's 0.22-micron copper HIP5 process. Motorola has not disclosed the initial frequency, but sources indicate it may debut at up to 500 MHz.

# Pipeline and Process Determine Frequency

The first-order terms in the frequency equation are pipeline length and IC process, as Figure 2 shows. Against the standard set by the P6, Athlon easily achieves its expected pipeline-defined clock rate, despite the fact that AMD's CS44E is substantially slower than Intel's P858. This achievement indicates a very evenly partitioned pipeline. Clearly Athlon's pipeline design is superior to the K6's, as Athlon operates at a 25% lower voltage; evidently Athlon doesn't require the transistors to be driven as hard as they were for the K6.

Mojave will debut below its natural pipeline frequencies, probably held there by process-speed limitations. The mP6 II will also operate below its natural pipeline frequency, but it is doing so despite an advanced 0.18-micron process. Perhaps there is a critical speed path that is limiting frequency, or perhaps we have overestimated the process technology Rise is using.

Motorola's G4 is obviously taking advantage of its advanced copper process to operate the G4 above its expected pipeline frequency. The G4, however, like the 750 and the 603 before it, is clearly underpipelined; the design would benefit greatly from a few additional pipeline stages.

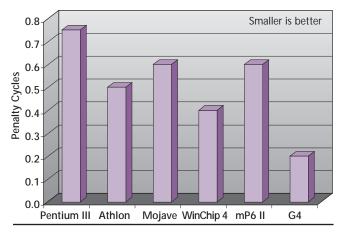

# Branch Misprediction Saps Performance

Although long pipelines can increase frequency, the payback comes on conditional branches. The P6 microarchitecture, first deployed in a 0.5-micron technology, was limited in the area that could be invested in dynamic branch-prediction hardware. Although Intel has never fully described the P6's branch hardware, academic studies of similar two-level schemes have shown prediction accuracies in the range of 90% to 95% on several benchmarks.

The newer x86 microarchitectures, initially designed for 0.25- or 0.18-micron processes, have been less constrained by silicon area. The more recent designs have also benefited from recent branch-prediction research and have implemented schemes that are consistently able to achieve

# 3 🔷 PC PROCESSORS FOR MODEL YEAR 2000

| IntelAMDCyrixIDTRiseMotorFeatureCoppermineAthlonMojaveWinChip 4mP6 IIG4Reference MPR Article3/8/99, p. 110/26/98, p. 111/16/98, p. 2412/7/98, p. 1811/16/98, p. 111/16/98Scheduled ProductionNov-99Jul-992Q004Q994Q992H9Microarchitecture/CoreP6K7JalapenoC4mP6750Integer Architecturex86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)v86 (CISC)v86 (CISC)Floating-Point Architecturex87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)v87 (stack)v87 (stack)v87 (stack)SIMD Int/FP ArchitectureMMX/SSEMMX/3DNowMMX/3DNowMMX/3DNowMMX/3DNowMMX/NoneAltiVec/AGP Registers, FP Registers8 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 8032 × 32, 3 × 30SIMD Integer Vector RegsUses FPRsUses FPRsUses FPRsUses FPRsUses FPRs32 × 12SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsNoneNone4 bits/instrInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PowerDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x866 RIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (RISC)<br>(flat)<br>(flat)<br>(tiVec<br>2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>C<br>1 br |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Reference MPR Article         3/8/99, p. 1         10/26/98, p. 1         11/16/98, p. 24         12/7/98, p. 18         11/16/98, p. 1         11/16/98           Scheduled Production         Nov-99         Jul-99         2Q00         4Q99         4Q99         2H9           Microarchitecture/Core         P6         K7         Jalapeno         C4         mP6         750           Integer Architecture         x86 (CISC)         x86 (CISC)         x86 (CISC)         x86 (CISC)         x86 (CISC)         powerPC           Floating-Point Architecture         x87 (stack)         x87 (stack)         x87 (stack)         x87 (stack)         x87 (stack)         powerPC           SIMD Int/FP Architecture         MMX/SSE         MMX/3DNow         MMX/3DNow         MMX/3DNow         MMX/3DNow         MMX/None         AltiVec/A           GP Registers, FP Registers         8 × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 80         32 × 32, 3 × 33         SIMD Integer Vector Regs         Uses FPRs         Uses FPRs         Uses FPRs         Uses FPRs         32 × 32, 3 × 30         S × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 30         32 × 32, 3 × 32, 3 × 32         SIMD Integer Vector Regs         8 × 128         Uses FPRs         Uses FPRs         Uses FPRs         Uses SIMI <t< th=""><th>(RISC)<br/>(flat)<br/>(tiVec<br/>2 × 64<br/>28<br/>0 IVRs<br/>(13%)<br/>rPC<br/>1 br<br/>C<br/>C<br/>C<br/>1 br</th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (RISC)<br>(flat)<br>(tiVec<br>2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>C<br>1 br           |

| Microarchitecture/Core<br>Integer ArchitectureP6K7JalapenoC4mP6750Integer Architecturex86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)PowerPCFloating-Point Architecturex87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)PowerPCSIMD Int/FP ArchitectureMMX/SSEMMX/3DNowMMX/3DNowMMX/3DNowMMX/3DNowMMX/NoneAltiVec/AGP Registers, FP Registers8 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 8032 × 32, 3SIMD Integer Vector RegsUses FPRsUses FPRsUses FPRsUses FPRsUses FPRs32 × 12SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsUses SIMIInstruction PredecodeNone3 bits/byte (38%)NoneNoneNone4 bits/instrInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PowerDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x862 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (RISC)<br>(flat)<br>ltiVec<br>2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>C<br>1 br           |

| Integer Architecturex86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)x86 (CISC)PowerPCFloating-Point Architecturex87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)PowerPCSIMD Int/FP ArchitectureMMX/SSEMMX/3DNowMMX/3DNowMMX/3DNowMMX/3DNowMMX/NoneAltiVec/AGP Registers, FP Registers8 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 8032 × 32, 3SIMD Integer Vector RegsUses FPRsUses FPRsUses FPRsUses FPRsUses FPRs32 × 12SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsUses FPRsUses SIMIInstruction PredecodeNone3 bits/byte (38%)NoneNoneNone4 bits/instrInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PowerDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x862 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (RISC)<br>(flat)<br>ltiVec<br>2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>C<br>1 br           |

| Floating-Point Architecturex87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)x87 (stack)PowerPCSIMD Int/FP ArchitectureMMX/SSEMMX/3DNowMMX/3DNowMMX/3DNowMMX/3DNowMMX/3DNowMMX/NoneAltiVec/AGP Registers, FP Registers8 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 803 2 × 32, 3 × 30SIMD Integer Vector RegsUses FPRsUses FPRsUses FPRsUses FPRsUses FPRs3 2 × 13SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsUses SIMIInstruction PredecodeNone3 bits/byte (38%)NoneNoneNone4 bits/instruction to be code WidthInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PowerDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x862 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (flat)<br>ltiVec<br>2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>1 br<br>C<br>1 br             |

| SIMD Int/FP ArchitectureMMX/SSEMMX/3DNowMMX/3DNowMMX/3DNowMMX/3DNowMMX/NoneAltiVec/AGP Registers8 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 808 × 32, 8 × 8032 × 32, 3SIMD Integer Vector RegsUses FPRsUses FPRsUses FPRsUses FPRsUses FPRs32 × 12SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsUses FPRs32 × 13Instruction PredecodeNone3 bits/byte (38%)NoneNoneNone4 bits/instrInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PoweDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x862 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ltiVec<br>2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>1 br                                    |

| GP Registers, FP Registers         8 × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 80         8 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 80         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30         3 × 32, 8 × 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 × 64<br>28<br>0 IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>1 br                                              |

| SIMD Integer Vector RegsUses FPRsUses FPRsUses FPRsUses FPRsUses FPRs32 × 1SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsUses FPRsUses SIMIInstruction PredecodeNone3 bits/byte (38%)NoneNoneNone4 bits/instrInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PoweDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x862 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28<br>D IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>1 br                                                        |

| SIMD FP Vector Regs8 × 128Uses FPRsUses FPRsUses FPRsNoneUses SIMIInstruction PredecodeNone3 bits/byte (38%)NoneNoneNoneA bits/instrInstruction Decode Width3 x86 (1 + 2)3 x862 x861 x86 (2 MMX)3 x863 PoweDispatch Width6 ROPs6 ROPs3 ROPs1 x86 (2 MMX)3 x862 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D IVRs<br>(13%)<br>rPC<br>1 br<br>C<br>C<br>1 br                                                              |

| Instruction Predecode         None         3 bits/byte (38%)         None         None         None         4 bits/instruction           Instruction Decode Width         3 x86 (1 + 2)         3 x86         2 x86         1 x86 (2 MMX)         3 x86         3 Power           Dispatch Width         6 ROPs         6 ROPs         3 ROPs         1 x86 (2 MMX)         3 x86         2 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (13%)<br>rPC<br>1 br<br>C<br>C<br>1 br                                                                        |

| Instruction Decode Width         3 x86 (1 + 2)         3 x86         2 x86         1 x86 (2 MMX)         3 x86         3 Powe           Dispatch Width         6 ROPs         6 ROPs         3 ROPs         1 x86 (2 MMX)         3 x86         2 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rPC<br>1 br<br>C<br>C<br>1 br                                                                                 |

| Dispatch Width         6 ROPs         6 ROPs         3 ROPs         1 x86 (2 MMX)         3 x86         2 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 br<br>C<br>C<br>1 br                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C<br>C<br>1 br                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C<br>1 br                                                                                                     |

| Issue Width 5 ROPs 9 ROPs 6 ROPs 1 x86 (2 MMX) 3 x86 6 RIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| Retirement Width 3 ROPs 6 ROPs 2 ROPs 1 x86 (2 MMX) 3 x86 2 RISC +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n buf                                                                                                         |

| Result Reordering Hardware Reorder buffer Future file Reorder buffer None None Completie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                               |

| Int/FP Rename Registers 40 36/36 64 None None 6/6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                               |

| Execution Units (nonbranch)5 units9 units5 units4 units7 units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                               |

| Int-Ld Pipeline (not incl retire)10–12 cycles8–10 cycles11–15 cycles11 cycles8 cycles4–5 cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| FP Add (throughput/latency)         1/3         1/4         1/4         2/6         1/4         1/3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| FP Mul or <sup>†</sup> Mul-Add         2/3         1/4         1/5         2/6 sp, 4/8 dp         1/4         1/3           Ch MD Add (1/2)         1/2 (-4)         1/2 (-4)         1/2 (-4)         1/2 (-4)         1/2 (-4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                               |

| SIMD Add (16b parallelism)         1/1 (×4)         1/2 (×4)         1/1 (×4)         1/1 (×4)         1/1 (×4)           SIMD Add (16b parallelism)         1/1 (×4)         1/2 (×4)         1/1 (×4)         1/1 (×4)         1/1 (×4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                                                                                             |

| SIMD Mul-Add         1/3         1/2         1/4         1/4         1/2         1/3           FP SIMD Add (SP parallelism)         2/4 (x4)         1/4 (x2)         1/3 (x2)         1/4 (x2)         None         1/4 (x2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| FP SIMD Add (3r parallelisin) $2/4$ (x4) $1/4$ (x2) $1/3$ (x2) $1/4$ (x2) $1/4$ (x2)           FP SIMD Mul or †Mul-Add $2/6$ $1/4$ $1/5$ $1/4$ None $1/4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                               |

| Branch Predictor Two-level GShare Two-level Two-level Static + or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                               |

| BHT $512 \times 2b^*$ 4,096 × 2b 1,024 × 7b 16K × 1b 512 × 2b 512 ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| BTAC or <sup>†</sup> BTIC 512 entries* 4,096 entries 1,024 entries 64 entries 512 entries 64 ent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | v†                                                                                                            |

| Mispredict Penalty (min) 10 cycles* 10 cycles 12 cycles 8 cycles 6 cycles 2 cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                             |

| Memory Op Reordering Ld-St, Ld-Ld Ld-St, Ld-Ld Ld-St, Ld-Ld In order In order L-S, L-L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | , S–S                                                                                                         |

| Store Reservation Stations         12         44         12         0         0         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                               |