SMJS011A-DECEMBER 1992-REVISED MARCH 1993

# **ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY**

Organization . . . 128K × 8-Bit Flash Memory

- Pin Compatible with Existing 1-Megabit **EPROMs**

- All inputs/Outputs TTL Compatible

- Maximum Access/Minimum Cycle Time

| VCC ± 10%  |        |

|------------|--------|

| '28F010-10 | 100 ns |

| '28F010-12 | 120 ns |

|            |        |

- '28F010-15 150 ns '28F010-17 170 ns

- **Industry-Standard Programming Algorithm**

- PEP4 Version Available With 168-Hour Burn-In, and Choice of Operating Temperature Ranges

- Chip Erase Before Reprogramming

- 10 000, 1 000, and 100 Program/Erase Cycle Versions Available

- Low Power Dissipation (V<sub>CC</sub> = 5.50 V)

- Active Write . . . 55 mW

- Active Read . . . 165 mW

- Electrical Erase . . . 82.5 mW

- Standby . . . 0.55 mW

(CMOS-input Levels)

**Automotive Temperature** Range: - 40°C to + 125°C

#### description

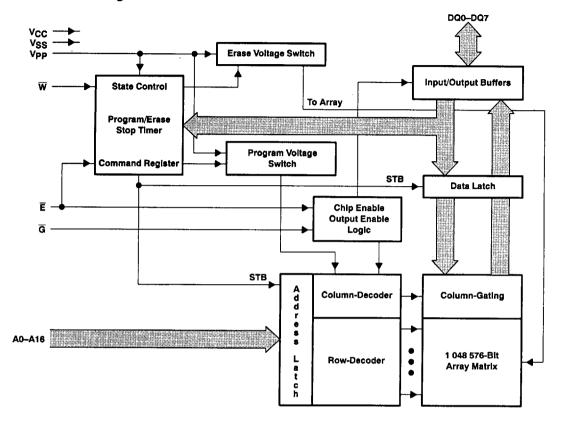

The TMS28F010 is a 1048 576-bit, programmable read-only memory that can be electrically bulk-erased and reprogrammed.

The TMS28F010 is available in 10 000, 1 000, and 100 program/erase endurance cycle versions.

The TMS28F010 Flash EEPROM is offered in a dual in-line plastic package (N suffix) designed for insertion in mounting-hole rows on 15,2 mm (600-mil) centers, a 32-lead plastic leaded-chip carrier package using 1,25 mm (50-mil) lead spacing (FM suffix), a 32-lead thin small outline package (DD suffix), and a reverse pinout TSOP package (DU suffix).

The TMS28F010 is offered with three choices of temperature ranges of 0°C to 70°C (NL. FML. DDL, and DUL suffixes), -40°C to 85°C (NE, FME, DDE, and DUE suffixes), and -40°C to 125°C (NQ, FMQ, DDQ, and DUQ suffixes), All package types are offered with 168 hour burn-in (4 suffix).

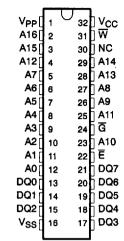

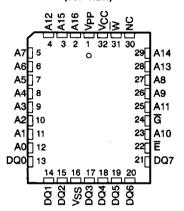

#### **FM PACKAGET** (TOP VIEW)

† The packages shown are for pinout reference only.

| PIN             | NOMENCLATURE           |

|-----------------|------------------------|

| A0A16           | Address Inputs         |

| Ē               | Chip Enable            |

| G               | Output Enable          |

| NC              | No Internal Connection |

| W               | Write Enable           |

| DQ0-DQ7         | Data In/Data Out       |

| Vcc             | 5-V Power Supply       |

| VPP             | 12-V Power Supply      |

| V <sub>SS</sub> | Ground                 |

ADVANCE INFORMATION concerns new products in the samp

Copyright @ 1993, Texas Instruments Incorporated

| <b>ভ</b> □ 1 ▽      | 32 🗖 A11             |

|---------------------|----------------------|

| A10 🗖 2             | 31 🗀 A9              |

| Ē □ 3               | 30 🗀 A8              |

| DQ7 🔲 4             | 29 🗀 A13             |

| DQ6 🔲 5             | 28 🗀 A14             |

| DQ5 🔲 6             | 27 🔲 NC              |

| DQ4 🔲 7             | · 26 🗀 😿             |

| DQ3 🔲 8             | 25 🔲 V <sub>CC</sub> |

| V <sub>SS</sub> 🔲 9 | 24 🔲 V <sub>PP</sub> |

| DQ2 [ 10            | 23 🔲 A16             |

| DQ1 🔲 11            | 22 🔲 A15             |

| DQ0 🔲 12            | 21 🔲 A12             |

| A0 🔲 13             | 20 🗀 A7              |

| A1 🔲 14             | 19 🗀 A6              |

| A2 🔲 15             | 18 🗀 A5              |

| A3 🔲 16             | 17 🗀 A4              |

<sup>†</sup> The packages shown are for pinout reference only.

TEXAS INSTR (ASIC/MEMORY)

# **ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY**

-17 = 170 ns

SMJS011A-DECEMBER 1992-REVISED MARCH 1993

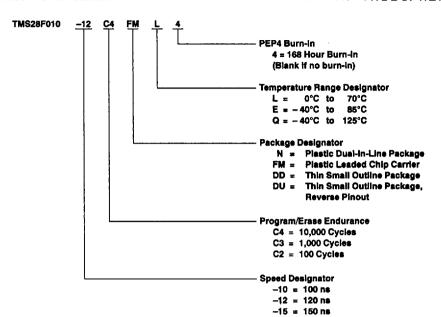

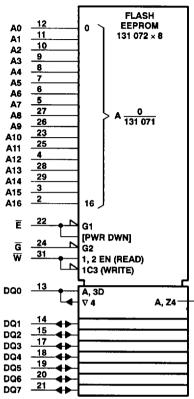

device symbol nomenclature

TEXAS INSTR (ASIC/MEMORY)

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77001

# **ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY**

SMJS011A-DECEMBER 1992-REVISED MARCH 1993

#### functional block diagram

TEXAS INSTR (ASIC/MEMORY)

|             |                           |                  | •               |           | FUN             | CTION           |      |                           |

|-------------|---------------------------|------------------|-----------------|-----------|-----------------|-----------------|------|---------------------------|

|             | MODET                     | Vpp§<br>(1)      | Ē<br>(22)       | G<br>(24) | A0<br>(12)      | A9<br>(26)      | (31) | DQ0-DQ7<br>(13-15, 17-21) |

|             | Read                      | VPPL             | V <sub>IL</sub> | VIL       | xt              | Х               | VIH  | Data Out                  |

|             | Output Disable            | VPPL             | VIL             | VIH       | Х               | Х               | VIH  | Hi-Z                      |

| Read        | Standby and Write Inhibit | V <sub>PPL</sub> | VIH             | Х         | х               | ×               | ×    | HI-Z                      |

|             | Cihu Mad-                 | V <sub>PPL</sub> | VIL             | VIL       | V <sub>IL</sub> | V4.*            | 1//  | MFG Code 97h              |

|             | Signature Mode            |                  |                 |           | VIH             | VH <sup>‡</sup> | Viн  | Device Code 75h           |

|             | Read                      | VPPH             | VIL             | VIL       | Х               | Х               | ViH  | Data Out                  |

| Read/Write  | Output Disable            | VPPH             | VIL             | ViH       | Х               | Х               | ViH  | HI-Z                      |

| HARD! MILLS | Standby and Write Inhibit | VPPH             | VIH             | Х         | Х               | х               | Х    | HI-Z                      |

|             | Write                     | VPPH             | VIL             | ViH       | Х               | Х               | VIL  | Data In                   |

TX can be VIL or VIH

#### operation

#### read/output disable

When the outputs of two or more TMS28F010s are connected in parallel on the same bus, the output of any particular device in the circuit can be read with no interference from the competing outputs of other devices.

To read the output of the TMS28F010, a low-level signal is applied to the  $\overline{E}$  and  $\overline{G}$  pins. All other devices in the circuit should have their outputs disabled by applying a high-level signal to one of these pins.

#### standby and write inhibit

Active I<sub>CC</sub> current can be reduced from 30 mA to 1 mA by applying a high TTL level on E or to 100 μA with a high CMOS level on E. In this mode, all outputs are in the high-impedance state. The TMS28F010 draws active current when it is deselected during programming, erasure, or program/erase verification. It will continue to draw active current until the operation is terminated.

#### signature mode

The signature mode provides access to a binary code identifying the manufacturer and device type. This mode is activated when A9 (pin 26) is forced to V<sub>H</sub>. Two identifier bytes are accessed by toggling A0. All other addresses must be held low. A0 low selects the manufacturer's code 97h, and A0 high selects the device code 75h, as shown in the signature mode table below:

| IDENTIFIER†       |     |     |     |     | PII | NS  |     |     |     |     |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| (DENTIFIER)       | AO  | DQ7 | DQ6 | DQ5 | DQ4 | DQ3 | DQ2 | DQ1 | DQ0 | HEX |

| Manufacturer Code | VIL | 1   | 0   | 0   | 1   | 0   | 1   | 1   | 1   | 97  |

| Device Code       | VIH | 0   | 1   | 1   | 1   | 0   | 1   | 0   | 1   | 75  |

† E = G = VIL, A1-A8 = VIL, A9 = VH, A10-A16 = VIL, Vpp = VppL.

#### programming and erasure

In the erased state, all bits are at a logic 1. Before erasing the device, all memory bits must be programmed to a logic 0. Afterwards, the entire chip is erased. At this point, the bits, now logic 1's, may be programmed accordingly. Refer to the Fastwrite and Fasterase algorithms for further detail.

<sup>\$11.5</sup> V < VH < 13.0 V

<sup>§</sup> VPPL ≤ VCC + 2 V; VPPH is the programming voltage specified for the device. For more details, refer to the recommended operating conditions.

# TMS28F010 1 048 576-BIT FLASH

### ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY

SMJS011A-DECEMBER 1992-REVISED MARCH 1993

#### command register

The command register controls the program and erase functions of the TMS28F010. The signature mode may be activated using the command register in addition to the above method. When VPP is high, the contents of the command register, and therefore the function being performed, may be changed. The command register is written to when  $\overline{E}$  is low and  $\overline{W}$  is pulsed low. The address is latched on the leading edge of the pulse, while the data is latched on the trailing edge. Accidental programming or erasure is minimized because two commands must be executed to invoke either operation.

#### power supply considerations

Each device should have a 0.1  $\mu$ F ceramic capacitor connected between  $V_{CC}$  and  $V_{SS}$  to suppress circuit noise. Changes in current drain on Vpp will require it to have a bypass capacitor as well. Printed circuit traces for both power supplies should be appropriate to handle the current demand.

**Table 2. Command Definitions**

| Signature Mode<br>Set-up Erase/Erase<br>Erase Verify | REQUIRED      | FIR                       | ST BUS CYCLE | SECOND BUS CYCLE |           |              |            |

|------------------------------------------------------|---------------|---------------------------|--------------|------------------|-----------|--------------|------------|

|                                                      | BUS<br>CYCLES | OPERATION<br>(see Note 1) | ADDRESS      | DATA             | OPERATION | ADDRESS      | DATA       |

| Read                                                 | 1             | Write                     | ×            | 00h              | Read      | RA           | RD         |

| Signature Mode                                       | 3             | Write                     | х            | 90h              | Read      | 0000<br>0001 | 97h<br>75h |

| Set-up Erase/Erase                                   | 2             | Write                     | X            | 20h              | Write     | Х            | 20h        |

| Erase Verify                                         | 2             | Write                     | EA†          | A0h              | Read      | х            | EVD        |

| Set-up Program/Program                               | 2             | Write                     | ×            | 40h              | Write     | PA           | PD         |

| Program Verify                                       | 2             | Write                     | х            | C0h              | Read      | Х            | PVD        |

| Reset                                                | 2             | Write                     | Х            | FFh              | Write     | Х            | FFh        |

NOTE 1: Modes of operation are defined in Table 1.

† Description of Terms

- EΑ Address of memory location to be read during erase verify.

- RA Address of memory location to be read.

- PA Address of memory location to be programmed. Address is latched on the falling edge of W.

- RD Data read from location RA during the read operation.

- EVD Data read from location EA during erase verify.

- PD Data to be programmed at location PA. Data is latched on the rising edge of  $\overline{W}$ .

- PVD Data read from location PA during program verify.

logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the N package.

# TMS28F010 1 048 576-BIT FLASH ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY

SMJS011A-DECEMBER 1992-REVISED MARCH 1993

#### command definitions

#### read command

Memory contents can be accessed while V<sub>PP</sub> is high or low. When V<sub>PP</sub> is high, writing 00h into the command register invokes the read operation. Also, when the device is powered up, the default contents of the command register are 00h and the read operation is enabled. The read operation remains enabled until a different, valid command is written to the command register.

#### signature mode command

The signature mode is activated by writing 90h into the command register. The manufacturer's code (97h) is identified by the value read from address location 0000h, and the device code (75h) is identified by the value read from address location 0001h.

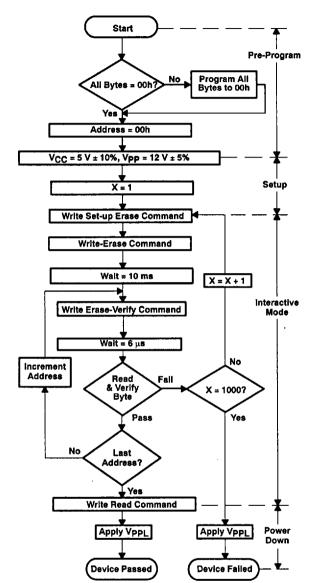

#### set-up erase/erase commands

The erase algorithm initiates with  $\overline{E} = V_{IL}$ ,  $\overline{W} = V_{IL}$ ,  $\overline{G} = V_{IH}$ ,  $V_{PP} = 12$  V, and  $V_{CC} = 5$  V. To enter the erase mode, write the set-up erase command, 20h, into the command register. After the TMS28F010 is in the erase mode, writing a second erase command, 20h, into the command register invokes the erase operation. The erase operation begins on the rising edge of  $\overline{W}$  and ends on the rising edge of the next  $\overline{W}$ . The erase operation requires 10 ms to complete before the erase-verify command, A0h, can be loaded.

Maximum erase timing is controlled by the internal stop timer. When the stop timer terminates the erase operation, the device enters an inactive state and remains inactive until a valid erase verify, read, or reset command is received.

#### erase-verify command

All bytes must be verified following an erase operation. After the erase operation is complete, an erased byte can be verified by writing the erase-verify command, A0h, into the command register. This command causes the device to exit the erase mode on the rising edge of  $\overline{W}$ . The address of the byte to be verified is latched on the falling edge of  $\overline{W}$ . The erase-verify operation remains enabled until a valid command is written to the command register.

To determine whether or not all the bytes have been erased, the TMS28F010 applies a margin voltage to each byte. If FFh is read from the byte, then all bits in the designated byte have been erased. The erase-verify operation continues until all of the bytes have been verified. If FFh is not read from a byte, then an additional erase operation needs to be executed. Figure 2 shows the combination of commands and bus operations for electrically erasing the TMS28F010.

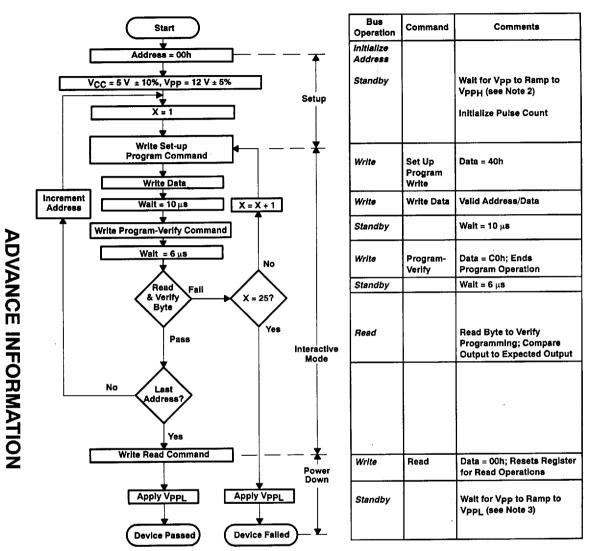

#### set-up program/program commands

The programming algorithm initiates with  $\overline{E} = V_{IL}$ ,  $\overline{W} = V_{IL}$ ,  $\overline{G} = V_{IH}$ ,  $V_{PP} = 12$  V, and  $V_{CC} = 5$  V. To enter the programming mode, write the set-up program command, 40h, into the command register. The programming operation will be invoked by the next write-enable pulse. Addresses are latched internally on the falling edge of  $\overline{W}$ , and data is latched internally on the rising edge of  $\overline{W}$ . The programming operation begins on the rising edge of  $\overline{W}$  and ends on the rising edge of the next  $\overline{W}$  pulse. The program operation requires 10  $\mu$ s for completion before the program-verify command, C0h, can be loaded.

Maximum program timing is controlled by the internal stop timer. When the stop timer terminates the program operation, the device enters an inactive state and remains inactive until a valid program verify, read, or reset command is received.

#### program-verify command

The TMS28F010 can be programmed sequentially or randomly because it is programmed one byte at a time. Each byte must be verified after it is programmed.

The program-verify operation prepares the device to verify the most recently programmed byte. To invoke the program-verify operation. C0h must be written into the command register. The program-verify operation will end on the rising edge of W.

While verifying a byte, the TMS28F010 applies an internal margin voltage to the designated byte. If the true data and programmed data match, programming can continue to the next designated byte location; otherwise, the byte must be reprogrammed. Figure 1 shows how commands and bus operations are combined for byte programming.

#### reset command

To reset the TMS28F010 after set-up erase command or set-up program command operations without changing the contents in memory, write FFh into the command register two consecutive times. After executing the reset command, a valid command must be written into the command register to change to a new state.

#### Fastwrite algorithm

The TMS28F010 is programmed using the Texas Instruments Fastwrite algorithm shown in Figure 1. This algorithm programs in a nominal time of two seconds.

## Fasterase algorithm

The TMS28F010 is erased using the Texas Instruments Fasterase algorithm shown in Figure 2. The memory array needs to be completely programmed (using the Fastwrite algorithm) before erasure begins. Erasure typically occurs in one second.

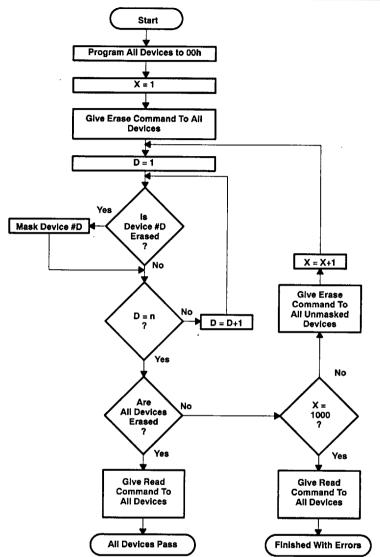

#### parallel erasure

To reduce total erase time, several devices may be erased in parallel. Since each Flash EEPROM may erase at a different rate, every device must be verified separately after each erase pulse. After a given device has been successfully erased, the erase command should not be issued to this device again. All devices that complete erasure should be masked until the parallel erasure process is finished. See Figure 3. Parallel Erase Flow Diagram.

Examples of how to mask a device during parallel erase include driving the device's E pin high, writing the read command (00h) to the device when the others receive a setup erase or erase command, or disconnecting it from all electrical signals with relays or other types of switches.

SMJS011A-DECEMBER 1992-REVISED MARCH 1993

NOTES: 2. Refer to the recommended operating conditions for the value of VppH.

3. Refer to the recommended operating conditions for the value of VppL.

Figure 1. Programming Flowchart: Fastwrite Algorithm

| Bus<br>Operation | Command         | Comments                                                          |

|------------------|-----------------|-------------------------------------------------------------------|

|                  |                 | Entire Memory Must = 00h<br>Before Erasure                        |

|                  |                 | Use Fastwrite<br>Programming Algorithm                            |

|                  |                 | Initialize Addresses                                              |

| Standby          |                 | Wait for Vpp to Ramp to<br>VppH (see Note 2)                      |

|                  |                 | Initialize Pulse Count                                            |

| Write            | Set Up<br>Erase | Data = 20h                                                        |

| Write            | Erase           | Data = 20h                                                        |

| Standby          |                 | Wait = 10 ms                                                      |

| Write            | Erase<br>Verify | Addr = Byte to Verify;<br>Data = A0h; Ends the Erase<br>Operation |

| Standby          |                 | Wait = 6 μs                                                       |

| Read             |                 | Read Byte to Verify Erasure;<br>Compare Output to FFh             |

|                  |                 |                                                                   |

| Write            | Read            | Data = 00h; Resets Register<br>for Read Operations                |

| Standby          |                 | Wait for Vpp to Ramp to<br>VppL (see Note 3)                      |

NOTES:

- 2 Refer to the recommended operating conditions for the value of VppH.

- 3 Refer to the recommended operating conditions for the value of VppL.

Figure 2. Flash-Erase Flowchart: Fasterase Algorithm

NOTE: n = number of devices being erased.

Figure 3. Parallel-Erase Flow Diagram

TEXAS INSTR (ASIC/MEMORY)

| solute maximum ratings over operating free-air temperature r   | <b>.</b> ,                     |

|----------------------------------------------------------------|--------------------------------|

| Supply voltage range, V <sub>CC</sub> (see Note 4)             |                                |

| Supply voltage range, VPP                                      | 0.6 V to 14 V                  |

| Input voltage range (see Note 5): All inputs except A9         | 0.6 V to V <sub>CC</sub> + 1 V |

| A9 (see Note 5)                                                | 0.6 V to 13.5 V                |

| Output voltage range (see Note 6)                              | 0.6 V to V <sub>CC</sub> + 1 V |

| Operating free-air temperature range during read/erase/program | 00                             |

| (NL, FML, DDL, DUL)                                            | 0°C to 70°C                    |

| Operating free-air temperature range during read/erase/program |                                |

| (NE, FME, DDE, DUE)                                            | 40°C to 85°C                   |

| Operating free-air temperature range during read/erase/program |                                |

| (NQ, FMQ, DDQ, DUQ)                                            | 40° C to 125°C                 |

| Storage temperature range                                      |                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 4. All voltage values are with respect to GND.

- 5. The voltage on any input pin may undershoot to -2.0 V for periods less than 20 ns.

- 6. The voltage on any output pin may overshoot to 7.0 V for periods less than 20 ns.

# ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY SMJS011A-DECEMBER 1992-REVISED MARCH 1993

### recommended operating conditions

|                 |                            |                                  |                               | '2<br>'2              | BF010-1<br>BF010-1<br>BF010-1<br>BF010-1 | 2<br>5               | UNIT     |

|-----------------|----------------------------|----------------------------------|-------------------------------|-----------------------|------------------------------------------|----------------------|----------|

|                 |                            |                                  |                               | MIN                   | TYP                                      | MAX                  |          |

| VCC             | Supply voltage             | During write/read/flash erase    | During write/read/flash erase |                       |                                          |                      | <b>V</b> |

| Vpp Supply      | Supply voltage             | During read only (VppL)          | During read only (Vppլ)       |                       |                                          | V <sub>CC</sub> + 2  | ٧        |

| TPP             | Oupply Voltage             | During write/read/flash erase (V | PPH)                          | 11.4                  | 12                                       | 12.6                 | V        |

| VIH             | High-level dc input        | h lavel de lavel vellage         |                               | 2                     |                                          | V <sub>CC</sub> +0.5 | · ·      |

| TIM             | riigh-lovel de impat       | Vollage                          | CMOS                          | V <sub>CC</sub> - 0.5 |                                          | V <sub>CC</sub> +0.5 | V        |

| V <sub>IL</sub> | Low-level dc input voltage |                                  | TTL                           | -0.5                  |                                          | 0.8                  | 14       |

| VIL.            | Low-level uc input v       | GND - 0.2                        |                               | GND+0.2               |                                          |                      |          |

# electrical characteristics over full ranges of operating conditions

|        | PARAMETER                                                   |                      | TEST CONDITIONS                                                                                                                   | MIN                   | TYP | MAX   | UNIT |

|--------|-------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-------|------|

| Vari   | High-level output voltage                                   |                      | I <sub>OH</sub> = - 2.5 mA                                                                                                        | 2.4                   |     |       | .,   |

| Vон    | nigh-level output voltage                                   |                      | I <sub>OH</sub> = - 100 μA                                                                                                        | V <sub>CC</sub> - 0.4 |     |       | ٧    |

| Vai    | Low lovel output voltage                                    |                      | IOL = 5.8 mA                                                                                                                      |                       |     | 0.45  | >    |

| VOL    | Low-level output voltage                                    |                      | l <sub>OL</sub> = 100 μA                                                                                                          |                       |     | 0.1   | V    |

| <br>In | Input current (leakage)                                     | All except A9        | V <sub>I</sub> = 0 to 5.5 V                                                                                                       |                       |     | ±1    | μΑ   |

|        | A9                                                          |                      | VI = 0 to 13 V                                                                                                                    |                       |     | ± 200 |      |

| Ю      | Output current (leakage)                                    |                      | VO = 0 to VCC                                                                                                                     |                       |     | ±10   | μΑ   |

| lan.   | Vpp supply current (read/sta                                | ndhu)                | Vpp = VppH, read mode                                                                                                             |                       |     | 200   | μА   |

| IPP1   | Abb arbbis critetir (teac/sta                               | пару)                | VPP = VppL                                                                                                                        |                       |     | ±10   | μА   |

| IPP2   | Vpp supply current (during p (see Note 7)                   | rogram pulse)        | Vpp = VppH                                                                                                                        |                       |     | 30    | mA   |

| IPP3   | Vpp supply current (during fl<br>(see Note 7)               | ash erase)           | Vpp = VppH                                                                                                                        |                       |     | 30    | mA   |

| IPP4   | VPP supply current (during p (see Note 7)                   | rogram/erase verify) | Vpp = VppH                                                                                                                        |                       |     | 5.0   | mA   |

| laaa   | VCC supply current (stand-                                  | TTL-Input level      | V <sub>CC</sub> = 5.5 V, <del>E</del> = V <sub>IH</sub>                                                                           |                       |     | 1     | mA   |

| Iccs   | by)                                                         | CMOS-input level     | V <sub>CC</sub> = 5.5 V, <del>E</del> = V <sub>CC</sub>                                                                           |                       |     | 100   | μΑ   |

| lCC1   | VCC supply current (active re                               | ead)                 | V <sub>CC</sub> = 5.5 V, E = V <sub>IL</sub> , f = 6 MHz, outputs open                                                            |                       |     | 30    | mA   |

| lCC2   | VCC average supply current (see Note 7)                     | (active write)       | VCC = 5.5 V, E = V <sub>IL</sub> , programming in progress                                                                        |                       |     | 10    | mA   |

| ССЗ    | V <sub>CC</sub> average supply current (see Note 7)         | (flash erase)        | VCC = 5.5 V, E = V <sub>IL</sub> , erasure in progress                                                                            |                       |     | 15    | mA   |

| ICC4   | V <sub>CC</sub> average supply current verify) (see Note 7) | (program/erase       | V <sub>CC</sub> = 5.5 V, $\overline{E}$ = V <sub>IL</sub> , V <sub>PP</sub> = V <sub>PPH</sub> , program/erase-verify in progress |                       |     | 15    | mA   |

NOTE 7: Not 100% tested; characterization data available.

TEXAS INSTR (ASIC/MEMORY)

# **ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY**

MJS011A-DECEMBER 1992-REVISED MARCH 1993

# capacitance over recommended ranges of supply voltage and operating free-air temperature, $f=1~\text{MHz}^\dagger$

|    | PARAMETER          | TEST CONDITIONS                | MIN | TYP | MAX | UNIT |

|----|--------------------|--------------------------------|-----|-----|-----|------|

| Ci | Input capacitance  | V <sub>I</sub> = 0 , f = 1MHz  |     |     | 6   | pF   |

| Co | Output capacitance | V <sub>O</sub> = 0 , f = 1 MHz | i i |     | 12  | pF   |

<sup>†</sup> Capacitance measurements are made on sample basis only.

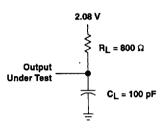

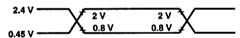

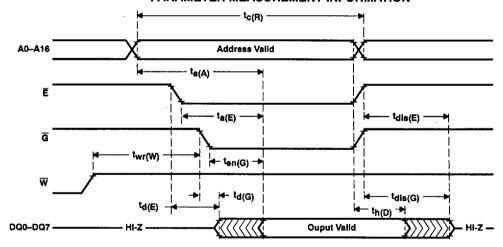

#### PARAMETER MEASUREMENT INFORMATION

Figure 4. AC Test Output Load Circuit

#### AC testing input/output wave forms

AC testing inputs are driven at 2.4 V for logic high and 0.45 V for logic low. Timing measurements are made at 2 V for logic high and 0.8 V for logic low on both inputs and outputs. Each device should have a 0.1  $\mu$ F ceramic capacitor connected between V<sub>CC</sub> and V<sub>SS</sub> as close as possible to the device pins.

# ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY SMJS011A-DECEMBER 1992-REVISED MARCH 1993

# switching characteristics over full ranges of recommended operating conditions

|                     | DECODURTION                                         | TEST                                                                     | ALTERNATE         | '28F01 | 0-10 | '28F0 | 10-12 | '28F0 | 10-15 | '28F0 | 10-17 | UNIT |

|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------|-------------------|--------|------|-------|-------|-------|-------|-------|-------|------|

| !                   | DESCRIPTION                                         | CONDITIONS                                                               | SYMBOL            | MIN    | MAX  | MIN   | MAX   | MIN   | MAX   | MiN   | MAX   | UNII |

| ta(A)               | Access time from address                            |                                                                          | †AVQV             | Ì      | 100  |       | 120   |       | 150   |       | 170   | ns   |

| <sup>t</sup> a(E)   | Access time from chip enable                        |                                                                          | †ELQV             |        | 100  |       | 120   |       | 150   |       | 170   | ns   |

| t <sub>en(G)</sub>  | Access time from output enable                      |                                                                          | <sup>t</sup> GLQV |        | 45   |       | 50    |       | 55    |       | 60    | ns   |

| <sup>t</sup> c(R)   | Read cycle time                                     |                                                                          | tavav             | 100    |      | 120   |       | 150   |       | 170   |       | ns   |

| <sup>t</sup> d(E)   | Delay time, chip<br>enable low to low-Z<br>output   | C <sub>L</sub> = 100 pF<br>1 Series 74                                   | <sup>t</sup> ELQX | 0      |      | 0     |       | 0     |       | 0     |       | ns   |

| <sup>t</sup> d(G)   | Delay time, output<br>enable low to low-Z<br>output | TTL Load<br>Input t <sub>r</sub> ≤ 20 ns<br>Input t <sub>f</sub> ≤ 20 ns | <sup>†</sup> GLQX | 0      |      | 0     |       | 0     |       | 0     |       | ns   |

| <sup>t</sup> dis(E) | Chip disable to hi-Z output                         |                                                                          | t <sub>EHQZ</sub> | 0      | 55   | 0     | 55    | 0     | 55    | 0     | 55    | ns   |

| <sup>t</sup> dis(G) | Hold time, output<br>enable to hi-Z output          |                                                                          | <sup>t</sup> GHQZ | 0      | 30   | 0     | 30    | 0     | 35    | 0     | 35    | ns   |

| t <sub>h(D)</sub>   | Hold time, data valid from address, E, or G†        |                                                                          | tAXQX             | 0      |      | 0     |       | 0     |       | 0     |       | ns   |

| t <sub>wr(W)</sub>  | Write recovery time<br>before read                  |                                                                          | twhgr             | 6      |      | 6     |       | 6     |       | 6     |       | μS   |

<sup>†</sup> Whichever occurs first.

**ADVANCE INFORMATION**

### AC characteristics-write/erase/program operations

| DESCRIPTION         |                                     | ALTERNATE         | '28F010-10 |     | '28F010-12 |     | '28F010-15 |     | '28F010-17 |     | UNIT |

|---------------------|-------------------------------------|-------------------|------------|-----|------------|-----|------------|-----|------------|-----|------|

|                     |                                     | SYMBOL            | MiN        | TYP | MIN        | TYP | MIN        | TYP | MIN        | TYP | UNIT |

| t <sub>c(W)</sub>   | Write cycle time                    | tavav             | 100        |     | 120        |     | 150        |     | 170        |     | ns   |

| tsu(A)              | Address setup time                  | †AVWL             | 0          |     | 0          |     | 0          |     | 0          |     | ns   |

| t <sub>h(A)</sub>   | Address hold time                   | tWLAX             | 55         |     | 60         |     | 60         |     | 70         |     | ns   |

| tsu(D)              | Data setup time                     | <sup>†</sup> D√WH | 50         |     | 50         |     | 50         |     | 50         |     | ns   |

| thw(D)              | Data hold time                      | twhox             | 10         |     | 10         |     | 10         |     | 10         |     | ns   |

| twr(W)              | Write recovery time before read     | twHGL             | 6          |     | 6          |     | 6          |     | 6          |     | μs   |

| trr(W)              | Read recovery time before write     | <sup>t</sup> GHWL | 0          |     | 0          |     | 0          |     | 0          |     | μS   |

| t <sub>su(E)</sub>  | Chip enable setup time before write | <sup>t</sup> ELWL | 20         |     | 20         |     | 20         |     | 20         |     | ns   |

| t <sub>h(E)</sub>   | Chip enable hold time               | <sup>†</sup> WHEH | 0          |     | 0          |     | 0          |     | 0          |     | ns   |

| tw(VV)              | Write pulse duration (see Note 8)   | †WLWH             | 60         |     | 60         |     | 60         |     | 60         |     | ns   |

| twh(W)              | Write pulse duration high           | <sup>‡</sup> WHWL | 20         |     | 20         |     | 20         |     | 20         |     | ns   |

| t <sub>c(W)B</sub>  | Duration of programming operation   | ™HWH1             | 10         |     | 10         |     | 10         |     | 10         |     | μs   |

| t <sub>c(E)B</sub>  | Duration of erase operation         | tWHWH2            | 9.5        | 10  | 9.5        | 10  | 9.5        | 10  | 9.5        | 10  | ms   |

| t <sub>su(P)E</sub> | Vpp setup time to chip enable low   | <sup>†</sup> ∨PEL | 1.0        |     | 1.0        |     | 1.0        |     | 1.0        |     | μs   |

| t <sub>su(E)P</sub> | Chip enable, setup time to Vpp ramp | <sup>t</sup> EHVP | 100        |     | 100        |     | 100        |     | 100        |     | ns   |

| t <sub>s(P)R</sub>  | Vpp rise time                       | tvppr             | 1          |     | 1          |     | 1          |     | 1          |     | μS   |

| t <sub>s(P)F</sub>  | Vpp fall time                       | t/PPF             | 1          |     | 1          |     | 1          |     | 1          |     | μS   |

NOTE 8: Rise/fall time ≤ 10 ns.

# alternative CE-controlled writes

|                     | DESCRIPTION                                | ALTERNATE         | '28F010-10 |     | '28F010-12 |     | '28F010-15 |     | '28F010-17 |     | LINUT |

|---------------------|--------------------------------------------|-------------------|------------|-----|------------|-----|------------|-----|------------|-----|-------|

| DESCRIPTION         |                                            | SYMBOL            | MIN        | MAX | MIN        | MAX | MIN        | MAX | MIN        | MAX | UNIT  |

| t <sub>c</sub> (W)  | Write cycle time                           | t <sub>AVAV</sub> | 100        |     | 120        |     | 150        |     | 170        |     | ns    |

| <sup>t</sup> su(A)  | Address setup time                         | †AVEL             | 0          |     | 0          |     | 0          |     | 0          |     | ns    |

| ħE(A)               | Address hold time                          | tELAX             | 75         |     | 80         |     | 80         |     | 90         |     | ns    |

| <sup>t</sup> su(D)  | Data setup time                            | <sup>t</sup> DVEH | 50         |     | 50         |     | 50         |     | 50         |     | ns    |

| thE(D)              | Data hold time                             | tEHDX             | 10         |     | 10         |     | 10         |     | 10         |     | ns    |

| t <sub>wr(E)</sub>  | Write recovery time before read            | <sup>t</sup> EHGL | 6          |     | 6          |     | 6          |     | 6          |     | μs    |

| <sup>t</sup> rr(E)  | Read recovery time before write            | <sup>t</sup> GHEL | 0          |     | 0          |     | 0          |     | 0          |     | μs    |

| <sup>t</sup> su(W)  | Write enable setup time before chip enable | tWLEL             | 0          |     | 0          |     | . 0        |     | 0          |     | ns    |

| th(W)               | Write enable hold time                     | tEHWH             | 0          |     | 0          |     | 0          |     | 0          |     | ns    |

| <sup>t</sup> w(E)   | Write pulse duration                       | teleh             | 70         |     | 70         |     | 70         |     | 80         |     | ns    |

| twh(E)              | Write pulse duration high                  | tEHEL.            | 20         |     | 20         |     | 20         |     | 20         |     | ns    |

| <sup>t</sup> su(P)E | Vpp setup time to chip enable low          | ¹∨PEL             | 1.0        |     | 1.0        |     | 1.0        |     | 1.0        |     | με    |

| tc(W)B              | Duration of programming operation          | teheh             | 10         |     | 10         |     | 10         |     | 10         |     | μs    |

#### PARAMETER MEASUREMENT INFORMATION

Figure 5. Read Cycle Timing

SMJS011A-DECEMBER 1992-REVISED MARCH 1993

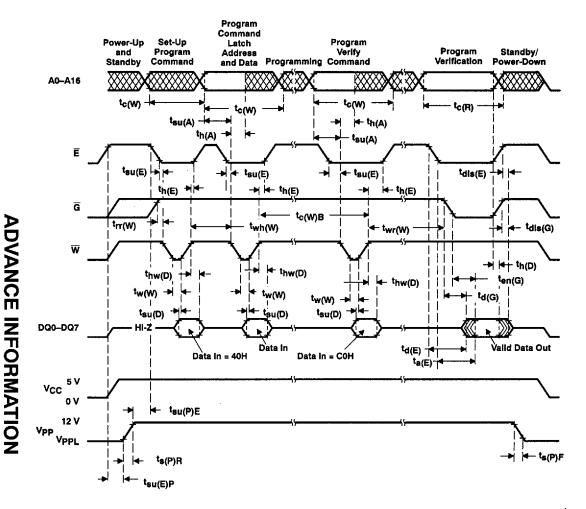

#### PARAMETER MEASUREMENT INFORMATION

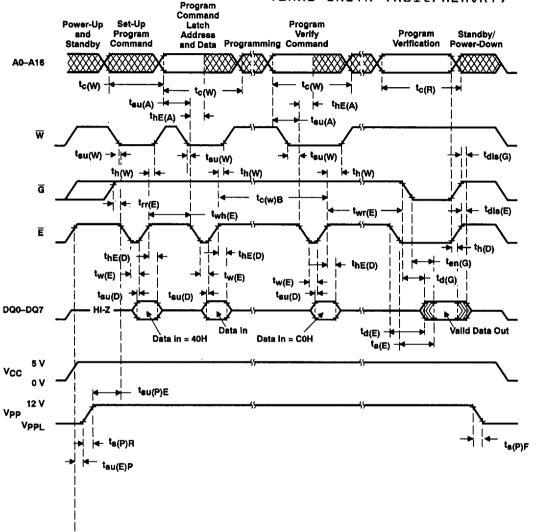

Figure 6. Write Cycle Timing

#### PARAMETER MEASUREMENT INFORMATION

Figure 7. Write Cycle (Alternative CE-Controlled Writes) Timing

#### PARAMETER MEASUREMENT INFORMATION

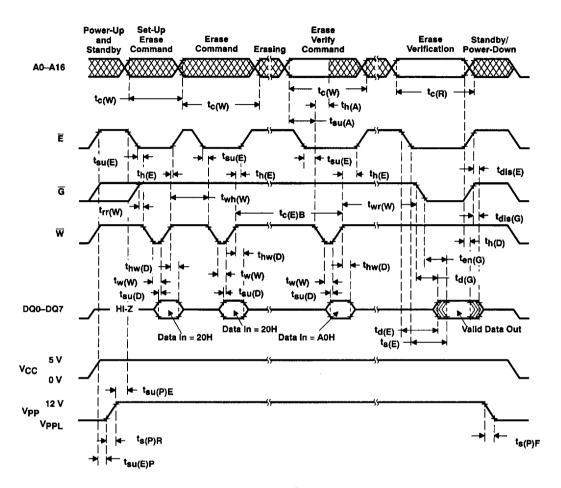

Figure 8. Flash-Erase Cycle Timing

TEXAS INSTR (ASIC/MEMORY)