#### US005459839A

## United States Patent [19]

Swarts et al.

[11] Patent Number:

5,459,839

[45] Date of Patent:

Oct. 17, 1995

### [54] SYSTEM AND METHOD FOR MANAGING QUEUE READ AND WRITE POINTERS

[75] Inventors: Jeffery L. Swarts, Falls Church; Gary L. Rouse, Manassas, both of Va.

[73] Assignee: International Business Machines

Corporation, Armonk, N.Y.

[21] Appl. No.: 293,930

[22] Filed: Aug. 22, 1994

### Related U.S. Application Data

|     |    | Int. Cl. <sup>6</sup>        | -                            |

|-----|----|------------------------------|------------------------------|

| [63 | 3] | Continuation of Ser. No. 755 | 468, Sep. 5, 1991, abandoned |

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,507,760 | 3/1985  | Fraser        | 365/221 |

|-----------|---------|---------------|---------|

| 4,682,284 | 7/1987  | Schrofer      | 395/425 |

| 4,807,111 | 2/1989  | Cohen et al.  | 395/250 |

| 4,816,996 | 3/1989  | Hill et al.   | 395/275 |

| 4,878,166 | 10/1989 | Johnson et al | 395/425 |

#### OTHER PUBLICATIONS

IBM TDB, vol. 24, No. 6 to Conroy, entitled "Hardware/Microcode Support Of Queuing", Nov. 1981, pp. 2716–2723.

Primary Examiner—Rebecca L. Rudolph Assistant Examiner—Reginald G. Bragdon Attorney, Agent, or Firm—Joseph C. Redmond, Jr.; John D. Flynn

### [57] ABSTRACT

A queue pointer manager contained in an integrated data controller is capable of controlling high speed data transfers between a high speed controlled data channel, a local processor bus and a dedicated local data bus. The overall design utilizes enhanced features of the Micro Channel architecture and data buffering to achieve maximum burst rates of 80 megabytes and to allow communications with 8, 16, 32 and 64 bit Micro Channel devices. Queued demands allow flexible programming of the Micro Channel master operations and reporting of completion statuses. The hardware control of command and status queuing functions increases the processing speed of control operations and reduces the need for software queuing. Extensive error checking/reporting, programming parameters, internal wrap self-test capability give the integrated data controller advanced functions as an input/output processor. The queue pointer manager also manages queue read and write point-

## 21 Claims, 56 Drawing Sheets

FIG. 2

FIG. 3B

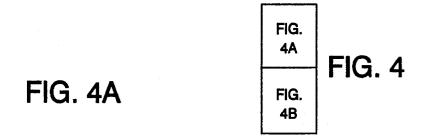

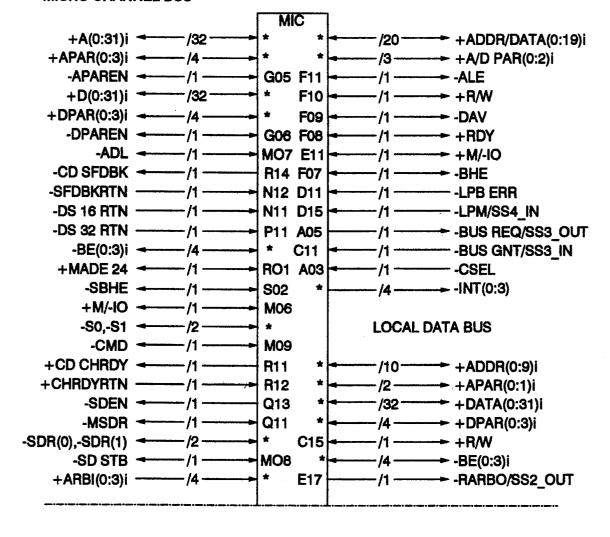

### MICRO CHANNEL BUS

FIG. 4B

FIG. 5

FIG. 60

NOTE: FOR ALL FIGURES THE FOLLOWING IS TRUE:

WHEN THE MUX SEL = 0, DATA INPUT B(X) IS SELECTED AND

WHEN THE MUX SEL = 1, DATA INPUT A(X) IS SELECTED.

FIG. 6E

FIG. 9

FIG. 11

FIG. 13

FIG. 14

SHUTDWN1 = ERRIN & ERRIN D1 & TRT EXP

SHUTDWN2 = ERRIN & ERRIN D1 & 2NDTOK

ERRRPT = ERROR REPORTED

= ERRIN & ERRIN D1 & TOKOUT STARTUP

= SHUTDWN1 & TOKDET & THT EXP NXTST LB

TOKREL = TOKOUT & SHUTDWN2 & 2ND TOK

= TOKIN & SHUTDWN1 & THT EXP TOKDET

= SHUTDWN2 & TOKREL & 2NDTOK NXTST\_2B

TRT\_EXP = TOKEN HOLD TIMER EXPIRED

2NDTOK = TOKIN

FIG. 15A-1

## FIG. 15A-2

Oct. 17, 1995

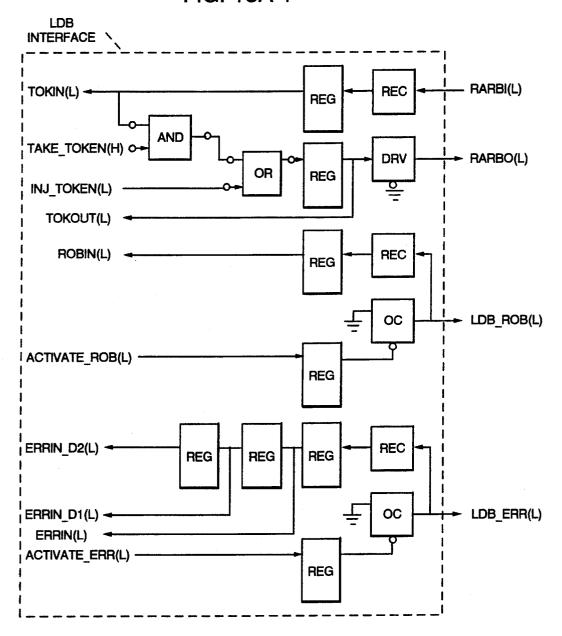

REC = RECEIVER, REG = REGISTER,

OC = OPEN COLLECTOR DRIVER, DRV = DRIVER

INJ\_TOKEN(L) = [STATE0 & RING\_MASTER & ERRIN & ERRIN\_D1 & TOKOUT + [STATE2 & TOKIN & RELOWN]

TAKE\_TOKEN(H) = [STATE1 & REQBUS & TOKDET] = [STATE1 & TRT\_EXP] + STATE2 & STATE3 + SYSRESET + [STATE0 & (ERRIN + ERRIN\_D1 + ERRIN\_D2)]

ACTIVATE\_ROB(L) = REQBUS & [(STATE1 & TOKIN) + (STATE2 & TOKOUT)]

ACTIVATE\_ERR(L) = STATE3 + (STATE1 & TRT-EXP) + (STATE2 & 2NDTOK)

RELOWN = RELEASE OWNERSHIP = STATE2 & TOKOUT & (THT\_EXP + REQBUS)

RELOWN = RELEASE OWNERSHIP

RPE = RING PARTICIPATE ENABLE

REQBUS = INTERNAL CHIP REQUEST TO USE BUS

RING\_MASTER = INITIALIZATION REGISTER THAT TELLS

DEVICE TO START RING IF IT WAS DOWN.

FIG. 16

FIG. 18

HA IS DEFINED AS LDB HIGH ADDRESS LA IS DEFINED AS LDB LOW ADDRESS

FIG. 19

HA IS DEFINED AS LDB HIGH ADDRESS LA IS DEFINED AS LDB LOW ADDRESS

THE SIGNALS ABOVE REPRESENT THE LDB INTERFACE AT THE MIC'S I/O PINS.

FIG. 20

THE SIGNALS ABOVE REPRESENT THE LDB INTERFACE AT THE MIC'S I/O PINS.

|        | MSB |     |     |     |           |     |     |     |    |     |      |      |    |    |          | LSB      |     |

|--------|-----|-----|-----|-----|-----------|-----|-----|-----|----|-----|------|------|----|----|----------|----------|-----|

| IBM    | 0   | .1  | 2   | 3   | 4<br>11 1 | 5   | 6   | 7   | 8  | 9   | _10  | 11   | 12 | 13 | 14       | 15       |     |

| VEN    | 15  | 14  | 13  | 12  | 77  7     | U   | 9   | 8   | /  | 0   | ן כ  | 4    | ၁  | 2  | <u> </u> | <u> </u> |     |

| WORD 0 | RET | ΓUR | N Q | ID  | REF       | ERI | ENC | EIC | )  |     | DE\  | /ICE | ID |    |          |          | LSB |

| WORD 1 |     |     | N   | 110 | CONT      | RO  | L B | LOC | KA | DDF | RESS | 3    |    |    |          |          | MSB |

## WORD BITS NAME: DESCRIPTION

| 0 | 0-3 I<br>15-12V  | RETURN QUEUE IDENTIFICATION (RQID) NUMBER: INDICATES THE QUEUE NUMBER WHICH THE MIC WILL RETURN THE MSW TO AT THE END OF THE COMMAND TRANSFER.                                                                                    |

|---|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 4-7 !<br>11-8 V  | REFERENCE IDENTIFICATION (RID) NUMBER: SOFTWARE POINTER TO REFERENCE THE MCW WITH THE MSW & MPC. NOTE: THIS FIELD HAS NO RELEVANCE TO MI OPERATIONS AND CAN BE REDEFINED AND USED BY SOFTWARE.                                    |

| 0 | 8-15 I<br>7-0 V  | DEVICE IDENTIFICATION (DID) NUMBER: SOFTWARE POINTER OR DEVICE REFERENCE FIELD. NOTE: THIS FIELD HAS NO RELEVANCE TO MIC OPERATIONS AND CAN BE REDEFINED AND USED BY SOFTWARE.                                                    |

| 1 | 0-15 I<br>15-0 V | MIC CONTROL BLOCK ADDRESS (MCB ADDR): THE UPPER 16-BITS OF THE LPB MEMORY ADDRESS WHERE THE MCB OR FIRST MCB IN A CHAIN CAN BE FOUND. THE STARTING MCB ADDRESS IS GENERATED BY THE FOLLOWING; MCB LPB ADDRESS = MCB ADDRESS: 0000 |

|        | MSB LSB              |      |      |      |      |        |     |      | ,   |    |    |      |      |    |     |

|--------|----------------------|------|------|------|------|--------|-----|------|-----|----|----|------|------|----|-----|

| IBM    | 0 1 2                | 3    | 4    | 5    | 6    | 7<br>8 | 8   | 9    | 10  | 11 | 12 | 13   | 14   | 15 |     |

| VEN    | 15 14 13             | 12   | 11   | 10   | 9    | 8      | 7   | 6    | 5   | 4  | 3  | 2    | 1    | 0  |     |

| WORD 0 | OPE                  | PCI  | JMP  | CHN  | NOP  | FMT    | BUF | PST  | WAT | 0  | 0  | 0    | AB   | М  | LSB |

| WORD 1 | MIC DEVIC            | E QU | JEUE | CON  | NTRO | )L I/C | ADI | DRES | SS  | 0  | MP | C QL | JEUE | ID |     |

| WORD 2 | SOURCE ADDRESS (MSB) |      |      |      |      |        |     |      |     |    |    |      |      |    |     |

| WORD 3 | SOURCE A             | DDR  | ESS  | (LSB | )    |        | 0   | 0    | 0   | 0  | 0  | 0    | 0    | 0  |     |

| WORD 4 | COMMAND              | /STA | TUS  | FLAC | 3S   |        |     |      |     |    |    |      |      |    |     |

| WORD 5 | TARGET ADDRESS (MSB) |      |      |      |      |        |     |      |     |    |    |      |      |    |     |

| WORD 6 | TARGET ADDRESS (LSB) |      |      |      |      |        |     |      |     |    |    |      |      |    |     |

| WORD 7 | BLOCK LEN            | NGTH |      |      |      |        |     |      |     |    |    |      | ···  |    | MSB |

| WORD | BITS             | NAME: DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0 - 21<br>15-13V | OPERATION (OPE):  THIS FIELD DEFINES THE DATA MOVEMENT DURING THE COMMANDED TRANSFER.  000 = LDB TO MICRO CHANNEL I/O ADDRESS SPACE.  001 = LDB TO MICRO CHANNEL MEMORY ADDRESS SPACE.  010 = MICRO CHANNEL I/O ADDRESS SPACE TO LDB.  011 = MICRO CHANNEL MEMORY ADDRESS SPACE TO LDB.  1XX = LDB TO LDB, WRAP OPERATION.  NOTE: THE CEN FIELD IN POS REGISTER 2 MUST BE DISABLED WHEN OPE = '1XX', LDB TO LDB WRAP OPERATION.  CEN MUST BE ENABLED WHEN OPE = '0XX'. |

| 0    | 3 I<br>12V       | PROGRAM CONTROLLED INTERRUPT (PCI):  0 = THE MIC WILL NOT POST A MSW TO A QUEUE AT THE END OF THE COMMANDED TRANSFER UNLESS THERE WAS AN ERROR.  1 = THE MIC WILL BUILD AND POST A MSW TO THE QUEUE NUMBER DEFINED IN THE RQID AT THE END OF THE COMMANDED XFER.                                                                                                                                                                                                       |

|      | <del>,</del> | 110.25                                                                                                                                                                                                                                                                                                                                                    |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WORD | BITS         | NAME: DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |

| 0    | 4 I<br>11 V  | JUMP (JMP):  0 = NO JUMP.  1 = THE MIC WILL USE THE LEAST SIGNIFICANT  16-BITS OF THE SOURCE ADDRESS FIELD  IN FORMING THE ADDRESS OF THE NEXT MCB.                                                                                                                                                                                                       |

| 0    | 5 I<br>10 V  | CHAIN (CHN):  0 = NO CHAINING.  1 = THE ADDRESS OF THE NEXT MCB IS EQUAL  TO THE CURRENT STARTING MCB ADDRESS  PLUS 16 BYTES.                                                                                                                                                                                                                             |

| 0    | 6 I<br>9 V   | NO OPERATION (NOP):  0 = NO NO-OP  1 = MIC WILL ONLY PROCESS THE PCI FLAG.  NO ACTUAL DATA OR COMMANDED TRANS-FER WILL OCCUR.                                                                                                                                                                                                                             |

| 0    | 7 I<br>8 V   | FORMAT (FMT):  THIS BIT INDICATES WHETHER DATA MOVEMENT DURING THE COMMANDED TRANSFER WILL OCCUR.  0 = DURING A DATA BLOCK MOVE OPERATION THE DESTINATION ADDRESS IS SPECIFIED BY THE TARGET ADDRESS.  1 = DURING A DATA BLOCK MOVE OPERATION THE DESTINATION ADDRESS IS READ FROM THE FREE BLOCK LIST POINTED TO BY THE MC DEVICE QUEUE CONTROL ADDRESS. |

| 0    | 8 I<br>7 V   | FREE BLOCK REQUEST (BUF):  0 = DURING A DATA BLOCK MOVE OPERATION  THE DESTINATION ADDRESS IS SPECIFIED BY  THE TARGET ADDRESS.  1 = DURING A DATA BLOCK MOVE OPERATION  THE DESTINATION ADDRESS IS READ FROM  THE FREE BLOCK LIST POINTED TO BY THE  MC DEVICE QUEUE CONTROL ADDRESS.                                                                    |

| 0    | 9 I<br>6 V   | POST COMMAND / STATUS REQUEST (PST):  0 = NO MPC WILL BE SENT TO A MC DEVICE AFTER THE COMPLETION OF THE COMMANDED TRANSFER.  1 = A MPC WILL BE BUILT AND SENT TO THE QUEUE DEFINED IN MPC QUEUE ID FIELD TO THE ADDRESS DEFINED BY THE MC DEVICE QUEUE CONTROL ADDRESS AFTER THE COMPLETION OF THE COMMANDED TRANSFER.                                   |

| WORD | BITS              | NAME: DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 10 I<br>5 V       | WAIT (WAT)  0 = THE MIC WILL PROCESS THE MCB IMMEDIATELY AND WILL CONTINUE TO READ THE REMAINING WORDS OF THE MCB.  1 = THE MCI WILL NOT PROCESS THE MCB AND WILL CONTINUE TO REREAD MCB WORD 0 UNTIL WAT=0.  NOTE: THE MIC WILL REREAD MCB WORD 0  APPROXIMATELY EVERY 256 CLOCK CYCLES (10.24 µSEC), AUTOMATICALLY.                                                                                                                  |

| 0    | 11-13 I<br>4- 2 V | RESERVED AT A VALUE OF '0'.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0    | 14-15 I<br>1- 0 V | ADDRESS BURST MANAGEMENT (ABM)  THIS FIELD DEFINES THE ABM SIZE USED FOR THE COMMANDED TRANSFER WRITES. THESE BITS OVERRIDE THE ABM FIELD DEFINED IN THE MC POS REGISTER 4 SUB-ADDRESS 0000. 00 = ABM DEFINED IN THE POS REGISTER (DEFAULT) 01 = 16 BYTE ADDRESS BOUNDARY. 10 = 32 BYTE ADDRESS BOUNDARY. 11 = 64 BYTE ADDRESS BOUNDARY. NOTE: THIS FIELD IS ONLY VALID WHEN OPE=00X.                                                  |

| 1    | 0-11 I<br>15- 4 V | MC DEVICE QUEUE CONTROL I/O ADDRESS:  THIS FIELD DEFINES THE STARTING MC I/O ADDRESS LOCATION WHERE THE MIC CAN ACCESS CONTROL REGISTERS NECESSARY TO COMPLETE A QUEUE OR FREE BLOCK FETCH OPERATION. THESE CONTROL REGISTER SHOULD HAVE THE SAME FORMAT AS THE MIC'S I/O CONTROL REGISTERS (QRC, QWC, QD, AND FB REGISTERS) AND SHOULD BE LOCATED AT THE FOLLOWING ADDRESS OFFSETS; QRCR = 0000, QWCR = 0100, QDR = 1000, FBR = 1100. |

| 1    | 12-15 l<br>3- 0 V | MICRO CHANNEL POST COMMAND QUEUE ID (MPC QID): THIS FIELD DEFINES THE QUEUE NUMBER ON ANOTHER MC DEVICE WHERE THE MPC CAN BE POSTED TO. THE RECEIVING QUEUE'S BYTE COUNT IS 8 BYTES.                                                                                                                                                                                                                                                   |

| 2    | 0-15 l            | SOURCE ADDRESS (MSB): THE HIGH ORDER ADDRESS BITS USED TO SOURCE DATA WHICH WILL BE MOVED DURING THE COMMANDED TRANSFER. FMT MUST EQUAL '0', TO USE THIS FIELD.                                                                                                                                                                                                                                                                        |

| WORD | BITS             | NAME: DESCRIPTION                                                                                                                                                                 |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | 0-15 l<br>15-0 V | SOURCE ADDRESS (LSB): THE LOW ORDER ADDRESS BITS USED TO SOURCE DATA WHICH WILL BE MOVED DURING THE COMMANDED TRANSFER. ALSO, THESE BITS DEFINE THE MCB LPB ADDRESS WHEN JMP='1'. |

| 4    | 0-7 I<br>15-8 V  | COMMAND / STATUS FLAGS: FLAGS USED FOR COMMAND / STATUS TRANSFERS. THIS WORD SPECIFIES NO MIC FUNCTION AND CAN BE USED FOR SOFTWARE DEFINED FUNCTIONS AND FLAGS.                  |

| 4    | 8-15 I<br>7-0 V  | RESERVED AT A VALUE OF '0'.                                                                                                                                                       |

| 5    | 0-15 I<br>15-0 V | TARGET ADDRESS (MSB): THE HIGH ORDER ADDRESS BITS USED TO TARGET DATA WHICH WILL BE MOVED DURING THE COMMANDED TRANSFER. NOTE: THE MPC DOES NOT USE THE 8 MSB OF THIS FIELD.      |

| 6    | 0-15 I<br>15-0 V | TARGET ADDRESS (LSB): THE LOW ORDER ADDRESS BITS USED TO TARGET DATA WHICH WILL BE MOVED DURING COMMANDED TRANSFER.                                                               |

| 7    | 0-15 l<br>15-0 V | BLOCK LENGTH: THE NUMBER OF BYTES WHICH WILL BE MOVED DURING THE COMMANDED TRANSFER.                                                                                              |

FIG. 28

| COMMANDED OPERATION   | OPE | PCI | JMP | CHN | NOP | FMT | BUF | PST | WAT |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| LDB TO MC I/O ADDR    | 000 | х   | 0   | х   | 0   | 0   | 0   | 0   | X   |

| LDB TO MC MEMORY ADDR | 001 | х   | 0   | Х   | 0   | 0   | 0   | X   | х   |

|                       | 001 | х   | 0   | Х   | 0   | 0   | 1   | 1   | х   |

| MC I/O ADDR TO LDB    | 010 | х   | 0   | Х   | 0   | 0   | 0   | 0   | х   |

| MC MEMORY ADDR TO LDB | 011 | х   | 0   | Х   | 0   | 0   | 0   | 0   | Х   |

| LDB TO LDB WRAP       | 1XX | х   | 0   | х   | 0   | 0   | 0   | 0   | Х   |

| POSTING ONLY          | oxx | х   | *   | *   | 0   | 1   | 0   | 1   | х   |

| NOP                   | xxx | х   | *   | *   | 1   | X   | x   | 0   | x   |

JMP CHN

\* - VALID CHAIN AND JUMP FLAGS ARE DEFINED IN THIS FIGURE

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | LAST MCB  MCB = MCB +16  MCB = SRC ADDR  ILLEGAL |

|------------------|------------------|--------------------------------------------------|

|                  |                  |                                                  |

# FIG. 29A

|            | MSE                       | }      |     |    |                |     |    |      |             |     |     |      |      |      | 1   | _SB |        |

|------------|---------------------------|--------|-----|----|----------------|-----|----|------|-------------|-----|-----|------|------|------|-----|-----|--------|

| IBM<br>VEN | 0                         | 1      | 2   | 3  | 4              | 5   | 6  | 7    | 8           | 9   | 10  | 11 4 | 12   | 13   | 14  | 15  |        |

| VEN        | 10                        | 1 1 -7 | 113 | 12 | 111            | 110 | 19 | 1 0  | 1 /         | 10  | 1 5 | 1 41 | 3    | 12   | 1 1 | U   | !<br>- |

| WORD 0     | 1                         | 1      | 0   | 1  | 1 REFERENCE ID |     |    | E ID | D DEVICE ID |     |     |      |      |      | LSB |     |        |

| WORD 1     | 0                         | 0      | 0   |    | MXSM STATE     |     |    | 0    | 0           | 0   | FBR | 1    | MXSI | и RC |     |     |        |

| WORD 2     | 0                         | 0      | 0   | 0  | 0              | 0   | 0  | 0    | 0           | 0   | 0   | 0    | 0    | 0    | 0   | 0   | 1      |

| WORD 3     | MIC CONTROL BLOCK ADDRESS |        |     |    |                |     |    |      |             | мѕв |     |      |      |      |     |     |        |

|      | <del>                                     </del> |                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WORD | BITS                                             | NAME: DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |

| 0    | 0- 31<br>15-12 V                                 | THESE BITS DEFINE THE SOURCE QUEUE NUMBER OF THE MSW, WHICH FOR THE MIC IS QUEUE # D ('1101')                                                                                                                                                                                                                                                                                    |

| 0    | 4- 7 <br>11- 8V                                  | REFERENCE IDENTIFICATION (RID) NUMBER: SOFTWARE POINTER TO REFERENCE THE MCW WITH THE MSW.                                                                                                                                                                                                                                                                                       |

| 0    | 8-15 I<br>7- 0 V                                 | DEVICE IDENTIFICATION (DID) NUMBER: SOFTWARE POINTER TO REFERENCE THE MCW WITH THE MSW.                                                                                                                                                                                                                                                                                          |

| 1    | 0- 21<br>15-13 V                                 | RESERVED AT A VALUE OF '0'.                                                                                                                                                                                                                                                                                                                                                      |

| 1    | 3- 7 I<br>12- 8 V                                | MASTER EXECUTION STATE MACHINE STATE: THIS FIELD DEFINES THE STATE WHICH THE MASTER EXECUTION UNIT WAS IN AT THE END OF THE COMMANDED TRANSFER. IF NO ERROR OCCURRED THEN MXSM STATE = '00000'.                                                                                                                                                                                  |

| 1    | 8-10 l<br>7-5 V                                  | RESERVED AT A VALUE OF '0'                                                                                                                                                                                                                                                                                                                                                       |

| 1    | 11 I<br>4 V                                      | FREE BLOCK RETURN (FBR):  THIS INDICATES THAT AN ERROR HAS OCCURRED WHICH REQUIRED THE MIC TO RETURN A FETCHED FREE BLOCK FROM ANOTHER MC DEVICE. IF MCB FIELD BUF='0' THEN THIS FIELD IS INVALID.  0 = THE MIC WAS UNSUCCESSFUL IN RETURNING THE FB TO THE MC DEVICE IT WAS FETCHED FROM.  1 = THE MIC WAS SUCCESSFUL IN RETURNING THE FB TO THE MC DEVICE IT WAS FETCHED FROM. |

|      |                                                  | TO THE MIC DEVICE IT WAS PETCHED FF                                                                                                                                                                                                                                                                                                                                              |

|      |                                                  |                                                                                                                                                                                                                                                                                                                                                                                  |

5,459,839

| <br> <br> |                  |                                                                                                                                     |

|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1         | 12-15 I<br>3-0 V | MASTER EXECUTION STATE MACHINE RETURN CODE:<br>THIS FIELD INDICATES THE COMPLETION STATUS<br>OF THE COMMANDED TRANSFER OPERATION. * |

| 2         | 0-15 I<br>15-0 V | RESERVED AT A VALUE OF '0'.                                                                                                         |

| 3         | 0-15 l<br>15-0 V | MCB ADDRESS: THE UPPER 16-BITS OF THE LPS MEMORY ADDRESS WHERE THE MCB OR LAST MCB WAS USED FOR THE COMMANDED TRANSFER.             |

FIG. 29A FIG. 29B

FIG. 29

FIG. 29B

| IBM<br>VEN | MSB   0   1   2   3   15   14   13   12 | 4   5   6   7<br> 11  10   9   8 | 8   9  10  11  12  13  14<br>  7   6   5   4   3   2   1 | LSE<br>15<br>0 | 3   |  |  |

|------------|-----------------------------------------|----------------------------------|----------------------------------------------------------|----------------|-----|--|--|

| WORD 0     | MC SOURCE ID                            | REFERENCE ID                     | DEVICE ID                                                |                | LSB |  |  |

| WORD 1     | COMMAND/S1                              | TARGET ADDRESS (MSB)             |                                                          |                |     |  |  |

| WORD 2     | TARGET ADDRESS (LSB) FER                |                                  |                                                          |                |     |  |  |

| WORD 3     | BLOCK LENGTH                            |                                  |                                                          |                |     |  |  |

|      | T                                   |                                                                                                                                                                                                                                                                                              |

|------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WORD | BITS                                | NAME: DESCRIPTION                                                                                                                                                                                                                                                                            |

| 0    | 0-31<br>15-12V                      | MC SOURCE ID/DEVICE ADDRESS: THESE BITS DEFINE THE MICS MICRO CHANNEL DEVICE ADDRESS. THESE BITS ARE EQUAL TO THE POS REQ2 DEVICE ADDR FIELD.                                                                                                                                                |

| 0    | 4-7 I<br>11-8 V                     | REFERENCE IDENTIFICATION (RID) NUMBER: SOFTWARE POINTER TO REFERENCE THE MCW WITH THE MSW.                                                                                                                                                                                                   |

| 0    | 8-15 I<br>7- 0 V                    | DEVICE IDENTIFICATION (DID) NUMBER:<br>SOFTWARE DEFINABLE.                                                                                                                                                                                                                                   |

| 0    | 0-71<br>15-8 V                      | COMMAND/STATUS FLAGS: FLAGS USED FOR COMMAND / STATUS TRANSFERS. THIS WORD SPECIFIES NO MIC FUNCTION AND CAN BE USED FOR SOFTWARE DEFINED FUNCTIONS AND FLAGS.                                                                                                                               |

| 1 2  | 8-15 I<br>7-0 V<br>0-14 I<br>15-1 V | TARGET ADDRESS: THESE BITS DEFINE THE LOWER 24BITS OF MC MEM ADDR WHERE THE MIC MOVED DATA TO. THIS ADDRESS FIELD IS EITHER THE TARGET ADDRESS DEFINED IN THE MCB OR THE FB ADDRESS FETCHED FROM THE MC DEVICE, DEPENDING ON THE MCB BUF FIELD                                               |

| 2    | 15 I<br>0 V                         | FREE BLOCK ERROR (FER): THIS FIELD DEFINES WHETHER THE TARGET ADDRESS WAS REALLY USED AS THE TARGET ADDRESS. ONLY VALID IF BUF='1'. 0 = TARGET ADDRESS VALID. 1 = TARGET ADDRESS BEING RETURNED, UNUSED ADDRESS. COMMANDED TRANSFER CONTAINED AN ERROR AND THE FREE BLOCK IS BEING RETURNED. |

| 3    | 0-15                                | BLOCK LENGTH:                                                                                                                                                                                                                                                                                |

|      | 15-0 V                              | THE NUMBER OF BYTES WHICH WERE MOVED DURING<br>A COMPLETED CT OR WERE SUPPOSED TO BE MOVED<br>FOR THE CT.                                                                                                                                                                                    |

5,459,839

FIG. 33

# FIG. 34A

|        | MSE         | 3  |         |                                                                                     | LSB     |

|--------|-------------|----|---------|-------------------------------------------------------------------------------------|---------|

| IBM    | 0           | 1  | 2 3     | 4   5   6   7   8   9   10   11   12   13   11   10   9   8   7   6   5   4   3   2 | 14   15 |

| VEN    | 15          | 14 | 13   12 | 11  10  9  8  7  6  5  4  3  2                                                      | 1 0     |

| WORD 0 | 0           | 0  | QBC     | QUEUE READ POINTER (QRP)                                                            | Q RPS   |

| WORD 1 | Q INTERRUPT |    |         | QUEUE WRITE POINTER (QWP)                                                           | Q WPS   |

| 0-1 I<br>15-14 V<br>2-3 I<br>13-12 V | RESERVED AT A '0' LEVEL.  QUEUE BYTE COUNT (QBC): DEFINES THE NUMBER OF BYTES FOR A QUEUE ENTRY.                                                                                                                                                                                                                                                                                       |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | DEFINES THE NUMBER OF BYTES FOR A QUEUE ENTRY.                                                                                                                                                                                                                                                                                                                                         |

|                                      | 00 - 4BYTES (1K Q ENTRIES) 10 - UNDEFINED<br>01 - 8BYTES (512 Q ENTRIES) 11 -16BYTES (256 Q ENTRIES)                                                                                                                                                                                                                                                                                   |

| 4-13 I<br>11-2 V                     | QUEUE READ POINTER (QRP): DEFINES THE CURRENT VALUE OF THE QUEUE READ POINTER. FOR 4 BYTE QUEUES ALL 10-BITS ARE VALID, FOR 8 BYTE QUEUES ONLY THE UPPER 9-BITS ARE VALID, AND FOR 16 BYTE QUEUES ONLY THE UPPER 8-BITS ARE VALID. NON-VALID BITS MUST BE SET TO '0'.                                                                                                                  |

| 14-15 I<br>1-0 V                     | QUEUE READ POINTER STATUS (Q RPS): DEFINES THE CURRENT STATUS FOR THE READ POINTER. 00 = POINTER IS AVAILABLE AND VALID. 01 = POINTER IS TEMP. BEING USED BY ANOTHER LPB DEVICE. 10 = THE QUEUE IS EMPTY. 11 = THE QUEUE IS NOT ENABLED, POINTER IS INVALID.                                                                                                                           |

| 0-3 I<br>15-12 V                     | QUEUE INTERRUPT (QI):  DEFINES THE INTERRUPT USED TO INDICATE THAT A QUEUE CONTAINS A QUEUE ENTRY.  0000 - DISABLED 1000 - MC IRQ(0)  0001 - RESERVED 1001 - MC IRQ(1)  0010 - RESERVED 1010 - MC IRQ(2)  0011 - RESERVED 1011 - MC IRQ(3)  0100 - LPB INT(0) 1100 - RESERVED  0101 - LPB INT(1) 1101 - RESERVED  0110 - LPB INT(2) 1110 - RESERVED  0111 - LPB INT(3) 1111 - RESERVED |

|                                      | 11-2 V<br>14-15 I<br>1-0 V                                                                                                                                                                                                                                                                                                                                                             |

| <br> <br> <br> |                  |                                                                                                                                                                                                                                                                       |

|----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 4-13 I<br>11-2 V | QUEUE WRITE POINTER (QWP):  DEFINES THE CURRENT VALUE OF THE QUEUE WRITE POINTER.  FOR 4 BYTE QUEUES ALL 10-BITS ARE VALID, FOR 8 BYTE QUEUES ONLY THE UPPER 9-BITS ARE VALID, FOR 16 BYTE QUEUES ONLY THE UPPER 8-BITS ARE VALID. NON-VALID BITS MUST BE SET TO '0'. |

| 1              | 14-15 I<br>1-0 V | QUEUE WRITE POINTER STATUS (Q WPS):  DEFINES THE CURRENT STATUS FOR THE WRITE POINTER.  00 = POINTER IS AVAILABLE AND VALID.  01 = POINTER IS TEMP. BEING USED BY ANOTHER  LPB DEVICE.  10 = THE QUEUE IS FULL.  11 = THE QUEUE IS NOT ENABLED, POINTER IS INVALID.   |

FIG. 34B

FIG. 34A

FIG. 34B

FIG. 35

Oct. 17, 1995

# FIG 36

|            |                        | 1 IG. 30                                                                          |                            |

|------------|------------------------|-----------------------------------------------------------------------------------|----------------------------|

|            | MSB                    | ·                                                                                 | LSB                        |

| IBM<br>VEN | 0 1 2 3<br>15 14 13 12 | 4   5   6   7   8   9   10   11   12   1<br>  11   10   9   8   7   6   5   4   3 | 3   14   15  <br>2   1   0 |

| WORD 0     | RESERVED               | QUEUE READ POINTER (QRP)                                                          | Q RPS                      |

| WORD 1     | RESERVED               | QUEUE WRITE POINTER (QWP)                                                         | Q WPS                      |

| WORD | BITS             | NAME: DESCRIPTION                                                                                                                                                                                                                                                     |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| . 0  | 0-3 I<br>15-12 V | RESERVED.                                                                                                                                                                                                                                                             |

| 0    | 4-13 I<br>11-2 V | QUEUE READ POINTER (QRP): DEFINES THE CURRENT VALUE OF THE QUEUE READ POINTER. FOR 4 BYTE QUEUES ALL 10-BITS ARE VALID, FOR 8 BYTE QUEUES ONLY THE UPPER 9-BITS ARE VALID, AND FOR 16 BYTE QUEUES ONLY THE UPPER 8-BITS ARE VALID. NON-VALID BITS MUST BE SET TO '0'. |

| 0    | 14-15 l<br>1-0 V | QUEUE READ POINTER STATUS (Q RPS): DEFINES THE CURRENT STATUS FOR THE READ POINTER. 00 = POINTER IS AVAILABLE AND VALID. 01 = POINTER IS TEMP. BEING USED BY ANOTHER LPB DEVICE. 10 = THE QUEUE IS EMPTY. 11 = THE QUEUE IS NOT ENABLED, POINTER IS INVALID.          |

| 1    | 0-3 l<br>15-12 V | RESERVED.                                                                                                                                                                                                                                                             |

| 1    | 4-13  <br>11-2 V | QUEUE WRITE POINTER (QWP):  DEFINES THE CURRENT VALUE OF THE QUEUE WRITE POINTER.  FOR 4 BYTE QUEUES ALL 10-BITS ARE VALID, FOR 8 BYTE QUEUES ONLY THE UPPER 9-BITS ARE VALID, FOR 16 BYTE QUEUES ONLY THE UPPER 8-BITS ARE VALID. NON-VALID BITS MUST BE SET TO '0'. |

| 1    | 14-15 I<br>1-0 V | QUEUE WRITE POINTER STATUS (Q WPS):  DEFINES THE CURRENT STATUS FOR THE WRITE POINTER.  00 = POINTER IS AVAILABLE AND VALID.  01 = POINTER IS TEMP. BEING USED BY ANOTHER  LPB DEVICE.  10 = THE QUEUE IS FULL.  11 = THE QUEUE IS NOT ENABLED, POINTER IS INVALID.   |

FIG. 37

FIG. 38

FIG. 39

FIG. 40

|                            | MSB |     |        |   |     |     |     | LSB |            |

|----------------------------|-----|-----|--------|---|-----|-----|-----|-----|------------|

| MC I/O ADDRESS             | 0   | 1 6 | 2<br>5 | 3 | 4 3 | 5 2 | 6   | 7   | IBM<br>VEN |

| MIC CR MC I/O BA + 00000   |     | QUE | UE #   | ŀ | STA | TUS | ACK | AVL |            |

| MIC CR MC I/O BA + 00000   | 0   | 0   | 0      | 0 | 0   | 0   | 0   | 0   |            |

| MIC CR MC I/O BA + 00000   | 0   | 0   | 0      | 0 | 0   | 0   | 0   | 0   |            |

| MIC CR MC I/O BA + 00000 → | 0   | 0   | 0      | 0 | 0   | 0   | 0   | 0   |            |

| CR MC I/O BA+ '00000' BITS 0 - 3 I 7 - 4 V  | STATUS: Q #: (READ/WRITE)  THE NUMBER OF THE QUEUE BEING REQUESTED FOR A QUEUE READ OPERATION. VALUES OF '0000' THROUGH '1111' ARE VALID.                                                                                                                                 |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR MC I/O BA+ '00000' BITS 4 - 5 I 3 - 2 V  | STATUS: (READ ONLY)  RETURN STATUS ON THE QUEUE READ OPERATION.  00 - QUEUE READ DATA READY  01 - QUEUE READ DATA NOT READY  1X - QUEUE READ DATA ERROR                                                                                                                   |

| CR MC I/O BA+<br>'00000'<br>BITS 6 I<br>1 V | ACKNOWLEDGE (ACK): (READ ONLY)  USED TO CLEAR THE QRC REGISTER SEMAPHORE AND MAKE THE MIC AVAILABLE FOR ANOTHER QUEUE READ OPERATION.  0 = NO EFFECT (WRITE) 0 = VALID (READ)  1 = CLEAR SEMAPHORE (WRITE) 1 = INVALID (READ)                                             |

| CR MC I/O BA+<br>'00000'<br>BITS 7 I<br>0 V | AVAILABLE (AVL): (READ ONLY)  THIS IS THE QRC REGISTER SEMAPHORE WHICH INDICATES THE AVAILABILITY OF PERFORMING A QUEUE READ OPERATION.  0 = OPERATION TEMPORARILY UNABAILABLE, CONTROL OF OPERATION HAS ALREADY BEEN OBTAINED BY ANOTHER USER.  1 = OPERATION AVAILABLE. |

| CR MC I/O BA+ '00001' THROUGH '00011'       | RESERVED AT A '0' VALUE.                                                                                                                                                                                                                                                  |

|                                          | MSB<br>0 | 1 | 2    | 3 | 4 3         | 5 | 6   | LSB | IBM |

|------------------------------------------|----------|---|------|---|-------------|---|-----|-----|-----|

| MC I/O ADDRESS  MIC CR MC I/O BA + 00000 | 7        |   | UE # |   | <del></del> |   | ACK | AVL | VEN |

| MIC CR MC I/O BA + 000000                | 0        | 0 | 0    | 0 | 0           | 0 | 0   | 0   |     |

| MIC CR MC I/O BA + 00000.                | 0        | 0 | 0    | 0 | 0           | 0 | 0   | 0   |     |

| MIC CR MC I/O BA + 00000                 | 0        | 0 | 0    | 0 | 0           | 0 | 0   | 0   |     |

| CR MC I/O BA+ '00000' BITS 0 - 3 I 7 - 4 V | STATUS: Q #: (READ/WRITE)  THE NUMBER OF THE QUEUE BEING REQUESTED FOR A QUEUE READ OPERATION. VALUES OF '0000' THROUGH '1111' ARE VALID.                                                                                                                                  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR MC I/O BA+ '00100' BITS 4 - 5 I 3 - 2 V | QUEUE BYTE COUNT (QBC): (READ/WRITE)  THE QUEUE BYTE COUNT FOR QUEUE WRITE OPERATIONS.  00 = 4 BYTES                                                                                                                                                                       |

| CR MC I/O BA+ '00100' BITS 6 I 1 V         | ACKNOWLEDGE (ACK): (READ/WRITE)  USED TO CLEAR THE QWC REGISTER SEMAPHORE AND MAKE THE MIC AVAILABLE FOR ANOTHER QUEUE WRITE OPERATION.  0 = NO EFFECT (WRITE)                                                                                                             |

| CR MC I/O BA+ '00100' BITS 7 I 0 V         | AVAILABLE (AVL): (READ ONLY)  THIS IS THE QWC REGISTER SEMAPHORE WHICH INDICATES THE AVAILABILITY OF PERFORMING A QUEUE WRITE OPERATION.  0 = OPERATION TEMPORARILY UNABAILABLE, CONTROL OF OPERATION HAS ALREADY BEEN OBTAINED BY ANOTHER USER.  1 = OPERATION AVAILABLE. |

| CR MC I/O BA+ '00101' THROUGH '00111'      | RESERVED AT A '0' VALUE.                                                                                                                                                                                                                                                   |

FIG. 43

ABORT/CLEAR QUEUE READ QPERATION

FIG. 44

# ABORT/CLEAR QUEUE WRITE QPERATION

# SYSTEM AND METHOD FOR MANAGING QUEUE READ AND WRITE POINTERS

This application is a continuation of U.S. patent application Ser. No. 07/755,468, filed Sep. 5, 1991, by J. L. 5 Swarts et al., entitled "Queue Pointer Manager" assigned to the same assignee as this application now abandoned.

#### BACKGROUND OF THE INVENTION

### 1. Technical Field

The present invention relates in general to data communications between components of a data processing system. More particularly, the invention relates to a queue management facility partially implemented in hardware resulting in 15 a relatively inexpensive queuing mechanism with increased performance over totally software managed queue structures.

#### 2. Background of the Invention

In data processing systems, a queue is commonly used to store a backlog of tasks that have been assigned to a unit of the system by other system units. A queue is implemented as memory, or a portion of memory, in which items of information—queue entries—are stored in the order in which they are received from the task requesting units, and from which they are retrieved in the same order by the task performing unit. Some queues have been managed by hardware logic circuitry and other queues have been managed by program or microprogrammed routines.

Two implementations of queues are common. One is a first-in/first-out (FIFO) memory, having the property that an item of information loaded into its input register, which is located at the tail end of the queue, automatically propagates through empty memory locations towards output registers 35 located at the head end of the queue, and is stored in the first empty location closest to the output register. Retrieval of an item of information from the output register causes all items remaining in the FIFO to shift one location closer to the output register. The other common implementation of a queue is a circular buffer having a read and write pointer associated therewith. The read pointer indicates the location at the head end of the queue from which the next item of information is to be retrieved and the write pointer indicates the location at the tail end of the queue into which the next 45 item of information is to be stored. Retrieval of an item causes the read pointer to point to the next consecutive location that holds information, while storage of an item of information causes the write pointer to point to the next consecutive free location, available for information storage. 50

In conventional data processing systems, task requestors and the task performer are allowed to communicate to the queue only. That is, a task requestor may not transfer a task to the task performer directly, by bypassing the queue, even when the task performer is idle or waiting receipt of a task.

The process of storing a task in a queue, then either propagating it through the FIFO queue or changing pointers on a circular buffer queue, and finally retrieving a task from the queue, takes time and hence the system is slowed down by these procedures and performance is adversely affected. Conventional queue administration systems are often not efficient in transferring information between devices that store information in the queue and devices that retrieve information from the queue.

Queues implemented in hardware are expensive and 65 require a lot of integrated circuitry. Hardware managed queue structures require memory address buses, data bus,

2

and multiplexing logic. There is a great deal of complexity in the memory timing and control logic necessary to access the queue memory. Because of these timing delays, there is a great latency in queue data transfers because of the indivisible, uninterruptible memory operations needed.

In a software managed queue structure there is a need to update the software and verify the queue write and queue read pointers. There is a need to determine queue overflow, underflow and other error conditions. The software must be used to set/clear the queue interrupts. Much internal central processing time and external memory sources are needed to hold the necessary pointer array. The programming code storage requirements of a software managed queue is very large.

What is needed is a relatively inexpensive queuing mechanism with increased performance to handle high speed data communications within a data processing system.

#### **OBJECTS OF THE INVENTION**

It is therefore an object of the invention to provide a queue management facility partially implemented in hardware resulting in a relatively inexpensive mechanism with increased performance over a totally software managed queue structure.

It is another object of the invention to provide a queue pointer manager that can be controlled by either hardware or software.

It is another object of this invention to provide a built-in public queue capability whereby a given queue may be written or read by more than one data processing entity.

### SUMMARY OF THE INVENTION

These and other objects, features and advantages are accomplished by a queue pointer manager having its performance critical functions implemented in hardware and the rest of the facility implemented in software. The hardware function consists of a read pointer register having a status field. The status field specifies queue busy/available, empty/full, and enable/disable information. Built-in hardware controls a write pointer region having a status field for each queue. Also in hardware is an interrupt field for each queue to denote which interrupt is activated when the queue goes non-empty, and a queue block length field for each queue to define the queue entry length in bytes. The hardware resources are implemented in fast-access registers. The pointers contain memory addresses to a general purpose random access memory in which the physical queue elements reside. The queue pointer manager is mapped into the CPU memory and/or input/output spaces. The above fields may be initialized by one region and actual queue operations may be performed by another region.

The facility software function involves reading either the queue read pointer or queue write pointer to perform queue read/write operations, checking the status of the queue, reading or writing the queue entry data as normal memory accesses and then returning the queue read pointer or write pointer to the queue pointer manager hardware function.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These and other objects, features and advantages of the invention will be more fully appreciated with reference to the accompanying figures.

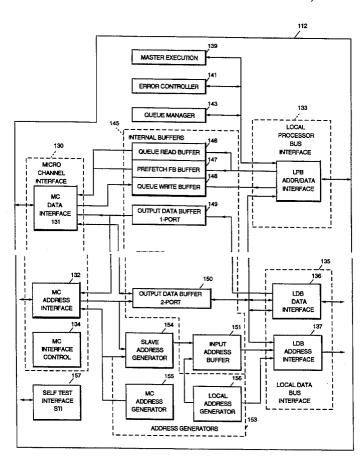

FIG. 1 is a representation of a local area network of personal computers, workstations and main frames.

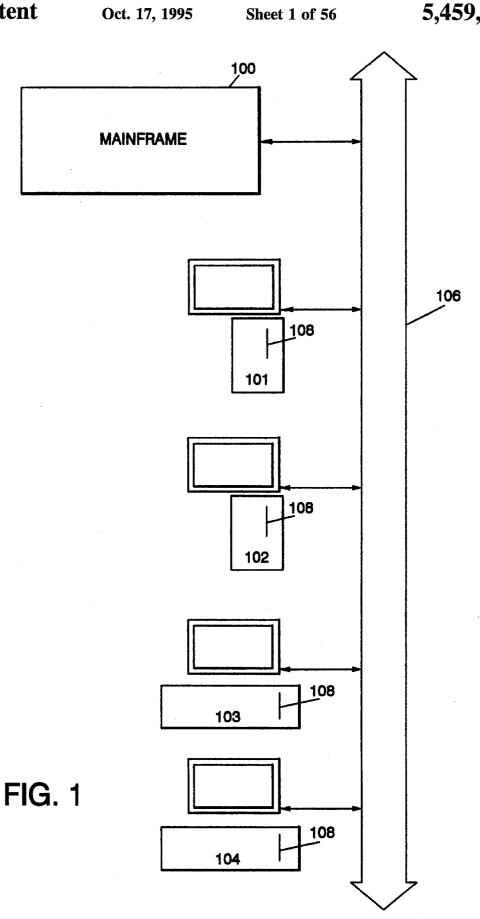

FIG. 2 is a block diagram of an interface according to the

present invention which links a Micro Channel bus to an external fiber optic bus through a local data bus and a local processor bus.

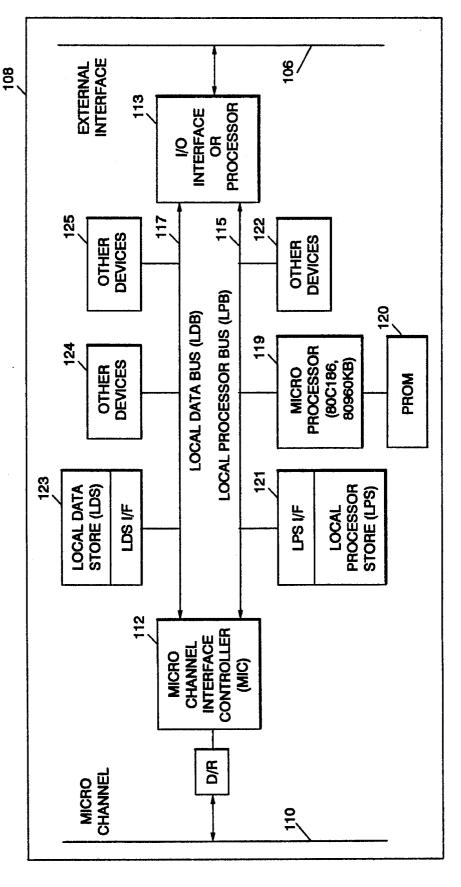

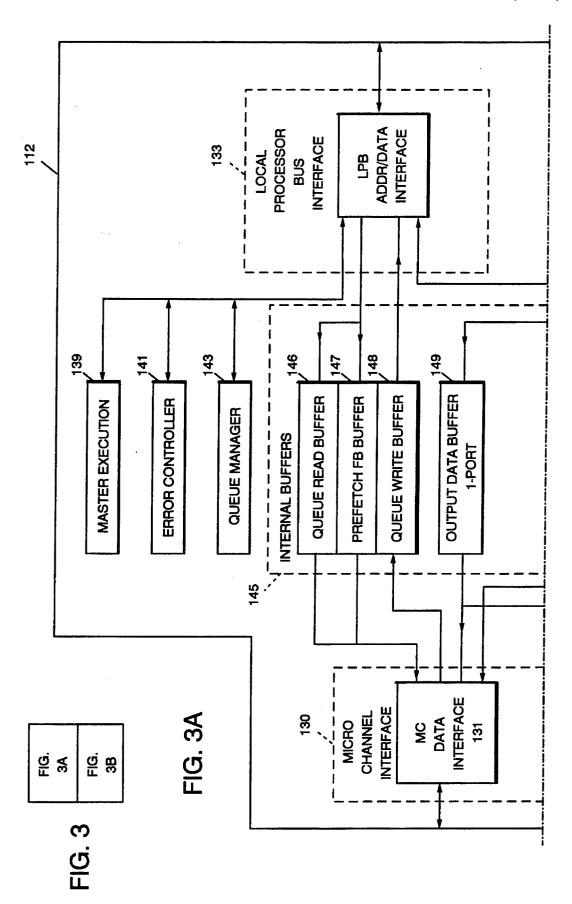

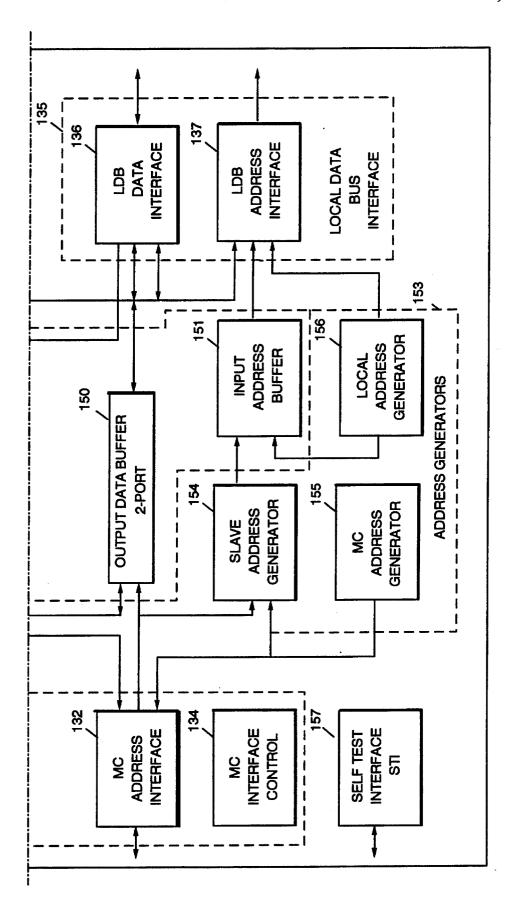

- FIGS. 3, 3A, and 3B are a block diagram of the Micro Channel interface chip.

- FIGS. 4, 4A, and 4B are a diagram of the external I/O pins to the Micro Channel in interface controller of the present invention.

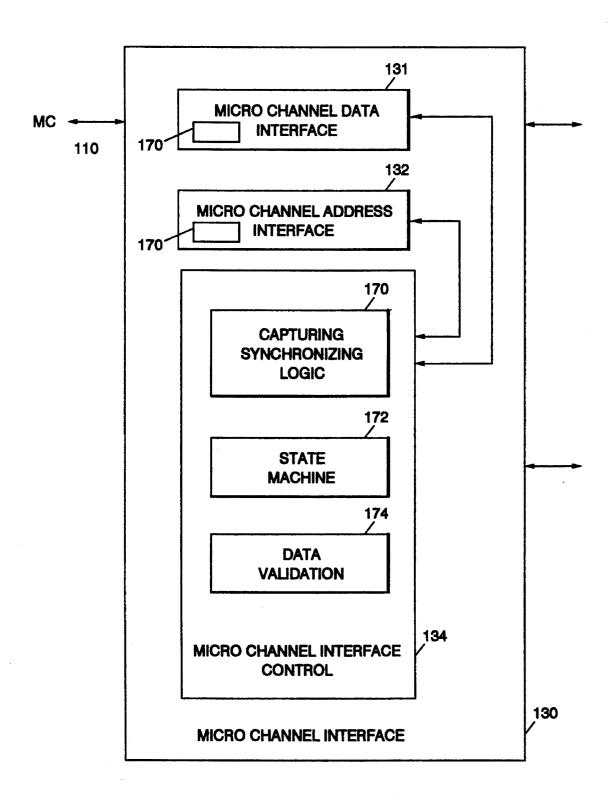

- FIG. 5 is a block diagram of the Micro Channel interface according to the present invention.

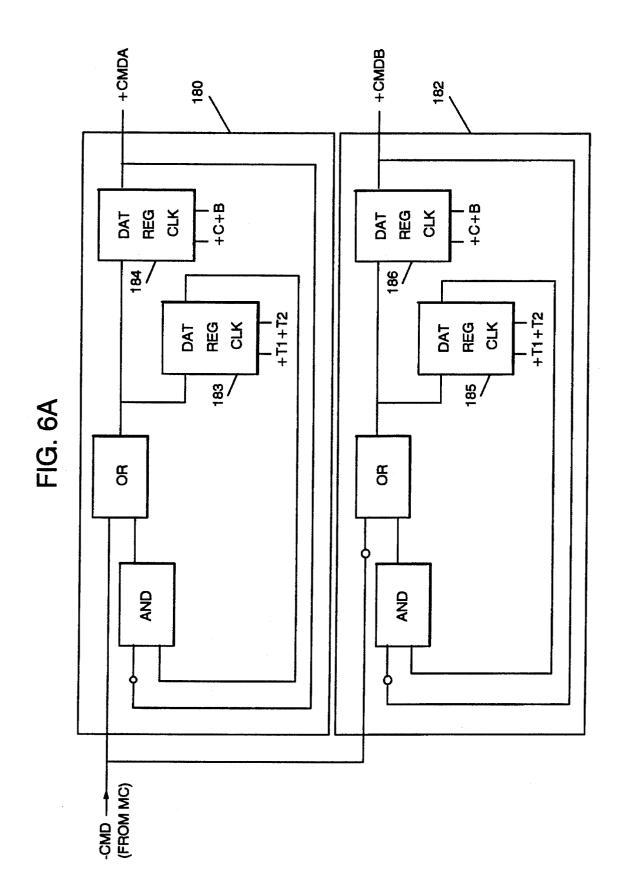

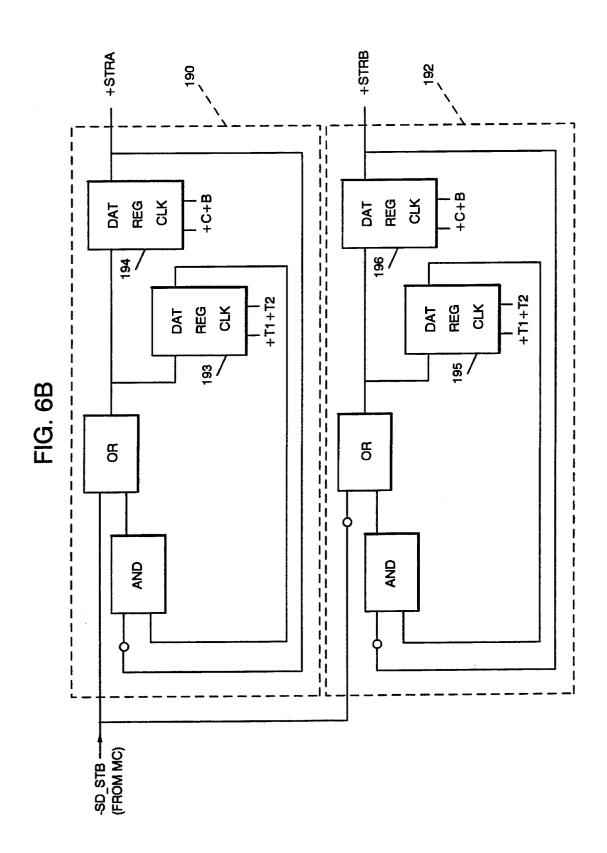

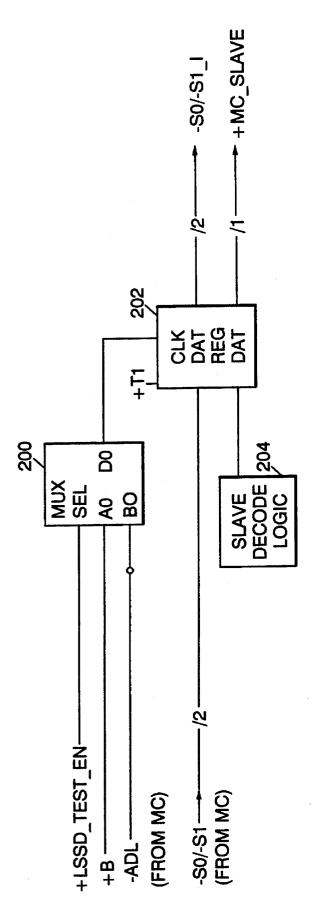

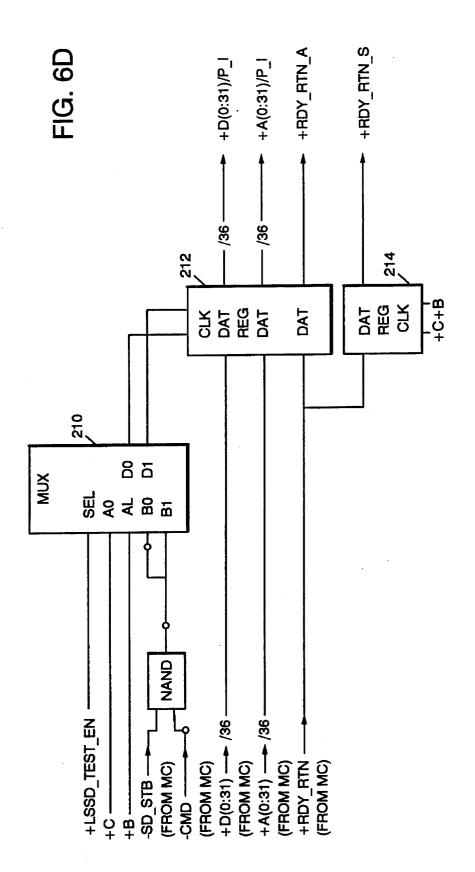

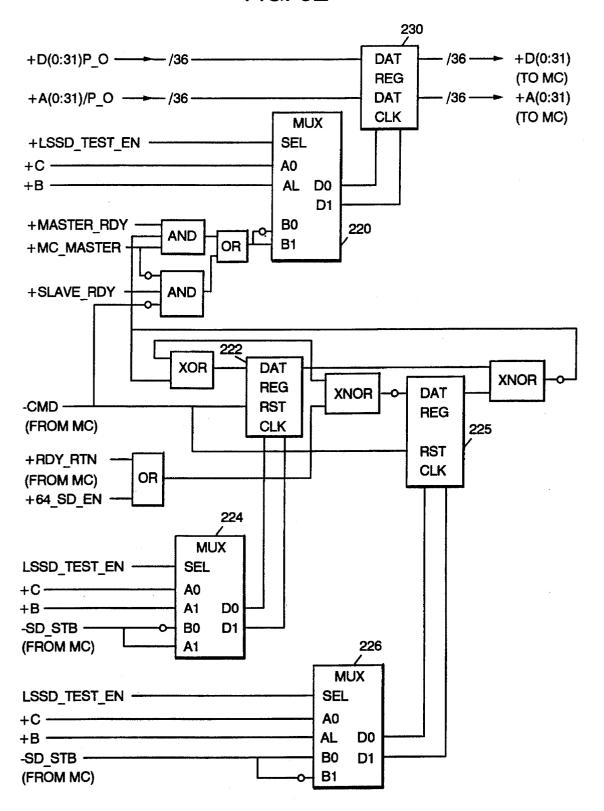

- FIGS. 6A-6E depict the logic in the control and data signal capturing and synchronizing block in the Micro Channel interface of the present invention.

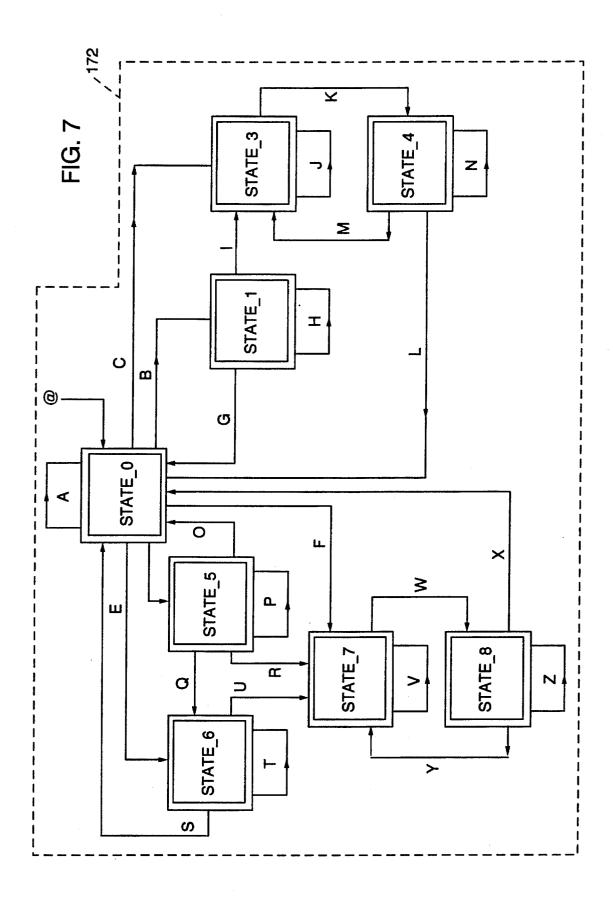

- FIG. 7 is a representation of a state machine in the Micro  $_{\mbox{\scriptsize 15}}$  Channel.

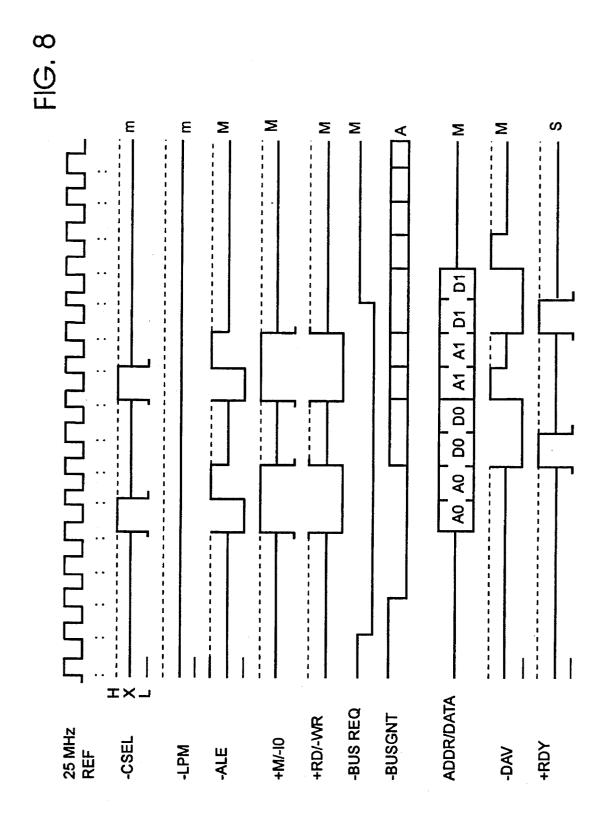

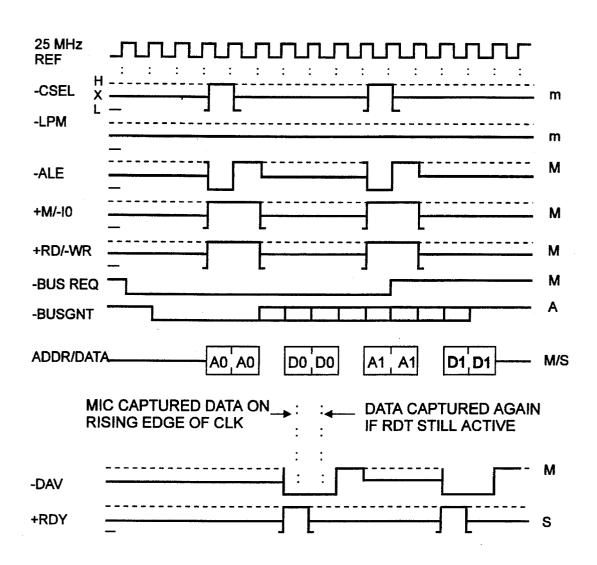

- FIG. 8 depicts a timing diagram where two words are written on the local processor bus.

- FIG. 9 depicts a timing diagram where two words are read from the local processor bus.

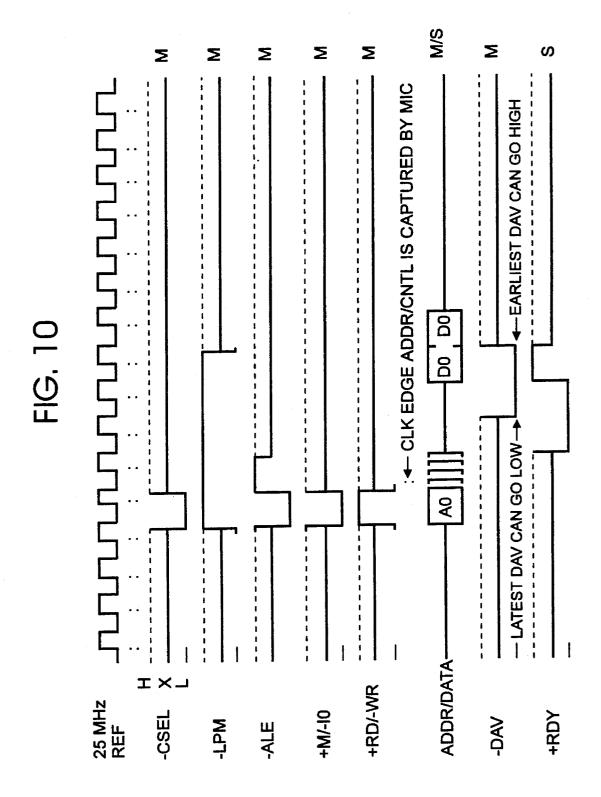

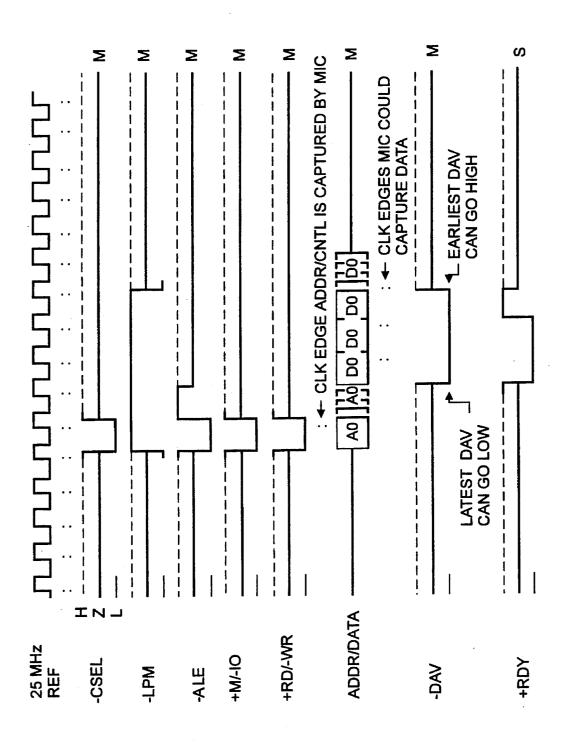

- FIG. 10 depicts a timing diagram where a read operation takes place in the Micro Channel interface chip while it is in a slave timing mode with two 25 MHz wait states.

- FIG. 11 depicts a timing diagram where a write operation takes place on the Micro Channel interface chip while it is in a slave timing mode with two 25 MHz wait states.

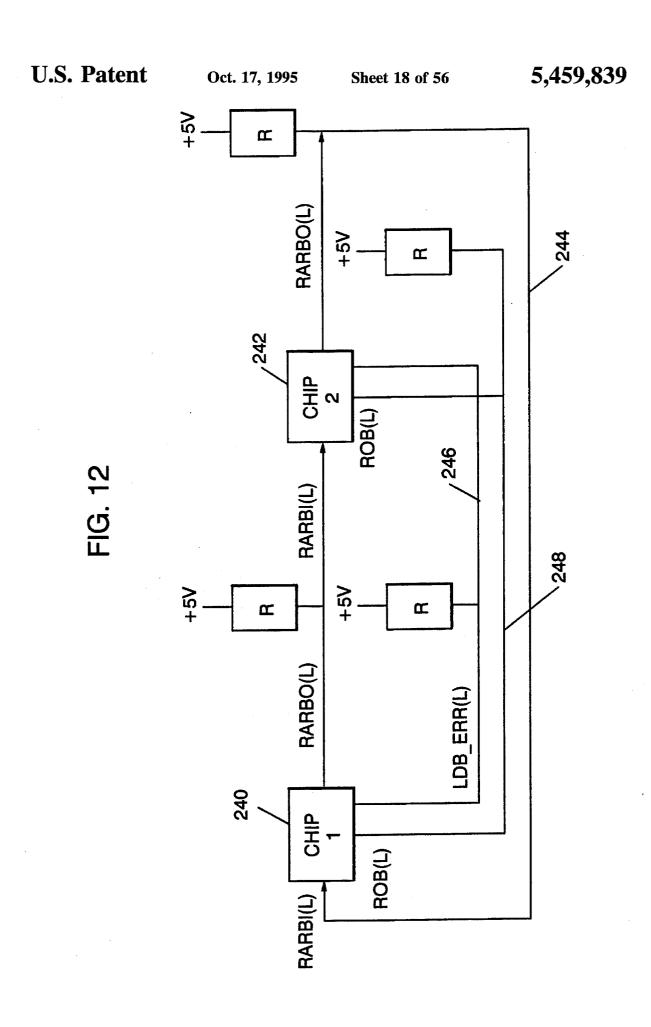

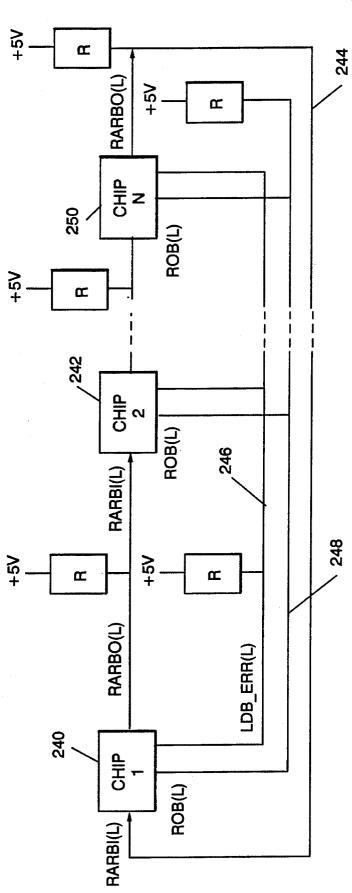

- FIG. 12 is a block diagram of the protocol signal connections for a two chip ring.

- FIG. 13 is a block diagram of the protocol signal connections for a multi-chip ring.

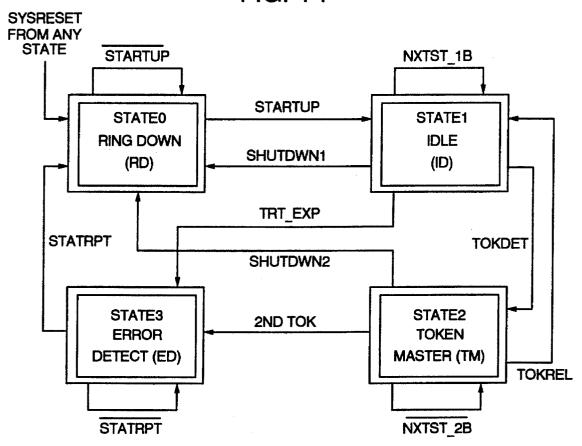

- FIG. 14 is a block diagram of the local data bus ring state machine

- FIGS. 15A-1 and 15A-2 are a block diagram of the local data bus protocol boundary logic.

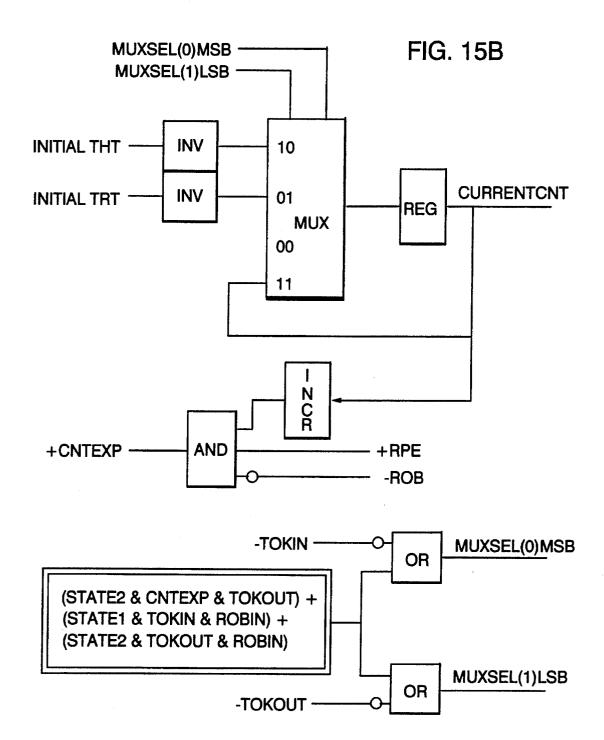

- FIG. 15B is a block diagram of the TRT and THT logic timers on the local data bus.

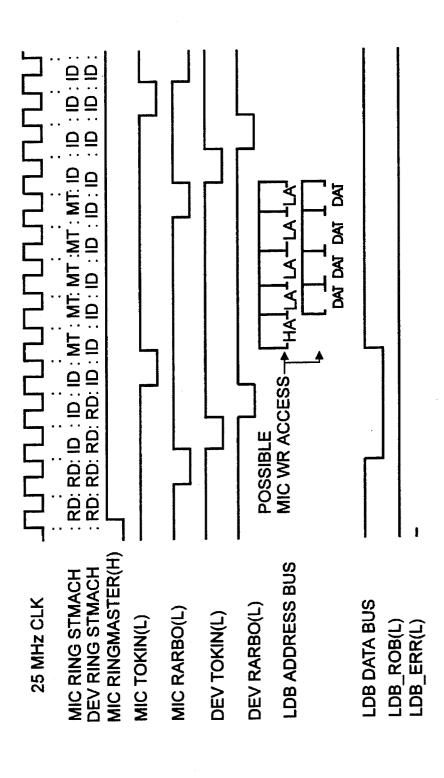

- FIG. 16 is a timing diagram of the local data bus start-up with immediate access to the Micro Channel interface chip.  $_{40}$

- FIG. 17 is a timing diagram for driving the local data bus signals.

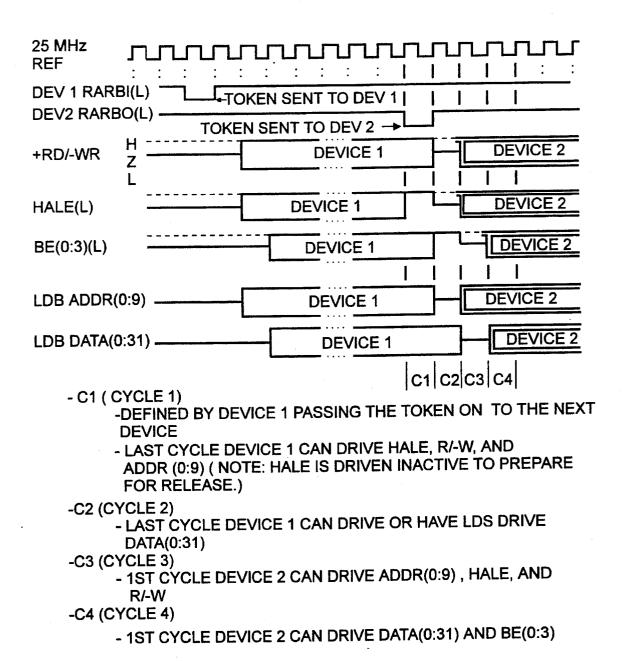

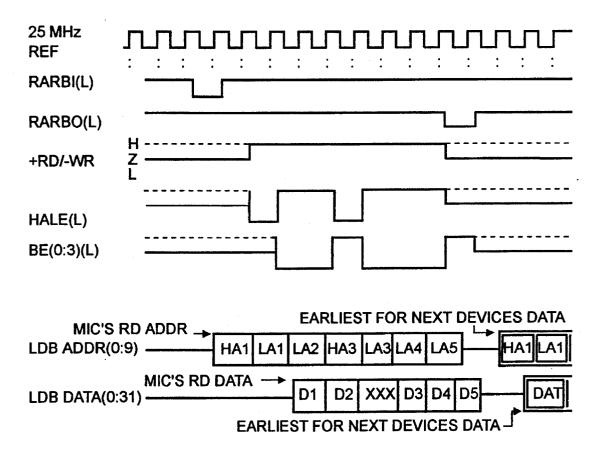

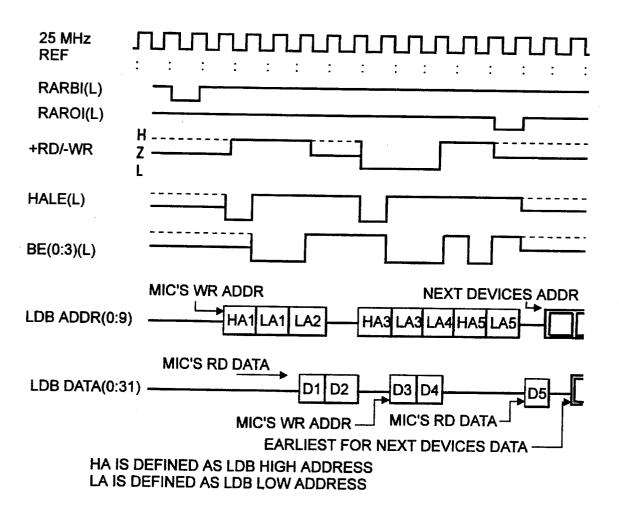

- FIG. 18 is a timing diagram of the local data bus depicting a Micro Channel interface chip read of five words with no wait states.

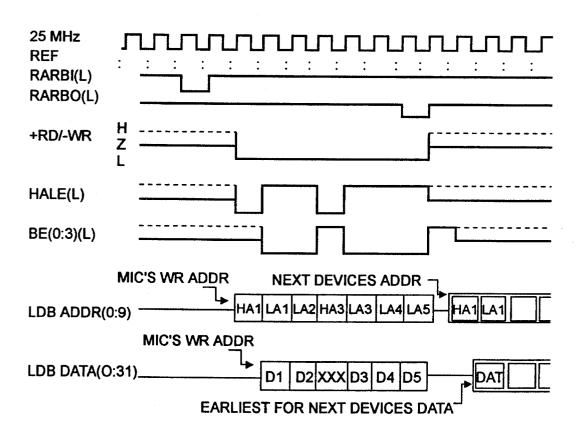

- FIG. 19 is a timing diagram of the local data bus depicting a Micro Channel interface chip write of five words.

- FIG. 20 is a timing diagram of the local data bus depicting a Micro Channel interface chip read of two words, write of two words and read of one word.

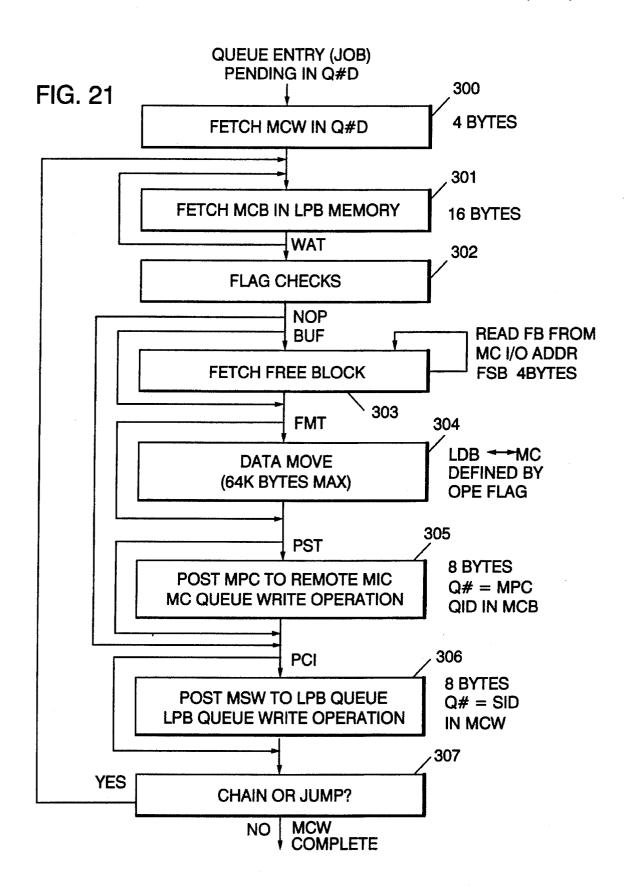

- FIG. 21 is a flow diagram of the master execution process.

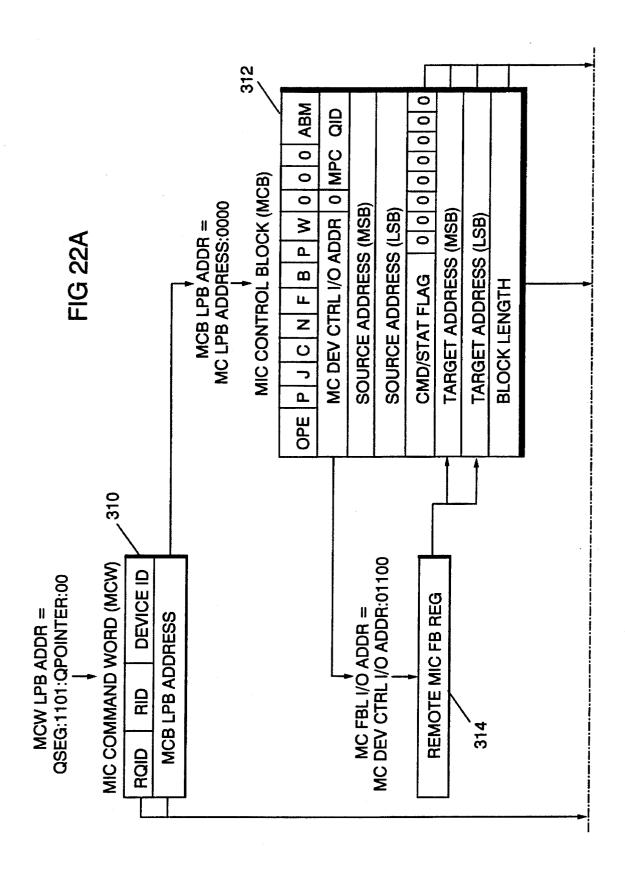

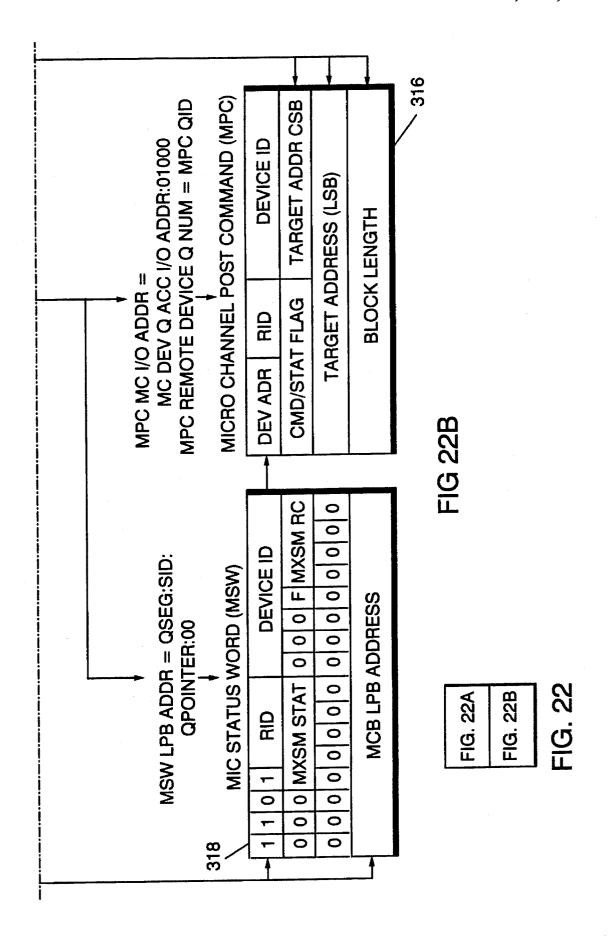

- FIGS. 22, 22A, and 22B are a block diagram depicting the relationship between the command word, the control block, the status word and the post command for the Micro Channel 55 interface chip.

- FIG. 23 depicts the fields within the Micro Channel interface chip command word.

- FIGS. 24–27 depict the fields within the Micro Channel interface chip control block.

- FIG. 28 depicts the valid combinations of Micro Channel interface chip control block flags in a preferred embodiment.

- FIGS. 29, 29A, and 29B depict the fields of the Micro Channel interface chip status word.

- FIG. 30 shows the fields of the Micro Channel interface chip post command.

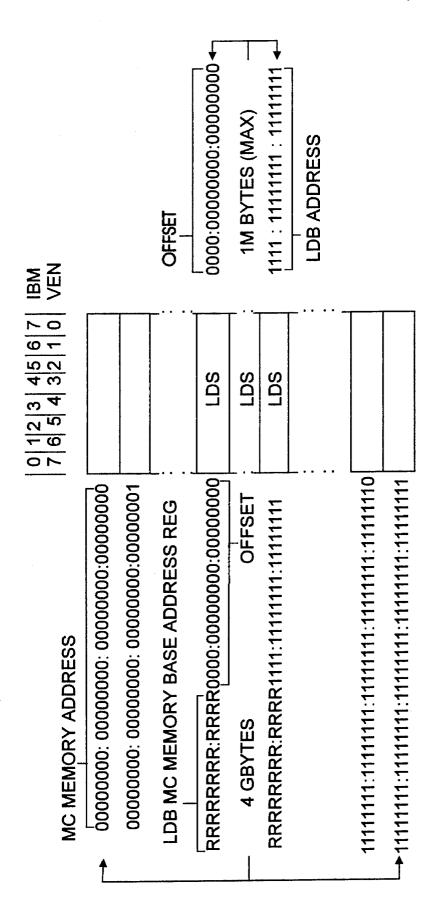

- FIG. 31 depicts the Micro Channel versus local data bus access memory map.

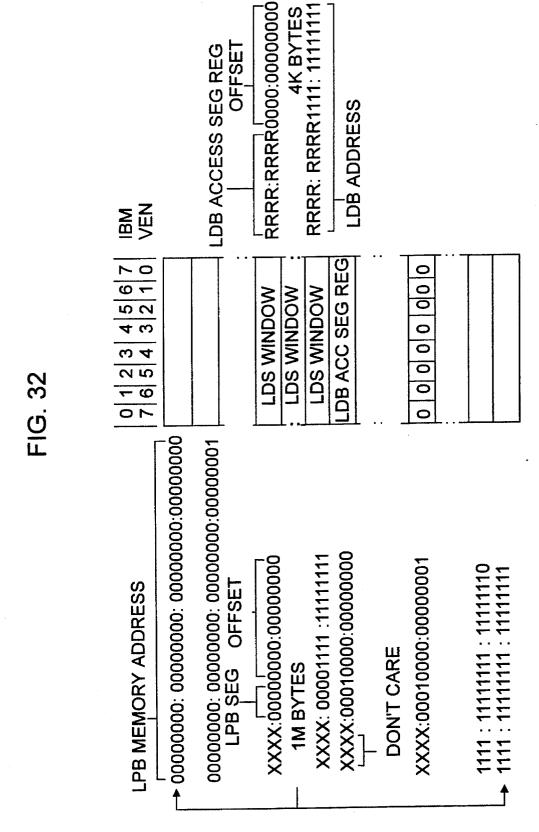

- FIG. 32 depicts the local processor bus to local data bus access memory map.

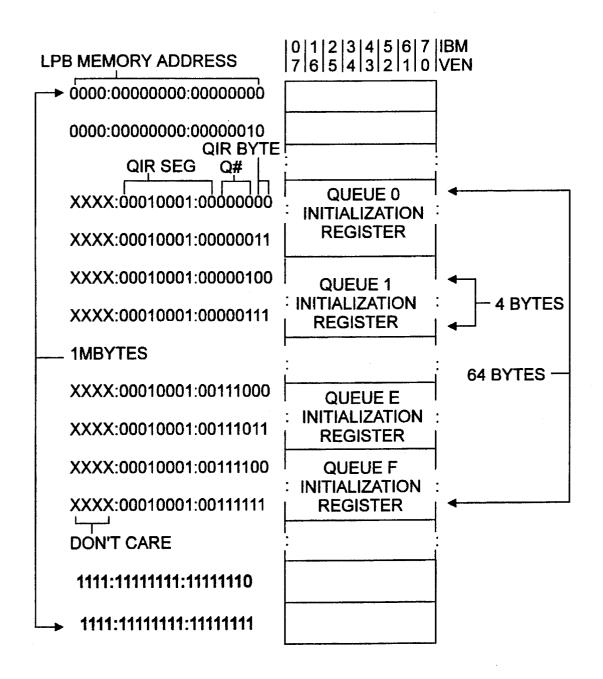

- FIG. 33 depicts the local processor bus memory map showing the queue initialization registers.

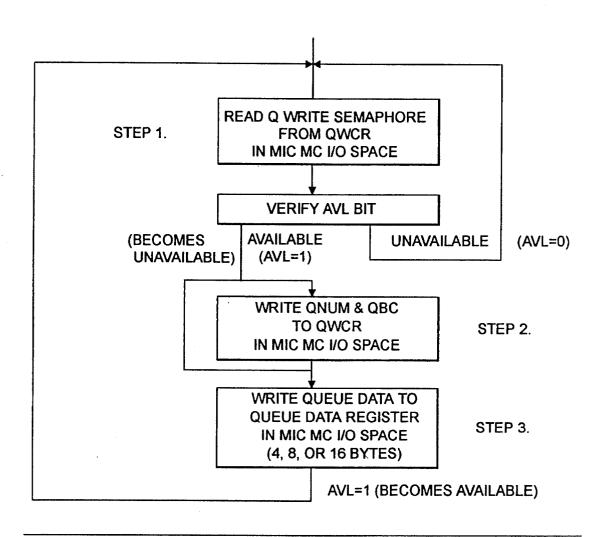

- FIGS. 34, 34A, and 34B show the fields in a queue initialization register according to the present invention.

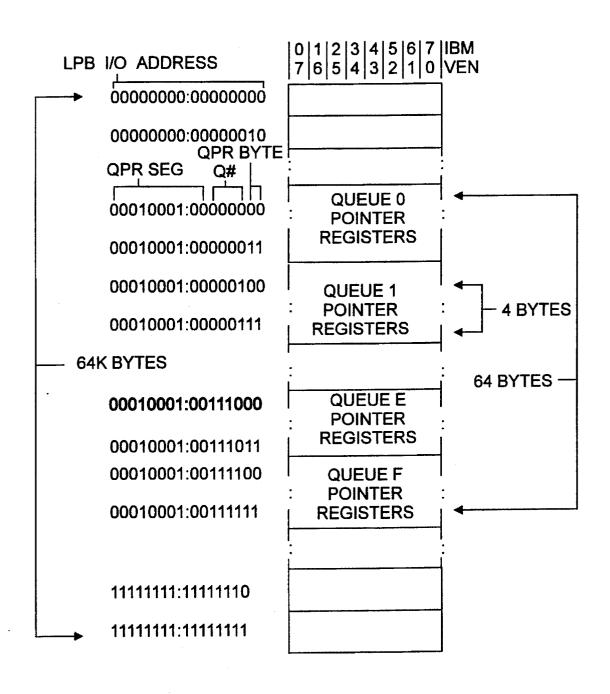

- FIG. 35 depicts the local processor bus I/O map showing the queue pointer registers.

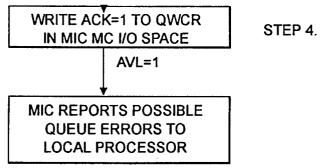

- FIG. 36 shows a preferred layout of a queue pointer register.

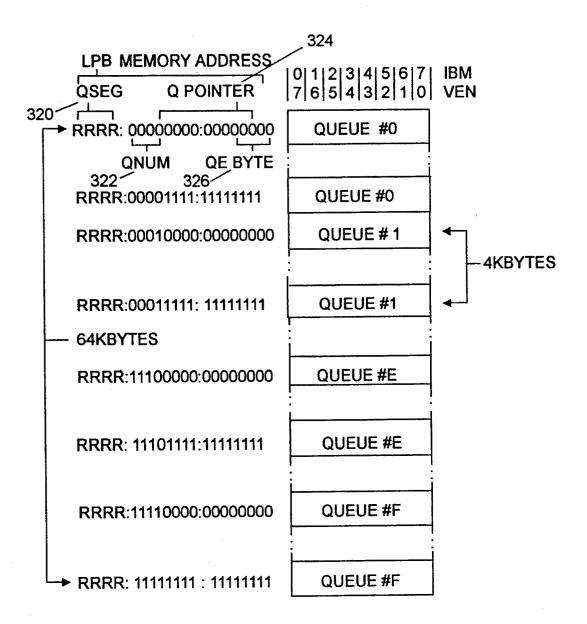

- FIG. 37 depicts the relative addresses of queues within the local process bus.

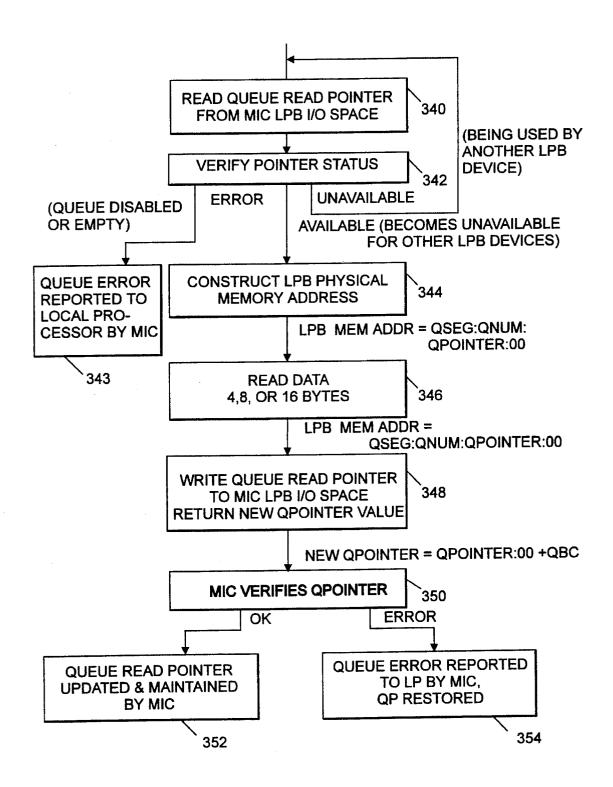

- FIG. 38 is a flow diagram of the local processor bus queue read operation protocol flow.

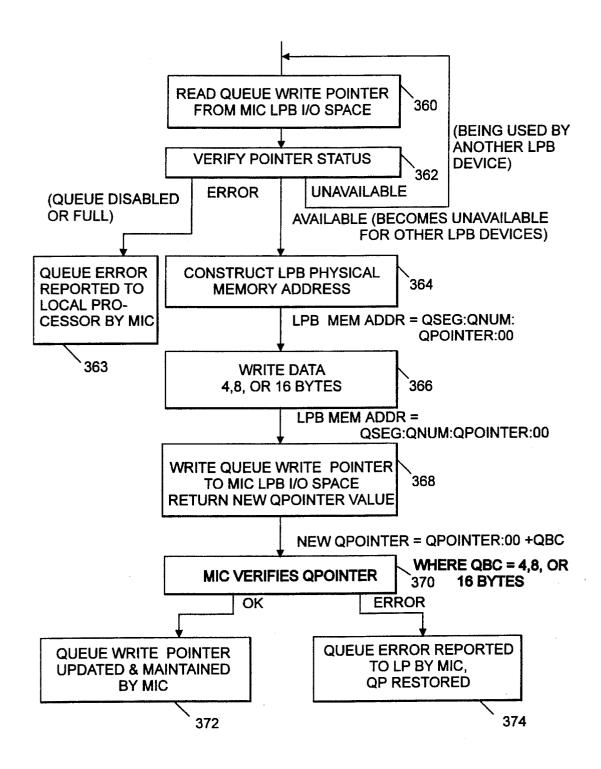

- FIG. 39 is a flow diagram of the local processor bus queue write operation protocol flow.

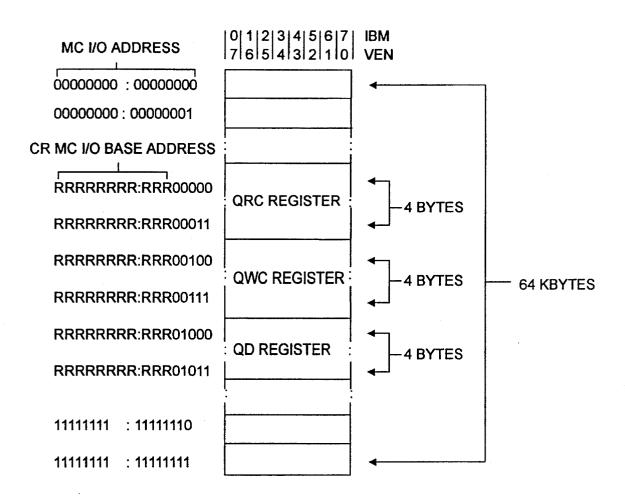

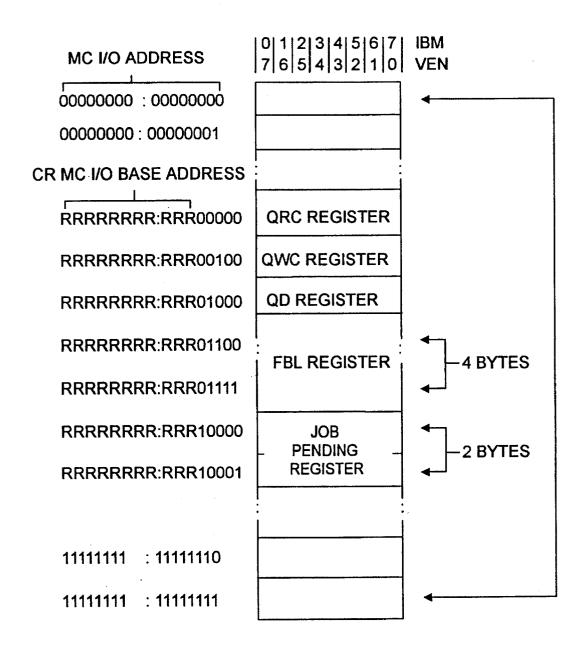

- FIG. 40 depicts the queue read control register, the queue write control register and the queue data register mapped against their Micro Channel I/O addresses.

- FIG. 41 depicts the queue read control register.

- FIG. 42 depicts the queue write control register.

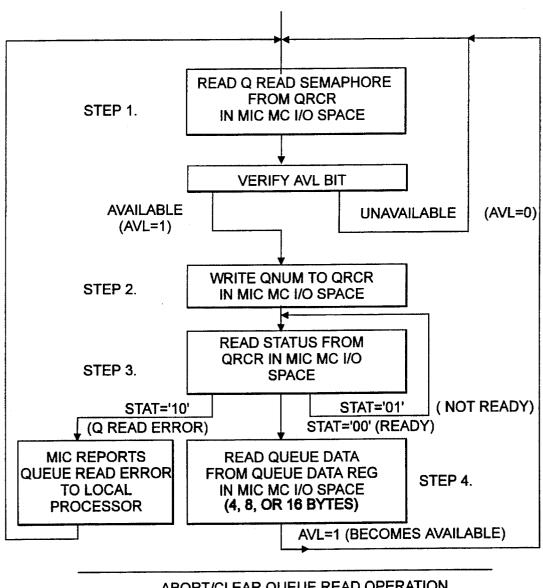

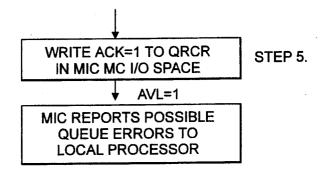

- FIG. 43 is a flow diagram of the Micro Channel queue read operation protocol flow.

- FIG. 44 is a flow diagram of the Micro Channel queue write operation protocol flow.

- FIG. 45 depicts the free block list and job pending register mapped against the Micro Channel I/O map.

# DETAILED DESCRIPTION OF THE INVENTION

The following definitions will be helpful to the reader in understanding the following description.

| Term                        | Definition                                                                                                                                 |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Byte                        | A group of eight signal lines contained within a bus.                                                                                      |

| Bus Participants            | Any device engaging in a data transfer or request of a bus.                                                                                |

| Central                     | A group of system logic responsible for                                                                                                    |

| Steering Logic              | assisting devices in maintaining and<br>controlling Micro Channel data bus width<br>compatibility.                                         |

| Device                      | A block of logic which drives or receives information onto or from a bus, interprets the information and/or performs a specified function. |

| I/O Slave                   | A slave device which is addressable within the I/O address space of the bus.                                                               |

| Master                      | A device which gains control of a bus with<br>the intent of causing a data transfer<br>to/from a slave.                                    |

| Memory Slave                | A slave device which contains memory within the bus addressable space.                                                                     |

| Vode                        | A device.                                                                                                                                  |

| Queue                       | A sequence of stored data or Queue Entries awaiting processing.                                                                            |

| Queue Entry                 | 4, 8, or 16 bytes of stored data which together define a task, control, or informational data to be processed at a later time              |

| Queue Read<br>Pointer (QRP) | A pointer to the current sequential location of the next Queue Entry to be processed.                                                      |

| Queue Write                 | A pointer to the current sequential                                                                                                        |

| Term          | Definition                                                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Pointer (QWP) | location where a Queue Entry can be appended to a Queue.                                                                                  |

| Resource      | A block of logic or device which makes itself accessible to a device for an information exchange.                                         |

| Semaphore     | A flag or indication of current status.                                                                                                   |

| Slave         | A device which provides or receives data during an operation under the control of a master.                                               |

| Steering      | Directing the bytes contained in a bus to another byte within the bus.                                                                    |

| System        | A group of system logic responsible for                                                                                                   |

| Controller    | Micro Channel arbitration, device<br>selection, system memory refresh, unique<br>functions, and interfacing with the system<br>processor. |

| Transfer      | An exchange of information between two devices.                                                                                           |

| Word          | A group of 16 signals contained in a bus, two bytes.                                                                                      |

FIG. 1 depicts a mainframe 100 such as an IBM mainframe following the 370 architecture connected to workstations 101 and 102 and personal computers 103 and 104 by means of a serial bus 106. In the preferred embodiment, the mainframe is an IBM mainframe following the 370 architecture such as the 3090, or ES/9000 (TM), the workstations 101 and 102 are IBM RISC System/6000's (TM) and the personal computers are in the IBM PS/2 (TM) family. The workstations 101, 102 and personal computers comprise 30 well known components such as a system processor unit, ROM, RAM, one or more system busses, a keyboard, a mouse and a display. Further information can be found on the RISC System/6000 in IBM RISC System/6000 POWERstation and POWERserver Hardware Technical Reference - 35 General Information Manual (SA23-2643), IBM RISC System/6000 POWERstation and POWERserver Hardware Technical Reference - Options and Devices (SA23-2646). IBM RISC System/6000 Hardware Technical Reference -7012 POWERstation and POWERserver (SA23-2660), IBM 40 RISC System/6000 Hardware Technical Reference - 7013 and 7016 POWERstation and POWERserver (SA23-2644) and IBM RISC System/6000 Hardware Technical Reference - 7015 POWERserver (SA23-2645). Information on the PS/2 family can be found in Technical Reference Manual Personal System Model 50,60 Systems, Part No. 68X2224, Order No. S68X-2224 and Technical Reference Manual Personal Systems (Model 80), Part No. 68X2256, Order No. S68X-2256. A description of the serial bus architecture can be found in Serial I/O Architecture: PKD081102, Feb. 29, 1989. Both the RISC System/6000 and the PS/2 incorporate the Micro Channel Bus as their systems bus. The Micro Channel contains a 32-bit address bus, a 32-bit data bus, an arbitration bus and a variety of control signals. Further information can be found on the Micro Channel in Low-End Parallel Bus Architecture, Family 2: LEPB-ADS-0002-00-4-U7 and Personal System/2 - Hardware Interface Technical Reference Architectures, Part No. 84F9808, Order No. X84F-9808-00. All the above references are available from the IBM Corporation.

All of the workstations and personal computers 101–104 interface with serial bus 106 by means of a Micro Channel to Serial Bus Adapter (MCSB) card 108. FIG. 2 shows a functional block diagram of the various components of the MCSB card 108. Serial bus 106 and Micro Channel Bus 110 65 are coupled to the serial interface 113 and the Micro Channel Interface controller (MIC) 112 respectively. The MIC chip

6

112 is a high performance interface between three busses: the Micro Channel, a general purpose microprocessor bus called the Local Processor Bus 115, and a dedicated data bus called the Local Data Bus 117. The purpose of the MIC 112 is to translate the protocol on these three busses and allow for quick and efficient data and control transfers between them. The MIC 112 is intended to be used on high speed I/O or processing adapters which require preprocessing, additional processing or data management functions before/after data can be moved to or sent by a device on the Micro Channel

Serial interface 113 represents the serial input/output circuitry which includes optical digital signal conversion, clock recovery synchronization, serial to parallel conversion, optic decoding and coding and clock conversion. The MIC 112 and the serial interface 113 are joined by the Local Processor Bus 115 and local data bus 117. The Local Processor 119 is preferably an INTEL 80960 (TM) processor which provides the processing power for the Micro Channel to serial bus interface 108. The Local Processor 119 also includes programmable read only memory 120 (same or different chip). A Local Processor Store 121 is also coupled to the Local Processor Bus 115 and provides storage for the INTEL 80960 programs as well as storage for the MIC 112 logic. PROM 120 contains diagnostics and initialization code for the devices coupled the Local Processor Bus 115. Other devices 122 such as printers, modems or video monitors can be coupled to the Local Processor Bus 115. The local data bus 117 is used for the data as opposed to processing functions between the MIC chip 112 and serial interface 113. The MIC 112 and serial interface 113 share the local data store 123 which provides a buffer for data which initially comes from either the serial or Micro Channel Busses 106, 110. For example, some data might initially come in from the Micro Channel 110, the MIC 112 would initially store the data in local data storage 123. The MIC 112 would then notify the Local Processor 119 that data is present and the Local Processor 119 would start the serial interface 113 to move the Micro Channel data from the local data store 123 to the serial bus 106.

One preferred embodiment of the Micro Channel to Serial Adapter Card is described in commonly assigned copending application Serial No. 07/693,834, and is entitled "Serial Channel Adapter" filed Apr. 30, 1991 now abandoned in favor of U.S. patent application No. 08/206,290, filed Mar. 7, 1994, which is hereby incorporated by reference. Other commonly assigned, copending applications related to the present invention include: "Micro Channel Interface Controller" by J. L. Swarts, et al., filed Sep. 5, 1991, as U.S. patent application No. 07/755,477, abandoned in favor of U.S. patent application No. 08/101,793, filed Aug. 2, 1993, now U.S. Pat. No. 5,379,386 issued Jan. 3, 1995 which describes the functions of the MIC 112; "1-Bit Token Ring Arbitration Architecture" by G. L. Guthrie, et al., filed Sep. 5, 1991 as U.S. patent application No. 07/755,474, now U.S. Pat. No. 5,388,223 issued Feb. 2, 1995; and "Micro Channel Interface State Machine and Logic" by J. L. Swarts, filed Sep. 5, 1991 as U.S. patent application No. 07/755,476.

Below is a summary of highlighted features/functions which the MIC 112 supports.

Micro Channel Interface Features

Master and Slave capability

10 MHz Streaming Data transfer rate

16/32/64-bit Streaming Data transfer widths

Bus Steering

Burst capability

Programmable Memory and I/O space utilization Memory Address capability of 4 G bytes I/O Address capability of 64K bytes Peer to peer capability

reer to peer capabil

Fairness

Address and Data Parity

Up to 8 Interrupts

Access to Vital Product Data

Local Processor Bus Interface Features

Intel 80C186/80960KB compatible bus. Some external MSI logic may be required depending on the specific implementation to guarantee proper interfacing with the microprocessor.

Master and Slave capability

Hardware Queue Management capability

Memory Address capability of 1 Mbyte

Address and Data Parity

Local Data Bus Interface Features

100 M bytes/sec burst transfer rate

Master capability

Address capability of 1 Mbyte

Programmable Read Wait States

Time shared bus arbitration

Address and Data Parity

Extensive error detection and logging

Self-Test capability

Internal Wrap capability

64 byte Data Buffering

# Micro Channel Interface Controller (MIC) Overview

In FIG. 3 the MIC 112 allows data transfers to occur between the MC 110, LDB 117, and LPB 115. To accommodate the high speeds of the MC 110, the MIC 112 provides buffers 145 which improve overall throughput 40 performance.

As shown in FIG. 3, the MIC 112 is partitioned into several functional units. Each of these functional units are dedicated to perform a special operation or task which will in some way interact with one or more of the other functional units. Each of the units contains a lower level of control and/or data logic specifically designed for performing its operation. Together, these units provide the MIC 112 with its interconnections between the MC 110, LDB 117, and LPB 115.

The MC Interface 130 is responsible for implementing the proper timing, control, and data interfacing required to connect the MIC 112 to the Micro Channel 110. The MC Interface 130 contains logic to synchronize, to interpret, and to control address, data, arbitration, parity, interrupt, and control handshaking signals with the other units within the MIC 112. The MC Interface 130 allows the operation of two MC modes, the Basic Transfer mode and the Stream Data Mode.

The Basic Transfer mode defines the default protocol of the MC 110. Most MC compatible devices have the ability to perform operations in this mode. While operating in this mode the MIC 112 can be defined by the following MC bus device types:

Intelligent Bus Controller I/O Slave

8

Memory Slave Setup Slave

When operating as an Intelligent Bus Controller the MIC 112 is considered to be a MC master. The MIC 112 only becomes a MC Master when a commanded transfer has been initiated. While operating as an I/O, Memory or Setup Slave the MIC 112 is considered to be a MC slave. The MIC 112 only becomes a MC slave when initiated by another device acting as a MC Master.

The Stream Data mode allows the MIC 112 to participate in high speed data transfers with other Stream Data mode MC devices. Stream Data mode provides significant performance enhancements for transfers of large blocks of data and automatic speed matching for clock synchronous data transfers. While in Stream Data mode the MIC 112 will operate as one of the following MC types:

Streaming Data Master

Streaming Data Slave

The MIC 112 operates as a Streaming Data Master only when initiated by a commanded transfer and operates as a Streaming Data Slave when initiated by another device acting as a Streaming Data Master. MC Data Interface 131 and MC Address Interface 132 are part of the MC interface and control the data and address information respectively. The Micro Channel Interface 130 also includes control code 134 which includes code used for capturing command and strobe signals of the Micro Channel, the synchronous state machine and data validation code.

The LPB Interface 133 is responsible for implementing the proper timing, control, and data interfacing required to connect the MIC 112 to the Local Processor Bus 115. The LPB Interface 133 contains logic to control the address, data, arbitration, interrupt, parity, error, and control handshaking signals. The MIC 112 can operate as a master or as a slave on the LPB 115. LPB Master operations can be initiated by tasks necessary to execute and complete a commanded transfer, a MC device, a reportable error, or maintenance of the Prefetch Free Block Buffer. Slave operations are controlled by devices on the LPB 115 requesting access to the LDB 117, the MIC's Queue Management function, or error and internal MIC 112 control and initialization registers.

The LDB Interface 135 is responsible for implementing the proper timing, control, and data interfacing required to connect the MIC 112 to the Local Data Bus 117. The LDB Interface 135 contains logic to control the address, data, arbitration, parity, error, and control signals. In the preferred embodiment, unlike the LPB 115 and MC 110 on the LDB 117, the MIC 112 only operates as a LDB Master. LDB Master operations are initiated by a commanded transfer, a MC device, or by a LPB device. However, when not a Master, the MIC 112 can monitor the LDB 117 and check for possible protocol or parity errors. The LDB Interface 135 can be divided in the LDB Data Interface 136 and LDB Address 137 which can handle the data and address signals respectively.

The Master Execution Unit 139 is responsible for controlling and coordinating all commanded transfer activities between other units within the MIC 112. A list of detailed operations and tasks which the Master Execution Unit is capable of performing is shown below:

Monitors the Queue Manager 143 for pending com-65 manded transfers.

Coordinates fetching of MIC Command Words (MCW) and MIC Control Blocks (MCB) with the LPB Interface 133.

Controls the initialization and loading of the Micro Channel Address Generator (MAG) 155, the Local Address Generator 156, and the Output Data Buffer (ODB) 149.

Controls when the MC Interface 130 fetches Free Blocks from other MC devices.

Coordinates the data transfer between the MC Interface 130 and LDB Interface 135.

Coordinates with the MC Interface 130 Queue Write operations for posting completion status to other MC devices

Controls the posting of MIC Status Words (MSW), which indicate completion status of the commanded transfer and possible errors which may have occurred.

The Error Controller (EC) 141 monitors MIC internal 15 activities for possible error situations or conditions. If an error occurs, the EC 141 is responsible for coordinating with the LPB Interface 133 posting of an Unsolicited Status Word (USW).

The Queue Manager 143 (QM) is responsible for controlling hardware pointers indicating the current locations of pending Command Words, Status Words, or Free Blocks and current locations where new Command Words, Status Words, or Free Blocks can be entered. In maintaining these pointers, queues of Command Words, Status Words, or Free Blocks can be stored in a FIFO like manner for later retrieval. The QM 143 is also responsible for indicating to either the MIC 112 or a LPB 119, 122 device whether a Queue contains pending data. The QM 143 has the ability to maintain pointers for 16 Queues located in the LPB Memory 30 space 121 and controlling an assignable interrupt to each Queue. Also, the QM monitors pointer activity for possible errors and reports them to the LPB Interface 133 for later retrieval.

The MIC 112 contains a group of six internal buffers 145. <sup>35</sup> These buffers are used to speed match and coordinate data transfers between the MC, LPB, and LDB Interfaces 130, 133, 135.

The Output Data Buffer (ODB) **149** is a 16×36-bit, 1-port FIFO capable of holding **64** bytes of data and byte parity. The purpose of the ODB **149** is to buffer MC Master data from the MIC LDB Interface **137** to the MC Interface **133** or to the IDB for LDB wrap operations. The loading and unloading of the ODB **149** is controlled by the MIC LDB and MC Interface **135**, **130** under the guidance of the Master Execution unit.

The Input Data Buffer (IDB) **150** is a 16×36-bit, 2-port FIFO, capable of holding **64** bytes of data and byte data parity. The purpose of the IDB **150** is to buffer data transfers during all MC Slave operations and MC Master read operations to and/or from the MIC LDB Interface **135** unit, as well as LDB wrap operations.

The Input Address Buffer (IAB) 151 is a 16×23-bit, 2-port FIFO. The purpose of the IAB 151 is to buffer addresses and 55 control signals related to data stored in the IDB 150. Addresses buffered in the IAB 151 can be loaded from either the Slave Address Generator (SAG) 154 or the Local Address Generator (LAG) 156.

The Queue Read Buffer (QRB) 146 is a 8×18-bit, 2-port 60 FIFO. The purpose of the QRB 146 is to buffer up to 16 bytes of Queue data and parity requested by a MC device. The LPB Interface 133 controls the writing of the QRB 146 under the management of the QM 143 when a request from the MC 110 is made. The QRB 146 can only be read when 65 the MIC 112 is a MC Slave. Read access to the QRB 146 is controlled by the MIC MC Interface 130 using a semaphore

and control register.

The Prefetched Free Block Buffer (FBB) 147 is an 8×18-bit, 2-port FIFO. The purpose of the FBB 147 is to maintain four byte Free Block entries for quick access by a MC device. These Free Block entries contain the starting physical MC Memory address needed to access an available block of memory on the LDB 117. When a MC device has removed a Free Block entry from the FBB 147, the MIC 112 can fetch another FB entry from the MIC LPB Interface 133. In the preferred embodiment, the FBB 147 can only be read when the MIC 112 is a MC Slave.

The Queue write Buffer (QWB) 148 is a 16×25-bit, 2-port FIFO. The purpose of the QWB 148 is to buffer data, parity, and control, which is designed for a Queue on the LPB 115 managed by the QM 143. Up to 32 bytes of Queue data can be buffered. In the preferred embodiment, the QWB 148 can only be written to when the MIC 112 is a MC Slave. Write access to the QWB 148 is controlled by the MC Interface 130 using a semaphore and control register. Read access to the QWB 148 is controlled by the MIC LPB Interface 133 and QM 143.

The MIC 112 contains three Address Generators 153 which provide most of the addressing requirements for data transfer between the MC and LDB Interfaces 130, 135.

The Slave Address Generator (SAG) 154 is used during MC Streaming Data Slave and LDB wrap operations. Its purpose is to provide addresses to the IAB 151 which correlate to the data being received by the MC Interface 130. These addresses are then used by the MIC LDB Interface 135. The SAG 154 can address up to 1 Mbyte of data.