|

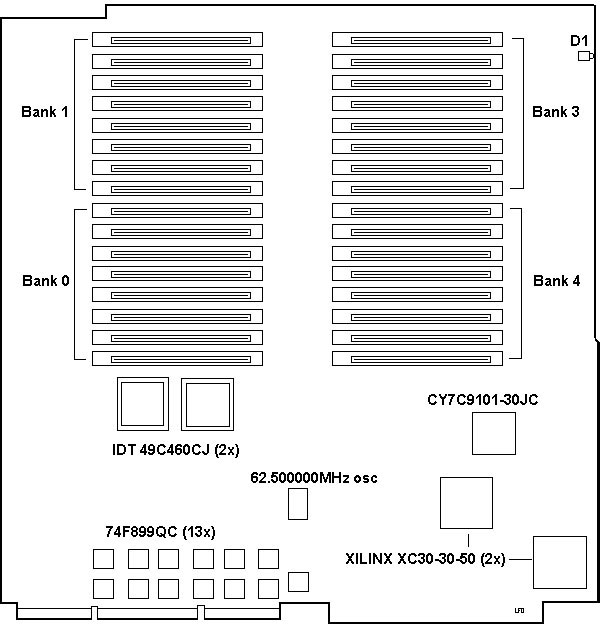

Outline of IPB Memory Slot

IPB Memory Board

49C460CJ 32-bit CMOS Error Detection and Correction Unit

KMM594000A 4Mx9 CMOS DRAM SIMM Memory Module

CY7C9101-30JC CMOS 16-bit ALU Slice Datasheet

74F899QC 9-bit Latchable Transceiver

62.500000MHz osc

ECC-P Memory with 4MB 30 Pin

SIMMs

The memory card has (32) 30 pin SIMM sockets. Each 32 MB

(two banks) has own memory controller. Memory was sold

in 32MB increments. That would be two blocks with four

30 pin SIMMs.

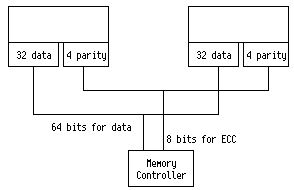

32+4=36, not enough for ECC, BUT... 36+36=72... 64 bits

for data, and 8 bits for ECC... Two 32 bit EDCs can be

chained for a 64 bit word.

So... you need one bank of 8 SIMMs each for ECC-P, so

the minimum is 32MB, the next is two banks (64MB), three

banks (96MB), and four banks for a maximum of 128MB.

-- OR --

So... you need two banks of 4 SIMMs each for ECC-P, so

the minimum is 32MB, the next is four banks (64MB), six

banks (96MB), and 8 banks for a maximum of 128MB.

Which one is right?!

Note: I have seen a

configuration screen, with a choice of "ECC: ON | OFF".

My guess is that ECC=P will not run on an odd number of

banks, so if you wanted to run 48MB, ECC would be "OFF".

Previous IBM servers such as the IBM Server 85 were able

to use standard memory to implement what is known as

ECC-P. ECC-P takes advantage of the fact that a

64-bit word needs 8 bits of parity in order to detect

single-bit errors (one bit/byte of data). Since it is

also possible to use an ECC algorithm on 64 bits of data

with 8 check bits, IBM designed a memory controller

which implements the ECC algorithm using the standard

memory SIMMs.

The following shows the implementation of ECC-P. When

ECC-P is enabled via the reference diskette, the

controller reads/writes two 32-bit words and 8 bits of

check information to standard parity memory. Since 8

check bits are available on a 64-bit word, the system is

able to correct single-bit errors and detect double-bit

errors just like ECC memory.

While ECC-P uses standard non-expensive memory, it needs

a specific memory controller that is able to read/write

the two memory blocks and check and generate the check

bits. Also, the additional logic necessary to

implement the ECC circuitry make it slightly slower than

true ECC memory. Since the price difference between a

standard memory SIMM and an ECC SIMM has narrowed, IBM

no longer implements ECC-P.

Memory Management and OS/2

version 1.3

Up to 128 MB of 80 ns ECC-P memory can be installed in the

Server 295. Although OS/2 1.3 can only address up

to 16 MB of this memory per processor, the rest can be

accessed via the Transparent Reserved Memory Manager

(RMM) utility.

When configured in multiprocessor mode, up to 16 MB of

memory can be assigned to each of the FP and the AP

processors, for a total of 32 MB. This allocation

is done using the utility MPSETUP.

The remaining memory can be accessed via RMM, which is

installed as a device driver. RMM enables this

extra memory to be accessed in a number of ways:

o Disk buffers for the PDAs

o HPFS cache

o Reserved memory for some OS/2 applications - for

example in response to DosAllocSeg and DosAllocHuge

segment requests

o RAM-based virtual disk

o SWAPPER.DAT file used for segment swapping to disk by

OS/2

RMM memory is allocated by the /TRMM= switch in the

CONFIG.SYS and CONFIG.FP files. Status information

on RMM can be displayed using the RMMSTAT utility.

RMM is needed because of the 16-bit limitations of OS/2

1.3, and results in substantial performance improvements

for some applications because massive amounts of data

can be held in memory rather than on disk.

|